EV-ADUCM350AUDZ

Analog Devices Inc.The ADuCM350 is a configurable Impedance Converter and Potentiostat with current and voltage measurement capability for both Electrochemical sensors and Biosensors. It is a complete, coin cell powered, high precision, MCU integrated solution for portable device applications such as point-of-care diagnostics and body-worn devices for monitoring vital signs.The ADuCM350 analog front end (AFE) features a 16-bit, precision, 160 kSPS analog-to-digital converter (ADC); 0.17% precision voltage reference; 12-bit, no missing codes digital-to-analog converter (DAC); and a reconfigurable ultralow leakage switch matrix. It has 4 voltage measurement channels, up to 8 current measurement channels and an impedance measurement DFT engine. The ADuCM350 also includes an ARM Cortex-M3-based processor, memory, and all I/O connectivity to support portable meters with display, USB communication, and active sensors. The ADuCM350 is available in a 120-lead, 8 mm ? 8 mm CSP_BGA and operates from ?40?C to +85?C. To support extremely low dynamic and hibernate power management, the ADuCM350 provides a collection of power modes and features, such as dynamic and software controlled clock gating and power gating.The AFE is connected to the ARM Cortex-M3 via an advanced high performance bus (AHPB) slave interface on the advanced microcontroller bus architecture (AMBA) matrix, as well as direct memory access (DMA) and interrupt connections.APPLICATIONS Point-of-care diagnostics Body-worn devices for monitoring vital signs Amperometric, voltametric, and impedometric measurements

EV-ADUCM350GPIOTHZ

Analog Devices Inc.The ADuCM350 is a configurable Impedance Converter and Potentiostat with current and voltage measurement capability for both Electrochemical sensors and Biosensors. It is a complete, coin cell powered, high precision, MCU integrated solution for portable device applications such as point-of-care diagnostics and body-worn devices for monitoring vital signs.The ADuCM350 analog front end (AFE) features a 16-bit, precision, 160 kSPS analog-to-digital converter (ADC); 0.17% precision voltage reference; 12-bit, no missing codes digital-to-analog converter (DAC); and a reconfigurable ultralow leakage switch matrix. It has 4 voltage measurement channels, up to 8 current measurement channels and an impedance measurement DFT engine. The ADuCM350 also includes an ARM Cortex-M3-based processor, memory, and all I/O connectivity to support portable meters with display, USB communication, and active sensors. The ADuCM350 is available in a 120-lead, 8 mm ? 8 mm CSP_BGA and operates from ?40?C to +85?C. To support extremely low dynamic and hibernate power management, the ADuCM350 provides a collection of power modes and features, such as dynamic and software controlled clock gating and power gating.The AFE is connected to the ARM Cortex-M3 via an advanced high performance bus (AHPB) slave interface on the advanced microcontroller bus architecture (AMBA) matrix, as well as direct memory access (DMA) and interrupt connections.APPLICATIONS Point-of-care diagnostics Body-worn devices for monitoring vital signs Amperometric, voltametric, and impedometric measurements

EV-ADUCM350-SMCZ

Analog Devices Inc.The ADuCM350 is a configurable Impedance Converter and Potentiostat with current and voltage measurement capability for both Electrochemical sensors and Biosensors. It is a complete, coin cell powered, high precision, MCU integrated solution for portable device applications such as point-of-care diagnostics and body-worn devices for monitoring vital signs.The ADuCM350 analog front end (AFE) features a 16-bit, precision, 160 kSPS analog-to-digital converter (ADC); 0.17% precision voltage reference; 12-bit, no missing codes digital-to-analog converter (DAC); and a reconfigurable ultralow leakage switch matrix. It has 4 voltage measurement channels, up to 8 current measurement channels and an impedance measurement DFT engine. The ADuCM350 also includes an ARM Cortex-M3-based processor, memory, and all I/O connectivity to support portable meters with display, USB communication, and active sensors. The ADuCM350 is available in a 120-lead, 8 mm ? 8 mm CSP_BGA and operates from ?40?C to +85?C. To support extremely low dynamic and hibernate power management, the ADuCM350 provides a collection of power modes and features, such as dynamic and software controlled clock gating and power gating.The AFE is connected to the ARM Cortex-M3 via an advanced high performance bus (AHPB) slave interface on the advanced microcontroller bus architecture (AMBA) matrix, as well as direct memory access (DMA) and interrupt connections.APPLICATIONS Point-of-care diagnostics Body-worn devices for monitoring vital signs Amperometric, voltametric, and impedometric measurements

EVAL01-HMC1030LP5E

Analog Devices Inc.The HMC1030LP5E is a dual-channel RMS power detector designed for high accuracy RF power signal measurement and control applications over the 0.1 to 3.9 GHz frequency range. The device can be used with input signals having RMS values from -60 dBm to +10 dBm referenced to 50 Ohm and large crest factors with no accuracy degradation. Each RMS detection channel is fully specified for operation up to 3.9 GHz, over a wide dynamic range of 70 dB. The HMC1030LP5E operates from a single +5V supply and provides two linear-in-dB detection outputs at the RMSA and RMSB pins with scaled slopes of 37 mV/dB. The RMSA and RMSB channel outputs provide RMS detection performance in terms of dynamic range, logarithmic linearity and temperature stability similar to Hittite?s HMC1021LP4E RMS Detector. The RMSA and RMSB outputs provide a read of average input signal power, or true-RMS power. Frequency detection up to 3.9 GHz is possible, with excellent channel matching of less than 1 dB, over a wide range of input frequencies and with low temperature drift. Applications Log ?> Root-Mean-Square (RMS) Conversion Tx/Rx Signal Strength Indication (TSSI / RSSI) Antenna VSWR Monitor Receiver Automatic Gain Control Transmitter Power Control

EVAL01-HMC1056LP4B

Analog Devices Inc.The HMC1056LP4BE is a compact I/Q MMIC mixer in a leadless ?Pb free? SMT package, which can be used as either an Image Reject Mixer or a Single Sideband Upconverter. The mixer utilizes two standard Hittite double balanced mixer cells and a 90 degree hybrid fabricated in a GaAs Schottky diode process. A low frequency quadrature hybrid was used to produce a 100MHz LSB IF output. This product is a much smaller alternative to hybrid style Image Reject Mixers and Single Sideband Upconverter assemblies. The HMC1056LP4BE eliminates the need for wire bonding and allows the use of surface mount manufacturing techniques.APPLICATIONS Point-to-Point and?Point-to-Multi-Point Radio Military Radar, EW & ELINT Satellite Communications Sensors

EVAL01-HMC1097LP4E

Analog Devices Inc.The HMC1097LP4E is a low noise, high linearity Direct Quadrature Modulator RFIC which is ideal for digital modulation applications from 0.1 to 6.0 GHz including; Cellular/3G, WiMAX/4G, Broadband Wireless Access & ISM circuits. Housed in a compact 4x4 mm (LP4) SMT QFN package, the RFIC requires minimal external components & provides a low cost alternative to more complicated double upconversion architectures. The RF output port is single-ended and matched to 50 Ohms with no external components. The LO requires -6 to +6 dBm and can be driven in either differential or single-ended mode. This device is optimized for a +5V supply, and offers improved carrier feedthrough and sideband suppression characteristics.APPLICATIONS UMTS, GSM or CDMA Basestations Fixed Wireless or WLL ISM Transceivers, 900 & 2400 MHz GMSK, QPSK, QAM, SSB Modulators Cellular/3G and WiMAX/4G

EVAL01-HMC190BMS8

Analog Devices Inc.The HMC190BMS8(E) is a low cost SPDT switch in a 8-lead MSOP package. The switch can control signals from DC to 3 GHz. It is especially suited for low and medium power applications using positive control voltages. The two control voltages require a minimal amount of DC current, which is optimal for battery powered radio systems at 0.9, 1.9, and 2.4 GHz. The HMC190BMS8(E) provides exceptional third order intermodulation performance of +56 dBm. The design has been optimized for the small MSOP package, and maintains a VSWR of better than 1.2:1 up to 2 GHz. This device is the positive control MSOP8 packaged version of our HMC239AS8(E) negative control device.APPLICATIONS MMDS & WirelessLAN Portable Wireless

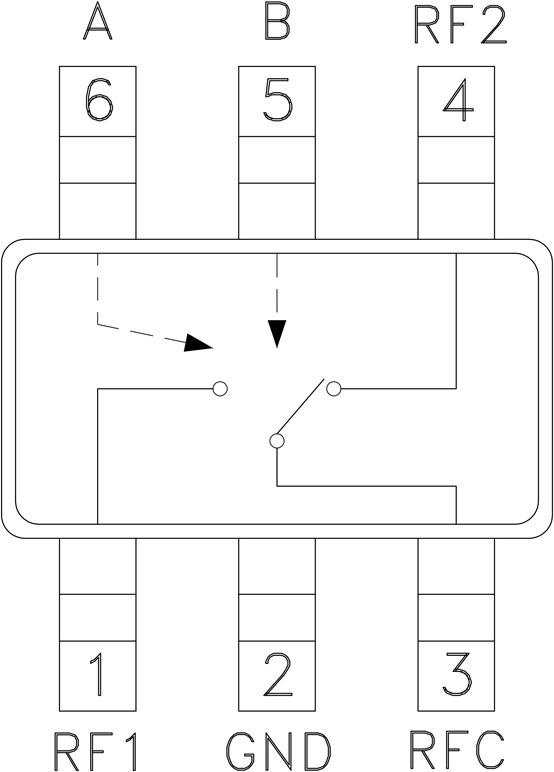

EVAL01-HMC197B

Analog Devices Inc.The HMC197B(E) is a low-cost SPDT switch in a 6-lead SOT26 plastic package for use in general switching applications which require very low insertion loss and very small size. The device can control signals from DC to 3 GHz and is especially suited for 900 MHz, 1.8 - 2.2 GHz, and 2.4 GHz ISM applications with less than 1 dB loss. The design provides exceptional insertion loss performance, ideal for filter and receiver switching. RF1 and RF2 are reflective shorts when ?Off?. The two control voltages require a minimal amount of DC current and offer compatibility with most CMOS & TTL logic families. See HMC221B for same performance in an alternate SOT26 pin-out.APPLICATIONS MMDS & WirelessLAN PCMCIA Wireless Cards Portable WIreless

EVAL01-HMC749LC3C

Analog Devices Inc.The HMC749LC3C is a T Flip-Flop w/Reset designed to support clock frequencies as high as 26 GHz. During normal operation, with the reset pin not asserted, the output toggles from its prior state on the positive edge of the clock. This results in a divide-by two function of the clock input. Asserting the reset pin forces the Q output low regardless of the clock edge state (asynchronous reset assertion). Reversing the clock inputs allows for negative-edge triggered applications. The HMC749LC3C also features an output level control pin, VR, which allows for loss compensation or for signal level optimization.All input signals to the HMC749LC3C are terminated with 50 to Vcc on-chip, and may be either AC or DC coupled. inputs or outputs can be connected directly to a 50 Vcc terminated system, while DC blocking capacitors may be used if the terminating system is 50? ground. The HMC749LC3C operates from a single +3.3V DC supply and is available in a ceramic RoHS compliant 3x3 mm SMT package.APPLICATIONS Serial Data Transmission up to 26 Gbps High Speed Frequency Divider?(up to 26 GHz) Broadband Test & Measurement RF ATE Applications

EVAL01-HMC834LP6GE

Analog Devices Inc.The HMC834LP6GE is a low noise, wide band, Fractional-N Phase-Locked-Loop (PLL) that features an integrated Voltage Controlled Oscillator (VCO) with a fundamental frequency of 2800 MHz - 4200 MHz, and an integrated VCO Output Divider (divide by 1/2/4/6.../60/62) and doubler, that together allow the HMC834LP6GE to generate frequencies from 45 MHz to 1050 MHz, from 1400 MHz to 2100 MHz, from 2800 MHz to 4200 MHz, and from 5600 MHz to 8400 MHz. The integrated Phase Detector (PD) and delta-sigma modulator, capable of operating at up to 100 MHz, permit wider loop-bandwidths with excellent spectral performance.The HMC834LP6GE features industry leading phase noise and spurious performance, across all frequencies, that enable it to minimize blocker effects, and improve receiver sensitivity and transmitter spectral purity. The superior noise floor (< -170 dBc/Hz) makes the HMC834LP6GE an ideal source for a variety of applications - such as; LO for RF mixers, a clock source for high-frequency data-converters, or a tunable reference source for ultra-low spurious applications.Additional features of the HMC834LP6GE include RF output power control from 0 to 6 dB (~2 dB steps), output Mute function, and a delta-sigma modulator Exact Frequency Mode which enables users to generate output frequencies with 0 Hz frequency error.Applications Cellular/4G, WiMax Infrastructure Repeaters and Femtocells Communications Test Equipment CATV Equipment Phased Array Applications DDS Replacement Very High Data Rate Radios Tunable Reference Source for?Spurious- Free Performance

EVAL02-HMC837LP6CE

Analog Devices Inc.The HMC837LP6CE is a fully functioned Fractional-N Phase-Locked-Loop (PLL) Frequency Synthesizer with an Integrated Voltage Controlled Oscillator (VCO). The synthesizer consists of an integrated low noise VCO with a triband output, an autocalibration subsystem for low voltage VCO tuning, a very low noise digital Phase Detector (PD), a precision controlled charge pump, a low noise reference path divider and a fractional divider.The fractional synthesizer features an advanced delta-sigma modulator design that allows both ultra-fine step sizes and low spurious products. The phase detector (PD) features cycle slip prevention (CSP) technology to allow faster frequency hopping times. Ultra low in-close phase noise and low spurious also allows wider loop bandwidths for faster frequency hopping and low micro-phonics.For theory of operation and register map refer to the 'PLLs with Integrated VCO - RF VCOs' Operating Guide.Applications Cellular/4G Infrastructure Repeaters & Femtocells Communications?Test Equipment CATV Equipment Phased Array Applications DDS Replacement? Very High Data Rate Radios

EVAL-24TSSOPEBZ

Analog Devices Inc.The ADG1414 is a monolithic complementary metal oxide semiconductor (CMOS) device containing eight independently selectable switches designed on an industrial CMOS (iCMOS?) process. iCMOS is a modular manufacturing process combining high voltage CMOS and bipolar technologies. iCMOS components can tolerate high supply voltages while providing increased performance, dramatically lower power consumption, and reduce the package size.The ADG1414 is a set of octal SPST (single-pole, single-throw) switches controlled via a 3-wire serial interface. On resistance is closely matched between switches and is very flat over the full signal range. Each switch conducts equally well in both directions and the input signal range extends to the supplies.Data is written to these devices in the form of eight bits; each bit corresponds to one channel.The ADG1414 utilizes a versatile 3-wire serial interface that operates at clock rates of up to 50 MHz and is compatible with standard SPI?, QSPI?, MICROWIRE?, and DSP interface standards. The output of the shift register, SDO, enables a number of these parts to be daisy chained.On power-up, all switches are in the off condition, and the internal registers contain all zeros.PRODUCT HIGHLIGHTS 50 MHz serial interface. 9.5 ? on resistance. 1.6 ? on-resistance flatness. 24-lead TSSOP and 4 mm ? 4 mm LFCSP packages.APPLICATIONS Automatic test equipment Data acquisition systems Battery-powered systems Sample-and-hold systems Audio signal routing Video signal routing Communication systems

EVAL-2LCANRS485EBZ

Analog Devices Inc.The ADM3053 is an isolated controller area network (CAN) physical layer transceiver with an integrated isolated dc-to-dc converter. The ADM3053 complies with the ISO 11898 standard.The device employs Analog Devices, Inc., iCoupler? technology to combine a 2-channel isolator, a CAN transceiver, and Analog Devices isoPower? dc-to-dc converter into a single SOIC surface mount package. An on-chip oscillator outputs a pair of square waveforms that drive an internal transformer to provide isolated power. The device is powered by a single 5 V supply realizing a fully isolated CAN solution.The ADM3053 creates a fully isolated interface between the CAN protocol controller and the physical layer bus. It is capable of running at data rates of up to 1 Mbps.The device has current limiting and thermal shutdown features to protect against output short circuits. The part is fully specified over the industrial temperature range and is available in a 20-lead, wide-body SOIC package.The ADM3053 contains isoPower technology that uses high frequency switching elements to transfer power through the transformer. Special care must be taken during printed circuit board (PCB) layout to meet emissions standards. Refer to the AN-0971 Application Note, Control of Radiated Emissions with?isoPower Devices, for details on board layout considerations.Applications CAN data buses Industrial field networks

EVAL-AD1940AZ

Analog Devices Inc.The AD1940 /?AD1941 are a complete 28-bit, single-chip, multi-channel audio SigmaDSP? for equalization, multiband dynamic processing, delay compensation, speaker compensation, and image enhancement. These algorithms can be used to compen-sate for the real world limitations of speakers, amplifiers, and listening environments, resulting in a dramatic improvement of perceived audio quality.The signal processing used in the AD1940 / AD1941 is comparable to that found in high end studio equipment. Most of the processing is done in full, 56-bit double-precision mode, resulting in very good, low level signal performance and the absence of limit cycles or idle tones. The dynamics processor uses a sophisticated, multiple-breakpoint algorithm often found in high end broadcast compressors. The AD1940 / AD1941 are a fully programmable DSP. Easy to use software allows the user to graphically configure a custom signal processing flow using blocks such as biquad filters, dynamics processors, and surround sound processors. An extensive control port allows click-free parameter updates, along with readback capability from any point in the algorithm flow.The AD1940 / AD1941?s digital input and output ports allow a glueless connection to ADCs and DACs by multiple, 2-channel serial data streams or TDM data streams. When in TDM mode, the AD1940 / AD1941 can input 8 or 16 channels of serial data, and can output 8 or 16 channels of serial data. The input and output port configurations can be individually set. The AD1940 is controlled by a 4-wire SPI? port; the AD1941 is controlled by a 2-wire I2C? bus. Other than the control interface, the functions of the two parts are identical. APPLICATIONS Automotive sound systems Digital televisions Home theater systems (Dolby digital/DTS postprocessor) Multichannel audio systems Mini-component stereos Multimedia audio Digital speaker crossover Musical instruments In-seat sound systems (aircrafts/motor coaches)

EVAL-AD2S1210SDZ

Analog Devices Inc.The AD2S1210 is a complete 10-bit to 16-bit resolution tracking resolver-to-digital converter, integrating an on-board programmable sinusoidal oscillator that provides sine wave excitation for resolvers.The converter accepts 3.15 V p-p ? 27% input signals, in the range of 2 kHz to 20 kHz on the sine and cosine inputs. A Type II servo loop is employed to track the inputs and convert the input sine and cosine information into a digital representation of the input angle and velocity. The maximum tracking rate is 3125 rps.The AD2S1210WDSTZ and the AD2S1210WDSTZRL7 models have been approved by an independent accredited body for use in Automotive Safety Integrity Level B rated applications according to ISO 26262. Contact your local Analog Devices, Inc., sales office to obtain a copy of the safety manual and ASIL B safety assessment certificate. PRODUCT HIGHLIGHTS Ratiometric tracking conversion. The Type II tracking loop provides continuous output position data without conversion delay. It also provides noise immunity and tolerance of harmonic distortion on the reference and input signals. System fault detection. A fault detection circuit can sense loss of resolver signals, out-of-range input signals, input signal mismatch, or loss of position tracking. The fault detection threshold levels can be individually programmed by the user for optimization within a particular application. Input signal range. The sine and cosine inputs can accept differential input voltages of 3.15 V p-p ? 27%. Programmable excitation frequency. Excitation frequency is easily programmable to a number of standard frequencies between 2 kHz and 20 kHz. Triple format position data. Absolute 10-bit to 16-bit angular position data is accessed via either a 16-bit parallel port or a 4-wire serial interface. Incremental encoder emulation is in standard A-quad-B format with direction output available. Digital velocity output. 10-bit to 16-bit signed digital velocity accessed via either a 16-bit parallel port or a 4-wire serial interface. APPLICATIONS DC and ac servo motor control Encoder emulation Electric power steering Electric vehicles Integrated starter generators/alternators Automotive motion sensing and control

EVAL-AD3542RFMCZ

Analog Devices Inc.The AD3542R is a low drift, dual channel, ultra-fast, 16-bit accuracy, voltage output digital-to-analog converter (DAC) that can be configured in multiple voltage span ranges. The AD3542R operates with a fixed 2.5 V reference.The device incorporates three drift compensating feedback resistors for the internal transimpedance amplifier (TIA) that scales the output voltage. Offset and gain scaling registers allow for generation of multiple output span ranges, such as 0 V to 2.5 V, 0 V to 5 V, 0 V to 10 V, ?5 V to +5 V, and ?2.5 V to +7.5 V.The DAC can operate in fast mode for maximum speed or precision mode for maximum accuracy.The serial peripheral interface (SPI) can be configured in single SPI (classic SPI) mode, dual SPI mode and synchronous dual SPI mode with single date rate (SDR) or double data rate (DDR), with logical levels from 1.2 V to 1.8 V.To improve device robustness, cyclic redundancy check (CRC) can be enabled. Multiple error checkers have also been integrated to detect VREF failures or memory map corruption.The AD3542R is specified over the extended industrial temperature range (?40?C to +105?C).APPLICATIONS Instrumentation Hardware in the loop Process control equipment Medical devices Automated test equipment Data acquisition system Programmable voltage sources Optical communications

EVAL-AD4000FMCZ

Analog Devices Inc.The AD4000/AD4004/AD4008 are high accuracy, high speed, low power, 16-bit, Easy Drive, precision successive approximation register (SAR) analog-to-digital converters (ADCs) that operate from a single power supply, VDD. The reference voltage, VREF, is applied externally and can be set independent of the supply voltage. The AD4000/AD40004/AD4008 power scales linearly with throughput. Easy Drive features reduce both signal chain complexity and power consumption while enabling higher channel density. The reduced input current, particularly in high-Z mode, coupled with a long signal acquisition phase, eliminates the need for a dedicated ADC driver. Easy Drive broadens the range of companion circuitry that is capable of driving these ADCs (see Figure 2 in the data sheet). Input span compression eliminates the need to provide a negative supply to the ADC driver amplifier while preserving access to the full ADC code range. The input overvoltage clamp protects the ADC inputs against overvoltage events, minimizing disturbances on the reference pin and eliminating the need for external protection diodes. Fast device throughput up to 2 MSPS allows users to accurately capture high frequency signals and to implement oversampling techniques to alleviate the challenges associated with antialias filter designs. Decreased serial peripheral interface (SPI) clock rate requirements reduce digital input and output power consumption, broadens digital host options, and simplifies the task of sending data across digital isolation. The SPI-compatible serial user interface is compatible with 1.8 V, 2.5 V, 3 V, and 5 V logic by using the separate VIO logic supply.APPLICATIONS Automated test equipment Machine automation Medical equipment Battery-powered equipment Precision data acquisition systems Instrumentation and control systems

EVAL-AD4111SDZ

Analog Devices Inc.The AD4111 is a low power, low noise, 24-bit, sigma-delta (?-?) analog-to-digital converter (ADC) that integrates an analog front end (AFE) for fully differential or single-ended, high impedance (?1 M?) bipolar, ?10 V voltage inputs, and 0 mA to 20 mA current inputs.The AD4111 also integrates key analog and digital signal conditioning blocks to configure eight individual setups for each analog input channel in use. The AD4111 features a maximum channel scan rate of 6.21 kSPS (161 ?s) for fully settled data.The embedded 2.5 V, low drift (5 ppm/?C), band gap internal reference (with output reference buffer) reduces the external component count.The digital filter allows flexible settings, including simultaneous 50 Hz and 60 Hz rejection at a 27.27 SPS output data rate. The user can select between the different filter settings depending on the demands of each channel in the application. The automatic channel sequencer enables the ADC to switch through each enabled channel.The precision performance of the AD4111 is achieved by integrating the proprietary iPassives? technology from Analog Devices, Inc. The AD4111 is factory calibrated to achieve a high degree of specified accuracy.The AD4111 also has the unique feature of open wire detection on the voltage inputs for system level diagnostics using a single 5 V or 3.3 V power supply.The AD4111 operates with a single power supply, making it easy to use in galvanically isolated applications. The specified operating temperature range is ?40?C to +105?C. The AD4111 is housed in a 40-lead, 6 mm ? 6 mm LFCSP package.APPLICATIONS Process control PLC and DCS modules Instrumentation and measuremen

EVAL-AD4116ASDZ

Analog Devices Inc.The AD4116 is a low power, low noise, 24-bit, ?-? analog-to-digital converter (ADC) that integrates an analog front end (AFE) for six fully differential or eleven single-ended, high impedance (?10 M?) bipolar, ?10 V voltage inputs. The additional two differential or four single-ended/pseudo differential direct ADC inputs provides excellent performance at lower input ranges.The AD4116 also integrates key analog and digital signal conditioning blocks to configure eight individual setups for each analog input channel in use. As many as 16 channels can be enabled at any time. A channel is defined as any of the standard analog voltage inputs or a low level direct ADC input. The AD4116 features a maximum channel scan rate of 12,422 SPS (80 ?s) using a sinc5 + sinc1 filter and 20,618 SPS per channel (48 ?s) using a sinc3 filter.The embedded 2.5 V, low drift (5 ppm/?C), band gap internal reference (with output reference buffer) reduces the external component count.The digital filter allows flexible settings, including simultaneous 50 Hz and 60 Hz rejection at a 27.27 SPS output data rate. The user can select between the different filter settings depending on the demands of each channel in the application. The automatic channel sequencer enables the ADC to switch through each enabled channel.The precision performance of the AD4116 is achieved by integrating the proprietary iPassives? technology from Analog Devices, Inc.The AD4116 operates with a single power supply, making it easy to use in galvanically isolated applications. The specified operating temperature range is ?40?C to +105?C. The AD4116 is housed in a 40-lead, 6 mm ? 6 mm LFCSP.APPLICATIONS Process control PLC and DCS modules Instrumentation and measurement

EVAL-AD4630-24-KTZ

Analog Devices Inc.The AD4630-24 is a two-channel, simultaneous sampling, Easy Drive, 2 MSPS successive approximation register (SAR) analog-to-digital converter (ADC). With a guaranteed maximum ?0.9 ppm INL and no missing codes at 24-bits, the AD4630-24 achieves unparalleled precision from ?40?C to +125?C. Figure 1 in the data sheet shows the functional architecture of the AD4630-24.A low-drift, internal precision reference buffer eases voltage reference sharing with other system circuitry. The AD4630-24 offers a typical dynamic range of 106 dB when using a 5 V reference. The low noise floor enables signal chains requiring less gain and lower power. A block averaging filter with programmable decimation ratio can increase dynamic range up to 153 dB. The wide differential input and common mode ranges allow inputs to use the full ?VREF range without saturating, simplifying signal conditioning requirements and system calibration. The improved settling of the Easy Drive analog inputs broadens the selection of analog front-end components compatible with the AD4630-24. Both single-ended and differential signals are supported.The versatile Flexi-SPI serial interface eases host processor and ADC integration. A wide data clocking window, multiple SDO lanes, and optional dual data rate (DDR) data clocking can reduce the serial clock to 10 MHz while operating at a sample rate of 2 MSPS. Echo clock mode and ADC master clock mode relax the timing requirements and simplify the use of digital isolators.The 64-ball chip scale package ball grid array (CSP_BGA) of the AD4630-24 integrates all critical power supply and reference bypass capacitors, reducing the footprint and system component count, and lessening sensitivity to board layout.APPLICATIONS Automatic test equipment Digital control loops Medical instrumentation Seismology Semiconductor manufacturing Scientific instrumentation