# **AK8856**

# NTSC/PAL Digital Video Decoder

## **General Description**

The AK8856 decodes NTSC or PAL composite video signals into digital video data. The outputs are ITU-R BT. 601 level compatible Y, Cb and Cr signals. The decoded result is scaled to 601, VGA (interlaced output), CIF, QVGA, QCIF, rotated QVGA, or rotated CIF(progressive). Information including closed caption, VBID, and WSS are encoded in the video signal can be read out externally. The AK8856 is controlled by through an I<sup>2</sup>C interface.

#### **Features**

- NTSC-M, NTSC-4.43 / PAL- B, D, G, H, I, N, Nc, M, 60 composite signal decoding process

- 10 Bit ADC (sampling at 24.5454MHz or 27MHz)

- Integrated PGA (0dB ~ 12dB)

- Automatic color control (ACC) function

- Adaptive automatic gain control (AGC) function

- 1D or 2D YC separation

- Phase compensation for PAL

- · Output interface

- ITU-R BT.656 output format (4:2:2 8-bit parallel output with EAV / SAV)

- Camera interface

- Interface with HD / VD / DVALID signals

- Closed caption decoding function (read by register setting)

- VBID (CGMS-A) decoding function (CRCC decode) (read by register setting)

- WSS decoding function (read by register setting)

- Macrovision signal detect function

- Power-down function

- 2-channel analog input selector

- I<sup>2</sup>C control compatible

- Core voltage (AVDD, DVDD) 1.65 1.8V

- I/O voltage (PVDD) 1.65 3.3V

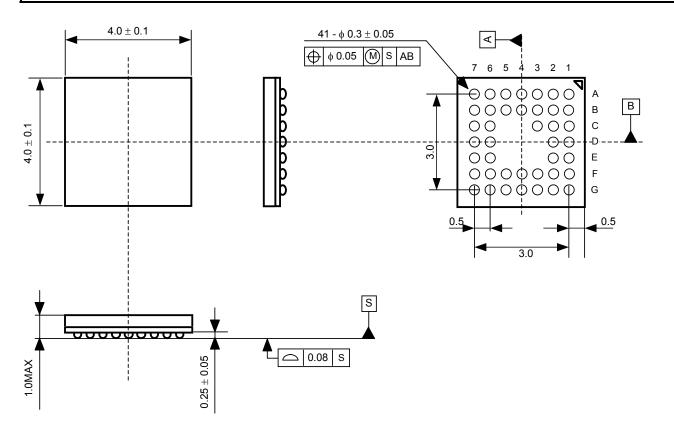

- Package: 41 FBGA 4.0mm x 4.0mm

<sup>\*</sup> The output that meets the ITU-R BT.656 standard according to the fineness of the input signal might not be available.

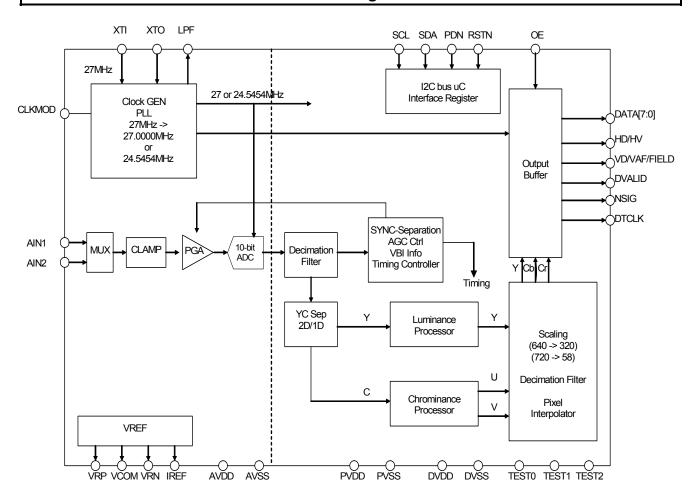

## **Block Diagram**

## **Ordering Guide**

AK8856VG 41-pin FBGA

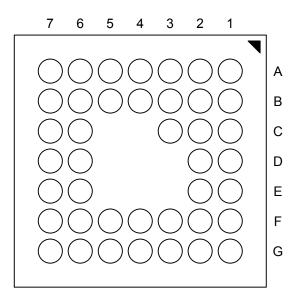

## **Pin Layout Drawing**

**Bottom View**

|   | 1       | 2      | 3     | 4      | 5     | 6     | 7     |

|---|---------|--------|-------|--------|-------|-------|-------|

| Α | NC      | AIN1   | VCOM  | VRP    | VRN   | XTI   | TEST0 |

| В | AVDD    | LPF    | IREF  | CLKMOD | DVSS  | PDN   | XTO   |

| С | AIN2    | AVSS   | NC    |        |       | RSTN  | DVDD  |

| D | DVDD    | DVSS   |       |        |       | SCL   | OE    |

| E | TEST2   | NSIG   |       |        |       | SDA   | PVDD  |

| F | VD/VAF* | DVALID | DATA7 | DATA5  | DATA3 | DATA1 | DTCLK |

| G | NC      | HD/VD  | DATA6 | DATA4  | DATA2 | DATA0 | TEST1 |

<sup>\* &</sup>quot;VD/VAF" is described "VD/VAF/FIELD" in this datasheet.

Top View

# Pin Description

| Pin | Pin<br>Name | A/D/P | I/O | Functional Outline                                                                                                                                                                                                                                                         |

|-----|-------------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A6  | XTI         | D     | ı   | Quartz crystal oscillator connection (tie to digital ground via a 22pF capacitor) - 27.00 MHz crystal oscillator should be used - input from 27.00 MHz crystal oscillator is connected to this pin                                                                         |

| B7  | хто         | D     | 0   | Quartz crystal oscillator connection (tie to digital ground via a 22pF capacitor) - 27.00 MHz crystal oscillator should be used this pin outputs DVSS level when PDN = L when a crystal oscillator is not used, this pin can either be left open (NC) or connected to DVSS |

| B4  | CLKMOD      | D     | I   | Clock mode set: connect to either DVDD (high) or DVSS (low) - Low setting: crystal oscillator is used - High setting: external clock source is used                                                                                                                        |

| D7  | OE          | Р     | ı   | Output enable - L : digital output pins are at high-Z - H : data is available for output - Hi-Z input on OE pin is prohibited                                                                                                                                              |

| E6  | SDA         | Р     | I/O | I <sup>2</sup> C data - this pin is pulled-up to PVDD - Hi-Z input is allowed when PDN is low - SDA input is not accepted during reset operation                                                                                                                           |

| D6  | SCL         | Р     | ı   | I <sup>2</sup> C clock input - an input level below PVDD should be input - Hi-Z input is allowed when PDN is low - SCL input is not accepted during reset operation                                                                                                        |

| C6  | RSTN        | Р     | ı   | Reset signal input - Hi-Z input to this pin is prohibited - L: reset - H: normal operation                                                                                                                                                                                 |

| В6  | PDN         | Р     | ı   | Power-down control - Hi-Z input to this pin is prohibited - L: power-down - H: normal operation                                                                                                                                                                            |

| F7  | DTCLK       | Р     | I/O | Data clock for output interface - output state is separately controlled by combinations of RSTN/PDN/OE pin settings (note 1) - this pin is used as an I/O pin in test mode                                                                                                 |

| F3  | DATA7       | Р     | I/O | Data output (MSB) - output state is controlled by combinations of RSTN/PDN/OE pin settings (note 1) - this pin is used as an I/O pin in test mode                                                                                                                          |

| G3  | DATA6       | Р     | 0   | Data output - output state is controlled by combinations of RSTN/PDN/OE pin settings (note 1)                                                                                                                                                                              |

| F4  | DATA5       | Р     | I/O | Data output - output state is controlled by combinations of RSTN/PDN/OE pin settings (note 1) - this pin is used as an I/O pin in test mode                                                                                                                                |

| G4  | DATA4       | Р     | 0   | Data output pin - output state is controlled by combinations of RSTN/PDN/OE pin settings (note 1)                                                                                                                                                                          |

|       |          |     |     | Data output                                                                                                         |

|-------|----------|-----|-----|---------------------------------------------------------------------------------------------------------------------|

| F5    | DATA3    | Р   | I/O | - output state is controlled by combinations of RSTN/PDN/OE pin settings (note 1)                                   |

|       |          |     |     | - this pin is used as an I/O pin in test mode                                                                       |

| G5    | DATA2    | Р   | 0   | Data output pin                                                                                                     |

|       |          |     |     | - output state is controlled by combinations of RSTN/PDN/OE pin settings (note 1)                                   |

| F6    | DATA1    | Р   | I/O | Data output - output state is controlled by combinations of RSTN/PDN/OE pin settings (note 1)                       |

| 6     | DATAT    | F   | 1/0 | - this pin is used as an I/O pin in test mode                                                                       |

|       |          |     |     | Data output pin ( LSB )                                                                                             |

| G6    | DATA0    | Р   | 0   | - output state is controlled by combinations of RSTN/PDN/OE pin settings (note 1)                                   |

|       |          |     |     | HD/HV timing signal output                                                                                          |

| G2    | HD/HV    | Р   | 0   | - output state is controlled by combinations of RSTN/PDN/OE pin settings (note 1)                                   |

|       |          |     |     | VD/VAF/FIELD timing signal output                                                                                   |

|       |          |     |     | - selection of VD/VAF signal output and FIELD signal output is determined by                                        |

|       | VD/VAF   |     |     | register setting                                                                                                    |

| F1    | /FIELD   | Р   | I/O | - in camera I/F mode, VAF signal is always output                                                                   |

|       |          |     |     | - output state is controlled by combinations of RSTN/PDN/OE pin settings (note 1)                                   |

|       |          |     |     | - this pin is used as an I/O pin in test mode                                                                       |

|       | D) /ALID | -   |     | Valid video interval                                                                                                |

| F2    | DVALID   | Р   | 0   | - output state is controlled by combinations of RSTN/PDN/OE pin settings (note 1)                                   |

|       |          |     |     | Indicates synchronization condition with input signal                                                               |

| E2    | NSIG     | Р   | 0   | - L : synchronized with input signal                                                                                |

| =2    | NSIG     | P   | U   | - H : no signal input or out of synchronization                                                                     |

|       |          |     |     | - output state is controlled by combinations of RSTN/PDN/OE pin settings (note 1                                    |

| E1    | TEST2    | Р   | I/O | Reserved – leave floating                                                                                           |

| A2    | AIN1     | Α   | I   | Analog input pin (1); if not used, leave floating                                                                   |

| C1    | AIN2     | Α   | I   | Analog input pin (2); if not used, leave floating                                                                   |

|       |          |     |     | Reference current setting                                                                                           |

| В3    | IREF     | Α   | I/O | - connect this pin to analog ground through a 6.8kΩ resistor (≤1% accuracy)                                         |

|       |          | , , |     | - this pin goes to high-Z in power-down mode (no high-Z test is performed in                                        |

|       |          |     |     | production test)                                                                                                    |

|       |          |     |     | Internal negative reference voltage for ADC                                                                         |

|       | \        |     | 1/0 | - connect this pin to analog ground through a 0.1uF or larger capacitor                                             |

| A5    | VRN      | Α   | I/O | - this pin may go to high-Z in power-down mode (no high-Z test is performed in                                      |

|       |          |     |     | production test)                                                                                                    |

|       |          |     |     | - do not use this as a reference voltage source for external circuitry  Internal positive reference voltage for ADC |

|       |          |     |     | - connect this pin to analog ground through a 0.1uF or larger capacitor                                             |

| A4    | VRP      | Α   | I/O | - there is a case when this pin becomes Hi-Z output at power-down ( no Hi-Z test is                                 |

| ' ' ' | VIXI     |     | "   | performed in mass-production test )                                                                                 |

|       |          |     |     | - do not use this pin as a reference voltage source for external circuit.                                           |

|       |          |     |     | Internal common voltage for AD converter                                                                            |

|       |          |     |     | - connect this pin to analog ground via a 0.1 uF or larger capacitor.                                               |

| A3    | VCOM     | Α   | I/O | - there is case when this pin becomes Hi-Z output at power-down (no Hi-Z test is                                    |

|       |          |     |     | performed in mass-production test ).                                                                                |

|       |          |     |     | - do not use this pin as a reference voltage source for external circuit.                                           |

| B2    | LPF      | Α   | I/O | I/O for analog test                                                                                                 |

| BZ    | LFI      | Α   | 1/0 | - connect this pin to AVSS for normal operation                                                                     |

| B1    | AVDD     | Α   | Р   | Analog power supply                                                                                                 |

| C2    | AVSS     | Α   | G   | Analog ground                                                                                                       |

| C7,   | DVDD     | D   | Р   | Digital power supply                                                                                                |

| D1    |          |     |     |                                                                                                                     |

| B5,   | DVSS     | D   | G   | Digital ground pins                                                                                                 |

| D2               |       |   |   |                                                                                                                                       |

|------------------|-------|---|---|---------------------------------------------------------------------------------------------------------------------------------------|

| E7               | PVDD  | Р | Р | Power supply for interface - interface power supply for DTCLK, OE, PDN, RSTN, DATA[7:0], HD/HV, VD/VAF/FIELD, NSIG, DVALID, SDA, SCL. |

| A7               | TEST0 | Р | I | Test mode 0 - connect this pin to DVSS (internally pulled-down)                                                                       |

| G7               | TEST1 | Р | I | Test mode 1 - connect this pin to DVSS (internally pulled-down)                                                                       |

| A1,<br>G1,<br>C3 | NC    |   |   | No connection – leave floating - Reserved for AKM testing                                                                             |

A/D/P A: AVDD, D: DVDD, P: PVDD

I/O I: Input pin, O: Output pin, I/O Input/Output pin

Note 1 ) Output pin conditions are determined by setting PDN and OE pins

| OE | PDN | RSTN | Output1*    | Output2*    |

|----|-----|------|-------------|-------------|

| L  | Х   | Х    | Hi-Z output | L output    |

| Н  | L   | Х    | L output    | L output    |

| Ц  | П   | L    | L output    | L output    |

| '' | 11  | Н    | Dataout(*1) | Dataout(*1) |

Output1\*: DATA[7:0], HD/HV, VD/VAF/FIELD, DVALID, DTCLK

Output2\*: NSIG, MACDET

Output pin conditions immediately following power-on are indeterminate, except at OE = "L"

(\*1 ) With no analog input signal, black level data (Y = 0x10, Cb/Cr = 0x80) is output in decoder mode operation

## **Electrical Characteristics**

## (1) Absolute Maximum Ratings

| Parameter                      | Min  | Max        | Units | Note                     |

|--------------------------------|------|------------|-------|--------------------------|

| Supply voltage                 |      |            |       |                          |

| DVDD, AVDD                     | -0.3 | 2.3        | V     |                          |

| PVDD                           | -0.3 | 4.3        | V     |                          |

| Analog input voltage (VinA)    | -0.3 | AVDD + 0.3 | V     |                          |

| Clock input voltage (Vckin)    | -0.3 | DVDD + 0.3 | V     | XTI                      |

| Digital Input voltage 1 (VinD) | -0.3 | DVDD + 0.3 | V     | CLKMOD                   |

| Digital input voltage 2 (VinP) | -0.3 | PVDD + 0.3 | V     | OE,PDN,RSTN,<br>SDA, SCL |

| Input current (lin)            | -10  | 10         | mA    |                          |

| Storage temperature            | -40  | 125        | °C    |                          |

Power supply voltages are values where each ground pin (DVSS = AVSS = PVSS) is at 0V All power supply ground pins (DVSS, AVSS and PVSS) should be at the same potential

When connecting digital output pins (DTCLK,DATA[7:0], HD/HV,VD/VAF/FIELD, NSIG, DVALID) to the data bus, the data bus operating voltage must be within the input pin voltage range as described above

## (2) Recommended Operating Conditions

| Parameter                   | Min  | Тур. | Max | Units | Conditions |

|-----------------------------|------|------|-----|-------|------------|

| Supply voltage * AVDD,DVDD  | 1.65 | 1.8  | 2.0 | V     | AVDD=DVDD  |

| Interface power supply PVDD | 1.65 | 1.8  | 3.3 | V     | PVDD>=DVDD |

| Operating temperature (Ta)  | -30  |      | 85  | °C    |            |

<sup>\*</sup> Power supply voltages are values where each ground pin (PVSS = AVSS = PVSS) is at 0 V (voltage reference )

All power supply ground pins (DVSS, AVSS and PVSS) should be at the same potential

## (3) DC Characteristics

operating voltage: PVDD =DVDD1.65~2.0V, temperature -30~+85°C

| Parameter                      | Symbol | Min     | Тур | Max     | Units | Conditions   |

|--------------------------------|--------|---------|-----|---------|-------|--------------|

| Digital input H voltage (VIH)  | VIH    | 0.8PVDD |     |         | V     |              |

| Digital input1 L voltage (VIL) | VIL    |         |     | 0.2PVDD | V     |              |

| Digital input leak current     | IL     |         |     | ±10     | uA    |              |

| Digital output H voltage (VOH) | VOH    | 0.7PVDD |     |         |       | IOH = -600uA |

| Digital output L voltage (VOL) | VOL    |         |     | 0.3PVDD |       | IOL = 1mA    |

| I2C (SDA) L output             | VOLC   |         |     | 0.3PVDD | V     | IOLC = 3mA   |

Digital output pins refer to DTCLK, DATA[7:0], HD/HV, VD/VAF/FIELD, NSIG, DVALID pin outputs in general terms Digital input pins refer to OE, PDN, RSTN, SCL, SDA pin outputs in general terms

SDA output is not included as a digital output pin unless otherwise noted

## (4) Analog Characteristics (AVDD = 1.8 V, temperature 25°C)

Selector Clamp

| Parameter           | Symbol | Min | Тур  | Max  | Units    | Conditions                 |

|---------------------|--------|-----|------|------|----------|----------------------------|

| Maximum input range | VIMX   | 0   | 0.64 | 0.75 | $V_{PP}$ | PGA_GAIN (minimum setting) |

| Clamp surrent       | CLPI   |     | 120  |      |          | FINE clamp (default)       |

| Clamp current       | UDCLP  |     | 40   |      | uA       | UP/DN clamp (default)      |

## **PGA**

| Parameter    | Symbol | Min | Тур   | Max   | Units | Conditions |

|--------------|--------|-----|-------|-------|-------|------------|

| Resolution   |        |     | 7     |       | bit   |            |

| Minimum gain | GMN    |     | 0     |       | dB    |            |

| Maximum gain | GMX    |     | 12    |       | dB    |            |

| Gain step    | GST    |     | 0.094 | 0.235 | dB    |            |

## A/D Converter

| Parameter                               | Symbol | Min | Тур           | Max | Units | Conditions                               |

|-----------------------------------------|--------|-----|---------------|-----|-------|------------------------------------------|

| Resolution                              | RES    | 10  |               |     | bits  |                                          |

| Operating clock frequency               | FS     |     | 24.5454<br>27 |     | MHz   |                                          |

| Integral non-linearity error            | INL    |     | 2.0           | 4.0 | LSB   | fs=27MHz,<br>PGA_GAIN (default)          |

| Differential non-linearity error        | DNL    |     | 1.0           | 2.0 | LSB   | fs=27MHz,<br>PGA_GAIN (default)          |

| S/N                                     | SN     |     | 50            |     | dB    | fin=1MHz, fs=27MHz<br>PGA_GAIN (default) |

| S/(N+D)                                 | SND    |     | 48            |     | dB    | fin=1MHz, fs=27MHz<br>PGA_GAIN (default) |

| ADC internal common voltage             | VCOM   |     | 0.8           |     | V     |                                          |

| ADC internal positive-side VREF voltage | VRP    |     | 1.0           |     | V     |                                          |

| ADC internal negative-side VREF voltage | VRN    |     | 0.6           |     | V     |                                          |

## **AAF (Anti Aliasing Filter)**

| Parameter            | Symbol | Min | Тур | Max | Units | Conditions |

|----------------------|--------|-----|-----|-----|-------|------------|

| Passband ripple      | Gp     | -1  |     | 1   | dB    | 6MHz       |

| Stopband attenuation | Gs     |     | -24 | -12 | dB    | 27MHz      |

## (5) Current consumption (DVDD = AVDD = PVDD = 1.8V, Ta = -30 ~ +85°C)

| Parameter                                                                                                    | Symb<br>ol | Min | Тур                 | Max | Units                | Conditions                                                   |

|--------------------------------------------------------------------------------------------------------------|------------|-----|---------------------|-----|----------------------|--------------------------------------------------------------|

| Operating power supply current Total current consumption Analog section: Digital section: Interface section: |            |     | 33<br>17<br>12<br>4 | 43  | mA<br>mA<br>mA<br>mA | Note1)  Crystal oscillator connection Load capacitor CL=15pF |

| Power-down current (digital + analog)     Analog section:     Digital section:     Interface section:        |            |     | <=1<br><=1<br><=1   | 20  | uA<br>uA<br>uA<br>uA |                                                              |

Note 1) Input / Output signal: Measured with 100 % Color Bar signal.

Decoder power supply current is measured in 601 output mode (internal clock operation at 27MHz) and 2D YC Separation Mode

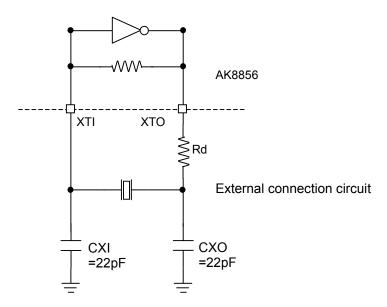

## (6) Quartz Crystal Oscillator circuit

Quartz crystal resonator and externally connecting load capacitance < Ta = -30 ~ +85°C >

| Parameter                                      | Symbol         | Min | Тур    | Max    | Units | Conditions |

|------------------------------------------------|----------------|-----|--------|--------|-------|------------|

| Oscillating frequency                          | f <sub>0</sub> |     | 27.000 |        | MHz   |            |

| Frequency accuracy                             | Delta f / f    |     |        | +/-100 | ppm   |            |

| Load capacitance                               | CL             |     | 15     |        | pF    |            |

| Effective equivalent resistance                | Re             |     |        | 100    | Ω     | note1      |

| Parallel capacitance                           | C0             |     |        | 0.85   | pF    |            |

| XTI pin externally connecting load capacitance | CXI            |     | 22     |        | pF    |            |

| XTO pin externally connecting load capacitance | СХО            |     | 22     |        | pF    |            |

note 1) effective equivalent resistance is generally given as:  $Re = R1 \times (1 + CO / CL)^2$ , where R1 = serial equivalent resistance of crystal oscillator and CO = parallel capacitance of crystal oscillator

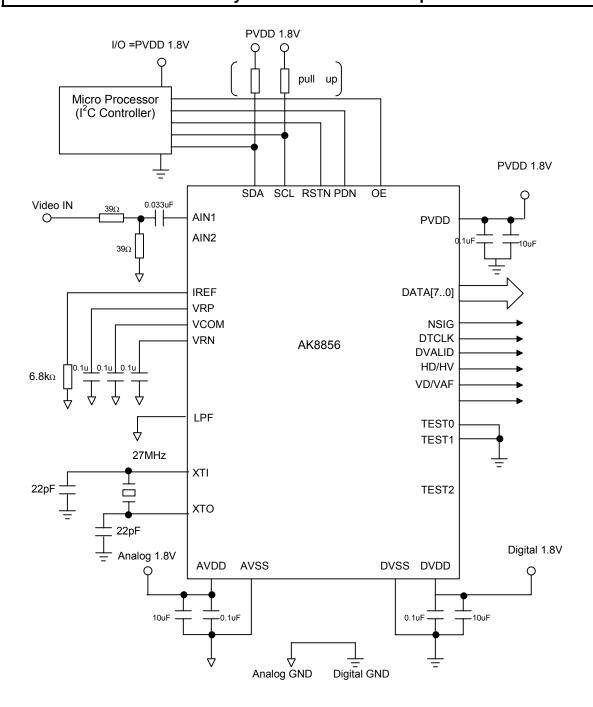

## Circuit connection example

Note) Refer to the quartz crystal oscillator section for the value of the limiting resistor Rd

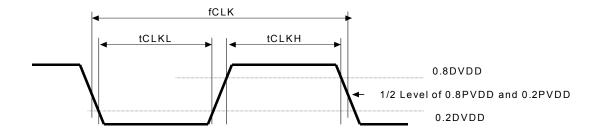

## **AC Timing**

(DVDD = PVDD = 1.65V, Ta at -30  $\sim$  +85 $^{\circ}$ C)

Load condition: CL = 15pF

## (1) CLK

Clock conditions (CLKMOD = 1: external clock mode)

| Parameter           | Symbol | Min | Тур   | Max  | Unit |

|---------------------|--------|-----|-------|------|------|

| CLK                 | fCLK   |     | 27.00 |      | MHz  |

| CLK duty ratio      | pCLKD  | 40  |       | 60   | %    |

| Frequency stability |        |     |       | ±100 | ppm  |

## (2) Clock specification (DTCLK output)

| Parameter | Symbol | Min. | Тур.    | Max | Unit  | Operating mode                   |

|-----------|--------|------|---------|-----|-------|----------------------------------|

|           |        |      | 12.2727 |     |       | QVGA / Rotate QVGA / Rotated CIF |

| DTCLK     | fDTCLK |      | 13.5    |     | MHz   | CIF(PAL), QCIF                   |

| DICLK     | IDTCLK |      | 24.5454 |     | IVITZ | VGA                              |

|           |        |      | 27      |     |       | CIF(NTSC)/601                    |

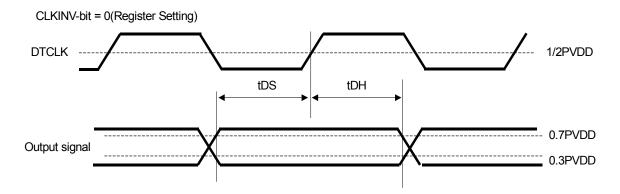

## (3) Output Data Timing

## All output signals except for NSIG and TESTFLG, and MACFLG outputs

| Parameter              | Symbol | Min | Тур | Max | Unit | Conditions |

|------------------------|--------|-----|-----|-----|------|------------|

| Output Data Setup Time | tDS    | 10  |     |     | nsec |            |

| Output Data Hold Time  | tDH    | 10  |     |     | nsec |            |

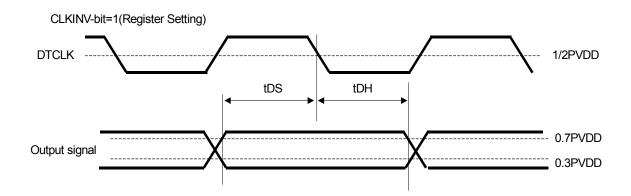

## (4) Reset Timing (Register reset)

| Parameter        | Symbol | Min | Тур | Max | Unit | Conditions        |

|------------------|--------|-----|-----|-----|------|-------------------|

| RSTN pulse width | pRES   | 100 |     |     | CLK  | Rising Clock Edge |

Note) clock input is required for reset. Set RSTN pin low after the clock is present.

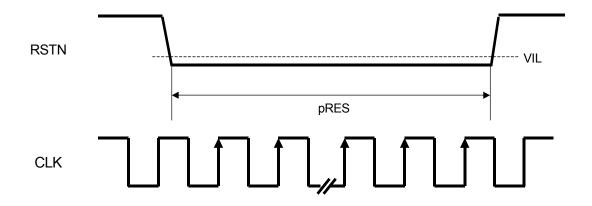

## (5) Power-down sequence and reset sequence after power-down release

Activate reset for longer than 1024 clock cycles before setting PDN (PDN to low) Activate reset after PDN release (PDN to high)

| Parameter                             | Symbol | Min  | Тур | Max | Unit   |

|---------------------------------------|--------|------|-----|-----|--------|

| RSTN pulse width                      | sRES   | 1024 |     |     | SYSCLK |

| Time from PDN to high to RSTN to high | hRES   | 10   |     |     | msec   |

During power-down, all control signals must be connected to either the selected power supply or ground, and <u>not</u> to ViH / ViL levels. When turning off power supplies (AVDD / DVDD) other than PVDD, place the AK8856 into power down mode.

Note ) Clock input is required for reset operation

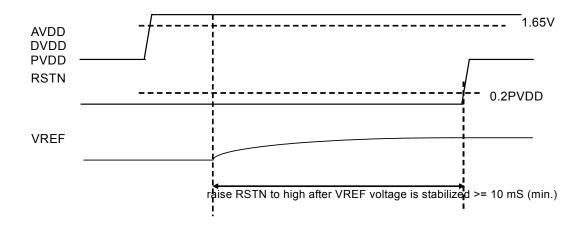

## (6) Power-On-Reset

At power-on, reset must be enabled until the analog reference voltage and current are stabilized.

Power-on operation must be initiated with either simultaneous power-on of PVDD / AVDD / DVDD or PVDD first and then AVDD / DVDD

| Parameter          | Symbol   | Min | Тур | Max | Unit | Conditions |

|--------------------|----------|-----|-----|-----|------|------------|

| RESETN pulse width | pRES_PON | 10  |     |     | msec |            |

Note) clock input is required for reset operation

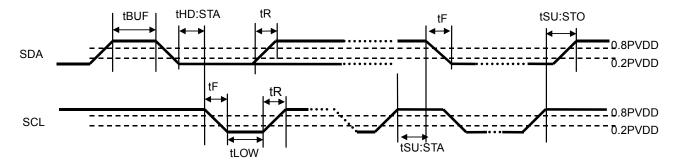

## (7) $I^2C$ bus input / output timing (DVDD = PVDD 1.65 V ~ 2.0V, Ta = -30 ~ +85°C)

## (7-1) Timing 1

| Parameter                    | Symbol  | Min | Max | Unit |

|------------------------------|---------|-----|-----|------|

| Bus free time                | tBUF    | 1.3 |     | usec |

| Hold time (start condition)  | tHD:STA | 0.6 |     | usec |

| Clock pulse low time         | tLOW    | 1.3 |     | usec |

| Input signal rise time       | tR      |     | 300 | nsec |

| Input signal fall time       | tF      |     | 300 | nsec |

| Setup time (start condition) | tSU:STA | 0.6 |     | usec |

| Setup time (stop condition)  | tSU:STO | 0.6 |     | usec |

$l^2C$  bus related timing is established by the  $l^2C$  Bus Specification, and it is not limited by the device performance. For details, please refer to the  $l^2C$  Bus Specification.

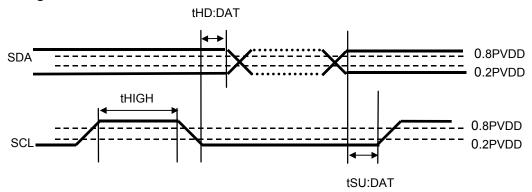

## (7-2) Timing 2

| Parameter             | Symbol  | Min         | Max         | Unit |

|-----------------------|---------|-------------|-------------|------|

| Data Setup Time       | tSU:DAT | 100 (note1) |             | nsec |

| Data Hold Time        | tHD:DAT | 0.0         | 0.9 (note2) | usec |

| Clock Pulse High Time | tHIGH   | 0.6         |             | usec |

note 1) when operating in  $I^2C$  Bus Standard mode,  $tSU:DAT \ge 250$  ns must be met

note 2) when the AK8856 is used in a bus interface where tLOW is not extended (at minimum specification of tLOW), this condition must be met.

## **Functional Outline**

#### (1) Clock

Connect a 27MHz crystal or a 27MHz clock source.

Internal operating clock rates are:

24.5454 MHz for VGA / QVGA / rotated QVGA size / rotated CIF size outputs

27 MHz for 601 pixel mode, CIF / QCIF

24.5454 MHz clock is generated by an internal PLL.

Although the clock is asynchronous with the input signal, vertical position is aligned since the Digital Pixel Interpolator is integrated.

#### (2) Analog Interface

The AK8856 accepts composite video signals.

## (3) Input Signal

NTSC-M, PAL-B, -D, -G, -H, -I compatible composite video signals are accepted as input signals.

#### (4) Analog Input Signal Processing

An anti-aliasing filter is integrated.

PGA 0 dB ~ 12 dB (approximately 0.1 dB / step)

ADC operates at either 24.5454 MHz or 27.00 MHz

#### (5) Clamp Processing

Sync-tip clamping is processed in the analog block and digital pedestal clamping is processed in the digital signal processing block.

#### (6) Adaptive AGC Function

Based on the difference between the sync-tip level and the pedestal level, the input signal value is corrected to a proper level.

A video signal level gain adjust function is applied if only the video signal is larger.

## (7) ACC Function

Based on the color burst level, the input color signal level is corrected to a proper level.

## (8) Y / C Separation Function

Choice of either primary Y / C separation or two dimensional Y / C separation is available.

Mode setting of Y / C separation is done through register settings.

#### (9) Pixel Interpolator

The AK8856 has an integrated Digital Pixel Interpolator to align the output pixels' vertical position. No line-synchronized clock is required.

## (10) Picture Quality Adjustment Function

Adjustments of contrast, brightness, color hue and color saturation levels are available.

#### (11) Output Interface

Outputs are ITU-R BT.601 compatible signal levels (with limit ON / OFF)

Output formats include:

- Camera interface

- ITU-R BT.656-like output\*

- Active video region is indicated by HD / VD (FIELD) / DVALID

- \* With SAV/EAV, 27MHz The number of clocks from EAV to SAV becomes irregular.

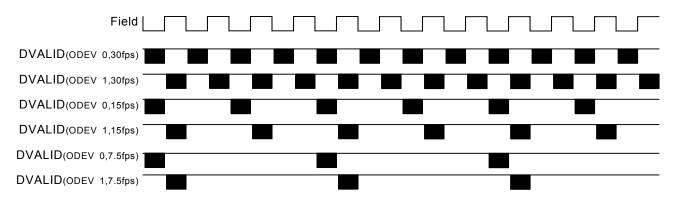

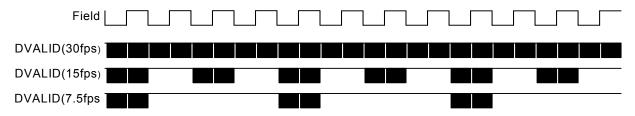

#### (12) Variable Frame-Rate Function

- \* Frame rates of 30 / 15 / 7.5 frames per second are selectable for NTSC video

- \* Frame rates of 25 / 12.5 / 6.75 frames per second are selectable for PAL video

## (13) Output Picture Size

- VGA (640 X 480 - interlaced output)

- QVGA (320 X 240) - CIF (352 X 288) - QCIF (176 X 144)

- 601 (NTSC: 720 X 480 / PAL: 720 X 576 - interlaced output)

- rotated QVGA (240 X 180) - rotated CIF (288 X 216)

## (14) Other Functions

- Black level signal (Y = 16, Cb / Cr = 128) is output in self-operating mode when no input signal is present (Blue back output is also possible)

- No signal input detection function

- I<sup>2</sup>C host interface

- Power-down function

- Decoding function for closed caption, VBID (CGMS-A 525 line), WSS signal (625 line signal). CRCC added to CGMS-A is decoded by the AK8856.

## **Input Signal**

The AK8856 is designed to decode the following video signals:

- NTSC

- PAL-B, -D, -G, -H, -I.

Those input signal types are set by Input Video Standard Register (R/W) [ Sub Address 0x00].

The input signal is converted into digital code as follows:

Then the digitized signal is processed in digital block.

Settings of the Input Video Standard Register ( R/W ) [ Sub Address 0x00 ] is described here. This register sets the input signal attributes.

| <b>Sub Address</b> | 0x00     |          |         |         |       | Default | Value : 0x00 |

|--------------------|----------|----------|---------|---------|-------|---------|--------------|

| bit 7              | bit 6    | bit 5    | bit 4   | bit 3   | bit 2 | bit 1   | bit 0        |

| Reserved           | Reserved | Reserved | AINSEL  | VLF     | VCEN  | VSCF1   | VSCF0        |

|                    |          |          | Default | t Value |       |         |              |

| 0                  | 0        | 0        | 0       | 0       | 0     | 0       | 0            |

## [VSCF1: VSCF0]-bit

The input signal sub-carrier frequency is set by the [VSCF1 : VSCF0] bits.

| [VSCF1:VSCF0]-bit | Sub-carrier frequency (MHz) | Conditions    |

|-------------------|-----------------------------|---------------|

| [00]              | 3.57954545                  | NTSC          |

| [01]              | 3.57561188                  |               |

| [10]              | 3.582054                    |               |

| [11]              | 4.43361875                  | PAL-B,D,G,H,I |

## [VCEN]-bit

The input signal Color Encoding system is set by the [VCEN]-bit.

| [VCEN]-bit | Color Encoding system | Conditions |

|------------|-----------------------|------------|

| 0          | NTSC                  |            |

| 1          | PAL                   |            |

## [VLF]-bit

The number of lines per each Frame of the input signal is set by the IVLF1 bit.

| [VLF]-bit | Number of lines | Conditions |

|-----------|-----------------|------------|

| 0         | 525 lines       |            |

| 1         | 625 lines       |            |

## [AINSEL]-bit

The input signal is selected by the [AINSEL] bit.

| [AINSEL]-bit | Input signal           | Conditions |

|--------------|------------------------|------------|

| 0            | AIN1 input is selected |            |

| 1            | AIN2 input is selected |            |

## PGA (Programmable Gain Amp)

A PGA (Programmable Gain Amp) is integrated into the input stage of the AK8856.

The PGA is adjustable from 0 dB to 12 dB, with gain steps of 0.1 dB / step.

The input signal is attenuated by 50% by a resistor divider.

The PGA setting is determined by PGA Control Register (R/W) [Sub Address 0x05].

By writing a "1" to the **Control 2 Register (R/W) [Sub Address 0x04]** AGC-bit, the AGC function is enabled. Since the setting of the AGC is written by the **PGA Control Register (R/W) [Sub Address 0x05]**, the AGC value can be read through this register (manual setting of the PGA is invalid).

When the AGC function is disabled, manual setting of the PGA gain is allowed.

Bit allocation of **PGA Control Register** is as follows:

## [PGA Control Register]

Sub Address 0x05 Default Value: 0x15

| bit 7    | bit 6         | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|----------|---------------|-------|-------|-------|-------|-------|-------|

| Reserved | PGA6          | PGA5  | PGA4  | PGA3  | PGA2  | PGA1  | PGA0  |

|          | Default Value |       |       |       |       |       |       |

| 0        | 0             | 0     | 1     | 0     | 1     | 0     | 1     |

## AGC

The AK8856 has an adaptive AGC function. When AGC is enabled, the input signal is controlled to an optimized level by the PGA.

When AGC is turned off, manual gain setting of PGA by is allowed.

Enable / disable setting of the AGC is done by Control 2 Register (R/W) [Sub Address 0x04].

#### Sub Address 0x04 Default Value: 0x00

| bit 7  | bit 6         | bit 5 | bit 4  | bit 3  | bit 2  | bit 1 | bit 0 |

|--------|---------------|-------|--------|--------|--------|-------|-------|

| CNTSEL | NSIGDEF       | ODEV  | FRMRT1 | FRMRT0 | COLKIL | ACC   | AGC   |

|        | Default Value |       |        |        |        |       |       |

| 0      | 0             | 0     | 0      | 0      | 0      | 0     | 0     |

#### [AGC]-bit

The [AGC] bit sets the mode of for the AGC.

| The proof six ooks the mode or for the reco. |          |           |  |  |  |  |

|----------------------------------------------|----------|-----------|--|--|--|--|

| [AGC]-bit                                    | Function | Condition |  |  |  |  |

| 0                                            | Disable  |           |  |  |  |  |

| 1                                            | Enable   |           |  |  |  |  |

note ) writing into the PGA register is possible while the AGC is enabled, but the written result is not valid to register. The written result becomes valid to the register when the AGC is disabled.

There are two types of AGC-bits – one is AGCC-bit to set coring level, and the other is AGCTR-bit to control transition speed between Peak AGC and Sync AGC operations.

AGCC [1:0]-bit

| [AGCC]-bit setting | Function               | Note |

|--------------------|------------------------|------|

| 00                 | +/- 2 LSB coring level |      |

| 01                 | +/- 3 LSB coring level |      |

| 10                 | +/- 4 LSB coring level |      |

| 11                 | no coring              |      |

## AGCCTR-bit

| [AGCTR]-bit setting | Function                                           | Note           |

|---------------------|----------------------------------------------------|----------------|

| 0                   | Slow                                               | same as AK8855 |

| 1                   | transition speed from Peak AGC to Sync AGC is fast |                |

The input signal is Analog Sync-Tip clamped. The Sync-Tip clamped input signal is then clamped to the Pedestal level after A/D conversion.

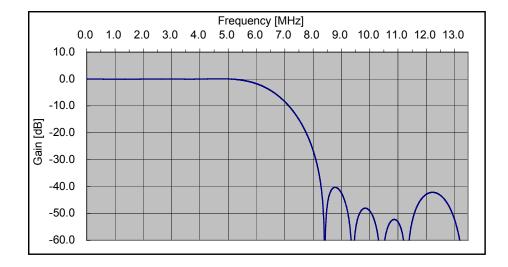

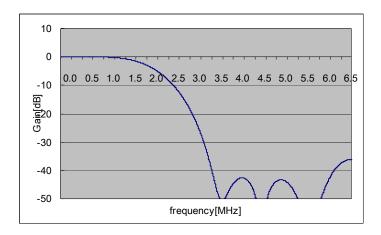

## **Anti-Aliasing Filter**

An Analog Band Limit Filter is integrated before the ADC input in the AK8856. The Anti-Aliasing Filter has following characteristics:

± 1.0dB (~ 6.0MHz) 27MHz -24dB (typ)

## Clock

Sampling is controlled by a fixed clock in the AK8856. A PLL to synchronize the sampling clock with analog input signal is not built-in. The clock rate differs depending on the selected output picture sizes and types of input signal. The internal operating clock is either 27MHz or 24.5454MHz, which is generated from the input clock by the PLL. The internal clock rate is automatically determined by the output picture size.

|      | Operation clock | Size      | Signal   | Note               |

|------|-----------------|-----------|----------|--------------------|

| VGA  | 24.5454MHz      | 640 x 480 | NTSC/PAL | Interlace output   |

| QVGA | 24.5454MHz      | 320 x 240 | NTSC/PAL | Progressive output |

| CIF  | 27MHz           | 352 x 288 | NTSC/PAL |                    |

| QCIF | 27MHz           | 176 x 144 | NTSC/PAL |                    |

| 601  | 27MHz           | 720 x 480 | NTSC     |                    |

|      | 27MHz           | 720 x 576 | PAL      |                    |

| QVGA | 24.5454MHz      | 240 x 180 | NTSC/PAL | Rotated size       |

| CIF  | 24.5454MHz      | 288 x 216 | NTSC/PAL | Rotated size       |

note) For rotated CIF size, both the left-end and right-end 16 pixels are omitted and 288 X 216 picture size is output (90% area of the effective picture is output). When decoding CIF (NTSC), output rate is 2X speed of input HD.

## **Output Picture Size**

The output picture size is set by the [OFORM2 : OFORM0] bits of Output Control 1 Register (R/W) [Sub Address 0x01].

## [OFORM2:OFORM0]-bit

| [OFORM2:OFROM0]-bit | Function     | Condition |

|---------------------|--------------|-----------|

| 000                 | QVGA         |           |

| 001                 | VGA          |           |

| 010                 | CIF          |           |

| 011                 | QCIF         |           |

| 100                 | Rotated QVGA |           |

| 101                 | Rotated CIF  |           |

| 110                 | 601          |           |

## **Decimation Filter**

Typical characteristic of the decimation filter is shown here (27 MHz sampling).

## Sync-Separation, Sync-Detection

Sync-Detection and Separation are executed from the digitized input signal. The recognized Sync-signal is used as reference timing for decoding process.

## **Digital Pedestal Clamp**

The pedestal is clamped in the digital domain. The internal clamp level differs according to the type of input signal (286mV Sync signal or 300 mV Sync signal), but the output is fixes the pedestal position at code 16 (8-bit Rec. 601 level) for either condition.

## **YC Separation**

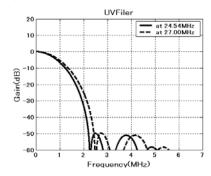

YC separation can be either 1D or 2D. The filter characteristic for YC separation is shown here (27 MHz sampling):

YC separation is set by the YCSEP-bit of the Control 1 Register (R/W) [Sub Address 0x03]

Sub Address 0x03 Default Value: 0x00

|          | ,             |       |       |       |          |          |       |

|----------|---------------|-------|-------|-------|----------|----------|-------|

| bit 7    | bit 6         | bit 5 | bit 4 | bit 3 | bit 2    | bit 1    | bit 0 |

| Reserved | VDFLD         | AGCTR | AGCC1 | AGCC0 | CKILSEL1 | CKILSEL0 | YCSEP |

|          | Default Value |       |       |       |          |          |       |

| 0        | 0             | 0     | 0     | 0     | 0        | 0        | 0     |

YCSEP-bit setting results in the following conditions:

| YCSEP-bit | NTSC                    |                   |                   |  |  |  |  |  |

|-----------|-------------------------|-------------------|-------------------|--|--|--|--|--|

| TCSEF-BIL | QVGA, QCIF, QVGAL, CIFL | CIF               | VGA, 601          |  |  |  |  |  |

|           | Y: 1DYC-filter          |                   | Y: 1DYC-filter    |  |  |  |  |  |

| 0         | C: 1DYC-filter          | Y: 1DYC-filter    | C: 1DYC-filter    |  |  |  |  |  |

|           | AK8855 compatible       | C: 1DYC-filter    | AK8855 compatible |  |  |  |  |  |

| 1         | Y: 1DYC-filter          | AK8855 compatible | Y : 2DYC-filter   |  |  |  |  |  |

| 1         | C: 2DYC-filter          |                   | C: 2DYC-filter    |  |  |  |  |  |

#### **PAL**

DPAL\* switch is turned ON / OFF by the YCSEP-bit (DPAL switch is always OFF in VGA mode (YCSEP-bit has no effect )).

DPAL\*: process of averaging Color phases between Lines.

## **Auto Color Control (ACC)**

This function is used to adjust the Color Burst level of the input signal to a proper level (NTSC: 286mV / PAL: 300mV). The Input Color signal level is determined by the Color Burst signal. ACC gain is 20dB maximum. ACC is turned ON / OFF by setting the ACC-bit of **Control 2 Register (R/W) [Sub Address 0x04]**.

Sub Address 0x04 Default Value: 0x00

| _ |               |         |       |        |        |        |       |       |

|---|---------------|---------|-------|--------|--------|--------|-------|-------|

|   | bit 7         | bit 6   | bit 5 | bit 4  | bit 3  | bit 2  | bit 1 | bit 0 |

|   | CNTSEL        | NSIGDEF | ODEV  | FRMRT1 | FRMRT0 | COLKIL | ACC   | AGC   |

|   | Default Value |         |       |        |        |        |       |       |

|   | 0             | 0       | 0     | 0      | 0      | 0      | 0     | 0     |

## [ACC] bit

The [ACC] bit selects enable / disable of ACC and time constant.

| [ACC]-bit | ACC Setting | Condition |

|-----------|-------------|-----------|

| 0         | Disable     |           |

| 1         | Enable      |           |

The ACC function operates independently from the Color Saturation Adjust function (when ACC is enabled, Color Saturation adjustment is performed on the signal, which is adjusted to a proper level by ACC).

## **Color Killer**

The Chroma Signal Quality is determined by the Color Burst level of the input signal. When the Chroma Signal level is lower than a threshold level, it is regarded as an improper signal, and the input signal is processed as strictly a luminance signal. In this case, Cb / Cr data from the AK8856 is fixed at 0x80 in 601 level.

Color Killer operation is selectable from the following 3 conditions, and it is set by the CKILSEL 1:0 bits:

- (1) When the Color Burst level is lower than approximately 23 dB.

- (2) When the PLL for Color decoding cannot be locked.

- (3) When either condition (1) or (2) is met.

Color Killer is set ON or OFF by the **Control 2 Register (R/W) [Sub Address 0x04].** Color Killer operating conditions are set by the CKILSEL[1:0] bit of the **Control 1 Register (R/W) [Sub Address 0x03].**

Sub Address 0x04 Default Value: 0x00

|               | 20.000.000 |       |        |        |        |       |       |  |

|---------------|------------|-------|--------|--------|--------|-------|-------|--|

| bit 7         | bit 6      | bit 5 | bit 4  | bit 3  | bit 2  | bit 1 | bit 0 |  |

| CNTSEL        | NSIGDEF    | ODEV  | FRMRT1 | FRMRT0 | COLKIL | ACC   | AGC   |  |

| Default Value |            |       |        |        |        |       |       |  |

| 0             | 0          | 0     | 0      | 0      | 0      | 0     | 0     |  |

## [COLKILL]-bit

This bit enables or disables the Color Killer function.

| COLKILL-bit | Color Killer Function | Condition |

|-------------|-----------------------|-----------|

| 0           | Enable                |           |

| 1           | Disable               |           |

Sub Address 0x03 Default Value: 0x00

| bit 7         | bit 6 | bit 5 | bit 4 | bit 3 | bit 2    | bit 1    | bit 0 |  |

|---------------|-------|-------|-------|-------|----------|----------|-------|--|

| Reserved      | VDFLD | AGCTR | AGCC1 | AGCC0 | CKILSEL1 | CKILSEL0 | YCSEP |  |

| Default Value |       |       |       |       |          |          |       |  |

| 0             | 0     | 0     | 0     | 0     | 0        | 0        | 0     |  |

[CKILSEL 1:01-bit

| CKILSEL1:0-bit | Color Killer Operation                                             | Note              |

|----------------|--------------------------------------------------------------------|-------------------|

| 00             | when either Color Burst level is lower than –23 dB or when PLL for |                   |

|                | Color decoding cannot be locked.                                   |                   |

| 01             | when PLL for Color decoding cannot be locked.                      |                   |

| 10             | when Color Burst level is lower than approximately – 23 dB.        | AK8855 compatible |

| 11             | Reserved                                                           |                   |

## **Frame Rate Setting**

The Frame Rate is set by the [FRMRT1: FRMRT0] bits of the Control 2 Register (R/W) [Sub Address 0x04].

| [FRMRT1:FRMRT0]-bit Frame Rate |                   | Condition |

|--------------------------------|-------------------|-----------|

| 00                             | 30/25(525/625)    |           |

| 01                             | 15/12.25(525/625) |           |

| 10                             | 7.5/6.25(525/625) |           |

| 11                             | Reserved          |           |

## **Even / Odd Field Selection**

Even or Odd Field setting is used for QVGA / CIF / QCIF output modes, selected by the [ODEV] bit of the **Control 2 Register (R/W) [Sub Address 0x04]**.

| ODEV-bit |            | Condition |

|----------|------------|-----------|

| 0        | ODD Field  |           |

| 1        | EVEN Field |           |

| LIV Filtor |

|------------|

| OV FIILEI  |

The UV Filter characteristic is shown here:

## **Picture Quality Adjust Process Function**

Picture Quality Adjustments such as contrast, brightness, color saturation and color hue are integrated in the AK8856.

## (1) Contrast

Contrast is adjusted by multiplying the Luminance signal (Y) by a gain value which is set by Contrast Control Register ( R/W ) [ Sub Address 0x06].

CNTSEL bit = 0

YOUT = CONT\* (YIN - 128) + 125 YOUT : contrast arithmetic operation result

: before contrast arithmetic operation CONT : contrast coefficient (register value)

It is also possible to define the equation by setting the register:

CNTSEL bit = 1

$YOUT = CONT^* (YIN - 128) + 16$ YOUT : contrast arithmetic operation result

> : before contrast arithmetic operation YIN CONT : contrast coefficient (register set value)

Setting is done with the [CNTSEL] bit of Control 2 Register (R/W) [Sub Address 0x04]

The range of the contrast gain coefficient varies from 0 to 1.99 (1/128 step), and when the arithmetic operation result exceeds this range, it is clipped to the upper-limit of 254, or the lower-limit of 1 (the output result ranges from 16 to 235 when the 601 limit-bit is 1).

Bit allocation of Contrast Control Register:

## Sub Address 0x06

| Sub Address 0x06 Default Value: 0x |       |       |       |       |       |       |       |

|------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| bit 7                              | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

| CONT7                              | CONT6 | CONT5 | CONT4 | CONT3 | CONT2 | CONT1 | CONT0 |

| Default Value                      |       |       |       |       |       |       |       |

| 1                                  | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Sub Address 0x04 **Default Value: 0x00**

| bit 7         | bit 6   | bit 5 | bit 4  | bit 3  | bit 2  | bit 1 | bit 0 |

|---------------|---------|-------|--------|--------|--------|-------|-------|

| CNTSEL        | NSIGDEF | ODEV  | FRMRT1 | FRMRT0 | COLKIL | ACC   | AGC   |

| Default Value |         |       |        |        |        |       |       |

| 0             | 0       | 0     | 0      | 0      | 0      | 0     | 0     |

#### [CNTSEL] bit

This bit sets the changeover point of the contrast adjustment.

| [CNTSEL]-bit | Function                                          | Condition |

|--------------|---------------------------------------------------|-----------|

| 0            | To be adjusted at Luminance 125 as a center point |           |

| 1            | To be adjusted at Luminance 16 as a center point. |           |

#### (2) Brightness

Brightness is adjusted by adding a value which is set by **Brightness Control Register (R/W) [Sub Address 0x07]** to the luminance (Y) signal.

YOUT = YIN + BR YOUT : brightness arithmetic operation result

YIN : before brightness arithmetic operation BR : brightness coefficient (register value)

Default Value: 0x00

Default Value: 0x80

Default Value: 0x00

The brightness coefficient varies from –127 to +127, and the value is in 2's complement format. When the arithmetic operation result exceeds this range, it is clamped to the upper-limit of 254 or the lower-limit of 1 (output result ranges from 16 to 235 when the 601 limit-bit is 1).

## Bit allocation of Brightness Control Register:

#### Sub Address 0x07

| bit 7 | bit 6         | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |  |  |  |  |

|-------|---------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| BR7   | BR6           | BR5   | BR4   | BR3   | BR2   | BR1   | BR0   |  |  |  |  |

|       | Default Value |       |       |       |       |       |       |  |  |  |  |

| 0     | 0             | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |  |

#### (3) Color Saturation

Color Saturation is adjusted by multiplying the Color Signal (C) by a value which is set by the **Saturation Control Register (R/W) [Sub Address 0x08]**. The arithmetic result is U / V de-modulated. The Saturation coefficient varies from 0 to 255 in 1/128 programmable steps. The default value of the register is a non-adjusted value (0x80).

#### Bit allocation of Saturation Control Register:

## Sub Address 0x08

|               | ONOU  | <u>.</u> |       |       |       |       | Tuluol onco |  |  |  |

|---------------|-------|----------|-------|-------|-------|-------|-------------|--|--|--|

| bit 7         | bit 6 | bit 5    | bit 4 | bit 3 | bit 2 | bit 1 | bit 0       |  |  |  |

| SAT7          | SAT6  | SAT5     | SAT4  | SAT3  | SAT2  | SAT1  | SAT0        |  |  |  |

| Default Value |       |          |       |       |       |       |             |  |  |  |

| 1             | 0     | 0        | 0     | 0     | 0     | 0     | 0           |  |  |  |

## (4) Color Hue

Color Hue can be rotated in the AK8856. The rotation amount of Color Hue is determined by a value which is set by the **HUE Control Register (R/W) [Sub Address 0x09]**. Rotation phase varies from ±45 degrees (0.35 degrees per step). The default value of the register is a non-adjusted value (0x00). The register value is in 2's complement format.

#### Bit allocation of Hue Control Register:

## Sub Address 0x09

| <br><i>.</i>  | . 07.00 | <u>.</u> |       | <u>.</u> | <u>.</u> |       | Tuluol onto |  |  |  |

|---------------|---------|----------|-------|----------|----------|-------|-------------|--|--|--|

| bit 7         | bit 6   | bit 5    | bit 4 | bit 3    | bit 2    | bit 1 | bit 0       |  |  |  |

| HUE7          | HUE6    | HUE5     | HUE4  | HUE3     | HUE2     | HUE1  | HUE0        |  |  |  |

| Default Value |         |          |       |          |          |       |             |  |  |  |

| 0             | 0       | 0        | 0     | 0        | 0        | 0     | 0           |  |  |  |

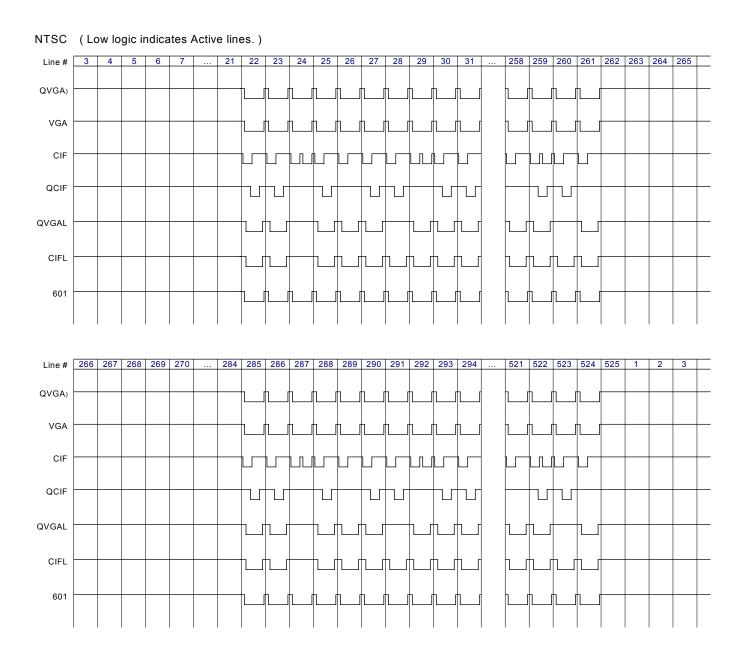

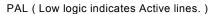

## **Input Video Decoding Period**

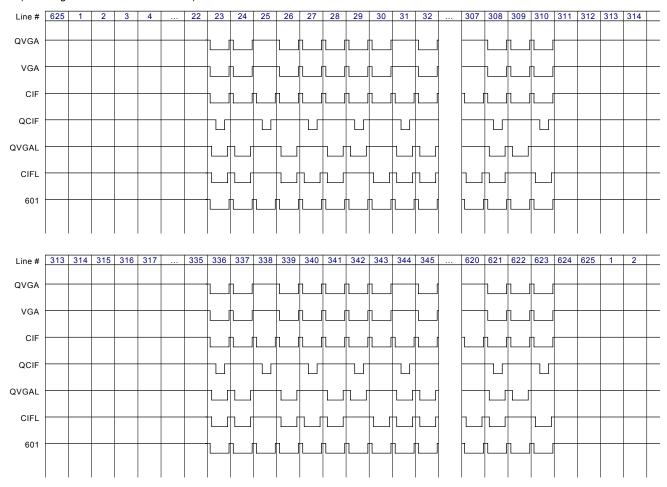

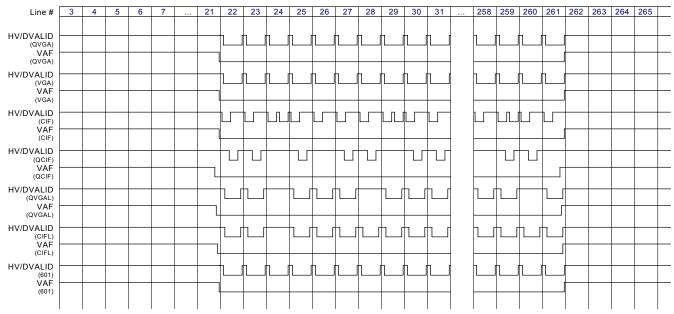

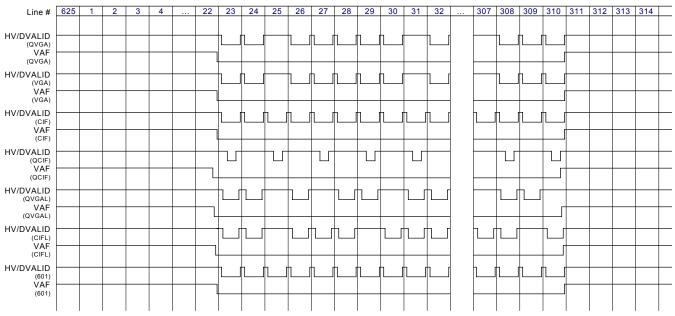

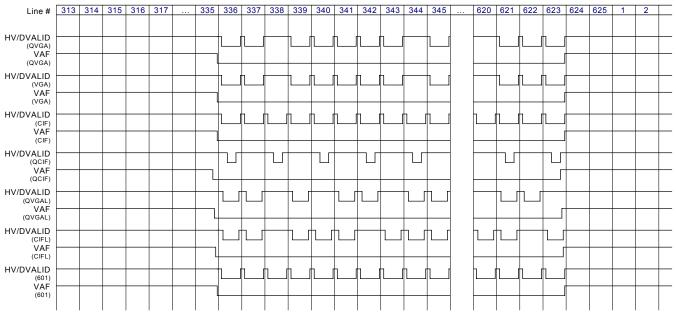

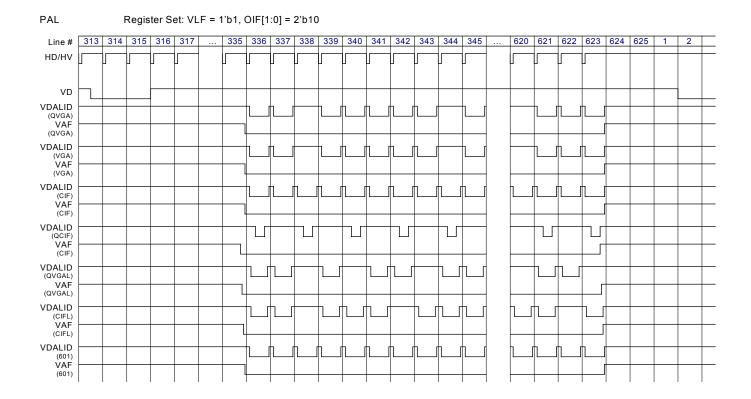

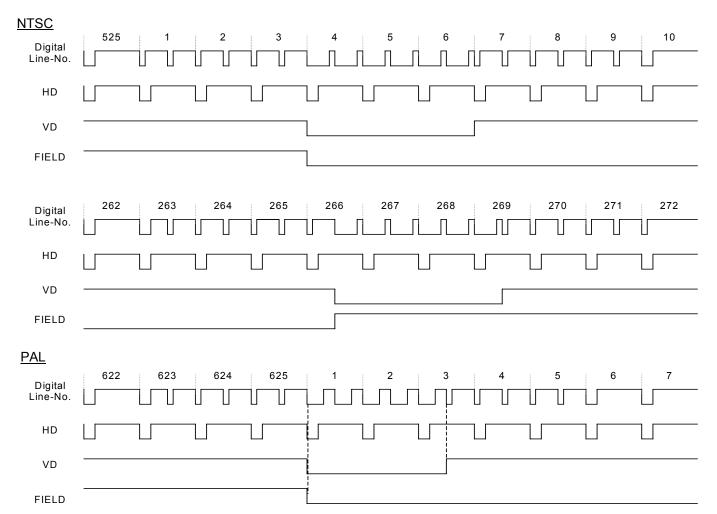

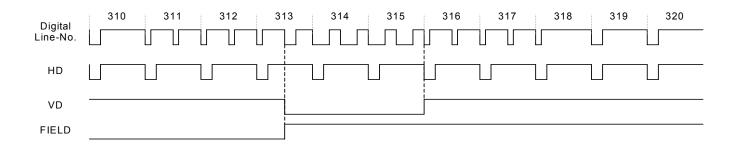

The number of lines used for video decoding varies according to the output mode. Refer to the figure on thr next page which shows "Input Video Signal vs. Output Data relationship".

#### Active Video Period:

525 line system: line 22 ~ line 261 & line 285 ~ line 524 625 line system: line 23 ~ line 310 & line 336 ~ line 623

## Vertical Blanking Period:

525 line system: line 525 ~ line 1 ~ line 21 & line 262 ~ line 284

625 line system: line 624 ~ line 625 – line1 ~ line 22 & line 311 ~ line 335

The default value for the output during the Vertical Blanking period is Black level (Y = 0x10, Cb/Cr = 0x80)

Input Video Signal vs Output Data Relationship (NTSC)

Input Video Signal vs Output Data Relationship (PAL)

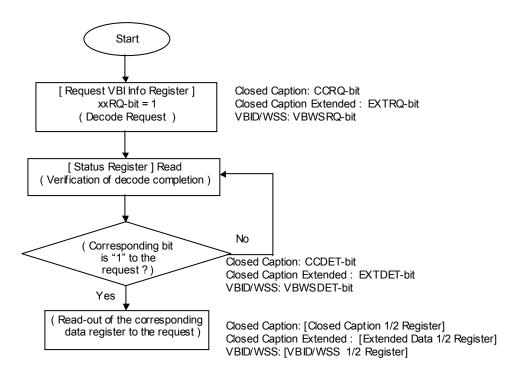

## Closed Caption / Closed Caption Extended Data / VBID (CGMS) / WSS

Closed Caption data, Closed Caption Extended data, VBID (CGMS) and WSS signals that are super-imposed during the VBI interval are decoded in the AK8856. The decoded data is written into a register. When the request bits [bit3: bit 0] of the **Request VBI Info Register (W) [Sub Address 0x0A]** are set, the AK8856 acknowledges that a decode request of the data has been made, and it is placed into a data wait condition. After data is detected and decoded, the host is notified, using [bit7: bit 5] of the **Status Register (R/W) [Sub Address 0x10]** that decoding has been completed.

The results are written into the Closed Caption 1 Register (R) [Sub Address 0x12] / Closed Caption 2 Register (R) [Sub Address 0x13], Extended Data 1 Register (R) [Sub Address 0x14] / Extended Data 2 Register (R) [Sub Address 0x15], VBID / WSS1 Register (R) [Sub Address 0x16] / VBID / WSS2 Register (R) [Sub Address 0x17] respectively.

The data are super-imposed on the respective line:

CRCC code of VBID data (CGMS-A) is decoded and the result is stored in the register.

| Signal                  | Line               | Note     |

|-------------------------|--------------------|----------|

| Closed Caption          | NTSC : Line-21     | 525-Line |

| Closed Caption Extended | NTSC : Line-284    | 525-Line |

| VBID                    | NTSC : Line-20/283 | 525-Line |

| WSS                     | PAL : Line-23      | 625-Line |

## Configuration of Request VBI INFO Register:

#### Sub Address 0x0A

| bit 7    | bit 6         | bit 5    | bit 4    | bit 3    | bit 2  | bit 1 | bit 0 |  |  |  |  |

|----------|---------------|----------|----------|----------|--------|-------|-------|--|--|--|--|

| Reserved | Reserved      | Reserved | Reserved | Reserved | VBWSRQ | EXTRQ | CCRQ  |  |  |  |  |

|          | Default Value |          |          |          |        |       |       |  |  |  |  |

| 0        | 0             | 0        | 0        | 0        | 0      | 0     | 0     |  |  |  |  |

Default Value: 0x00

Configuration of Status Register is as follows

#### Sub Address 0x10

| bit 7    | bit 6  | bit 5 | bit 4  | bit 3    | bit 2   | bit 1    | bit 0 |

|----------|--------|-------|--------|----------|---------|----------|-------|

| VBWSSDET | EXTDET | CCDET | AGCSTS | VLOCKSTS | PKWHITE | COLKILST | NSIG  |

Information read-out flow during VBI interval:

#### Reading Closed Caption data:

Write a "1" to the CCRQ-bit of Request VBI Info Register (W) [Sub Address 0x0A]. When a "1" is written to this bit, the AK8856 is placed in a wait condition for Closed Caption Data decoding. Then when data arrives, it is decoded and a "1" is written back to the CCDET-bit of the Status Register (R / W) [Sub Address 0x10].

After reset, the CCDET-bit is "1" (it goes to "0" when a "1" is written to the CCRQ-bit). The decoded data is written into the Closed Caption 1 Register (R) [Sub Address 0x12] and the Closed Caption 2 Register (R) [Sub Address 0x13]. Data in the Closed Caption 1 Register and Closed Caption 2 Register are retained until they are over-written with new data.

Configuration of Closed Caption 1 Register and Closed Caption 2 Register:

## Closed Caption 1 Register (R) [Sub Address 0x12]

#### Sub Address 0x12

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CC7   | CC6   | CC5   | CC4   | CC3   | CC2   | CC1   | CC0   |

# Closed Caption 2 Register (R) [Sub Address 0x13]

#### Sub Address 0x13

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CC15  | CC14  | CC13  | CC12  | CC11  | CC10  | CC9   | CC8   |

#### Reading out Closed Caption Extended Data:

Write a "1" to the EXTRQ-bit of the **Request VBI Info Register ( W ) [ Sub Address 0x0A ]**. When a "1" is written to this bit, the AK8856 is placed in a wait condition for Extended Data decoding. Then when data arrives, it is decoded and a "1" is written to the EXTDET-bit of the **Status Register (R / W) [ Sub Address 0x10]**.

After reset, the EXTDET-bit is "1" (it goes to "0" when a "1" is written to the EXTRQ-bit). The decoded data is written into the **Extended Data 1 Register (R) [Sub Address 0x14]** and the **Extended Data 2 Register (R) [Sub Address ox15]**. Data in the **Extended Data 1 Register** and **Extended Data 2 Register** are retained until they are over-written with new data.

Configuration of Extended Data 1 Register and Extended Data 2 Register:

# Extended Data 1 Register (R) [Sub Address 0x14] Sub Address 0x14

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EXT7  | EXT6  | EXT5  | EXT4  | EXT3  | EXT2  | EXT1  | EXT0  |

# Extended Data 2 Register (R) [Sub Address 0x15]

## Sub Address 0x15

| <u> </u> | 0 0/(10 |       |       |       |       |       |       |   |

|----------|---------|-------|-------|-------|-------|-------|-------|---|

| bit 7    | bit 6   | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | Ī |

| EXT15    | EXT14   | EXT13 | EXT12 | EXT11 | EXT10 | EXT9  | EXT8  |   |

## Reading out VBID Data:

Write a "1" to the VBWSRQ-bit of the **Request VBI Info Register (W) [Sub Address 0x0A]**. When a "1" is written to this bit, the AK8856 is placed in a wait condition for VBID data decoding. Then when data arrives, it is decoded and a "1" is written to the VBWSDET-bit of the **Status Register (R / W) [Sub Address 0x10 ]**.

After reset, the VBWSDET-bit is a "1" (it goes to "0" when a "1" is written to the VBWSRQ-bit). Decoded data is 13-bits long, and it is written into the VBID / WSS1 Register (R) [Sub Address 0x16] and VBID / WSS 2 Register (R) [Sub Address 0x17]. VBID data is valid only in a 525-line system. These registers are also commonly used for WSS Read-Out register.

CRCC code is decoded and the result is stored in the register. Data in the VBID / WSS 1 Register and VBID / WSS 2 Register are retained until they are over-written with new data.

Configuration of VBID / WSS 1 Register and VBID / WSS 2 Register:

# VBID/WSS 1 Register (R) [Sub Address 0x16] Register to store VBID data Sub Address 0x16

| bit 7    | bit 6    | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|----------|----------|-------|-------|-------|-------|-------|-------|

| Reserved | Reserved | VBID1 | VBID2 | VBID3 | VBID4 | VBID5 | VBID6 |

# VBID/WSS 2 Register (R) [Sub Address 0x17] Register to store VBID data Sub Address 0x17

| bit 7 | bit 6 | bit 5 | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  |

|-------|-------|-------|--------|--------|--------|--------|--------|

| VBID7 | VBID8 | VBID9 | VBID10 | VBID11 | VBID12 | VBID13 | VBID14 |

#### Reading out WSS Data:

Write a "1" to the VBWSRQ-bit of the **Request VBI Info Register (W) [Sub Address 0x0A]**. When a "1" is written to this bit, the AK8856 is placed in a wait condition for VBWS data decoding. Then when data arrives, it is decoded and a "1" is written back to the VBWS-bit of **Status Register (R / W) [Sub Address 0x10]**.

After reset, the VBWS-bit is a "1" (it goes to "0" when a "1" is written to the VBWSRQ-bit). WSS data is valid only for 625-line systems. These registers are also commonly used for VBID Read-Out register. Decoded data are written into the VBID / WSS 1 Register (R) [Sub Address 0x16] and the VBID / WSS 2 Register (R) [Sub Address 0x17]. Data in the VBID / WSS 1 Register and the VBID / WSS 2 Register are retained until they are over-written with new data.

# VBID/WSS 1 Register (R) [Sub Address 0x16] Register for storing WSS data Sub Address 0x16

| bit 7    | bit 6    | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|----------|----------|-------|-------|-------|-------|-------|-------|

| Reserved | Reserved | G4-13 | G4-12 | G4-11 | G3-10 | G3-9  | G3-8  |

# VBID/WSS 2 Register (R) [Sub Address 0x17] Register for storing WSS data Sub Address 0x17

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| G2-7  | G2-6  | G2-5  | G2-4  | G1-3  | G1-2  | G1-1  | G1-0  |

# **Macrovision Decoding**

When a Macrovision Copy Protect signal is present, the AK8856 decodes the additional Macrovision information and stores the result in the **Macrovision Status Register (R/W) [Sub Address 0x11]**.

Configuration of the Macrovision Status Register:

#### Sub Address 0x11

| bit 7    | bit 6  | bit 5   | bit 4  | bit 3   | bit 2  | bit 1 | bit 0  |

|----------|--------|---------|--------|---------|--------|-------|--------|

| Reserved | PSPDET | AGCPDET | BPPDET | SYNCRED | CSTYPE | CSDET | AGCDET |

#### [AGCDET] bit

When Macrovision AGC process is detected, this bit goes to "1".

| [AGCDET]-bit | Status of Macrovision Detection | Condition |

|--------------|---------------------------------|-----------|

| 0            | AGC Process not detected        |           |

| 1            | AGC Process detected            |           |

#### [CSDET] bit

When Macrovision Color Stripe Process is detected, this bit goes to "1".

| [CSDET]-bit | Status of Macrovision Detection   | Condition |

|-------------|-----------------------------------|-----------|

| 0           | Color Stripe Process not detected |           |

| 1           | Color Stripe Process detected     |           |

#### [CSTYPE] bit

When the CSDET-bit is "1", Color Stripe Process type is indicated.

| [CSTYPE]-bit | Status of Macrovision Detection | Condition |

|--------------|---------------------------------|-----------|

| 0            | Color Stripe Type 2 is set      |           |

| 1            | Color Stripe Type 3 is set      |           |

#### [SYNCRED] bit

When the SYNCRED-bit is "1", Sync Reduction has been detected.

| [SYNCRED]-bit | Status of Macrovision Detection | Condition |

|---------------|---------------------------------|-----------|

| 0             | -                               |           |

| 1             | Sync Reduction detected         |           |

### [BPPDET] bit

When the BPPDET-bit is "1", an "End of Field Back Porch Pulse" has been detected.

| [BPPDET]-bit | Status of Macrovision Detection        | Condition |

|--------------|----------------------------------------|-----------|

| 0            | -                                      |           |

| 1            | End of Field Back Porch Pulse detected |           |

#### [AGCPDET] bit

When AGCPDET-bit is "1", an AGC Pulse has been detected.

| [AGCPDET]-bit | Status of Macrovision Detection | Condition |

|---------------|---------------------------------|-----------|

| 0             | -                               |           |

| 1             | AGC Pulse detected              |           |

#### [PSPDET] bit

When PSPDET-bit is "1", a Pseudo Sync Pulse has been detected.

| [PSPDET]-bit | Status of Macrovision Detection | Condition |

|--------------|---------------------------------|-----------|

| 0            | -                               |           |

| 1            | Pseudo Sync Pulse detected.     |           |

# **Decode Data Output (Rec. 601 Limit)**

The AK8856 outputs decoded data at a level (Y / Cb / Cb 4:2:2) specified by ITU-R BT.601. Minimum and maximum output data can be selected by the [LIMIT601] bit of the Output Control 1 Register (R/W) [Sub Address 0x01].

Bit allocation of Output Control 1 Register is as follows.

| Sub Address 0x01 Default Value : 0x |                               |      |      |          |        |        | Value: 0x00 |

|-------------------------------------|-------------------------------|------|------|----------|--------|--------|-------------|

| bit 7                               | bit 7 bit 6 bit 5 bit 4 bit 3 |      |      |          |        | bit 1  | bit 0       |

| VDPSUP                              | TRSVSEL                       | OIF1 | OIF0 | LIMIT601 | OFORM2 | OFORM1 | OFORM0      |

| Default Value                       |                               |      |      |          |        |        |             |

| 0                                   | 0                             | 0    | 0    | 0        | 0      | 0      | 0           |

### [LIMIT601] bit

Maximum and minimum output data is specified by the [LIMIT601]-bit. All internal arithmetic operations are processed at Min. = 1, Max. = 254. Clipping value of the output code differs by the setting of the [LIMIT601] -bit. The default setting value is "0".

| LIMIT601-bit | Condition                        |                   |

|--------------|----------------------------------|-------------------|

| 0            | Y : 1 ~ 254<br>Cb/Cr : 1 ~ 254   | ( Default value ) |

| 1            | Y : 16 ~ 235<br>Cb/Cr : 16 ~ 240 |                   |

### **Output Interface**

The AK8856 supports 3 types of interfaces:

- (1) Camera interface (QVGA / CIF / QCIF)

- (2) Interface by HD / VD / DVALID (VGA / QVGA / CIF / QCIF)

- (3) 656 Interface (601 specification compatible size (720 X 480))

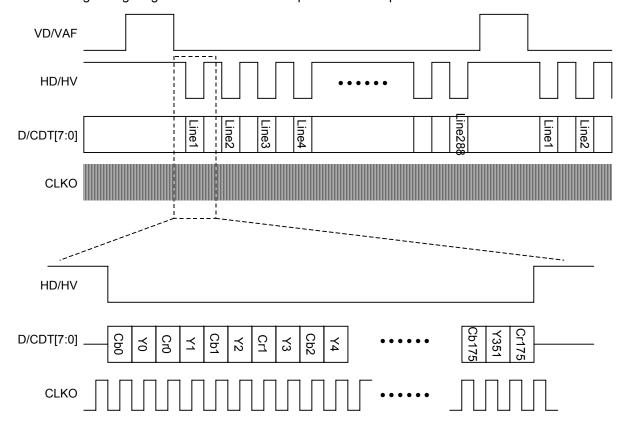

#### (1) Camera Interface

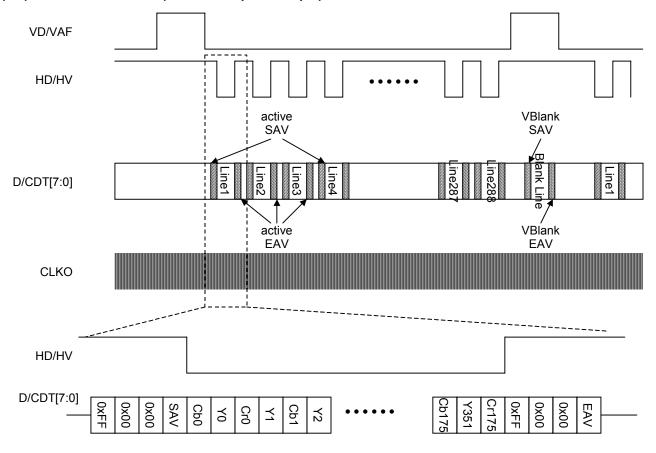

There are two types of data interfaces: "(1-1) HV & VAF Interface Mode" and "(1-2) SAV / EAV Interface Mode".

In this mode, since synchronization shift with the input signal is adjusted at the head part of the line, the interval between lines may fluctuate to some degree. When an exceptional input signal is decoded, there may be cases where the lack of number of lines and lack of number of pixels per line occur, regardless of operation mode. At the default value, an end of frame is set at the rising edge of the VAF signal, and an end of line is set by the HV signal. The polarity of VAF / HV / DVALID / CLKO is programmable through the **Output Control 2 Register** (R/W) [Sub Address (0x02)].

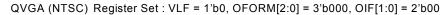

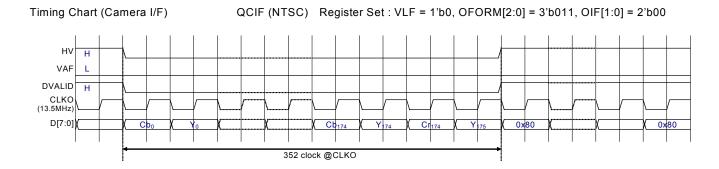

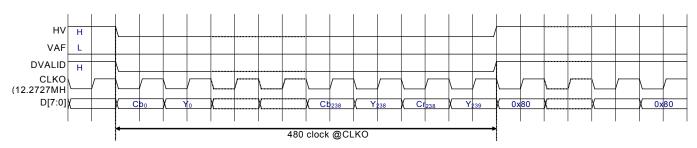

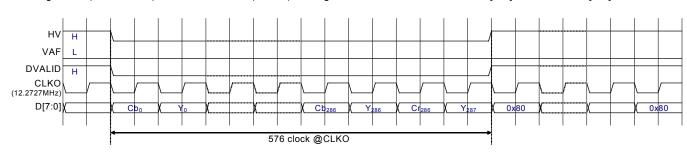

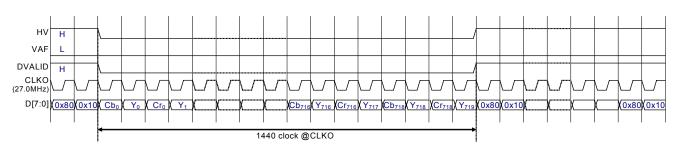

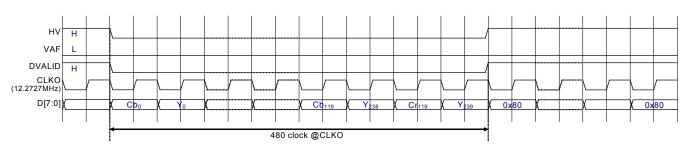

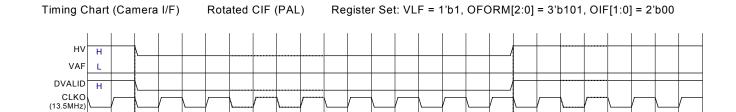

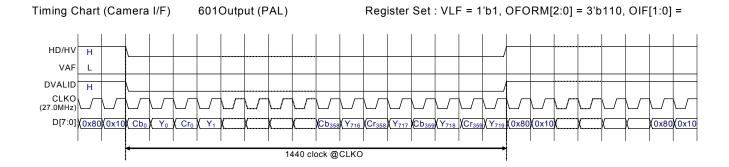

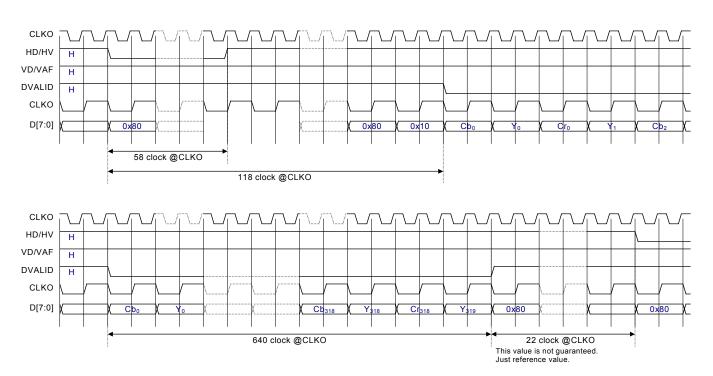

The following timing diagrams show operation examples at HDP = 0, VDP = 0, DVALDP = 0, and CLKINV = 1 settings.

Since the output is progressive in Camera Interface mode, picture sizes in this mode are QVGA / CIF / QCIF / rotated QVGA / rotated CIF.

Definition of SAV / EAV Interface Mode:

|        | SAV  | EAV  |

|--------|------|------|

| Active | 0x80 | 0x9D |

| VBlank | 0xAB | 0xB6 |

In SAV / EAV output mode, HV / VAF signal is not output by default. The register must be set for this mode.

(1-1) HV / VAF Interface

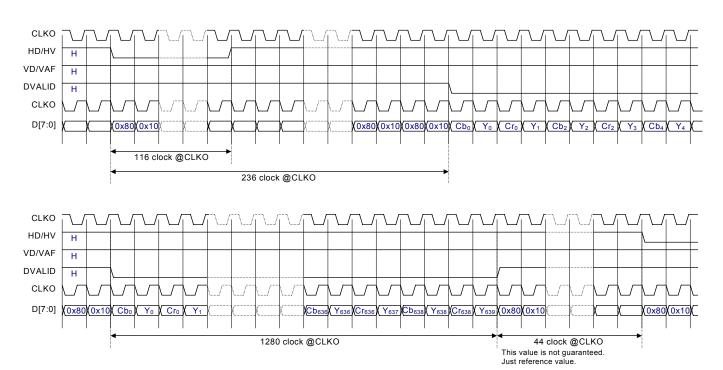

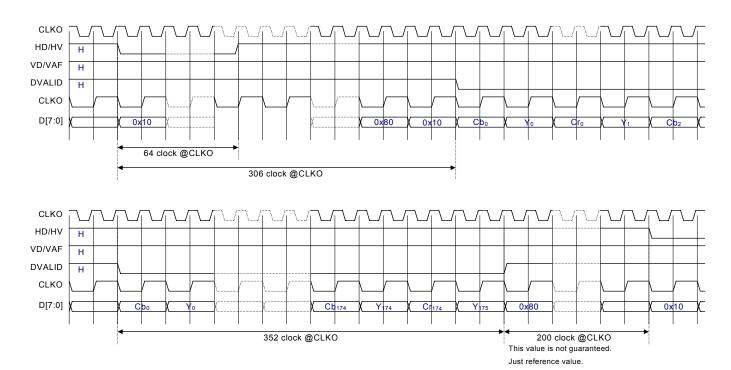

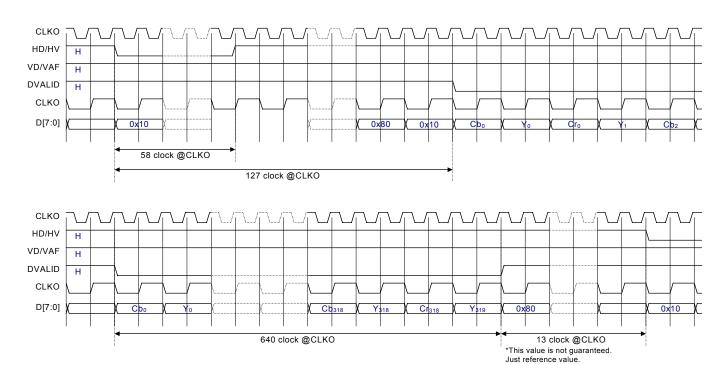

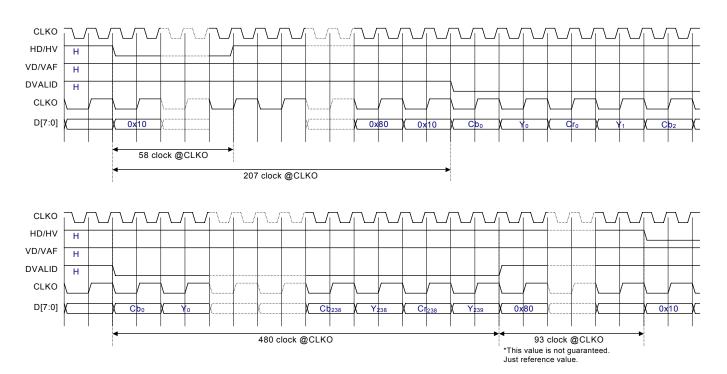

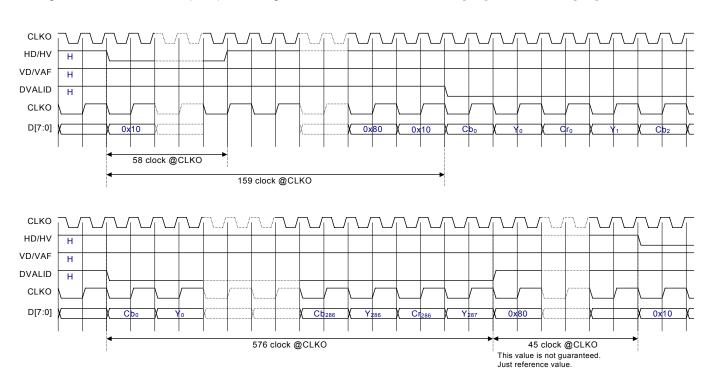

The following timing diagram shows CIF size output as an example.

# (1-2) SAV / EAV Interface (CIF size output example)

Output timing for the Camera Interface mode is illustrated here (the polarity of HV/VAF/DVALID can be changed by register setting).

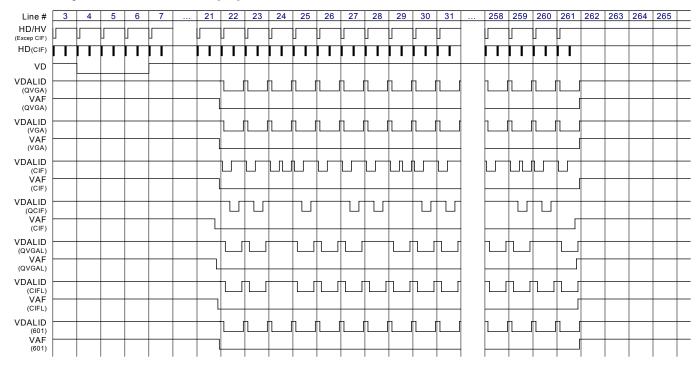

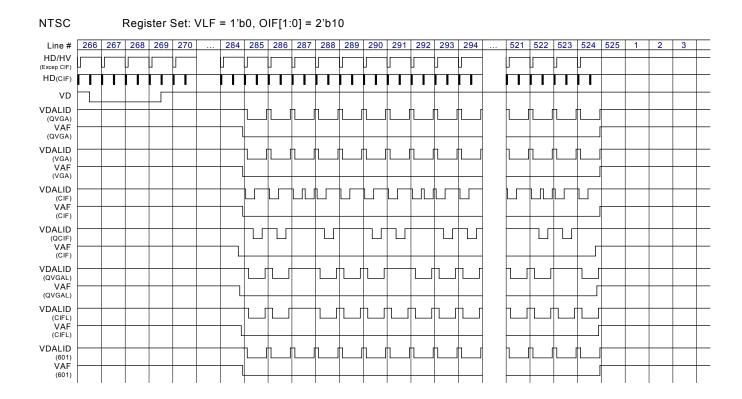

#### NTSC Register Set: VLF = 1'b0, OIF[1:0] = 2'b10

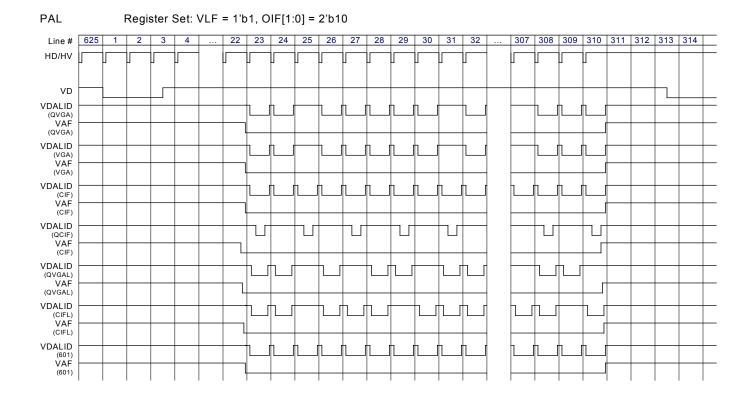

# PAL Register Set : VLF = 1'b1, OIF[1:0] = 2'b10

Note: For output mode modes other than VGA or 601, DVALID signal becomes active (low) for either ODD or EVEN timing QVGAL: Rotated QVGA, CIFL: Rotated CIF

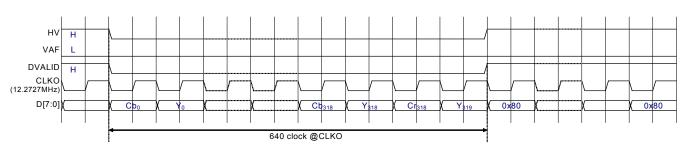

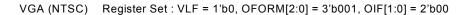

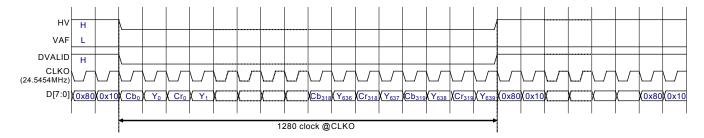

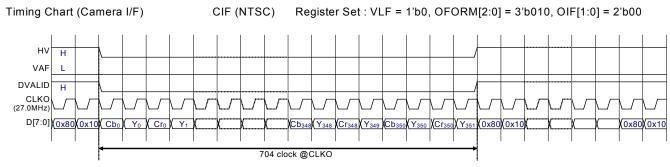

Timing Chart (Camera I/F)

Timing Chart (Camera I/F)

For NTSC, CIF output mode, 2 lines are output while the 1 line input. HD/VD signal are also output doubled rate.

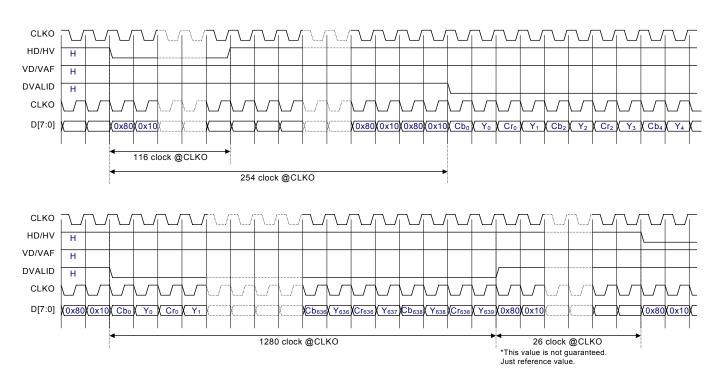

Timing Chart (Camera I/F) Rotated CIF (NTSC) Register Set: VLF = 1'b0, OFORM[2:0] = 3'b101, OIF[1:0] = 2'b00

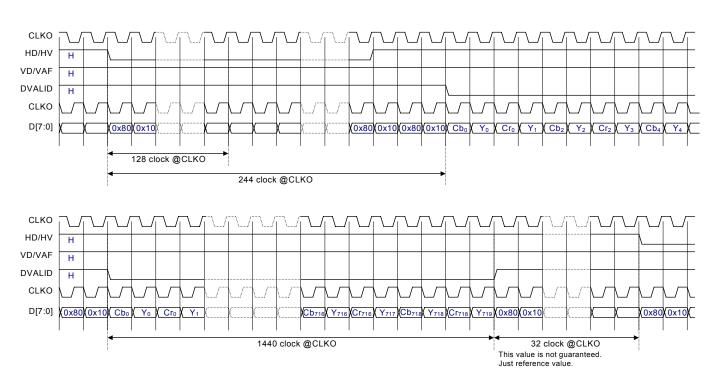

Timing Chart (Camera I/F) 601Output (NTSC) Register Set: VLF = 1'b0, OFORM[2:0] = 3'b110, OIF[1:0] = 2'b00

Timing Chart (Camera I/F) QVGA (PAL) Register Set: VLF = 1'b1, OFORM[2:0] = 3'b000, OIF[1:0] = 2'b00

704 clock @CLKO

Cb<sub>143</sub>

576 clock @CLKO

Cr<sub>143</sub>

Y<sub>287</sub>

0x80

D[7:0]

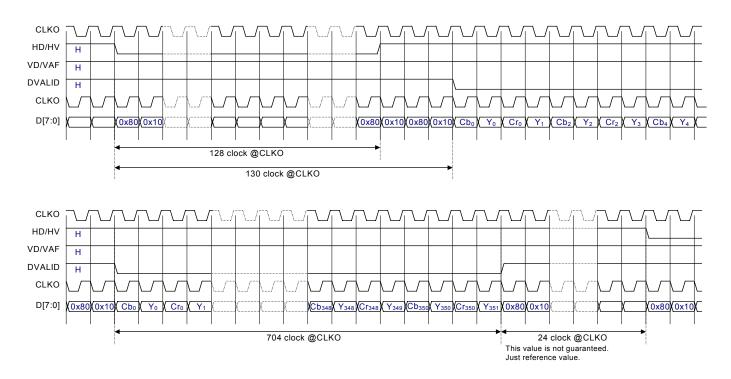

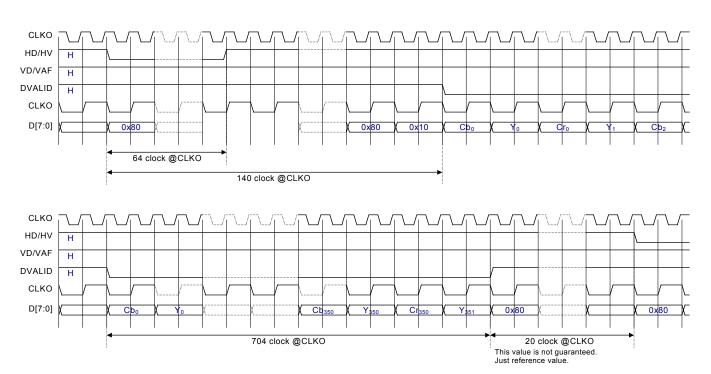

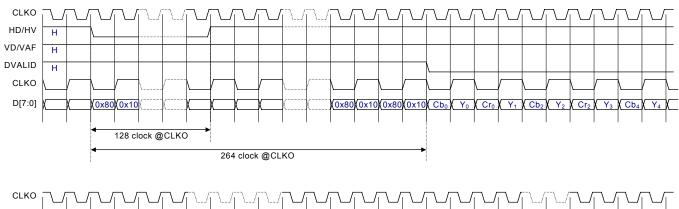

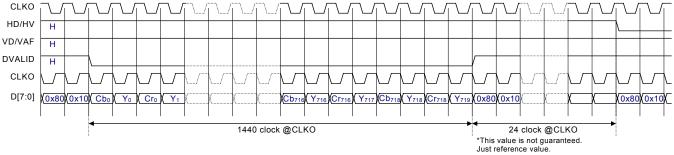

#### (2) Interface by HD / VD / DVALID

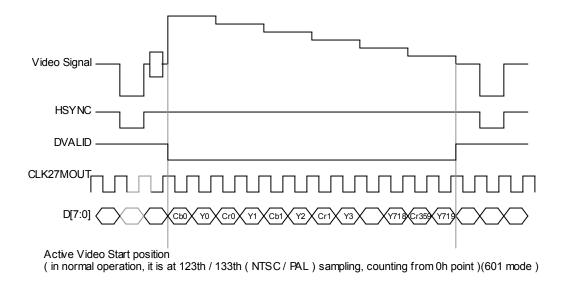

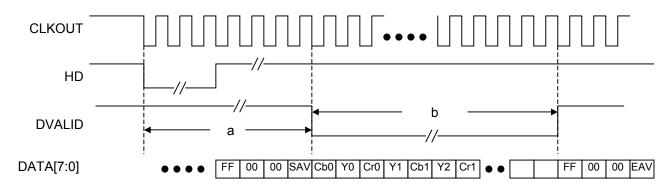

In this interface mode, synchronization is determined by HD and VD. The DVALID signal is active low during the active video space. Since even and odd field recognition can be achieved through HD and VD, interlace information is known. The relationship of the DVALID signal and video data is illustrated here (601 output):

Timing diagram for HD / VD interface mode:

(Data FF0000SAV & FF0000EAV are in Rec.656 mode. For modes other than Rec.656, the data are replaced with 10H80H10H80H data)

| Mode            | [OFORM2:OFROM0] | 525-Line (VLF-bit = 0)  Number of CLKO cycles |      |            | 625-Line (VLF-bit = 1)  Number of CLKO cycles |      |            |

|-----------------|-----------------|-----------------------------------------------|------|------------|-----------------------------------------------|------|------------|

|                 |                 | а                                             | b    | DTCLK Rate | а                                             | b    | DTCLK Rate |

| QVGA            | 000             | 118                                           | 640  | 12.2727MHz | 127                                           | 640  | 12.2727MHz |

| VGA             | 001             | 236                                           | 1280 | 24.5454MHz | 254                                           | 1280 | 24.5454MHz |

| CIF             | 010             | 130                                           | 704  | 27.0MHz    | 140                                           | 704  | 13.5MHz    |

| QCIF            | 011             | 306                                           | 352  | 13.5MHz    | 316                                           | 352  | 13.5MHz    |

| Rotated<br>QVGA | 100             | 198                                           | 480  | 12.2727MHz | 207                                           | 480  | 12.2727MHz |

| Rotated CIF     | 101             | 150                                           | 576  | 12.2727MHz | 159                                           | 576  | 12.2727MHz |

| 601             | 110             | 244                                           | 1440 | 27MHz      | 264                                           | 1440 | 27.0MHz    |

<sup>\*</sup> note: output data rate of CIF size mode in 525 line system (NTSC) is doubled.

The relationship of HD/VD/DVALID is illustrated here. (The polarity of HD/VD/DVALID can be changed by setting the register)

NTSC Register Set: VLF = 1'b0, OIF[1:0] = 2'b10

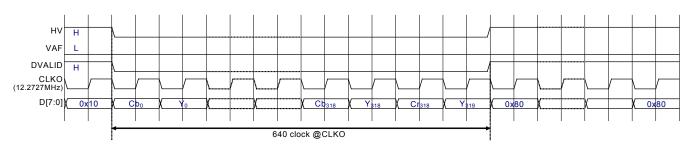

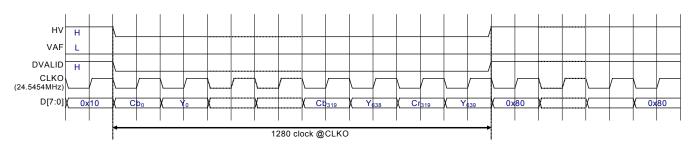

Timing Chart VGA (NTSC) Register set: VLF = 1'b0, OFORM[2:0] = 3'b001, OIF[1:0] = 2'b10

For NTSC and CIF output mode, two lines are output while one line is input. HD/VD signal are also output at a doubled rate.

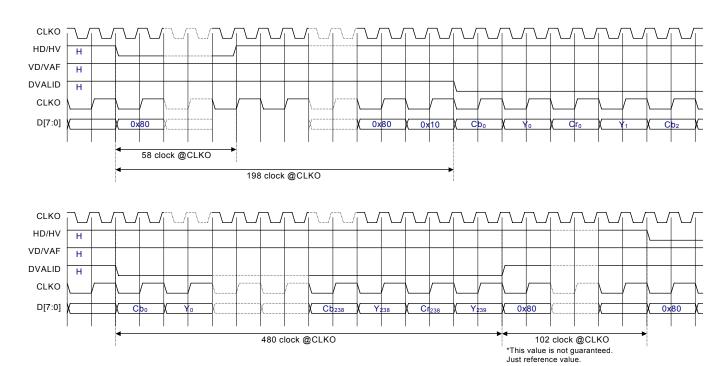

Timing Chart QCIF (NTSC) Register Set: VLF = 1'b0, OFORM[2:0] = 3'b011, OIF[1:0] = 2'b10

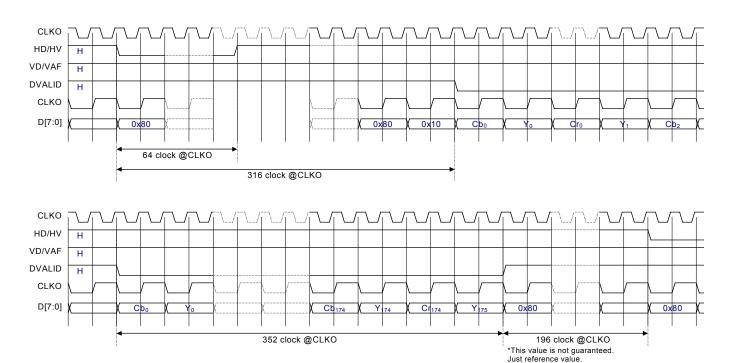

Timing Chart Rotated QVGA (NTSC) Register Set: VLF = 1'b0, OFORM[2:0] = 3'b100, OIF[1:0] = 2'b10

Timing Chart Rotated CIF(NTSC) Register Set: VLF = 1'b0, OFORM[2:0] = 3'b101, OIF[1:0] = 2'b10

Timing Chart QVGA (PAL) Register Set: VLF = 1'b1, OFORM[2:0] = 3'b000, OIF[1:0] = 2'b10

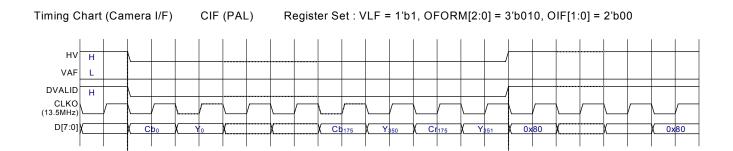

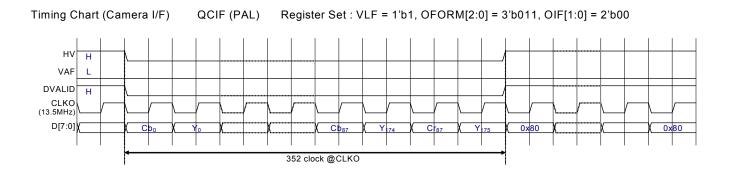

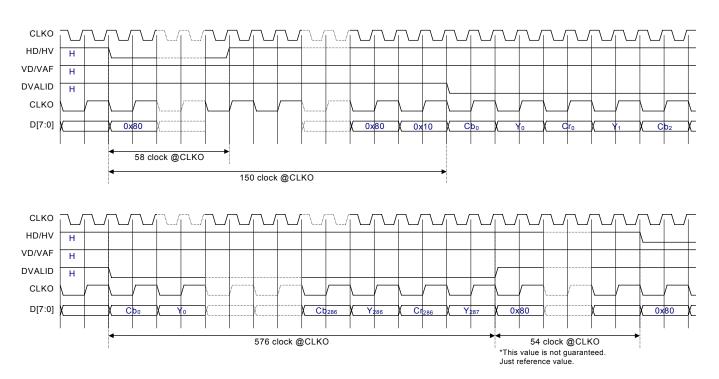

Timing Chart QCIF (PAL) Register Set: VLF = 1'b1, OFORM[2:0] = 3'b011, OIF[1:0] = 2'b10

Timing Chart Rotated QVGA (PAL) Register Set: VLF = 1'b1, OFORM[2:0] = 3'b100, OIF[1:0] = 2'b10

Timing Chart Rotated CIF (PAL) Register Set: VLF = 1'b1, OFORM[2:0] = 3'b101, OIF[1:0] = 2'b10

# Timing Chart 601output (PAL) 2'b10

Register Set: VLF = 1'b1, OFORM[2:0] = 3'b110, OIF[1:0] =

#### (3) 656 Interface

The AK8856 is designed for applications where the video data is typically processed with an MPEG algorithm. As such, it is capable of supporting a specific subset of the BT656 data interface. In 656 mode, the AK8856 generates synchronization codes SAV and EAV to indicate active video data. These codes are interpreted by the external digital video processor. In this mode, HD, DV, and DVALID signals are held low. The HD and DV signals can be read through a register setting.

The relationship between the interface and the output format register is described here. Related registers are [OFORM1 : OFORM0] bits and [OIF2 : OIF0] bits of the **Output Control 1 Register (R/W) [Sub Address 0x01]**.

Interface modes are set, regardless of OFORM register setting.

OIF[0] = 1'b0: without SAV/EAV

1'b1: with SAV/EAV (at OFORM [2:0] = = 3'b 110 ", ITU-R BT.656)

OIF[1] = 1'b0 : Camera I/F

1'b1: HD/VD/DVALID I/F

The Rec.656 mode supported by the AK8855 can be ITU-R BT. 656 compatible by setting OIF with SAV / EAV code (OIF [0] = = 1'b 1) when OFORM [2:0] = = 3' b 110. In all other codes, the V-bit of SAV / EAV becomes "0" during Vertical Active Video region only.