## **Freescale Semiconductor**

## **Advance Information**

Document Number: MKW01Z128

Rev. 0.0, 10/3/12

# MKW01Z128

**Package Information**

#### **Ordering Information**

| Device       | Device Marking | Package |

|--------------|----------------|---------|

| MKW01Z128CHN | MKW01Z128CHN   | LGA-60  |

|              |                |         |

# MKW01Z128

Highly-integrated, cost-effective single-package solution for sub-1 GHz applications

## 1 Introduction

The MKW01Z device is highly-integrated, cost-effective, smart radio, sub-1 GHz wireless node solution composed of a transceiver supporting FSK, GFSK, MSK, or OOK modulations with a low-power ARM® Cortex M0+ CPU. The highly integrated RF transceiver operates over a wide frequency range including 315 MHz, 433 MHz, 470 MHz, 868 MHz, 915 MHz, 928 MHz, and 955 MHz in the license-free Industrial, Scientific and Medical (ISM) frequency bands. This configuration allows users to minimize the use of external components.

The MKW01Z128 is targeted for the following low-power wireless applications:

- Automated Meter Reading

- Wireless Sensor Networks

- Home and Building Automation

- Wireless Alarm and Security Systems

- Industrial Monitoring and Control

Freescale supplements the MKW01Z128 with tools and software that include hardware evaluation and

#### **Contents**

| 1 | Introduction 1                                |

|---|-----------------------------------------------|

| 2 | Features 2                                    |

| 3 | Smart Radio Sub-1 GHz Wireless Node $\ldots5$ |

| 4 | MKW01Z128 Pin Assignments and                 |

|   | Connections                                   |

| 5 | System and Power Management 15                |

| 6 | Development Environment                       |

| 7 | System Electrical Specification 19            |

| 8 | Typical Applications Circuit 63               |

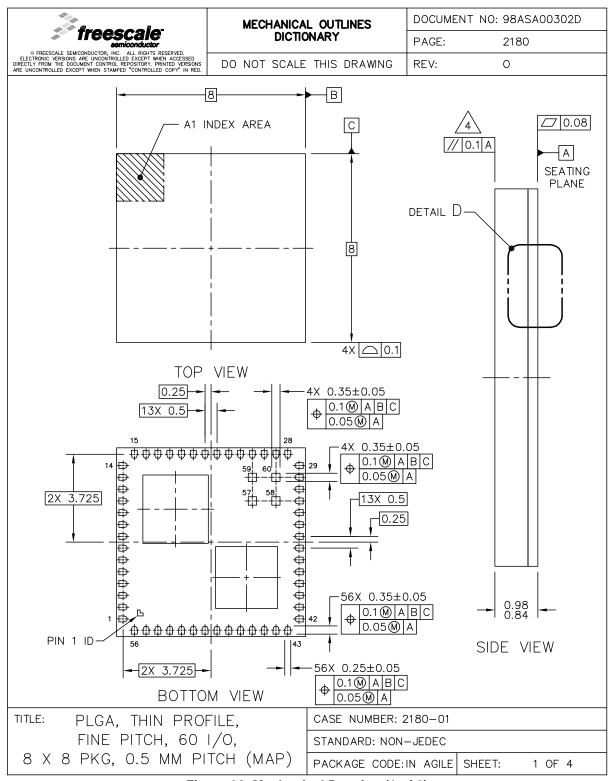

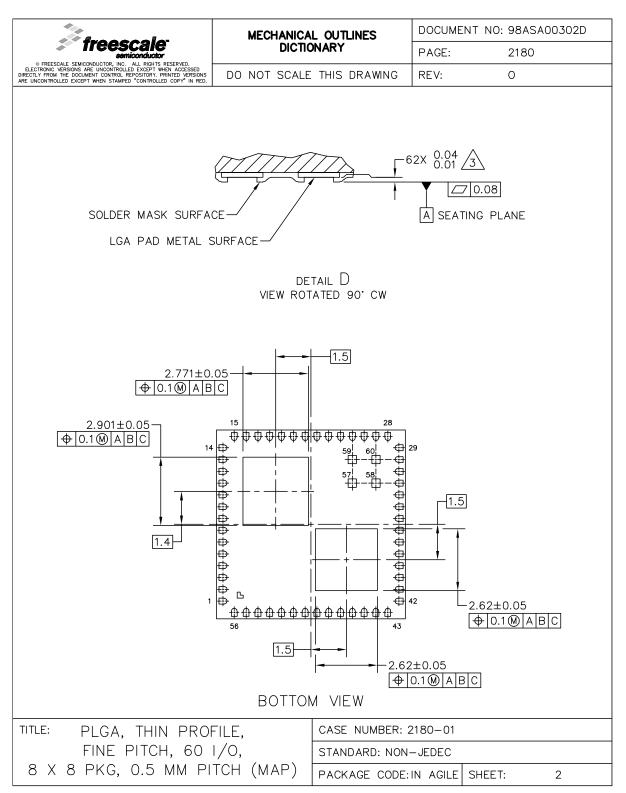

| 9 | Mechanical Drawings 66                        |

|   |                                               |

This document contains information on a product under development. Freescale reserves the right to change or discontinue this product without notice.

development boards, software development IDE and applications, drivers, custom PHY usable with Freescale's IEEE 802.15.4 compatible MAC and SMAC.

## 2 Features

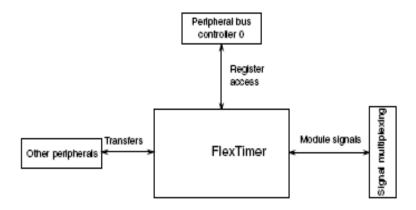

This section provides a simplified block diagram and highlights MKW01Z128 features.

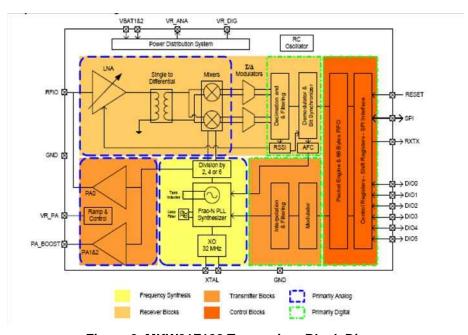

# 2.1 Block Diagram

Figure 1 shows a simplified block diagram of the MKW01Z128.

#### System Sub-1GHz Radio Transceiver Core Memory ARM Cortex M0+ 128KB RF I/O 48MHz 32 MHz **16KB RF Boost** Oscillator Low-RAM Debug Controll Leakage Packet Interfaces 66-byte Wake Engine Up Unit FIFO (AES) Analog Timer **Interfaces** Clock IIC Loop 16-bit ADC 2x 10-ch Timer SPI Frequency-Locked Loop Analog eiodic Interrupt Comparator UART 6-bit DAC Low Power Timer GPIO **Xtrinsic Internal Ref** Touchsensing

### MKW01 Block Diagram

Figure 1. MKW01Z128 Simplified Block Diagram

## 2.2 Features Summary

#### • RF Transceiver Features

- Operating Voltage from 1.8V to 3.6V.

- Programmable bit rate up to 600kbps (FSK)

- High Sensitivity: down to -120 dBm at 1.2 kbps

- High Selectivity: 16-tap FIR Channel Filter

- Bullet-proof front end: IIP3 = -18 dBm, IIP2 = +35 dBm, 80 dB Blocking Immunity, no Image Frequency response

- Low current: Rx = 16mA, 100nA register retention

- Programmable Pout : -18 to +17 dBm in 1 dB steps

- Constant RF performance over voltage range of chip

- Fully integrated synthesizer with a resolution of 61 Hz

- FSK, GFSK, MSK, GMSK and OOK modulations

- Built-in Bit Synchronizer performing Clock recovery

- Incoming Sync Word Recognition

- Automatic RF Sense with ultra-fast AFC

- Packet engine with CRC, AES-128 encryption and 66-byte FIFO

- Built-in temperature sensor and Low battery indicator

- 32 MHz crystal oscillator clock source

- Dedicated I/O's for connection with an external 32 kHz crystal

#### MCU Features

### System:

- 48 MHz Max. Central Processor Unit (CPU) frequency

- 24 MHz Max. Bus frequency

- Vectored Interrupt Controller (NVIC) with 32 vectored interrupts with 4 programmable interrupt priority levels

- Wake-up Interrupt Controller (WIC)

- 4 channel Direct Memory Access (DMA)

- DMA request multiplex

- Non Maskable Interrupt (NMI)

- Software COP

- Low leakage Wake-up Unit (LLWU)

- Debug and Trace

- 2-pin Serial Wire Debug (SWD)

- Basic Branch Buffering (BBB)

- Boundary scan

- 80-bit wide ID number

#### Memory:

- 128 KB P-Flash with 64 byte flash cache

- 16 KB RAM

- Low Leakage Standby Memory:

- 8KB in VLLS2 mode

- 32 Register File Bytes in VLLS1 mode

- Register File and PMC lose control and others in TBD in VLLS0

- 16-bit or 32-bit Cyclic Redundancy Check (CRC) with programmable generator polynominal

#### Clocks:

- External crystal oscillator or resonator:

- 32 40 kHz low range, low power or full swing

- 3 MHz 32 MHz high range, low power or full swing

- DC 48 MHz external square wave input clock

- Internal clock references:

- 31.25 kHz to 39.063 kHz oscillator with +/- 2% max. deviation across temperature

- 4 MHz oscillator with +/- 5% max. deviation across temperature

- 1 kHz oscillator

- Phase Locked Loop (PLL) with up to 100 MHz VCO

- Frequency Locked Loop (FLL):

- Range 1: 20 25 MHz

- Range 2: 40 48 MHz

#### Analog:

- Power Management Controller (PMC) with low voltage warning (LVW) and detect with selectable trip points.

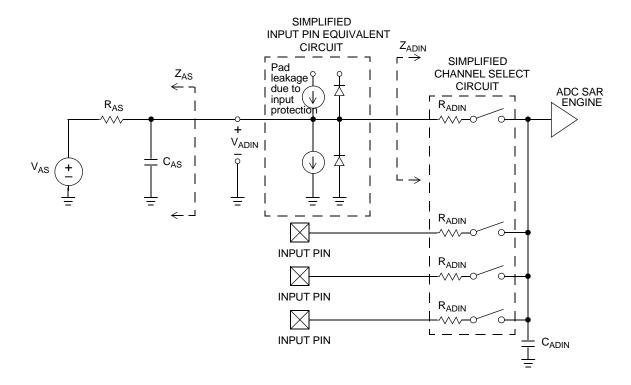

- 16-bit analog to digital converter

- 16 single ended channels

- 2 status, control and results registers

- DMA support

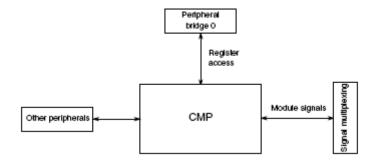

- 1 High Speed Comparator (HSCMP) with internal 6-bit digital to analog converters (DAC)

- One 12-bit DAC with DMA support and 2 x 16 bit data buffer

#### Timers:

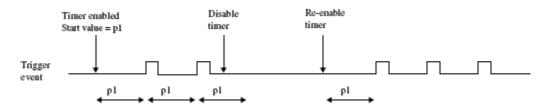

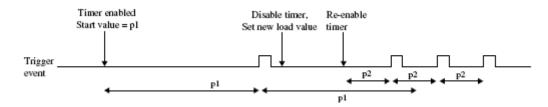

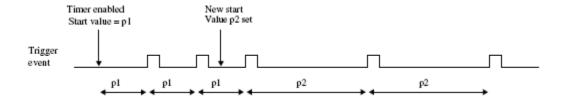

- 6 channel 16-bit flexible timer 0 (FTM0) / (LPTPM0) with basic TPM function and functional in STOP/VLPS modes

- 2 channel 16-bit FTM1 (LPTPM1) with basic TPM function and functional in STOP/VLPS modes.

- 2 channel 16-bit FTM2 (LPTPM2) with basic TPM function and functional in STOP/VLPS modes

- 2 channel 32-bit Programmable Input Timer (PIT)

- 24-bit counter System Tick Timer (SYSTIK)

- Independent Real Time Clock (SRTC) supporting an auxiliary supply, 32 kHz external oscillator and 32 Byte register file

- Low Power Timer (LPTMR) supporting 1 channel 16-bit pulse counter or periodic interrupt functional in all power modes except VLLS0.

#### Communication Interface:

- Two Inter-Integrated Circuits (IIC's) with DMA support

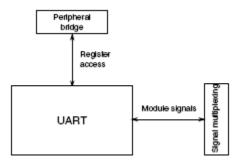

- One Universal Asynchronous Receiver / Transmitter 0 (UART0) / (LPSCIO) that supports standard features plus:

- Tx pin true open drain with enable / disable programmable

- x4, x8, x16 oversampling

- Functional in STOP / VLPS modes

- DMA support

- UART0 is clocked by the bus clock

- UART1 (SCI) that supports standard features with DMA support

- UART1 is clocked by the core clock

#### Human Machine Interface (HMI)

- General Purpose Input/Output (GPIO) supporting:

- 5 V Tolerant I/O

- Default to disabled (no leakage)

- 4 pins with 18 mA high current drive capability

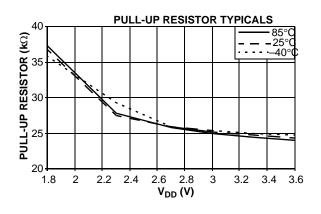

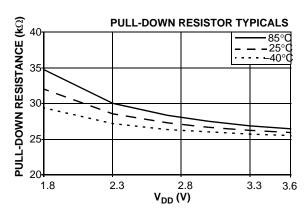

- Hysteresis and configurable pull up device on all input pins

- Slew rate and drive strength fixed on all output pins

- Single cycle GPIO control via IOPORT

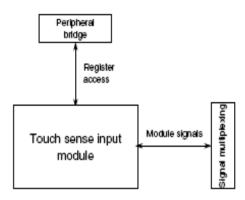

- Touch Sensor Inputs (TSI)

- 16 channel

- Selectable single channel wakeup source available in all modes

- DMA support

- Pin Interrupt

### Freescale will support the MKW01Z128 platform with:

• SMAC (Simple Media Access Contoller) - This codebase provides simple communication and test apps based on drivers/PHY utilities available as source code. This environment is useful for hardware and RF debug, hardware standards certification, and developing proprietary applications.

The Freescale MKW01Z128 solutions are provided through a powerful software environment called the Freescale BeeKit Wireless Connectivity Toolkit. BeeKit is a comprehensive codebase of wireless networking libraries, application templates, and sample applications. The BeeKit Graphical User Interface (GUI), part of the BeeKit Wireless Connectivity Toolkit, allows users to create, modify, and update various wireless networking implementations.

# 3 Smart Radio Sub-1 GHz Wireless Node

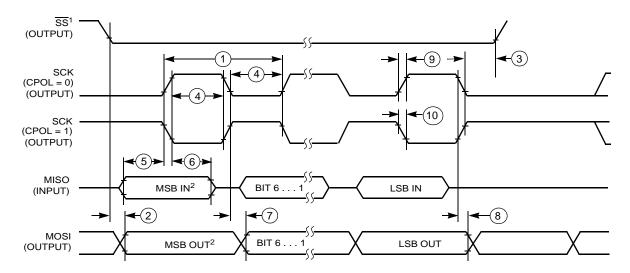

The MKW01Z128 brings together a transceiver chip and an MCU chip on a single substrate to provide a small footprint, cost-effective sub-1 GHz wireless node. The transceiver is controlled by the MCU through

a dedicated SPI interface. The SPI bus interface and some status signals are connected onboard the substrate to eliminate the need for external connections. The SPI supports bit order swapping providing hardware support for bit endianess reducing processing overhead.

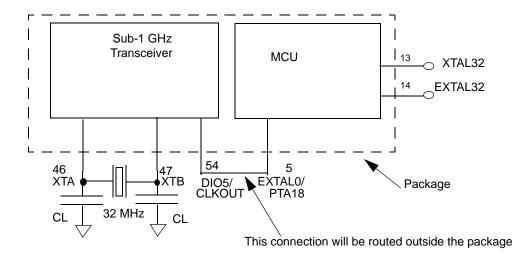

### 3.1 RF Transceiver

The transceiver (see Figure 2) is a single-chip integrated circuit ideally suited for today's high performance ISM band RF applications. Its advanced features set, including state of the art packet engine, greatly simplifies system design while the high level of integration reduces the external RF component bill of material (BOM) to a handful of passive de-coupling and matching components. It is intended for use as a high-performance, low-cost FSK, GFSK, MSK, GMSK, and OOK RF transceiver for robust, frequency agile, half-duplex bi-directional RF links.

The MKW01Z128 is intended for applications over a wide frequency range, including the 433 MHz, the 868 MHz European, and the 902-928 MHz North American ISM bands. Coupled with a link budget in excess of 135 dB, the transceiver advanced system features include a 66 byte TX/RX FIFO, configurable automatic packet handler, listen mode, temperature sensor and configurable DIO's which greatly enhance system flexibility while at the same time significantly reducing MCU requirements. The transceiver complies with both ETSI and FCC regulatory requirements.

Figure 2. MKW01Z128 Transceiver Block Diagram

The major RF communication parameters of the MKW01Z128 transceiver are programmable and most can be dynamically set. This feature offers the unique advantage of programmable narrow-band and wide-band communication modes without the need to modify external components. The transceiver is also optimized for low power consumption while offering high RF output power and channelized operation.

### 3.2 ARM ® 32-bit Cortex M0+ CPU

The onboard MCU integrated circuit features an ARM ® Cortex M0+ CPU, up to 16 KB RAM, 128 KB Flash memory, and a rich set of peripherals (see Section 2.2, "Features Summary"). The RF transceiver is controlled through the MCU SPI port which is dedicated to the RF device interface. Two of the transceiver status IO lines are also directly connected to the MCU GPIO to monitor the transceiver operation. In addition, the transceiver reset and additional status can be connected to the MCU through external connections.

Operational modes of the MKW01Z128 are determined by the software running on the MCU. The MCU itself has a run mode as well as an array of low power modes that are coordinated by the PMC. The MCU in turn set the operational modes of the transceiver which include sleep, standby, and radio operational modes.

Two common application scenarios are:

- Low power, battery-operated standalone wireless node a common example of this configuration would be a remote sensor monitor. The wireless node programmed for standalone operation, typically has a low active-mode duty cycle, and is designed for long battery life, i.e., lowest power.

- Communication channel to a higher level contoller in this example, the wireless node implements the lower levels of a communications stack and is subordinate to the primary controller. Typically the MKW01Z128 is connected to the controller through a command channel implemented via a UART/SCI port or other serial communication port.

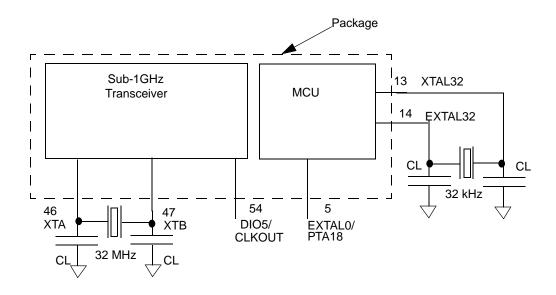

## 3.3 System Clock Configuration

The MKW01Z128 device allows for various system clock configurations:

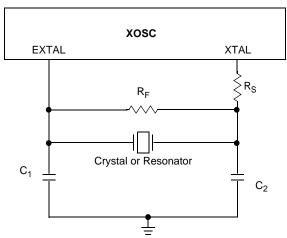

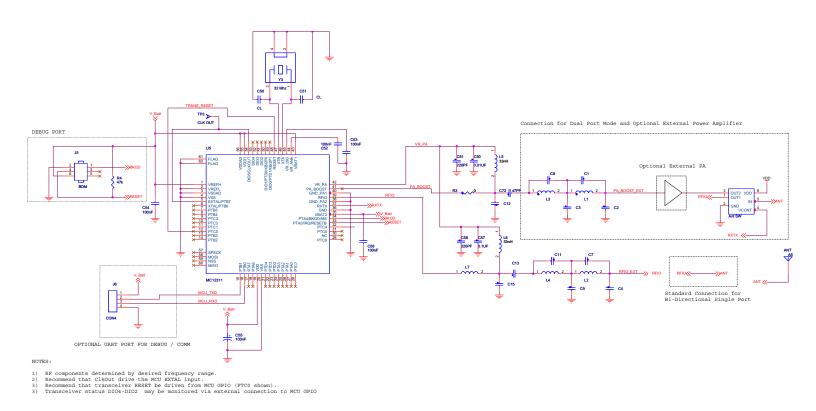

- Pins 46 & 47 are provided to input a 32 MHz crysal for the transceiver reference clock source (required) as shown in Figure 3.

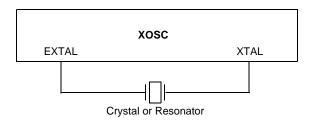

- The transceiver can be programmed to provide programmable frequency clock output (ClkOut Pin #54) that can be used as an external source to the CPU (see Figure 3 and Figure 4). As a result, a single crystal system clock solution is possible where the transceiver reference clock source can be divided by 2, 4, 8, 16 and 32.

- The MCU provides a trimmable internal reference clock and also supports an external clock source. An optional onboard frequency locked loop (FLL) can be used with either clock source to support a CPU clock as high as 48 MHz at 3.6 V.

- Pins 16 and 15 are available to provide an external 32.768kHz external clock source for the radio.

Figure 3. MKW01Z128 Single Crystal System Clock Connection

Figure 4. MKW01Z128 Two Crystal System Clock Connection

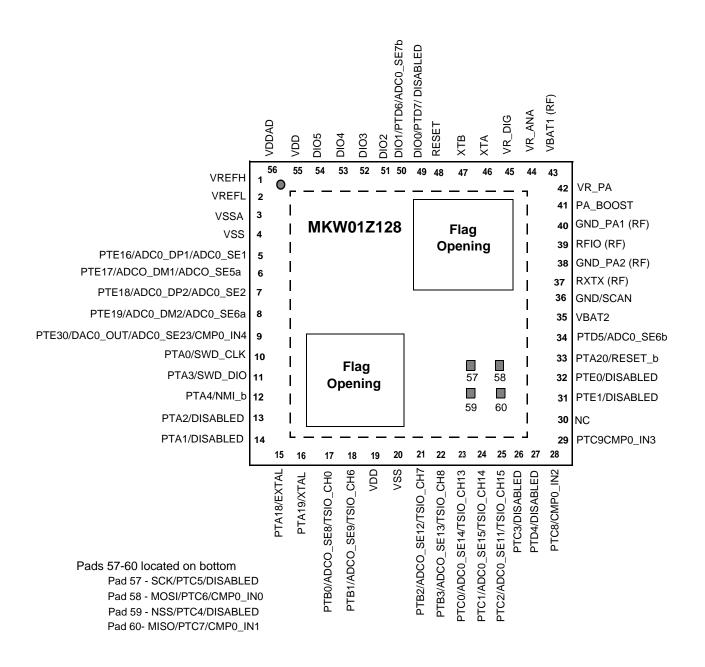

# 4 MKW01Z128 Pin Assignments and Connections

Figure 5 shows the MKW01Z128 pinout.

Figure 5. MKW01Z128 Pinout (Top View)

# 4.1 Pin Definitions

Table 1 details the MKW01Z128 pinout and functionality.

Table 1. Pin Function Description<sup>1</sup>

| Pin# | Pin Name <sup>1</sup>                                             | Туре                      | Description                                                                                                                                                                                 | Functionality     |

|------|-------------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1    | VREFH                                                             | Input                     | MCU high reference voltage for ADC                                                                                                                                                          |                   |

| 2    | VREFL                                                             | Input                     | MCU low reference voltage for ADC                                                                                                                                                           |                   |

| 3    | VSSA                                                              | Power Input               | MCU ADC Ground                                                                                                                                                                              | Connect to ground |

| 4    | VSS                                                               | Power Input               | MCU Ground                                                                                                                                                                                  | Connect to ground |

| 5    | PTE16/ADC0_DP1/ADCO_S<br>E1/SPI0_PCS0/ FTM_CLKIN0                 | Digital Input /<br>Output | MCU Port E Bit 16 / ADC0 Single Ended<br>analog channel input DP1/ ADC0 Single<br>Ended analog channel input SE1 / SPI<br>module 0 PCS0 / Flex Timer module Clock<br>In 0                   |                   |

| 6    | PTE17/ADC0_DM1/ADCO_S<br>E5a/SPI0_SCK/<br>FTM_CLKIN1/LPTMR0_ALT3  | Digital Input /<br>Output | MCU Port E Bit 17 / ADC0 Single Ended analog channel input DM1/ ADC0 Single Ended analog channel input 5a / SPI module 0 SCK / Flex Timer module Clock In 1 / Low Power Timer Module 0 ALT3 |                   |

| 7    | PTE18/ADC0_DP2/ADC0_SE<br>2/SPI0_MOSI/IIC0_SDA/SPI0<br>_MISO      | Digital Input /<br>Output | MCU Port E Bit 18 / ADC0 Single Ended<br>analog channel input DP2/ ADC0 Single<br>Ended analog channel input 2 / SPI module<br>0 MOSI / IIC0 Bus Data / SPI module 0<br>MISO                |                   |

| 8    | PTE19/ADC0_DM2/<br>ADC0_SE6a/SPI0_MISO<br>/IIC0_SCL/ SPI0_MOSI    | Digital Input /<br>Output | MCU Port E Bit 19 / ADC0 Single Ended<br>analog channel input DM2/ ADC0 Single<br>Ended analog channel input 6a / SPI<br>module 0 MISO / IIC0 Bus Clock / SPI<br>module 0 MOSI              |                   |

| 9    | PTE30/DAC0_OUT/<br>ADCO_SE23/<br>CMP0_IN4/FMT0_CH3/FTM_<br>CLKIN1 | Digit-I Input /<br>Output | MCU Port E Bit 30 / DAC0 Output/ ADC0<br>Single Ended analog channel input 23 /<br>Comparator 0 Analog Voltage Input 4/ Flex<br>Timer module 0 Channel 3 / Flex Timer<br>module Clock In 1  |                   |

| 10   | PTA0/SWD_CLK/TSIO_CH1/<br>FMT0_CH5                                | Digital Input /<br>Output | MCU Port A Bit 0 / Serial Wire Data Clock<br>/ Touch Screen Interface Channel 1/Flex<br>Timer module 0 Channel 5                                                                            |                   |

| 11   | PTA3/SWD_DIO/TSIO_CH4/<br>IIC1_SCL/FMT0_CH0                       | Digital Input /<br>Output | MCU Port A Bit 3 / Serial Wire Data DIO /<br>Touch Screen Interface Channel 4 / IIC1<br>Bus Clock /Flex Timer module 0 Channel 0                                                            |                   |

| Pin # | Pin Name <sup>1</sup>                                     | Туре                      | Description                                                                                                                                                                                | Functionality                |

|-------|-----------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 12    | PTA4/NMI_b/TSIO_CH5/<br>IIC1_SDA/FMT0_CH1                 | Digital Input /<br>Output | MCU Port A Bit 4/ / Non Maskable<br>Interrupt_ b/Touch Screen Interface<br>Channel 5 /IIC1 Bus Data/Flex Timer<br>module 0 Channel 1                                                       |                              |

| 13    | PTA2//DISABLED/TSIO_CH3/<br>UARTO_TX/FTM2_CH1             | Digital Input /<br>Output | MCU Port A Bit 2/Touch Screen Interface<br>Channel 3/UART module 0 Transmit/Flex<br>Timer module 2 Channel 1                                                                               |                              |

| 14    | PTA1//DISABLED/TSIO_CH2/<br>UARTO_RX/FTM2_CH0             | Digital Input /<br>Output | MCU Port A Bit 1/Touch Screen Interface<br>Channel 2/UART module 0 Receive/Flex<br>Timer module Channel 0                                                                                  |                              |

| 15    | PTA18/EXTAL/UART1_RX/<br>FTM_CLKIN0                       | Digital Input /<br>Output | MCU Port A Bit 18 / EXTAL/ UART module<br>1 Receive / Flex Timer module Clock In 0                                                                                                         |                              |

| 16    | PTA19/XTAL/UART1_TX/FTM<br>_CLKIN1/LPTMR0_ALT1            | Digital Input /<br>Output | MCU Port A Bit 19 / XTAL/ UART module 1<br>Transmit/ Flex Timer module Clock In 1<br>/Low Power Timer module 0 ALT1                                                                        |                              |

| 17    | PTB0/ADC0_SE8/TSIO_CH0/<br>LLWU_P5/IIC0_SCL/<br>FMT1_CH0  | Digital Input /<br>Output | MCU Port B Bit 0 / ADC0 Single Ended<br>analog channel input SE8 / Touch Screen<br>Interface Channel 0/ Low Leakage Wake<br>Up Port 5 / IIC0 Bus Clock / Flex Timer<br>module 1 Channel 0  |                              |

| 18    | PTB1/ADCO_SE9/TSIO_CH6<br>/LLWU_P5/IICO_SDA/<br>FMT1_CH1  | Digital Input /<br>Output | MCU Port B Bit 1 / ADC0 Single Ended analog channel input SE9/ IIC0 Bus Data/Flex Timer module 1 Channel 1                                                                                 |                              |

| 19    | VDD                                                       | Power Input               | MCU VDD supply input                                                                                                                                                                       | Connect to system VDD supply |

| 20    | VSS                                                       | Power Input               | MCU Ground                                                                                                                                                                                 | Connect to ground            |

| 21    | PTB2/ADC0_SE12/TSIO_CH<br>7/LLWU_P5/IIC0_SCL/<br>FMT2_CH0 | Digital<br>Input/Output   | MCU Port B Bit 2 / ADC0 Single Ended<br>analog channel input SE12 / Touch Screen<br>Interface Channel 7/ Low Leakage Wake<br>Up Port 5 / IIC0 Bus Clock / Flex Timer<br>module 2 Channel 0 |                              |

| 22    | PTB3/ADC0_SE13/TSIO_CH<br>8/LLWU_P5/IIC0_SDA/<br>FMT2_CH1 | Digital<br>Input/Output   | MCU Port B Bit 3 / ADC0 Single Ended<br>analog channel input SE13 / Touch Screen<br>Interface Channel 8 /Low Leakage Wake<br>Up Port 5/ IIC0 Bus Data / Flex Timer<br>module 2 Channel 1   |                              |

| 23    | PTC0/ADC0_SE14/<br>TSIO_CH13/EXTRG_IN/<br>CMP0_OUT        | Digital Input /<br>Output | MCU Port C Bit 0 / ADC0 Single Ended<br>analog channel input SE14/ Touch Screen<br>Interface Channel 13/ ExternalTrigger<br>Input/Comparator 0 Analog Voltage Output                       |                              |

1

| Pin # | Pin Name <sup>1</sup>                                                | Туре                                        | Description                                                                                                                                                                                                                  | Functionality                |

|-------|----------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 24    | PTC1/ADC0_SE15/TSIO_CH<br>14/LLWU_P6/RTC_CLKIN/<br>IIC1_SCL/FMT0_CH0 | Digital Input<br>Output /<br>Analog Input   | MCU Port C Bit 1 /ADC0 Single Ended<br>analog channel input SE15/ Touch Screen<br>Interface Channel 14/ Low Leakage Wake<br>Up Port 6 / Real Time Counter Clock Input/<br>IC1 Bus Clock/ Flex Timer module 0<br>Channel 0    |                              |

| 25    | PTC2/ADC0_SE11/TSIO_CH<br>15/LLWU_P6/RTC_CLKIN/<br>IIC1_SDA/FMT0_CH1 | Digital Input /<br>Output /<br>Analog Input | MCU Port C Bit 2 / ADC0 Single Ended<br>analog channel input SE11// Touch Screen<br>Interface Channel 15 / Low Leakage Wake<br>Up Port 6/ Real Time Counter Clock Input/<br>IIC1 Bus Data / Flex Timer module 0<br>Channel 1 |                              |

| 26    | PTC3/DISABLED/LLWU_P7/<br>UART1_RX/FMT0_CH2<br>/CLKOUTa              | Digital Input /<br>Output                   | MCU Port C Bit 3 / Low Leakage Wake Up<br>Port 7 / UART module 1 Receive / Flex<br>Timer module 0 Channel 2/ Clock OutA                                                                                                      |                              |

| 27    | PTD4/DISABLED/LLWU_P14/<br>SPI1_PCS0/FMT0_CH4                        | Digital Input /<br>Output                   | MCU Port D Bit 4 / Low Leak Wake Up Port<br>14 / SPI module 1 PCS0 / Flex Timer<br>module 0 Channel 4                                                                                                                        |                              |

| 28    | PTC8/CMP0_IN2/IIC0_SCL<br>/FTM0_CH4                                  | Digital Input /<br>Output /<br>Analog Input | MCU Port C Bit 8 / Comparator 0 Analog<br>Voltage Input 2 / IIC1 Bus Clock / Flex<br>Timer module 0 Channel 4                                                                                                                |                              |

| 29    | PTC9/CMP0_IN3/IIC0_SDA<br>/FTM0_CH5                                  | Digital Input /<br>Output /<br>Analog Input | MCU Port C Bit 9 / Comparator 0 Analog<br>Voltage Input 3 / IIC0 Bus Data / Flex Timer<br>module 0 Channel 5.                                                                                                                |                              |

| 30    | NC                                                                   |                                             | No Connect                                                                                                                                                                                                                   |                              |

| 31    | PTE1/DISABLED/SPI1_MOSI<br>/UART1_RX/SPI1_MISO/<br>IIC1_SCL          | Digital<br>Input/Output                     | MCU Port E Bit 1/ SPI module 1<br>MOSI/UART module 1 Receive/SPI<br>module 1 MISO/ IIC1 Bus Clock                                                                                                                            |                              |

| 32    | PTE0/DISABLED/UART1_TX/<br>RTC_CLKOUT/CMP0OUT/<br>IIC1_SDA           | Digital<br>Input/Output                     | MCU Port E Bit 0 / UART module 1<br>Transmit/Real Time Counter Clock<br>Output/Comparator 0 Analog voltage<br>Output/IIC1 Bus Data                                                                                           |                              |

| 33    | PTA20/RESETB                                                         | Digital<br>Input/Output                     | MCU Port a Bit 20/MCU RESET                                                                                                                                                                                                  |                              |

| 34    | PTD5/ADC0_SE6b/<br>SPI1_SCK/ FTM0_CH5                                | Digital<br>Input/Output                     | MCU Port D Bit 5 / ADC0 single ended<br>analog channel input 6b / SPI module 1<br>SCK / Flex Timer module 0 Channel 5                                                                                                        |                              |

| 35    | VBAT2                                                                | Power Input                                 | Transceiver VDD                                                                                                                                                                                                              | Connect to system VDD supply |

| 36    | GND/SCAN                                                             | Power Input                                 | Transceiver Ground                                                                                                                                                                                                           | Connect to ground            |

| 37    | RXTX (RF)                                                            | Digital<br>Output                           | Transceiver Rx / Tx RF Switch Control Output; high when in TX                                                                                                                                                                |                              |

| 38    | GND_PA2 (RF)                                                         | Power Input                                 | Transceiver RF Ground                                                                                                                                                                                                        | Connect to ground            |

| 39    | RFIO (RF)                                                            | RF Input /<br>Output                        | Transceiver RF Input / Output                                                                                                                                                                                                |                              |

MKW01Z128 Product Electrical Specification, Rev. 0.0

| Pin # | Pin Name <sup>1</sup>                                               | Туре                    | Description                                                                                                                                                                      | Functionality                                                                                             |

|-------|---------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 40    | GND_PA1 (RF)                                                        | Power Input             | Transceiver RF Ground                                                                                                                                                            | Connect to ground                                                                                         |

| 41    | PA_BOOST                                                            | RF Output               | Transceiver Optional High-Power PA<br>Output                                                                                                                                     |                                                                                                           |

| 42    | VR_PA                                                               | Power<br>Output         | Transceiver regulated output voltage for VR_PA use.                                                                                                                              | De-coupling cap suggested.                                                                                |

| 43    | VBAT1 (RF)                                                          | Power Input             | Transceiver VDD for RF circuitry                                                                                                                                                 | Connect to system VDD supply                                                                              |

| 44    | VR_ANA                                                              | Power<br>Output         | Transceiver regulated output voltage for analog circuitry.                                                                                                                       | Decouple to ground with 100 nF capacitor                                                                  |

| 45    | VR_DIG                                                              | Power<br>Output         | Transceiver regulated output voltage for digital circuitry.                                                                                                                      | Decouple to ground with 100 nF capacitor                                                                  |

| 46    | XTA                                                                 | Xtal Osc                | Transceiver crystal reference oscillator                                                                                                                                         | Connect to 32 MHz crystal and load capacitor                                                              |

| 47    | ХТВ                                                                 | Xtal Osc                | Transceiver crystal reference oscillator                                                                                                                                         | Connect to 32 MHz crystal and load capacitor                                                              |

| 48    | RESET                                                               | Digital Input           | Transceiver hardware reset input                                                                                                                                                 | Typically driven from MCU GPIO                                                                            |

| 49    | DIO0 / PTD7/<br>DISABLED/SPI1_MISO /<br>UART0_TX/SPI1_MOSI          | Digital<br>Input/Output | Transceiver GPIO Bit 0 / MCU Port D Bit 7 / SPI module 1 MISO/ UART module 0 Transmit/SPI module 1 MOSI                                                                          | MCU IO and Transceiver IO connected onboard                                                               |

| 50    | DIO1/PTD6/ADC0_SE7b/<br>LLWU_P15/SPI1_MOSI/<br>UART0_RX/SPI1_MISO   | Digital<br>Input/Output | Transceiver GPIO Bit 1 / MCU Port D Bit 6 / ADC0 single ended analog channel input 7b / Low leakage Wake Up Port 15/ SPI module 1 MOSI / UART module 0 Receive/SPI module 1 MISO | MCU IO and Transceiver IO connected onboard                                                               |

| 51    | DIO2                                                                | Digital<br>Input/Output | Transceiver GPIO Bit 2                                                                                                                                                           |                                                                                                           |

| 52    | DIO3                                                                | Digital<br>Input/Output | Transceiver GPIO Bit 3                                                                                                                                                           |                                                                                                           |

| 53    | DIO4                                                                | Digital<br>Input/Output | Transceiver GPIO Bit 4                                                                                                                                                           |                                                                                                           |

| 54    | DIO5/CLKOUT                                                         | Digital<br>Input/Output | Transceiver GPIO Bit 5 / ClkOut                                                                                                                                                  | Commonly programmed as ClkOut to supply MCU clock; connect to Pin 5                                       |

| 55    | VDD                                                                 | Power Input             | MCU VDD supply                                                                                                                                                                   | Connect to VDD supply                                                                                     |

| 56    | VDDAD                                                               | Power Input             | MCU Analog supply                                                                                                                                                                | Connect to Analog supply                                                                                  |

| 57    | SCK /<br>PTC5/DISABLED/LLWU_P9/<br>SPI0SCK/LPTMR0_ALT2/<br>CMP0_OUT | Digital<br>Input/Output | SPI Port Clock driven from MCU Port C Bit 5/ MCU Port C Bit 5 / Low Leakage Wake UP Port 9/ SPI module 0 SCK/Low Power Timer module 0 ALT2/ Comparator 0 Analog voltage Output   | MCU IO and<br>Transceiver IO<br>connected onboard     MCU IO must be<br>configured for this<br>connection |

| Pin # | Pin Name <sup>1</sup>                                               | Туре                    | Description                                                                                                                                                                                      | Functionality                                                                                             |

|-------|---------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 58    | MOSI / PTC6 /<br>CMP0_IN0/LLWU_P10/SPI0_<br>MOSI/EXTRG_IN/SPI0_MISO | Digital<br>Input/Output | SPI Port MOSI signal connected to MCU<br>Port C Bit 6 / Comparator 0 Analog voltage<br>Input 0/ Low Leakage Wake Up Port 10/<br>SPI module 0 MOSI/ External Trigger Input<br>/ SPI module 0 MISO | MCU IO and<br>Transceiver IO<br>connected onboard     MCU IO must be<br>configured for this<br>connection |

| 59    | NSS / PTC4/<br>DISABLED/LLWU_P8/<br>SPI0_PCS0/UART1_TX/<br>FTM0_CH3 | Digital<br>Input/Output | SPI Port SS signal connected to MCU Port C Bit 4/Low leakage Wake Up Port 8/ SPI module 0 PCS/UART module 1Transmit/ Flex Timer module 0 Channel 3                                               | MCU IO and<br>Transceiver IO<br>connected onboard     MCU IO must be<br>configured for this<br>connection |

| 60    | MISO / PTC7 /<br>CMP0_IN1/SPI0_MISO/<br>SPI0_MOSI                   | Digital<br>Input/Output | SPI Port MISO signal connected to MCU<br>Port C Bit 7/Comparator 0 Analog voltage<br>Input 1/ SPI module 0 MISO/ SPI module 0<br>MOSI                                                            | MCU IO and<br>Transceiver IO<br>connected onboard     MCU IO must be<br>configured for this<br>connection |

| FLAG  | VSS                                                                 | Power input             | External package flag. Common VSS                                                                                                                                                                | Connect to ground.                                                                                        |

<sup>&</sup>lt;sup>1</sup> Refer to ADD Table 1-3 for additional pin-out information on default and alternate setting selections.

## 4.2 Internal Functional Interconnects

The MCU provides control to the transceiver through the SPI Port and receives status from the transceiver from the DIOx pins. Certain interconnects between the devices are routed onboard the SiP. In addition, the signals are brought out to external pads.

Table 2. MKW01Z128 Internal Functional Interconnects

| Pin # | MCU Signal                   | Transceiver<br>Signal | Description                                                     |

|-------|------------------------------|-----------------------|-----------------------------------------------------------------|

| 49    | PTD7/SPI1_MISO<br>SPI1_MOSI  | DIO0                  | Transceiver DIO0 can be programmed to provide status to the MCU |

| 50    | PTD6/SPI1_MOSI<br>SPI1_MISO  | DIO1                  | Transceiver DIO1 can be programmed to provide status to the MCU |

| 57    | PTC5/SPI0SCK                 | SCK                   | MCU SPI connection must be initiated, not default               |

| 58    | PTC6/SPI0_MOSI/<br>SPI0_MISO | MOSI                  | MCU SPI connection must be initiated, not default               |

| 59    | PTC4/SPI0_PCS0               | NSS                   | MCU SPI connection must be initiated, not default               |

| 60    | PTC7/SPI0_MISO/<br>SPI0_MOSI | MISO                  | MCU SPI connection must be initiated, not default               |

#### NOTE

• As shown in Table 2, the MCU SPI Port pin selection must be configured by software.

• The transceiver DIO pins must be programmed to provide desired status

### 4.3 External Functional Interconnects

In addition to the onboard device interconnection, other external connections between the MCU and the transceiver are common:

- 1. Freescale recommends driving/controlling the transceiver reset from an MCU GPIO This allows over-riding control of the transceiver from the system application.

- 2. The other DIO2-DIO4 status and RXTX signals can prove useful for monitoring the transceiver operation the DIO2-DIO4 signals must be programmed to provide operational status. All signals must be connected externally to appropriate MCU GPIO for this function.

# 5 System and Power Management

The MKW01Z128 consists of an independent transceiver and MCU. The MCU controls the transceiver through programming of the SPI Port, and sets its operational mode through this control channel. Total current draw for the MKW01Z128 is dependent on the operation mode of both devices where different modes allow for different levels of power-down. Some additional features supported are:

- Transceiver Sleep with MCU set at the lowest power state.

- The transceiver mode selection being independent of the MCU's mode selection.

- The transceiver uses/powers-up the tansmitter or receiver only as required.

- MCU peripheral control clock gating being disabled on a module-by-module basis to provide lowest power.

- RTC can be used as wake-up timer.

- LLWU (Low Leakage Wake-up Unit) available.

### 5.1 MCU Power Modes

The MCU has 10 different modes of operation to allow the user to optimize power consumption for the level of functionality needed. Depending on the STOP requirements of the user application, a variety of STOP modes are available that provide state retention, partial power down or full power down of certain logic and/or memory. I/O states are held in all modes of operation. Table 3 outlines the various available power modes of MCU operation.

For each RUN mode there is a corresponding WAIT and STOP mode. WAIT modes are similiar to ARM sleep modes. STOP modes (VLPS, STOP) are similiar to ARM sleep deep mode. The very low power run (VLPR) operating mode can greatly reduce runtime power when the maximum bus frequency is not required to handle application needs. The 3 primary modes of operation are RUN, WAIT and STOP. The WFI instruction invokes both WAIT and STOP modes for the MCU. The primary modes are augmented in a number of ways to provide lower power based on application needs.

Table 3. MCU power modes

| Power Mode                                                         | Description                                                                                                                                                                                                                | Current <sup>1</sup> | Normal Recovery method | Recovery time |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------|---------------|

| Normal RUN (all peripherals, "clock off")                          | Allows maximum performance of chip.                                                                                                                                                                                        | 125uA / MHz          | _                      | _             |

| Normal WAIT-<br>via WFI                                            | Allows peripherals to function while allowing the CPU to go to sleep reducing power.                                                                                                                                       | TBD                  | Interrupt              | 0ns           |

| Normal STOP-<br>via WFI                                            | Places chip in static state. Lowest power mode that retains all registers while amintaining LVD protection                                                                                                                 | 127uA                | Interrupt              | 4.3us         |

| VLPR (Very Low<br>Power RUN) (all<br>peripherals off)              | Reduced frequency (1MHz), Flash access mode, regulator in low power mode, LVD off. Internal oscillator can provide low power 4MHz source for the core. (Values at 2MHz core / 1MHz bus, module off, execution from flash). | 100uA /MHz           | Interrupt              | 4us           |

| VLPW (Very Low<br>Power WAIT)<br>-via WFI (all<br>peripherals off) | Similiar to VLPR, with CPU in sleep to further reduce power. (Values at 2MHz core /1MHz bus, module off).                                                                                                                  | TBD                  | Interrupt              | 4us           |

| VLPS (Very Low<br>Power STOP)<br>-via WFI                          | Places MCU in static state, with LVD operation off, lowest power mode with ADC and all pin interrupt functional. LP timer, RTC CMP can be operational.                                                                     | 5.76uA               | Interrupt              | 4.3us         |

| LLS (Low<br>Leakage STOP)                                          | State retention power mode, LLWU,<br>LPTimer, RTC, LCD,CMP can be operational                                                                                                                                              | 4.14uA               | Wakeup Interrupt       | 4.6us         |

| VLLS3 (Very<br>Low Leakage<br>STOP3)                               | Full SRAM retention. LLWU, LPTimer, RTC, LCD,CMP can be operational.                                                                                                                                                       | 1.36uA               | Wakeup Reset           | 53us          |

| VLLS1 (Very<br>Low Leakage<br>STOP1) with<br>LPTimer + LPO         | All SRAM powered off. LLWU, LPTimer, RTC, CMP can be operational.                                                                                                                                                          | 521nA                | Wakeup Reset           | 115us         |

| VLLS0 (Very<br>Low Leakage<br>STOP0)                               | Disable all analog modules in PMC and retains I/O state and DGO state. LPO shut down, optional POR brown-out detection, Pin interrupt only.                                                                                | 61nA                 | Wakeup Reset           | 115us         |

<sup>&</sup>lt;sup>1</sup> Typical conditions

### 5.1.1 Power mode transitions

Figure 6 shows power mode transitions. Any reset always brings the MCU back to normal state run. In RUN, WAIT and STOP modes active power regulation is enabled. The VLPx modes are limited in frequency but offer a lower power operating power mode than normal modes. The LLS and VLLSx modes are the lowest power stop modes based on the amount of logic or memory that is required to be reatined by the application.

Figure 6. Power mode state transition diagram

## 5.2 Transceiver modes of operation.

The transceiver can be set in numerous modes of operation as described in Table 4. By default, when switching from one mode to another various features are selectively turned on coordinated by a pre-defined optimized sequence using the automatic sequencer. Alternatively, these operating modes can be selected directly by disabling the automatic sequencer.

**Selected Mode Enabled blocks** Sleep None Stand-by Main regulator and crystal osillator Idle Main regulator and RC osillator FS Frequency synthesizer **Transmit** Frequency synthesizer and transmitter Receive Frequency synthesizer and receiver Listen Periodical receive wake-up from Idle operation

**Table 4. Basic Transceiver modes**

An overview of the transceiver modes of operation is described below:

- Sleep provides lowest power consumption and is the full power down state.

- Idle provides very low standby power consumption and has the main voltage regulator and the RC oscillator enabled.

- Standby similar to Idle withlow standby power consumption but has the main voltage regulator and the crystal oscillator enabled.

- FS (Frequency synthesizer) the frequency synthesizer is alive to shorten startup time to transmit or receive states.

- Transmit transmitter is active.

- Receive receiver is active.

## 5.3 System Protection

The MKW01Z128 provides numerous vehicles to maintain security or a high level of system robustness:

- Standard COP Watchdog reset with option to run from dedicated 1-kHz internal clock source or bus clock. The COP watchdog is intended to force a system reset when the application software fails to execute as expected.

- LVD protection with reset or interrupt; selectable trip points.

- HardFault exception on attempts to execute undefined instructions or access to undefined memory space.

- LOCKUP reset resource from core.

- Flash protection

# 6 Development Environment

Development support for the ARM® Cortex M0+ MCU on the MKW01Z128 is configured to provide maximum flexibility as allowed by the restrictions of the pinout and other available resources. One debug interface is supported:

• Two-wire Serial Wire Debug (SWD) interface

Table 5 presents a brief description of the serial wire debug description.

| Module | Туре          | Description                                                                                                                                                    |

|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWCLK  | Input         | Serial Wire Clock. This pin is the clock for debug logic when in the Serial Wire Debug mode. This pin is pulled down internally.                               |

| SWDIO  | Input /Output | Serial Wire debug data input / output. The SWDIO pin is used by an external debug tool for communication and devive control. This pin is pulled up internally. |

|        |               |                                                                                                                                                                |

**Table 5. Debug Components Description**

# 7 System Electrical Specification

This section details maximum ratings for the 60 pin LGA package and recommended operating conditions, DC characteristics, and AC characteristics for the modem, and the MCU.

## 7.1 LGA Package Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maximum rating is not guaranteed. Stress beyond the limits specified in Table 6 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either  $V_{SS}$  or  $V_{DD}$ ) or the programmable pull-up resistor associated with the pin is enabled.

Table 6 shows the maximum ratings for the 60 Pin LGA package.

**Table 6. LGA Package Maximum Ratings**

| Rating                       | Symbol                                 | Value                              | Unit |

|------------------------------|----------------------------------------|------------------------------------|------|

| Maximum Junction Temperature | T <sub>J</sub>                         | 95                                 | °C   |

| Storage Temperature Range    | T <sub>stg</sub>                       | -55 to 115                         | °C   |

| Power Supply Voltage         | V <sub>BATT</sub> , V <sub>DDINT</sub> | -0.3 to 3.8                        | Vdc  |

| Digital Input Voltage        | Vin                                    | -0.3 to (V <sub>DDINT</sub> + 0.3) |      |

| RF Input Power               | P <sub>max</sub>                       | 6                                  | dBm  |

Note: Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the limits in the Electrical Characteristics

or Recommended Operating Conditions tables.

Note: Meets Human Body Model (HBM) = 2 kV. RF input/output pins have no ESD protection.

#### 7.2 **ESD Protection and Latch-Up Immunity**

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, normal handling precautions should be used to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with the JESD22 Stress Test Qualification for Commercial Grade Integrated Circuits. During the device qualification ESD stresses were performed for the human body model (HBM), the machine model (MM) and the charge device model (CDM).

All latchup testing is in conformity with the JESD78 IC Latch-Up Test.

A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification.

Table 7. ESD and Latch-up Test Conditions

| Model         | Description                           | Symbol | Value        | Unit |

|---------------|---------------------------------------|--------|--------------|------|

|               | Series resistance                     | R1     | 1500         | Ω    |

| Human<br>Body | Storage capacitance                   | С      | 100          | pF   |

|               | Number of pulses per pin <sup>1</sup> | _      | 1            |      |

|               | Series resistance                     | R1     | 0            | Ω    |

| Machine       | Storage capacitance                   | С      | 200          | pF   |

|               | Number of pulses per pin <sup>1</sup> | _      | 1            |      |

| Lotob up      | Minimum input voltage limit           |        | <b>–</b> 1.8 | V    |

| Latch-up      | Maximum input voltage limit           |        | 4.32         | V    |

<sup>1</sup> This number represents a minimum number for both positive pulse(s) and negative pulse(s)

Table 8. ESD and Late lection Characteristics

| No. | Rating <sup>1</sup>                       | Symbol           | Min    | Max | Unit |

|-----|-------------------------------------------|------------------|--------|-----|------|

| 1   | Human body model (HBM)                    | V <sub>HBM</sub> | ± 2000 | _   | V    |

| 2   | Machine model (MM)                        | $V_{MM}$         | ± 200  | _   | V    |

| 3   | Charge device model (CDM)                 | V <sub>CDM</sub> | ± 750  | _   | V    |

| 4   | Latch-up current at T <sub>A</sub> = 85°C | I <sub>LAT</sub> | ± 100  | _   | mA   |

Parameter is achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted.

## 7.3 Transceiver Electrical Characteristics

The tables below give the electrical specifications of the transceiver under the following conditions: Supply voltage VBAT1= VBAT2=VDD=3.3 V, temperature = 25 °C, FXOSC = 32 MHz, FRF = 915 MHz, Pout = +13dBm, 2-level FSK modulation without pre-filtering, FDA = 5 kHz, Bit Rate = 4.8 kb/s and terminated in a matched 50 Ohm impedance, unless otherwise specified.

#### NOTE

Unless otherwise specified, the performances in the other frequency bands are similar or better.

## 7.3.1 Transceiver Recommended Operating Conditions

**Table 9. Recommended Operating Conditions**

| Characteristic                                      | Symbol           | Min                      | Тур   | Max                      | Unit |

|-----------------------------------------------------|------------------|--------------------------|-------|--------------------------|------|

| Power Supply Voltage (V <sub>BATT</sub> )           |                  | 1.8                      |       | 3.6                      | Vdc  |

| Operating Temperature Range                         | T <sub>A</sub>   | -40                      | 25    | 85                       | °C   |

| Logic Input Voltage Low                             | V <sub>IL</sub>  | 0                        | -     | 20%<br>V <sub>BATT</sub> | V    |

| Logic Input Voltage High                            | V <sub>IH</sub>  | 80%<br>V <sub>BATT</sub> | -     | V <sub>BATT</sub>        | V    |

| Logic Output Voltage Low (I <sub>max</sub> = -1 mA) | V <sub>OL</sub>  | 0                        | -     | 10%<br>V <sub>BATT</sub> | V    |

| Logic Output Voltage High (I <sub>max</sub> = 1 mA) | V <sub>OH</sub>  | 90%<br>V <sub>BATT</sub> | -     | V <sub>BATT</sub>        | V    |

| Load capacitance on digital ports                   | C <sub>L</sub>   |                          |       | 25                       | pF   |

| SPI Clock Rate                                      | f <sub>SPI</sub> | -                        | -     | 8.0                      | MHz  |

| RF Input Power                                      | P <sub>max</sub> | -                        | -     | 0                        | dBm  |

| Crystal Reference Oscillator Frequency              | f <sub>ref</sub> |                          | 32 MH | lz Only                  |      |

# 7.3.2 Transceiver Power Consumption

**Table 10. Power Supply Current**

| Characteristic                                                                     | Conditions                                                                                                                                           | Symbol  | Min              | Тур                        | Max              | Unit                 |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|----------------------------|------------------|----------------------|

| Supply current in Sleep mode                                                       |                                                                                                                                                      | IDDSL   | -                | 0.1                        | 1                | μA                   |

| Supply current in Idle mode                                                        | RC oscillator enabled                                                                                                                                | IDDIDLE | -                | 1.2                        | -                | μA                   |

| Supply current in Standby mode                                                     | Crystal oscillator enabled                                                                                                                           | IDDST   | -                | 1.25                       | 1.5              | mA                   |

| Supply current in Synthesizer mode                                                 |                                                                                                                                                      | IDDFS   | -                | 9                          | -                | mA                   |

| Supply current in Receive mode                                                     |                                                                                                                                                      | IDDR    | -                | 16                         | -                | mA                   |

| Supply current in Transmit mode with appropriate matching, stable across VDD range | RFOP = +17 dBm, on PA_BOOST<br>RFOP = +13 dBm, on RFIO pin<br>RFOP = +10 dBm, on RFIO pin<br>RFOP = 0 dBm, on RFIO pin<br>RFOP = -1 dBm, on RFIO pin | IDDT    | -<br>-<br>-<br>- | 95<br>45<br>33<br>20<br>16 | -<br>-<br>-<br>- | mA<br>mA<br>mA<br>mA |

# 7.3.3 Transceiver Frequency Synthesis

**Table 11. Frequency Synthesizer Specification**

| Characteristic                                                     | Conditions                                                                                          | Symbol | Min               | Тур                                    | Max                | Unit                                                     |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------|-------------------|----------------------------------------|--------------------|----------------------------------------------------------|

| Synthesizer Frequency Range                                        | Programmable                                                                                        | FR     | 290<br>424<br>862 | -<br>-<br>-                            | 340<br>510<br>1020 | MHz<br>MHz<br>MHz                                        |

| Crystal oscillator frequency                                       |                                                                                                     | FXOSC  | -                 | 32                                     | -                  | MHz                                                      |

| Crystal oscillator wake-up time                                    |                                                                                                     | TS_OSC | -                 | 250                                    | 500                | μs                                                       |

| Frequency synthesizer wake-up time to PIILock signal               | From Standby mode                                                                                   | TS_FS  | -                 | 80                                     | 150                | μs                                                       |

| Frequency synthesizer hop time at most 10 kHz away from the target | 200 kHz step<br>1 MHz step<br>5 MHz step<br>7 MHz step<br>12 MHz step<br>20 MHz step<br>25 MHz step | _      | -                 | 20<br>20<br>50<br>50<br>80<br>80<br>80 | -                  | та<br>та<br>та<br>та<br>та<br>та<br>та<br>та<br>та<br>та |

| Frequency synthesizer step                                         | FSTEP = FXOSC/2 <sup>19</sup>                                                                       | FSTEP  | -                 | 61.0                                   | -                  | Hz                                                       |

| RC Oscillator frequency                                            | After calibration                                                                                   | FRC    | -                 | 62.5                                   | -                  | kHz                                                      |

| Bit rate, FSK                                                      | Programmable                                                                                        | BRF    | 1.2               | -                                      | 600                | kbps                                                     |

| Bit rate, OOK                                                      | Programmable                                                                                        | BRO    | 1.2               | -                                      | 32.768             | kbps                                                     |

| Frequency deviation, FSK                                           | Programmable<br>FDA + BRF/2 =< 500 kHz                                                              | FDA    | 0.6               | -                                      | 300                | kHz                                                      |

### 7.3.4 Receiver

All receiver tests are performed with RxBw = 10 kHz (Single Side Bandwidth) as programmed in RegRxBw, receiving a PN15 sequence with a BER of 0.1% (Bit Synchronizer is enabled), unless otherwise specified. The LNA impedance is set to 200 Ohms, by setting bit LnaZin in RegLna to 1. Blocking tests are performed with an unmodulated interferer. The wanted signal power for the Blocking Immunity, ACR, IIP2, IIP3 and AMR tests is set 3 dB above the nominal sensitivity level.

**Table 12. Receiver Specification**

| Characteristic                                                                           | Conditions                                                                               | Symbol            | Min         | Тур                  | Max         | Unit              |

|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------|-------------|----------------------|-------------|-------------------|

| FSK sensitivity, highest LNA gain                                                        | FDA = 5 kHz, BR = 1.2 kb/s<br>FDA = 5 kHz, BR = 4.8 kb/s<br>FDA = 40 kHz, BR = 38.4 kb/s | RFS_F             | -<br>-<br>- | -118<br>-114<br>-105 | -<br>-<br>- | dBm<br>dBm<br>dBm |

|                                                                                          | FDA = 5 kHz, BR = 1.2 kb/s <sup>1</sup>                                                  |                   | -           | -120                 | -           | dBm               |

| OOK sensitivity, highest LNA gain                                                        | BR = 4.8 kb/s                                                                            | RFS_O             | -           | -112                 | -109        | dBm               |

| Co-Channel Rejection                                                                     |                                                                                          | CCR               | -13         | -10                  | -           | dB                |

| Adjacent Channel Rejection                                                               | Offset = +/- 25 kHz<br>Offset = +/- 50 kHz                                               | ACR               | -<br>37     | 42<br>42             | -           | dB<br>dB          |

| Blocking Immunity                                                                        | Offset = +/- 1 MHz<br>Offset = +/- 2 MHz<br>Offset = +/- 10 MHz                          | ВІ                | -<br>-<br>- | -45<br>-40<br>-32    |             | dBm<br>dBm<br>dBm |

| Blocking Immunity Wanted signal at sensitivity +16dB                                     | Offset = +/- 1 MHz<br>Offset = +/- 2 MHz<br>Offset = +/- 10 MHz                          |                   | -<br>-<br>- | -36<br>-33<br>-25    | -<br>-<br>- | dBm<br>dBm<br>dBm |

| AM Rejection , AM modulated interferer with 100% modulation depth, fm = 1 kHz, square    | Offset = +/- 1 MHz<br>Offset = +/- 2 MHz<br>Offset = +/- 10 MHz                          | AMR               | -<br>-<br>- | -45<br>-40<br>-32    | -<br>-<br>- | dBm<br>dBm<br>dBm |

| 2nd order Input Intercept Point<br>Unwanted tones are 20 MHz above<br>the LO             | Lowest LNA gain<br>Highest LNA gain                                                      | IIP2              | -           | +75<br>+35           | -           | dBm<br>dBm        |

| 3rd order Input Intercept point<br>Unwanted tones are 1MHz and 1.995<br>MHz above the LO | Lowest LNA gain<br>Highest LNA gain                                                      | IIP3              | -<br>-23    | +20<br>-18           | -           | dBm<br>dBm        |

| Single Side channel filter BW                                                            | Programmable                                                                             | BW_SSB            | 2.6         | -                    | 500         | kHz               |

| Image rejection in OOK mode                                                              | Wanted signal level = -106 dBm                                                           | IMR_<br>OOK       | 27          | 30                   | -           | dB                |

| Receiver wake-up time, from PLL locked state to <i>RxReady</i>                           | RxBw = 10 kHz, BR = 4.8 kb/s<br>RxBw = 200 kHz, BR = 100 kb/s                            | TS_RE             | -           | 1.7<br>96            | -           | ms<br>µs          |

| Receiver wake-up time, from PLL locked state, AGC enabled                                | RxBw= 10 kHz, BR = 4.8 kb/s<br>RxBw = 200 kHz, BR = 100 kb/s                             | TS_RE_<br>AGC     | -           | 3.0<br>163           |             | ms<br>µs          |

| Receiver wake-up time, from PLL lock state, AGC and AFC enabled                          | RxBw= 10 kHz, BR = 4.8 kb/s<br>RxBw = 200 kHz, BR = 100 kb/s                             | TS_RE_<br>AGC&AFC |             | 4.8<br>265           |             | ms<br>µs          |

| FEI sampling time                                                                        | Receiver is ready                                                                        | TS_FEI            | -           | 4.T <sub>bit</sub>   | -           | -                 |

| AFC Response Time                                                                        | Receiver is ready                                                                        | TS_AFC            | -           | 4.T <sub>bit</sub>   | -           | -                 |

**Table 12. Receiver Specification**

| Characteristic     | naracteristic Conditions |         | Min | Тур                | Max | Unit       |

|--------------------|--------------------------|---------|-----|--------------------|-----|------------|

| RSSI Response Time | Receiver is ready        | TS_RSSI | -   | 2.T <sub>bit</sub> | -   | -          |

| RSSI Dynamic Range | AGC enabled Min Max      | DR_RSSI |     | -115<br>0          |     | dBm<br>dBm |

<sup>1</sup> Set SensitivityBoost in RegTestLna to 0x2D to reduce the noise floor in the receiver

### 7.3.5 Transmitter

**Table 13. Transmitter Specidication**

| Characteristic                                                 | Conditions                                                               | Symbol | Min | Тур        | Max | Unit       |

|----------------------------------------------------------------|--------------------------------------------------------------------------|--------|-----|------------|-----|------------|

| RF output power in 50 ohms<br>On RFIO pin                      | Programmable with 1dB steps<br>Max<br>Min                                | RF_OP  | -   | +13<br>-18 | -   | dBm<br>dBm |

| Max RF output power, on PA_BOOST pin                           | With external match to 50 ohms                                           | RF_OPH | -   | +17        | -   | dBm        |

| RF output power stability                                      | From VDD=1.8V to 3.6V                                                    | ∆RF_OP | -   | +/-0.3     | -   | dB         |

| Transmitter Phase Noise                                        | 50 kHz Offset from carrier<br>868 / 915 MHz bands<br>434 / 315 MHz bands | PHN    | -   | -95<br>-99 | -   | dBc/Hz     |

| Transmitter adjacent channel power (measured at 25 kHz offset) | BT=0.5 . Measurement conditions as defined by EN 300 220-1 V2.1.1        | ACP    | -   | -          | -37 | dBm        |

| Transmitter wake up time, to the first rising edge of DCLK     | Frequency Synthesizer enabled,<br>PaRamp = 10 µs, BR = 4.8 kb/s.         | TS_TR  | -   | 120        | 1   | μs         |

# 7.4 MCU Electrical Characteristics

The following sections describe the electrical characteristics of the MKW01Z128 MCU.

## 7.4.1 MCU DC Characteristics

This section includes information about power supply requirements and I/O pin characteristics.

**Table 14. DC Characteristics**

| Num | С | Characteristic      |                                  | Symbol | Condition                                  | Min                   | Typ <sup>1</sup> | Max | Unit |

|-----|---|---------------------|----------------------------------|--------|--------------------------------------------|-----------------------|------------------|-----|------|

| 1   |   | Operating Voltage   | )                                |        |                                            | 1.8 <sup>2</sup>      |                  | 3.6 | V    |

|     | С | Output high voltage | All I/O pins, low-drive strength |        | 1.8 V, I <sub>Load</sub> = -2 mA           | V <sub>DD</sub> – 0.5 | _                | _   |      |

| 2   | Р | -                   | All I/O pins,                    | 1 V()H | $2.7 \text{ V}, I_{Load} = -10 \text{ mA}$ | V <sub>DD</sub> – 0.5 | _                | _   | V    |

|     | Т |                     | high-drive strength              |        | $2.3 \text{ V}, I_{Load} = -6 \text{ mA}$  | V <sub>DD</sub> – 0.5 | _                | _   |      |

|     | С |                     |                                  |        | 1.8V, $I_{Load} = -3 \text{ mA}$           | V <sub>DD</sub> - 0.5 | _                | _   |      |

**Table 14. DC Characteristics (continued)**

| Num | С | Cha                                                          | aracteristic                                       | Symbol             | Condition                                       | Min                    | Typ <sup>1</sup> | Max                    | Unit |

|-----|---|--------------------------------------------------------------|----------------------------------------------------|--------------------|-------------------------------------------------|------------------------|------------------|------------------------|------|

| 3   | D | Output high current                                          | Max total I <sub>OH</sub> for all ports            | I <sub>OHT</sub>   |                                                 | _                      |                  | 100                    | mA   |

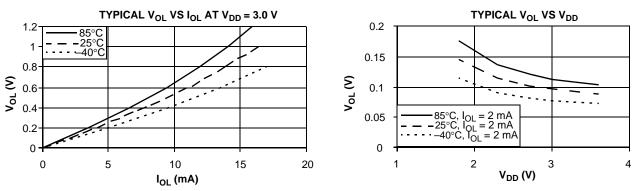

|     | С | Output low voltage                                           | All I/O pins, low-drive strength                   |                    | 1.8 V, I <sub>Load</sub> = 2 mA                 | _                      | _                | 0.5                    |      |

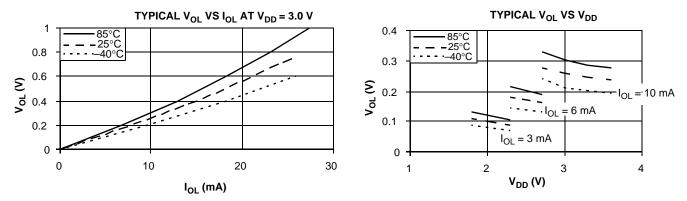

| 4   | Р |                                                              | All I/O pins,                                      | $V_{OL}$           | 2.7 V, I <sub>Load</sub> = 10 mA                | _                      |                  | 0.5                    | V    |

|     | T |                                                              | high-drive strength                                |                    | $2.3 \text{ V}, I_{\text{Load}} = 6 \text{ mA}$ |                        |                  | 0.5                    |      |

|     | С |                                                              |                                                    |                    | 1.8 V, I <sub>Load</sub> = 3 mA                 | _                      |                  | 0.5                    |      |

| 5   | D | Output low current                                           | Max total I <sub>OL</sub> for all ports            | I <sub>OLT</sub>   |                                                 | _                      | _                | 100                    | mA   |

| 6   | Р | Input high                                                   | all digital inputs                                 | V                  | V <sub>DD</sub> > 2.7 V                         | 0.70 x V <sub>DD</sub> | _                | _                      |      |

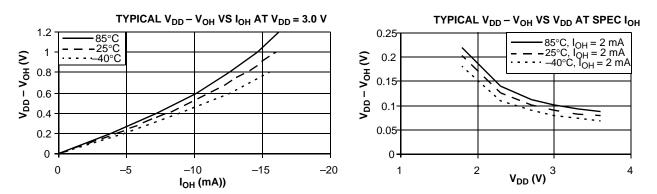

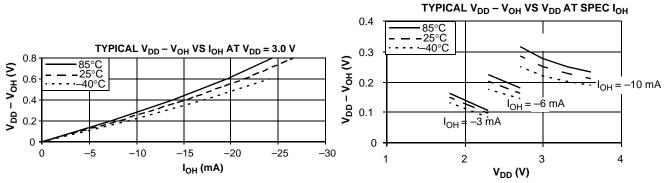

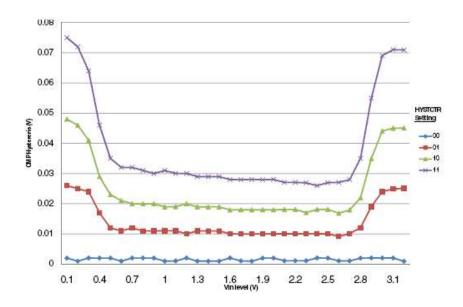

| Ü   | С | voltage                                                      |                                                    | $V_{IH}$           | V <sub>DD</sub> > 1.8 V                         | 0.85 x V <sub>DD</sub> |                  | _                      | V    |