## **High-Voltage Switchmode Controllers**

#### **DESCRIPTION**

The Si9110/9111 are BiC/DMOS integrated circuits designed for use as high-performance switchmode controllers. A high-voltage DMOS input allows the controller to work over a wide range of input voltages (10 to 120 VDC). Current-mode PWM control circuitry is implemented in CMOS to reduce internal power consumption to less than 10 mW.

A push-pull output driver provides high-speed switching for MOSPOWER devices large enough to supply 50 W of output power. When combined with an output MOSFET and transformer, the Si9110/9111 can be used to implement single-ended power converter topologies (i.e., flyback, forward, and cuk).

The Si9110/9111 are available in both standard and lead (Pb)-free 14-pin plastic DIP and SOIC packages which are specified to operate over the industrial temperature range of - 40 °C to 85 °C.

#### **FEATURES**

- 10 V to 120 V Input Range

- **Current-Mode Control**

- High-Speed, Source-Sink Output Drive

- High Efficiency Operation (> 80 %)

- Internal Start-Up Circuit

- Internal Oscillator (1 MHz)

- SHUTDOWN and RESET

- Reference Selection Si9110 - ± 1 % Si9111 - ± 10 %

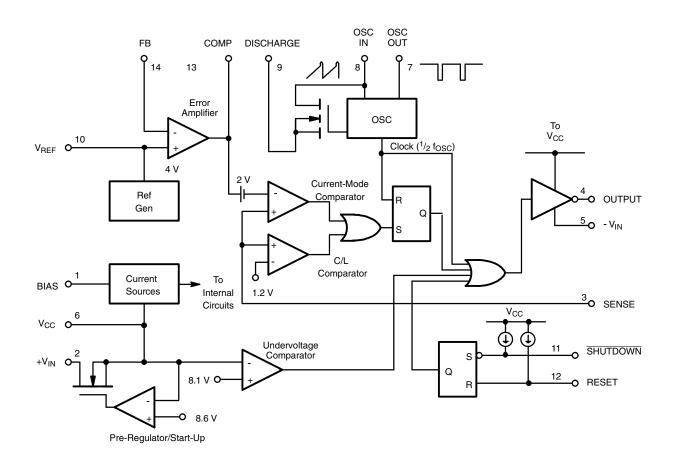

#### **FUNCTIONAL BLOCK DIAGRAM**

Document Number: 70004 S11-0975-Rev. I, 16-May-11

| ABSOLUTE MAXIMUM RATINGS                                              |                                                                                              |                                |       |  |  |  |  |  |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------|-------|--|--|--|--|--|

| Parameter                                                             |                                                                                              | Limit                          | Unit  |  |  |  |  |  |

| Voltages Referenced to - V <sub>IN</sub> (Note: V <sub>CC</sub> < + V | Voltages Referenced to - V <sub>IN</sub> (Note: V <sub>CC</sub> < + V <sub>IN</sub> + 0.3 V) |                                |       |  |  |  |  |  |

| V <sub>CC</sub>                                                       |                                                                                              | 15                             |       |  |  |  |  |  |

| +V <sub>IN</sub>                                                      |                                                                                              | 120                            | V     |  |  |  |  |  |

| Logic Inputs (RESET, SHUTDOWN, OSC IN, OSC                            | SC OUT)                                                                                      | - 0.3 to V <sub>CC</sub> + 0.3 | v     |  |  |  |  |  |

| Linear Inputs (FEEDBACK, SENSE, BIAS, V <sub>REF</sub>                | -)                                                                                           | - 0.3 to V <sub>CC</sub> + 0.3 |       |  |  |  |  |  |

| HV Pre-Regulator Input Current (continuous)                           |                                                                                              | 5                              | mA    |  |  |  |  |  |

| Storage Temperature                                                   |                                                                                              | - 65 to 150                    |       |  |  |  |  |  |

| Operating Temperature                                                 |                                                                                              | - 40 to 85                     | °C    |  |  |  |  |  |

| Junction Temperature (T <sub>J</sub> )                                |                                                                                              | 150                            |       |  |  |  |  |  |

| Dawer Dissination (Daskage)                                           | 14-Pin Plastic DIP (J Suffix) <sup>b</sup>                                                   | 750                            | mW    |  |  |  |  |  |

| Power Dissipation (Package) <sup>a</sup>                              | 14-Pin SOIC (Y Suffix) <sup>c</sup>                                                          | 900                            | 11100 |  |  |  |  |  |

| Thermal Impedance $(\Theta_{1A})$                                     | 14-Pin Plastic DIP                                                                           | 167                            | °C/W  |  |  |  |  |  |

| Thomas impodance (OJA)                                                | 14-Pin SOIC                                                                                  | 140                            |       |  |  |  |  |  |

#### Notes:

- a. Device Mounted with all leads soldered or welded to PC board.

- b. Derate 6 mW/°C above 25 °C.

- c. Derate 7.2 mW/°C above 25 °C.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| RECOMMENDED OPERATING RANGE              |                          |                                       |  |  |  |

|------------------------------------------|--------------------------|---------------------------------------|--|--|--|

| Parameter                                | Limit                    | Unit                                  |  |  |  |

| Voltages Referenced to - V <sub>IN</sub> |                          |                                       |  |  |  |

| V <sub>CC</sub>                          | 9.5 to 13.5              | V                                     |  |  |  |

| + V <sub>IN</sub>                        | 10 to 120                | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |  |  |  |

| fosc                                     | 40 kHz to 1 MHz          |                                       |  |  |  |

| R <sub>OSC</sub>                         | 25 kΩ to 1 MΩ            |                                       |  |  |  |

| Linear Inputs                            | 0 to V <sub>CC</sub> - 3 | V                                     |  |  |  |

| Digital Inputs                           | 0 to V <sub>CC</sub>     |                                       |  |  |  |

| SPECIFICATIONS <sup>a</sup>          |                   |                                                                                                                                                                                                  |        |        |                                     |                   |                   |        |

|--------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|-------------------------------------|-------------------|-------------------|--------|

|                                      |                   | Test Conditions Unless Otherwise Specified DISCHARGE = - $V_{IN} = 0 \text{ V}$ $V_{CC} = 10 \text{ V}, + V_{IN} = 48 \text{ V}$ $R_{BIAS} = 390 \text{ k}\Omega, R_{OSC} = 330 \text{ k}\Omega$ |        |        | <b>D Suffix</b><br>- 40 °C to 85 °C |                   |                   |        |

| Parameter                            | Symbol            |                                                                                                                                                                                                  |        | Temp.b | Min. <sup>d</sup>                   | Typ. <sup>c</sup> | Max. <sup>d</sup> | Unit   |

| Reference                            |                   |                                                                                                                                                                                                  |        |        |                                     |                   |                   |        |

|                                      |                   | 300 IN                                                                                                                                                                                           | Si9110 | Room   | 3.92                                | 4.0               | 4.08              | - v    |

| Output Voltage                       | V <sub>R</sub>    | OSC IN = - V <sub>IN</sub><br>(OSC Disabled)                                                                                                                                                     | Si9111 | Room   | 3.60                                | 4.0               | 4.40              |        |

| Output Voltage                       | VR                | $R_{\rm L} = 10  \text{M}\Omega$                                                                                                                                                                 | Si9110 | Full   | 3.86                                |                   | 4.14              |        |

|                                      |                   |                                                                                                                                                                                                  | Si9111 | Full   | 3.52                                |                   | 4.46              |        |

| Output Impedance <sup>e</sup>        | Z <sub>OUT</sub>  |                                                                                                                                                                                                  |        | Room   | 15                                  | 30                | 45                | kΩ     |

| Short Circuit Current                | I <sub>SREF</sub> | $V_{REF} = -V_{IN}$                                                                                                                                                                              |        | Room   | 70                                  | 100               | 130               | μΑ     |

| Temperature Stability <sup>e</sup>   | T <sub>REF</sub>  |                                                                                                                                                                                                  |        | Full   |                                     | 0.5               | 1.0               | mV/°C  |

| Oscillator                           |                   |                                                                                                                                                                                                  |        |        |                                     |                   |                   |        |

| Maximum Frequency <sup>e</sup>       | f <sub>MAX</sub>  | $R_{OSC} = 0$                                                                                                                                                                                    |        | Room   | 1                                   | 3                 |                   | MHz    |

| Initial Accuracy                     | fosc              | R <sub>OSC</sub> = 330 k, See Note f                                                                                                                                                             |        | Room   | 80                                  | 100               | 120               | kHz    |

|                                      | OSC               | R <sub>OSC</sub> = 150 k, See Note                                                                                                                                                               | f      | Room   | 160                                 | 200               | 240               | NI IZ  |

| Voltage Stability                    | ∆f/f              | $\Delta f/f = f(13.5 \text{ V}) - f(9.5 \text{ V})/f(9.5 \text{ V})$                                                                                                                             |        | Room   | ·                                   | 10                | 15                | %      |

| Temperature Coefficient <sup>e</sup> | T <sub>OSC</sub>  |                                                                                                                                                                                                  |        | Full   |                                     | 200               | 500               | ppm/°C |

|                                                             |                        | Test Conditions<br>Unless Otherwise Specified<br>DISCHARGE = - V <sub>IN</sub> = 0 V                                | d       |              | D Suffix<br>- 40 °C to 85 °C |                   |                   |            |

|-------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------|---------|--------------|------------------------------|-------------------|-------------------|------------|

| Parameter                                                   | Symbol                 | $V_{CC} = 10 \text{ V}, + V_{IN} = 48 \text{ V}$<br>$R_{BIAS} = 390 \text{ k}\Omega, R_{OSC} = 330 \text{ k}\Omega$ |         | Temp.b       | Min. <sup>d</sup>            | Typ. <sup>c</sup> | Max. <sup>d</sup> | Unit       |

| Error Amplifier                                             |                        |                                                                                                                     |         |              |                              |                   |                   |            |

| Feedback Input Voltage                                      | V <sub>FB</sub>        | FB Tied to COMP<br>OSC IN = - V <sub>IN</sub> , (OSC Disabled)                                                      | Si9110  | Room         | 3.96                         | 4.00              | 4.04              | ٧          |

| Input BIAS Current                                          |                        | OSC IN = - $V_{IN}$ , $V_{FB} = 4 V$                                                                                | Si9111  | Room         | 3.60                         | 4.00<br>25        | 4.40<br>500       | nA         |

| Input OFFSET Voltage                                        | I <sub>FB</sub>        | 030 IIV = - V <sub>IN</sub> , V <sub>FB</sub> = 4 V                                                                 |         | Room         |                              | ± 15              | ± 40              | m\         |

| 1 0                                                         |                        | OSC IN - V                                                                                                          |         | Room         | 60                           | ± 15              | ± 40              | dB         |

| Open Loop Voltage Gain <sup>e</sup>                         | A <sub>VOL</sub><br>BW | OSC IN = $-V_{IN}$<br>(OSC Disabled)                                                                                |         | Room         | 1                            | 1.3               |                   | MH         |

| Unity Gain Bandwidthe                                       |                        | (OGC Disabled)                                                                                                      |         | Room         | '                            | 1000              | 2000              | Ω          |

| Dynamic Output Impedance <sup>e</sup>                       | Z <sub>OUT</sub>       | Source (V <sub>FB</sub> = 3.4 V)                                                                                    |         | Room         |                              | - 2.0             | - 1.4             | 52         |

| Output Current                                              | I <sub>OUT</sub>       | Sink (V <sub>FB</sub> = 4.5 V)                                                                                      |         | Room         | 0.12                         | 0.15              | - 1.4             | m <i>P</i> |

| Power Supply Rejection                                      | PSRR                   | $9.5 \text{ V} \le \text{V}_{CC} \le 13.5 \text{ V}$                                                                |         | Room         | 50                           | 70                |                   | dB         |

| Current Limit                                               | 1 01111                | 0.0 v = v <sub>CC</sub> = 10.0 v                                                                                    |         | 1100111      | 50                           |                   |                   | L          |

| Threshold Voltage                                           | V <sub>SOURCE</sub>    | V <sub>FB</sub> = 0                                                                                                 |         | Room         | 1.0                          | 1.2               | 1.4               | V          |

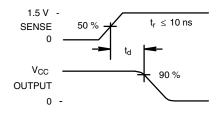

| Delay to Output <sup>e</sup>                                | t <sub>d</sub>         | V <sub>SENSE</sub> = 1.5 V, See Figure                                                                              | 1       | Room         | 1.0                          | 100               | 150               | ns         |

| Pre-Regulator/Start-Up                                      | -a                     | - SENSE , COS . IGUIO                                                                                               |         |              |                              |                   |                   |            |

| Input Voltage                                               | + V <sub>IN</sub>      | I <sub>IN</sub> = 10 μA                                                                                             |         | Room         | 120                          |                   |                   | V          |

| Input Leakage Current                                       | + I <sub>IN</sub>      | V <sub>CC</sub> ≥ 9.4 V                                                                                             |         | Room         |                              |                   | 10                | μΑ         |

| Pre-Regulator Start-Up Current                              | I <sub>START</sub>     | Pulse Width ≤ 300 μs, V <sub>CC</sub> = V <sub>ULVO</sub>                                                           |         | Room         | 8                            | 15                |                   | m/         |

| V <sub>CC</sub> Pre-Regulator Turn-Off<br>Threshold Voltage | V <sub>REG</sub>       | I <sub>PRE-REGULATOR</sub> = 10 μA                                                                                  |         | Room         | 7.8                          | 8.6               | 9.4               |            |

| Undervoltage Lockout                                        | V <sub>UVLO</sub>      |                                                                                                                     |         | Room         | 7.0                          | 8.1               | 8.9               | V          |

| V <sub>REG</sub> - V <sub>UVLO</sub>                        | V <sub>DELTA</sub>     |                                                                                                                     |         | Room         | 0.3                          | 0.6               |                   |            |

| Supply                                                      |                        |                                                                                                                     |         |              |                              |                   |                   | l          |

| Supply Current                                              | I <sub>CC</sub>        | V <sub>LOAD</sub> ≤ 75 pF (Pin 4)                                                                                   |         | Room         | 0.45                         | 0.6               | 1.0               | m/         |

| Bias Current                                                | I <sub>BIAS</sub>      | LOAD                                                                                                                |         | Room         | 10                           | 15                | 20                | μA         |

| Logic                                                       |                        |                                                                                                                     |         |              |                              |                   |                   |            |

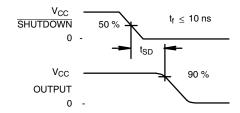

| SHUTDOWN Delay <sup>e</sup>                                 | t <sub>SD</sub>        | C <sub>L</sub> = 500 pF, V <sub>SENSE</sub> = - V <sub>IN</sub> , See F                                             | igure 2 | Room         |                              | 50                | 100               |            |

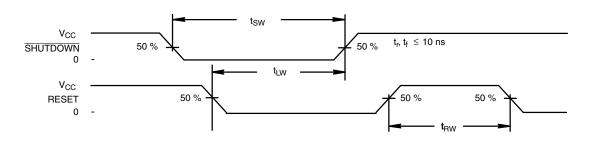

| SHUTDOWN Pulse Width <sup>e</sup>                           | t <sub>SW</sub>        | See Figure 3                                                                                                        |         | Room         | 50                           |                   |                   |            |

| RESET Pulse Width <sup>e</sup>                              | t <sub>RW</sub>        |                                                                                                                     |         | Room         | 50                           |                   |                   | ns         |

| Latching Pulse Width SHUTDOWN and RESET Lowe                | t <sub>LW</sub>        | See Figure 3                                                                                                        |         | Room         | 25                           |                   |                   |            |

| Input Low Voltage                                           | $V_{IL}$               |                                                                                                                     |         | Room         |                              |                   | 2.0               | V          |

| Input High Voltage                                          | V <sub>IH</sub>        |                                                                                                                     |         | Room         | 8.0                          |                   |                   | _ ′        |

| Input Current Input Voltage High                            | I <sub>IH</sub>        | V <sub>IN</sub> = 10 V                                                                                              |         | Room         |                              | 1                 | 5                 |            |

| Input Current Input Voltage Low                             | I <sub>IL</sub>        | V <sub>IN</sub> = 0 V                                                                                               |         | Room         | - 35                         | - 25              |                   | μΑ         |

| Output                                                      |                        |                                                                                                                     |         |              |                              |                   |                   |            |

| Output High Voltage                                         | V <sub>OH</sub>        | I <sub>OUT</sub> = - 10 mA                                                                                          |         | Room<br>Full | 9.7<br>9.5                   |                   |                   | V          |

| Output Low Voltage                                          | V <sub>OL</sub>        | I <sub>OUT</sub> = 10 mA                                                                                            |         | Room<br>Full |                              | _                 | 0.30<br>0.50      |            |

| Output Resistance                                           | R <sub>OUT</sub>       | I <sub>OUT</sub> = 10 mA, Source or Sink                                                                            |         | Room<br>Full |                              | 20<br>25          | 30<br>50          | Ω          |

| Rise Time <sup>e</sup>                                      | t <sub>r</sub>         | C <sub>L</sub> = 500 pF                                                                                             |         | Room         |                              | 40                | 75                | ns         |

| Fall Time <sup>e</sup>                                      | t <sub>f</sub>         | - L 222 F1                                                                                                          |         | Room         |                              | 40                | 75                |            |

- a. Refer to PROCESS OPTION FLOWCHART for additional information.

b. Room = 25 °C, Full = as determined by the operating temperature suffix.

c. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

d. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum.

- e. Guaranteed by design, not subject to production test. f.  $C_{STRAY}$  Pin 8 =  $\leq$  5 pF.

### **TIMING WAVEFORMS**

Figure 2.

Figure 3.

### **TYPICAL CHARACTERISTICS**

Figure 5. Output Switching Frequency vs. Oscillator Resistance

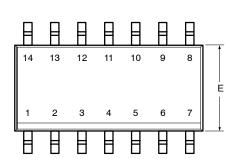

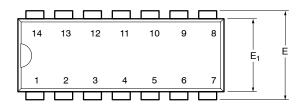

#### PIN CONFIGURATIONS AND ORDERING INFORMATION

#### **Dual-In-Line and SOIC BIAS** FΒ COMP $+V_{IN}$ SENSE RESET OUTPUT SHUTDOWN $V_{\mathsf{REF}}$ 10 - V<sub>IN</sub> DISCHARGE $V_{CC}$ OSC OUT OSC IN Top View

#### **DETAILED DESCRIPTION**

#### Pre-Regulator/Start-Up Section

Due to the low guiescent current requirement of the Si9110/ 9111 control circuitry, bias power can be supplied from the unregulated input power source, from an external regulated low-voltage supply, or from an auxiliary "bootstrap" winding on the output inductor or transformer.

When power is first applied during start-up, + V<sub>IN</sub> (pin 2) will draw a constant current. The magnitude of this current is determined by a high-voltage depletion MOSFET device which is connected between +  $V_{IN}$  and  $V_{CC}$  (pin 6). This start-up circuitry provides initial power to the IC by charging an external bypass capacitance connected to the V<sub>CC</sub> pin. The constant current is disabled when V<sub>CC</sub> exceeds 8.6 V. If  $V_{CC}$  is not forced to exceed the 8.6 V threshold, then  $V_{CC}$  will be regulated to a nominal value of 8.6 V by the pre-regulator circuit.

As the supply voltage rises toward the normal operating conditions, an internal undervoltage (UV) lockout circuit keeps the output driver disabled until V<sub>CC</sub> exceeds the undervoltage lockout threshold (typically 8.1 V). This guarantees that the control logic will be functioning properly and that sufficient gate drive voltage is available before the MOSFET turns on. The design of the IC is such that the undervoltage lockout threshold will be at least 300 mV less than the pre-regulator turn-off voltage. Power dissipation can be minimized by providing an external power source to V<sub>CC</sub> such that the constant current source is always disabled.

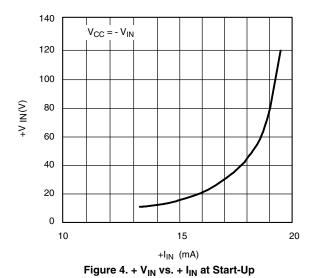

Note: During start-up or when V<sub>CC</sub> drops below 8.6 V the start-up circuit is capable of sourcing up to 20 mA. This may lead to a high level of power dissipation in the IC (for a 48 V input, approximately 1 W). Excessive start-up time caused by external loading of the V<sub>CC</sub> supply can result in device damage. Figure 6 gives the typical pre-regulator current at BiC/DMOS as a function of input voltage.

#### **BIAS**

To properly set the bias for the Si9110/9111, a 390 k $\Omega$ resistor should be tied from BIAS (pin 1) to - V<sub>IN</sub> (pin 5). This determines the magnitude of bias current in all of the analog

| ORDERING INFORMATION                  |                  |         |  |  |  |  |

|---------------------------------------|------------------|---------|--|--|--|--|

| Part Number Temperature Range Package |                  |         |  |  |  |  |

| Si9110DY                              |                  |         |  |  |  |  |

| Si9110DY-T1                           | 1                |         |  |  |  |  |

| Si9110DY-T1-E3                        | 1                | SOIC-14 |  |  |  |  |

| Si9111DY                              |                  | 3010-14 |  |  |  |  |

| Si9111DY-T1                           | - 40 °C to 85 °C |         |  |  |  |  |

| Si9111DY-T1-E3                        | - 40 10 10 85 10 |         |  |  |  |  |

| Si9110DJ                              | 7                |         |  |  |  |  |

| Si9110DJ-E3                           |                  | PDIP-14 |  |  |  |  |

| Si9111DJ                              |                  | FDIP-14 |  |  |  |  |

| Si9111DJ-E3                           |                  |         |  |  |  |  |

sections and the pull-up current for the SHUDOWN and RESET pins. The current flowing in the bias resistor is nominally 15 µA.

#### **Reference Section**

The reference section of the Si9110 consists of a temperature compensated buried zener and trimmable divider network. The output of the reference section is connected internally to the non-inverting input of the error amplifier. Nominal reference output voltage is 4 V. The trimming procedure that is used on the Si9110 brings the output of the error amplifier (which is configured for unity gain during trimming) to within ± 1 % of 4 V. This compensates for input offset voltage in the error amplifier.

The output impedance of the reference section has been purposely made high so that a low impedance external voltage source can be used to override the internal voltage source, if desired, without otherwise altering performance of the device.

Applications which use a separate external reference, such as non-isolated converter topologies and circuits employing optical coupling in the feedback loop, do not require a trimmed voltage reference with 1 % accuracy. The Si9111 accommodates the requirements of these applications at a lower cost, by leaving the reference voltage untrimmed. The 10 % accurate reference thus provided is sufficient to establish a dc bias point for the error amplifier.

#### **Error Amplifier**

Closed-loop regulation is provided by the error amplifier, which is intended for use with "around-the-amplifier" compensation. A MOS differential input stage provides for low input current. The noninverting input to the error amplifier (V<sub>REF</sub>) is internally connected to the output of the reference supply and should be bypassed with a small capacitor to ground.

#### **DETAILED DESCRIPTION (CONT'D)**

#### **Oscillator Section**

The oscillator consists of a ring of CMOS inverters, capacitors, and a capacitor discharge switch. Frequency is set by an external resistor between the OSC IN and OSC OUT pins. (See Figure 5 for details of resistor value vs. frequency.) The DISCHARGE pin should be tied to - VINI for normal internal oscillator operation. A frequency divider in the logic section limits switch duty cycle to ≤ 50 % by locking the switching frequency to one half of the oscillator frequency.

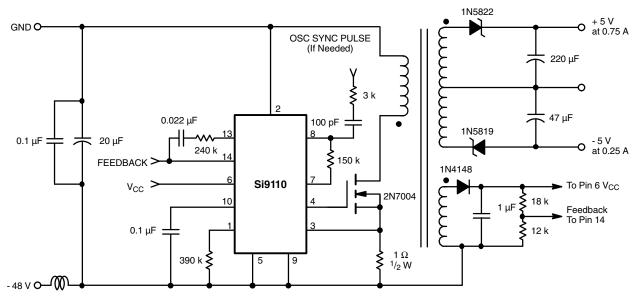

Remote synchronization is accomplished by capacitive coupling of a positive SYNC pulse into the OSC IN (pin 8) terminal. For a 5 V pulse amplitude and 0.5 µs pulse width, typical values would be 100 pF in series with 3 k $\Omega$  to pin 8.

#### **SHUTDOWN** and RESET

SHUTDOWN (pin 11) and RESET (pin 12) are intended for overriding the output MOSFET switch via external control logic. The two inputs are fed through a latch preceding the output switch. Depending on the logic state of RESET, SHUTDOWN can be either a latched or unlatched input. The output is off whenever SHUTDOWN is low. By simultaneously having SHUTDOWN and RESET low, the latch is set and SHUTDOWN has no effect until RESET goes high. The truth table for these inputs is given in Table 1.

Table 1. Truth Table for the SHUTDOWN and RESET Pins

| SHUTDOWN | RESET | Output                       |

|----------|-------|------------------------------|

| Н        | Н     | Normal Operation             |

| Н        | 7     | Normal Operation (No Change) |

| L        | H     | Off (Not Latched)            |

| L        | L     | Off (Latched)                |

|          | L     | Off (Latched, No Change)     |

Both pins have internal current source pull-ups and should be left disconnected when not in use. An added feature of the current sources is the ability to connect a capacitor and an open-collector driver to the SHUTDOWN or RESET pins to provide variable shutdown time.

#### **Output Driver**

The push-pull driver output has a typical on-resistance of 20  $\Omega$  . Maximum switching times are specified at 75 ns for a 500 pF load. This is sufficient to directly drive MOSFETs such as the 2N7004, 2N7005, IRFD120 and IRFD220. Larger devices can be driven, but switching times will be longer, resulting in higher switching losses. In order to drive large MOSPOWER devices, it is necessary to use an external driver IC, such as the Vishay Siliconix D469A. The D469A can switch very large devices such as the SMM20N50 (500 V, 0.3  $\Omega$ ) in approximately 100 ns.

#### **APPLICATIONS**

Figure 6. 5 Watt Power Supply for Telecom Applications

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see www.vishay.com/ppg?70004

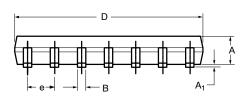

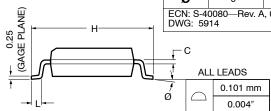

### SOIC (NARROW): 14-LEAD (POWER IC ONLY)

|                                             | MILLIMETERS |          | INC   | ICHES |  |  |

|---------------------------------------------|-------------|----------|-------|-------|--|--|

| Dim                                         | Min         | Max      | Min   | Max   |  |  |

| Α                                           | 1.35        | 1.75     | 0.053 | 0.069 |  |  |

| A <sub>1</sub>                              | 0.10        | 0.20     | 0.004 | 0.008 |  |  |

| В                                           | 0.38        | 0.51     | 0.015 | 0.020 |  |  |

| С                                           | 0.18        | 0.23     | 0.007 | 0.009 |  |  |

| D                                           | 8.55        | 8.75     | 0.336 | 0.344 |  |  |

| Е                                           | 3.8         | 4.00     | 0.149 | 0.157 |  |  |

| е                                           | 1.27        | 1.27 BSC |       | BSC   |  |  |

| Н                                           | 5.80        | 6.20     | 0.228 | 0.244 |  |  |

| L                                           | 0.50        | 0.93     | 0.020 | 0.037 |  |  |

| Ø                                           | 0°          | 8°       | 0°    | 8°    |  |  |

| ECN: S-40080—Rev. A, 02-Feb-04<br>DWG: 5914 |             |          |       |       |  |  |

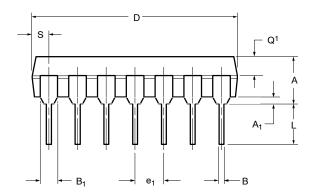

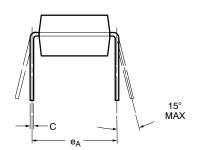

### PDIP: 14-LEAD (POWER IC ONLY)

|                                             | MILLIMETERS |       | INC   | HES   |  |

|---------------------------------------------|-------------|-------|-------|-------|--|

| Dim                                         | Min         | Max   | Min   | Max   |  |

| Α                                           | 3.81        | 5.08  | 0.150 | 0.200 |  |

| A <sub>1</sub>                              | 0.38        | 1.27  | 0.015 | 0.050 |  |

| В                                           | 0.38        | 0.51  | 0.015 | 0.020 |  |

| B <sub>1</sub>                              | 0.89        | 1.65  | 0.035 | 0.065 |  |

| С                                           | 0.20        | 0.30  | 0.008 | 0.012 |  |

| D                                           | 17.27       | 19.30 | 0.680 | 0.760 |  |

| Е                                           | 7.62        | 8.26  | 0.300 | 0.325 |  |

| E <sub>1</sub>                              | 5.59        | 7.11  | 0.220 | 0.280 |  |

| e <sub>1</sub>                              | 2.29        | 2.79  | 0.090 | 0.110 |  |

| e <sub>A</sub>                              | 7.37        | 7.87  | 0.290 | 0.310 |  |

| L                                           | 2.79        | 3.81  | 0.110 | 0.150 |  |

| Q <sub>1</sub>                              | 1.27        | 2.03  | 0.050 | 0.080 |  |

| S                                           | 1.02        | 2.03  | 0.040 | 0.080 |  |

| ECN: S-40081—Rev. A, 02-Feb-04<br>DWG: 5919 |             |       |       |       |  |

www.vishay.com Document Number: 72814 28-Jan-04

## **Legal Disclaimer Notice**

Vishay

### **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk and agree to fully indemnify and hold Vishay and its distributors harmless from and against any and all claims, liabilities, expenses and damages arising or resulting in connection with such use or sale, including attorneys fees, even if such claim alleges that Vishay or its distributor was negligent regarding the design or manufacture of the part. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

# **Material Category Policy**

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.

Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.