**Features**

# 16-Bit, RISC, Microcontroller-Based, **Ultrasonic Distance-Measuring System**

# **General Description**

The MAXQ7667 smart system-on-a-chip (SoC) provides a time-of-flight ultrasonic distance-measuring solution. The device is optimized for applications involving large distance measurement with weak input signals or multiple target identification. The MAXQ7667 features high signalto-noise ratio achieved by combining flexible electronics with the intelligence necessary to optimize each function as environmental and target conditions change.

An integrated burst signal generator and echo reception components process ultrasonic signals between 25kHz and 100kHz. Echo reception components include a programmable gain low-noise amplifier (LNA), a 16-bit sigma-delta ADC to digitize the received echo signals. and digital signal processing (DSP). DSP limits noise with a bandpass filter, and creates an echo envelope through demodulation and lowpass filtering. Input referred noise is a low 0.7µV<sub>RMS</sub>. A programmable phase-locked loop (PLL) frequency synthesizer supplies the reference frequency for the burst generator and the clock for the echo receiver's digital filter. An embedded 16-bit MAXQ20 microcontroller (µC) controls all the preceding functions.

The µC optimizes the burst frequency and reception frequency for each transmission at any temperature. The MAXQ7667 achieves smart sensing by monitoring the echo signals and then actively changing the transmitted and received parameters to obtain optimum results. Digital filtering and burst synthesis do not require CPU intervention. This leaves all the CPU power available for echo optimization, communication, diagnostics, and additional signal processing.

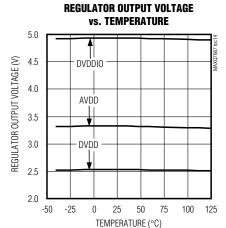

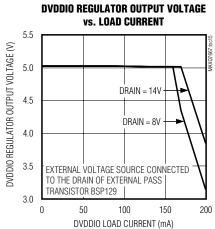

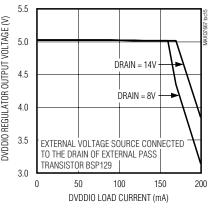

The MAXQ7667 operates with three different power supply voltages: +5V, +3.3V, and +2.5V. Two internal linear regulators allow operation from a single +5V supply when three external power supplies are not available. Alternatively, the MAXQ7667 can control an external pass transistor to allow operation from a single supply voltage of +8V to +65V or more, depending on the external component tolerance. The device is available in a 48-pin LQFP package and is specified to operate from -40°C to +125°C.

# **Applications**

Automotive Parking Vehicle Security Industrial Processing

Automation Handheld Devices **♦ Smart Analog Peripherals**

**Dedicated Ultrasonic Burst Generator** Echo Receiving Path (Includes LNA, Sigma-Delta ADC)

5-Channel, 12-Bit SAR ADC with 250ksps Sampling Rate

Internal Bandgap Voltage Reference for the **ADCs (Also Accepts External Voltage Reference)**

- ◆ Timer/Digital I/O Peripherals

- ♦ High-Performance, Low-Power, 16-Bit RISC Core

- ♦ Program and Data Memory

- ♦ Crystal/Clock Module

- ♦ 16 x 16 Hardware Multiplier with 48-Bit **Accumulator, Single Clock Cycle**

- **♦ Power-Management Module**

- **♦ JTAG Interface**

- ♦ Universal Asynchronous Receiver-Transmitter (UART)

- ◆ Local Interconnect Network (LIN)

See the Detailed Features section for complete list of features.

# **Ordering Information**

| PART            | PIN-PACKAGE | RAM<br>(KB) | FLASH<br>(KB) |

|-----------------|-------------|-------------|---------------|

| MAXQ7667AACM/V+ | 48 LQFP     | 4           | 32            |

**Note:** All devices are specified over the -40°C to +125°C operating temperature range.

/V denotes an automotive qualified part.

+Denotes a lead(Pb)-free/RoHS-compliant package.

Pin Configuration appears at end of data sheet.

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, go to: www.maxim-ic.com/errata.

Maxim Integrated Products 1

# **ABSOLUTE MAXIMUM RATINGS**

| DVDDIO, GATE5, REG3P3, REG2    | P5 to                         |

|--------------------------------|-------------------------------|

| DGND                           | 0.3V to +6.0V                 |

| AVDD to AGND                   | 0.3V to +4.0V                 |

| DVDD to DGND                   | 0.3V to +3.0V                 |

| DVDDIO to DVDD                 | 0.3V to +6.0V                 |

| AVDD to DVDD                   | 0.3V to +4.0V                 |

| AGND to DGND                   | 0.3V to +0.3V                 |

| Digital Inputs/Outputs to DGND | 0.3V to $(V_{DVDDIO} + 0.3V)$ |

| Analog Inputs/Outputs to AGND               | 0.3V to (V <sub>AVDD</sub> + 0.3V) |

|---------------------------------------------|------------------------------------|

| XIN, XOUT to DGND                           | $-0.3V$ to $(V_{DVDD} + 0.3V)$     |

| Maximum Current into Any Pin                | 50mA                               |

| Continuous Power Dissipation ( $T_A = +7$ ) | O°C)                               |

| 48-Pin LQFP (derate 21.7mW/°C abo           | ve +70°C)1739.1mW                  |

| Operating Temperature Range                 | 40°C to +125°C                     |

| Storage Temperature Range                   |                                    |

| Lead Temperature (soldering, 10s)           | +300°C                             |

|                                             |                                    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(V_{DVDDIO} = +5V, V_{AVDD} = +3.3V; V_{DVDD} = +2.5V, system clock (f_{SYSCLK}) = 16MHz, burst frequency (f_{BURST}) = bandpass frequency (f_{BPF}) = 50kHz, C_{REFBG} = C_{REF} = 1 \mu F$  in parallel with  $0.01 \mu F$ ,  $f_{ADCCLK} = 2MHz$  (SAR data rate = 125ksps),  $T_{A} = T_{MIN}$  to  $T_{MAX}$ , unless otherwise specified. Typical values are at  $T_{A} = +25^{\circ}C$ .)

| PARAMETER                            | SYMBOL          | CONDI                                        | TIONS                                           | MIN  | TYP                   | MAX | UNITS                    |  |

|--------------------------------------|-----------------|----------------------------------------------|-------------------------------------------------|------|-----------------------|-----|--------------------------|--|

| ECHO INPUT (Low-Noise Am             | plifier and S   | Sigma-Delta ADC)                             |                                                 |      |                       |     | ·                        |  |

| Input-Referred Noise                 |                 | VGA gain adjust = 1.55µV <sub>P-P</sub> /LSB |                                                 | 5.6  |                       |     |                          |  |

| (Note 1)                             |                 | VGA gain adjust = 0                          | O.1µV <sub>P-P</sub> /LSB                       |      | 0.7                   |     | μVRMS                    |  |

| Minimum Datastahla Cismal            |                 | VGA gain adjust =                            | 1.55µV <sub>P-P</sub> /LSB                      |      | 80                    |     | \/                       |  |

| Minimum Detectable Signal            |                 | VGA gain adjust = 0                          | 0.1µV <sub>P-P</sub> /LSB                       |      | 10                    |     | – μV <sub>P-P</sub>      |  |

| Operating Input Range                |                 | VGA gain adjust = unclipped                  | 1.55µV <sub>P-P</sub> /LSB,                     |      | 100                   |     | mV <sub>P-P</sub>        |  |

| Operating input hange                |                 | VGA gain adjust = 0<br>unclipped             | D.1μV <sub>P-P</sub> /LSB,                      |      | 6.7                   |     | J 11144-h                |  |

| Draguementala Caia                   |                 | From echo input to                           | VGA gain adjust<br>= 1.55µV <sub>P-P</sub> /LSB | 1.55 |                       |     | U/D D/I CD               |  |

| Programmable Gain                    |                 | bandpass filter in reply to input            | VGA gain adjust<br>= 0.1µV <sub>P-P</sub> /LSB  |      | 0.1                   |     | – μV <sub>P-P</sub> /LSB |  |

| Programmable-Gain Adjust Resolution  |                 | (Note 2)                                     |                                                 |      | 10                    |     | %                        |  |

| LNA Bandwidth                        |                 |                                              |                                                 |      | 150                   |     | kHz                      |  |

| ADC Sampling Rate                    |                 |                                              |                                                 |      | 80 x f <sub>BPF</sub> |     | kHz                      |  |

| ADC Output Data Rate                 |                 |                                              |                                                 |      | 10 x f <sub>BPF</sub> |     | kHz                      |  |

| ADC Output Data Resolution           |                 |                                              |                                                 |      | 16                    |     | Bits                     |  |

| Echo-Input Resistance                | R <sub>IN</sub> | For each echo inpu                           | t                                               |      | 14                    |     | kΩ                       |  |

| Echo-Input Capacitance               |                 |                                              |                                                 |      | 14                    |     | pF                       |  |

| Echo-Input DC Bias Voltage           |                 |                                              |                                                 |      | V <sub>AVDD</sub> /2  |     | V                        |  |

| Maximum Overvoltage<br>Recovery Time |                 | Recover from 2V <sub>P-P</sub>               | input                                           |      | 10                    |     | μs                       |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DVDDIO} = +5V, V_{AVDD} = +3.3V; V_{DVDD} = +2.5V, system clock (f_{SYSCLK}) = 16MHz, burst frequency (f_{BURST}) = bandpass frequency (f_{BPF}) = 50kHz, C_{REFBG} = C_{REF} = 1\mu F in parallel with 0.01\mu F, f_{ADCCLK} = 2MHz (SAR data rate = 125ksps), T_A = T_{MIN} to T_{MAX}, unless otherwise specified. Typical values are at T_A = +25°C.)$

| PARAMETER                             | SYMBOL  | CONDITIONS                             | MIN                  | TYP                     | MAX                  | UNITS             |

|---------------------------------------|---------|----------------------------------------|----------------------|-------------------------|----------------------|-------------------|

| BANDPASS FILTER                       | •       |                                        | ·                    |                         |                      | '                 |

| Center Frequency                      | fBPF    |                                        | 25                   |                         | 100                  | kHz               |

| Passband Width                        |         | -3dB                                   |                      | 0.14 x f <sub>BPF</sub> |                      | kHz               |

| Minimum Stopband<br>Rejection         |         | One decade away from center frequency  |                      | -60                     |                      | dB                |

| Output Data Rate                      |         |                                        |                      | 10 x f <sub>BPF</sub>   |                      | ksps              |

| Output Data Resolution                |         |                                        |                      | 16                      |                      | Bits              |

| LOWPASS FILTER                        |         |                                        |                      |                         |                      |                   |

| Corner Frequency                      | fLPF    | -3dB                                   |                      | 0.1 x f <sub>BPF</sub>  |                      | kHz               |

| Rolloff                               |         |                                        |                      | 40                      |                      | dB/Decade         |

| Output Data Rate                      |         |                                        |                      | 5 x f <sub>BPF</sub>    |                      | ksps              |

| Output Data Resolution                |         |                                        |                      | 16                      |                      | Bits              |

| SAR ADC                               | 1       |                                        | <b>'</b>             |                         |                      | •                 |

| Danakatan                             |         | Measurement                            | 12                   |                         |                      | D:4-              |

| Resolution                            |         | No missing codes                       | 11                   |                         |                      | Bits              |

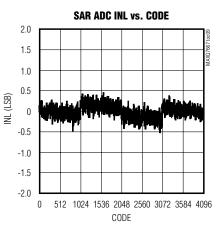

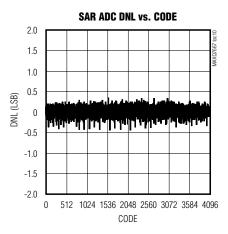

| Integral Nonlinearity                 |         | Tested at 125ksps                      |                      | ±1                      | ±2                   | LSB               |

| Differential Nonlinearity             |         | Tested at 125ksps                      | -2                   |                         | +2                   | LSB               |

| Offset Error                          |         |                                        |                      | ±1                      | ±3                   | mV                |

| Offset-Error Drift                    |         |                                        |                      | ±5                      |                      | μV/°C             |

| Gain Error                            |         |                                        |                      |                         | ±1                   | %                 |

| Gain-Error Temperature<br>Coefficient |         |                                        |                      | ±0.4                    |                      | ppmFS/°C          |

| Input-Referred Noise                  |         | At ADC inputs                          |                      | 400                     |                      | μV <sub>RMS</sub> |

| Differential Invest December          |         | Unipolar                               | 0                    |                         | V <sub>REF</sub>     | \/                |

| Differential Input Range              |         | Bipolar                                | -V <sub>REF</sub> /2 |                         | +V <sub>REF</sub> /2 | V                 |

| Absolute Input Range                  |         |                                        | 0                    |                         | Vavdd                | V                 |

| Input Leakage Current                 |         |                                        |                      | ±0.1                    |                      | μΑ                |

| Conversion Time                       |         | 13 ADCCLK cycles at 2MHz               |                      |                         | 6.5                  | μs                |

| Input Capacitance                     |         |                                        |                      | 14                      |                      | pF                |

| Track-and-Hold Acquisition<br>Time    |         | Three ADCCLK cycles at 2MHz            |                      |                         | 1.5                  | μs                |

| Turn-On Time                          |         | Eight ADCCLK cycles at 2MHz            |                      |                         | 4                    | μs                |

| Conversion Clock                      | fADCCLK |                                        | 0.5                  |                         | 4                    | MHz               |

| Conversion Rate                       |         | fADCCLK = 4MHz (not production tested) |                      |                         | 250                  | ksps              |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DVDDIO} = +5V, V_{AVDD} = +3.3V; V_{DVDD} = +2.5V, system clock (f_{SYSCLK}) = 16MHz, burst frequency (f_{BURST}) = bandpass frequency (f_{BPF}) = 50kHz, C_{REFBG} = C_{REF} = 1\mu F in parallel with 0.01\mu F, f_{ADCCLK} = 2MHz (SAR data rate = 125ksps), T_A = T_{MIN} to T_{MAX}, unless otherwise specified. Typical values are at T_A = +25°C.)$

| PARAMETER                          | SYMBOL     | CONDITIONS                                                                     | MIN                        | TYP  | MAX                        | UNITS             |

|------------------------------------|------------|--------------------------------------------------------------------------------|----------------------------|------|----------------------------|-------------------|

| REFERENCE BUFFER                   |            |                                                                                |                            |      |                            |                   |

| Offset                             |            |                                                                                |                            | 5    |                            | mV                |

| Minimum Load                       |            |                                                                                | 2.5                        |      |                            | kΩ                |

| Output Bypass Capacitor            |            |                                                                                |                            | 0.47 |                            | μF                |

| EXTERNAL VOLTAGE REFE              | RENCE (Re  | ference Buffer Disabled)                                                       |                            |      |                            |                   |

| Reference Input Range              |            | Applied at REF                                                                 | 1.0                        |      | V <sub>AVDD</sub>          | V                 |

| Reference Input Impedance          |            | Measured at REF with the SAR and sigma-delta ADCs running at maximum frequency |                            | 50   |                            | kΩ                |

| INTERNAL VOLTAGE REFER             | RENCE (REI | FBG)                                                                           |                            |      |                            |                   |

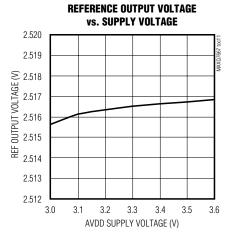

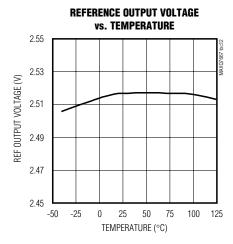

| Initial Accuracy                   |            |                                                                                | 2.45                       | 2.5  | 2.55                       | V                 |

| Maximum Temperature<br>Coefficient |            |                                                                                |                            | 100  |                            | ppm/°C            |

| Output Impedance                   |            |                                                                                |                            | 1.1  |                            | kΩ                |

| Power-Supply Rejection Ratio       |            | V <sub>AVDD</sub> = 3.0V to 3.6V                                               |                            | 60   |                            | dB                |

| Output Noise                       |            |                                                                                |                            | 0.5  |                            | mV <sub>RMS</sub> |

| PROGRAMMABLE BURST-F               | REQUENCY   | OSCILLATOR                                                                     |                            |      |                            | •                 |

| Burst-Frequency Range              |            |                                                                                | 0.025                      |      | 1.335                      | MHz               |

| Burst-Frequency Resolution         |            |                                                                                |                            | 0.1  |                            | %                 |

| Burst-Frequency Locking            |            | Change from 40kHz to 60kHz                                                     |                            | 5    |                            |                   |

| Time                               |            | Change from 50kHz to 50.5kHz                                                   |                            | 2    |                            | ms                |

| CRYSTAL OSCILLATOR                 |            |                                                                                |                            |      |                            |                   |

|                                    |            | Tested crystal frequency                                                       |                            | 16   |                            |                   |

| Frequency Range                    |            | Minimum crystal frequency                                                      |                            | 4    |                            | MHz               |

|                                    |            | External clock input                                                           | 4                          |      | 16                         |                   |

| Temperature Stability              |            | Excluding crystal                                                              |                            | 25   |                            | ppm/°C            |

| Startup Time                       |            | 16MHz crystal                                                                  |                            | 10   |                            | ms                |

| XIN Input Low Voltage              |            | When driven with external clock source                                         |                            |      | 0.3 x<br>V <sub>DVDD</sub> | V                 |

| XIN Input High Voltage             |            | When driven with external clock source                                         | 0.7 x<br>V <sub>DVDD</sub> |      |                            | V                 |

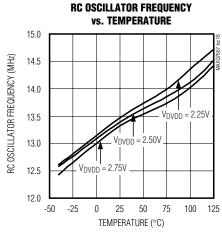

| INTERNAL RC OSCILLATOR             |            |                                                                                |                            |      |                            |                   |

| Frequency                          |            |                                                                                |                            | 13.5 |                            | MHz               |

| Initial Accuracy                   |            |                                                                                |                            | 10.5 |                            | %                 |

| Temperature Drift                  |            | TA = T <sub>MIN</sub> to T <sub>MAX</sub>                                      |                            | 700  |                            | ppm               |

| Supply Rejection                   |            | V <sub>DVDD</sub> = 2.25V to 2.75V                                             |                            | -1.5 |                            | %                 |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DVDDIO} = +5V, V_{AVDD} = +3.3V; V_{DVDD} = +2.5V, system clock (f_{SYSCLK}) = 16MHz, burst frequency (f_{BURST}) = bandpass frequency (f_{BPF}) = 50kHz, C_{REFBG} = C_{REF} = 1 \mu F in parallel with 0.01 \mu F, f_{ADCCLK} = 2MHz (SAR data rate = 125ksps), T_A = T_{MIN} to T_{MAX}, unless otherwise specified. Typical values are at T_A = +25°C.)$

| PARAMETER                                              | SYMBOL    | CONDITIONS                                                                                    | MIN                          | TYP        | MAX     | UNITS |

|--------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------|------------------------------|------------|---------|-------|

| Adjustable Frequency Range                             |           | Using the RCTRM register                                                                      | -40                          |            | +40     | %     |

| Frequency Adjustment<br>Resolution                     |           |                                                                                               |                              | 0.2        |         | %     |

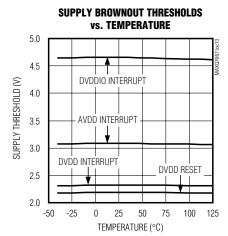

| SUPPLY VOLTAGE SUPERV                                  | ISORS     |                                                                                               |                              |            |         |       |

| DVDD Reset Threshold                                   |           | Asserts RESET if V <sub>DVDD</sub> falls below this threshold                                 | 2.10                         |            | 2.25    | V     |

| DVDD Interrupt Threshold                               |           | Generates an interrupt if V <sub>DVDD</sub> falls below this threshold                        | 2.25                         |            | 2.38    | V     |

| Minimum Reset and Interrupt<br>Threshold Difference    |           |                                                                                               | 150                          |            |         | mV    |

| AVDD Interrupt Threshold                               |           | Generates an interrupt if V <sub>AVDD</sub> falls below this threshold                        | 2.95                         |            | 3.15    | V     |

| DVDDIO Interrupt Threshold                             |           | Generates an interrupt if V <sub>DVDDIO</sub> falls below this threshold                      | 4.5                          |            | 4.75    | V     |

| Supervisor Operating Range                             |           | At DVDD                                                                                       | 1.5                          |            | 2.75    | V     |

| Supervisor Hysteresis                                  |           |                                                                                               |                              | 1          |         | %     |

| RESET Release Delay                                    |           | After V <sub>DVDD</sub> rises above the reset threshold                                       |                              | 35         |         | μs    |

| Power-Up Time                                          |           | Time from RESET is released to the execution of the first instruction (serial bootloader off) |                              | 1          |         | μs    |

| +5V LINEAR REGULATOR (C<br>Circuit/Functional Diagram) | VDDIO, GA | TE5, Requires External Pass Transisto                                                         | or, see the Ty               | pical Appl | ication |       |

| Regulator Output Voltage                               |           | At DVDDIO                                                                                     | 4.75                         |            | 5.25    | V     |

| GATE5 Output High Voltage                              |           | ISOURCE = 0µA (no load)                                                                       | V <sub>DVDDIO</sub><br>- 0.1 |            |         | V     |

| GATE5 Output Low Voltage                               |           | ISINK = 500µA                                                                                 |                              |            | 2       | V     |

| GATE5 Output Resistance                                |           | ISINK = 0µA to 50µA                                                                           |                              | 330        |         | Ω     |

| Gain Bandwidth                                         |           | DVDDIO to GATE5                                                                               |                              | 1.58       |         | kHz   |

| Gain                                                   |           | DVDDIO to GATE5                                                                               |                              | 1700       |         | V/V   |

| GATE5 Slew Rate                                        |           |                                                                                               |                              | 4.3        |         | V/ms  |

| Maximum Load Capacitance                               |           | Maximum capacitance on DVDDIO when using an external pass transistor                          |                              | 1          |         | μF    |

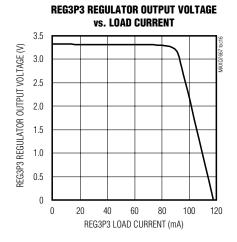

| +3.3V LINEAR REGULATOR                                 | (REG3P3)  |                                                                                               |                              |            |         |       |

| REG3P3 Output Voltage                                  |           |                                                                                               | 3.15                         |            | 3.45    | V     |

| Load Current                                           |           |                                                                                               |                              |            | 50      | mA    |

| Output Short-Circuit Current                           | _         | REG3P3 shorted to AGND                                                                        |                              | 150        |         | mA    |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DVDDIO} = +5V, V_{AVDD} = +3.3V; V_{DVDD} = +2.5V, system clock (f_{SYSCLK}) = 16MHz, burst frequency (f_{BURST}) = bandpass frequency (f_{BPF}) = 50kHz, C_{REFBG} = C_{REF} = 1 \mu F in parallel with 0.01 \mu F, f_{ADCCLK} = 2MHz (SAR data rate = 125ksps), T_A = T_{MIN} to T_{MAX}, unless otherwise specified. Typical values are at T_A = +25°C.)$

| PARAMETER                    | SYMBOL      | co                                                             | NDITIONS                                        | MIN                 | TYP   | MAX  | UNITS |

|------------------------------|-------------|----------------------------------------------------------------|-------------------------------------------------|---------------------|-------|------|-------|

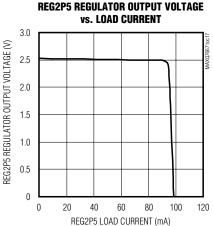

| +2.5V LINEAR REGULATOR (     | REG2P5)     |                                                                |                                                 |                     |       |      |       |

| REG2P5 Output Voltage        |             |                                                                |                                                 | 2.38                |       | 2.62 | V     |

| Load Current                 |             |                                                                |                                                 |                     |       | 50   | mA    |

| Output Short-Circuit Current |             | REG2P5 shorted                                                 | d to DGND                                       |                     | 100   |      | mA    |

| POWER REQUIREMENTS           |             |                                                                |                                                 |                     |       |      |       |

|                              |             | DVDD                                                           |                                                 | 2.25                | 2.5   | 2.75 |       |

| Supply Voltage Range         |             | AVDD                                                           |                                                 | 3.00                | 3.3   | 3.6  | V     |

|                              |             | DVDDIO                                                         |                                                 | 4.5                 | 5.0   | 5.5  |       |

|                              |             | All analog funct                                               | tions enabled                                   |                     | 12    | 18   | mA    |

|                              |             | All analog funct                                               | tions disabled                                  |                     | 3     | 10   | μΑ    |

|                              |             |                                                                | LNA                                             |                     | 2.4   |      | m 1   |

|                              |             |                                                                | Sigma-delta ADC                                 |                     | 12    |      | mA mA |

|                              |             |                                                                | SAR ADC, 250ksps,<br>f <sub>ADCCLK</sub> = 4MHz |                     | 600   |      |       |

| A) (DD 0                     |             | PLL                                                            |                                                 | 300                 |       |      |       |

| AVDD Supply Current          |             | Incremental<br>AVDD supply<br>current                          | Supply voltage supervisors                      |                     | 3     |      | μΑ    |

|                              |             |                                                                | Internal voltage reference                      |                     | 220   |      |       |

|                              |             |                                                                | Reference buffer                                |                     | 300   |      |       |

|                              |             | Bias (any AVDD module enabled)                                 |                                                 | 1.5                 |       | mA   |       |

| DVDD Supply Current          |             |                                                                |                                                 |                     | 11    |      | mA    |

| DVDDIO Supply Current        |             |                                                                |                                                 |                     | 2.5   |      | mA    |

| DIGITAL INPUTS (GPIO, UART   | Γ, JTAG, SI | PI™)                                                           |                                                 |                     |       |      |       |

| Input High Voltage           |             |                                                                |                                                 | V <sub>DVDDIO</sub> |       |      | V     |

| Input Low Voltage            |             |                                                                |                                                 |                     |       | 0.8  | V     |

| Input Hysteresis             |             | V <sub>D</sub> VDDIO = 5.0V                                    | ,                                               |                     | 500   |      | mV    |

| Input Leakage Current        |             | Digital input vol<br>DVDDIO, pullup                            | Itage = DGND or disabled                        |                     | ±0.01 | ±1   | μΑ    |

| Pullup/Pulldown Resistance   |             | Pulled up to DVDDIO internally, pulled down to DGND internally |                                                 |                     | 150   |      | kΩ    |

| Input Capacitance            |             |                                                                |                                                 |                     | 15    |      | pF    |

SPI is a trademark of Motorola, Inc.

6 \_\_\_\_\_\_ /VI/XI/M

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DVDDIO} = +5V, V_{AVDD} = +3.3V; V_{DVDD} = +2.5V, system clock (f_{SYSCLK}) = 16MHz, burst frequency (f_{BURST}) = bandpass frequency (f_{BPF}) = 50kHz, C_{REFBG} = C_{REF} = 1 \mu F in parallel with 0.01 \mu F, f_{ADCCLK} = 2MHz (SAR data rate = 125ksps), T_A = T_{MIN} to T_{MAX}, unless otherwise specified. Typical values are at T_A = +25°C.)$

| PARAMETER                  | SYMBOL     | CONDITIONS                                       | MIN                        | TYP   | MAX  | UNITS |

|----------------------------|------------|--------------------------------------------------|----------------------------|-------|------|-------|

| DIGITAL OUTPUTS (GPIO, U   | ART, JTAG, | SPI)                                             |                            |       |      | •     |

| Output Low Voltage         |            | I <sub>SINK</sub> = 0.5mA, drive strength = low  |                            |       | 0.4  | V     |

| Output Low voltage         |            | I <sub>SINK</sub> = 1.0mA, drive strength = high |                            |       | 0.4  | V     |

| Outsout High Walks are     |            | ISOURCE = 0.5mA,<br>drive strength = low         | V <sub>D</sub> VDDIO - 0.5 |       |      | V     |

| Output High Voltage        |            | ISOURCE = 1.0mA,<br>drive strength = high        | V <sub>D</sub> VDDIO - 0.5 |       |      | V     |

| Maximum Output             |            | Drive strength = low                             |                            | 880   |      | Ω     |

| Impedance                  |            | Drive strength = high                            |                            | 450   |      | 1 12  |

| Three-State Leakage        |            |                                                  |                            | ±0.01 | ±1   | μΑ    |

| Three-State Capacitance    |            |                                                  |                            | 15    |      | pF    |

| BURST OUTPUT               |            |                                                  |                            |       |      |       |

| Output Low Voltage         |            | I <sub>SINK</sub> = 8mA                          |                            |       | 0.4  | V     |

| Output High Voltage        |            | ISOURCE = 8mA                                    | V <sub>D</sub> VDDIO - 0.5 |       |      | V     |

| Maximum Output             |            | Drive strength = low                             |                            | 90    |      | 0     |

| Impedance                  |            | Drive strength = high                            |                            | 45    |      | Ω     |

| Three-State Leakage        |            |                                                  |                            | ±0.01 | ±1   | μΑ    |

| Three-State Capacitance    |            |                                                  |                            | 15    |      | pF    |

| Short-Circuit Current      |            | Burst drive set to high                          |                            | 50    |      | mA    |

| RESET                      |            |                                                  |                            |       |      |       |

| Internal Pullup Resistance |            | Pulled up to DVDDIO                              |                            | 120   |      | kΩ    |

| Output Low Voltage         |            | I <sub>SINK</sub> = 0.5mA                        |                            |       | 0.4  | V     |

| Output High Voltage        |            | No external load                                 | V <sub>D</sub> VDDIO - 0.5 |       |      | V     |

| Input Low Voltage          |            | When driven by external source                   |                            |       | 0.8  | V     |

| Input High Voltage         |            | When driven by external source                   | V <sub>D</sub> VDDIO -     |       |      | V     |

| UART/LIN INTERFACE (UTX    | , URX)     |                                                  | 1                          |       |      | ı     |

| ,                          |            | Asynchronous mode (system clock/32)              |                            |       | 500  |       |

| UART Baud Rates            |            | Synchronous mode (system clock/8)                |                            |       | 2000 | kbps  |

|                            |            | LIN 2.0 compatibility (Note 3)                   | 1                          |       | 20   |       |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DVDDIO} = +5V, V_{AVDD} = +3.3V; V_{DVDD} = +2.5V, system clock (f_{SYSCLK}) = 16MHz, burst frequency (f_{BURST}) = bandpass frequency (f_{BPF}) = 50kHz, C_{REFBG} = C_{REF} = 1\mu F in parallel with 0.01\mu F, f_{ADCCLK} = 2MHz (SAR data rate = 125ksps), T_A = T_{MIN} to T_{MAX}, unless otherwise specified. Typical values are at T_A = +25°C.)$

| PARAMETER                                             | SYMBOL             | CONDITIONS                      | MIN                         | TYP    | MAX | UNITS  |

|-------------------------------------------------------|--------------------|---------------------------------|-----------------------------|--------|-----|--------|

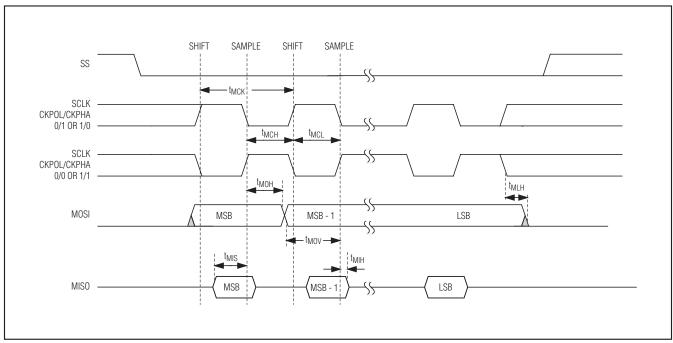

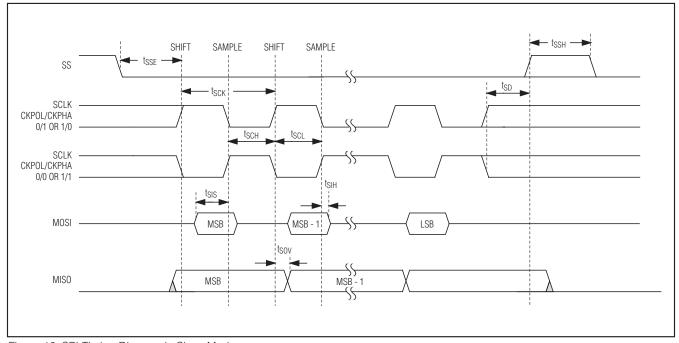

| SPI INTERFACE TIMING (Fig                             | ures 11 and        | i 12)                           |                             |        |     |        |

| SPI Master Operating<br>Frequency                     | 1/t <sub>MCK</sub> | 0.5 x fsysclk                   |                             |        | 8   | MHz    |

| SPI Slave Operating<br>Frequency                      | 1/t <sub>SCK</sub> | 0.25 x fsysclk                  |                             |        | 4   | MHz    |

| SCLK Output Pulse-Width<br>High/Low                   | tMCH,<br>tMCL      |                                 | t <sub>MCK</sub> /2<br>- 25 |        |     | ns     |

| MOSI Output Hold Time<br>After SCLK Sample Edge       | tмон               |                                 | t <sub>MCK</sub> /2<br>- 25 |        |     | ns     |

| MOSI Output Valid to Sample Edge                      | t <sub>MOV</sub>   |                                 | t <sub>MCK</sub> /2<br>- 25 |        |     | ns     |

| MISO Input Valid to SCLK<br>Sample Edge               | tMIS               |                                 | 25                          |        |     | ns     |

| MISO Input Hold Time After<br>SCLK Sample Edge        | tMIH               |                                 | 0                           |        |     | ns     |

| SCLK Inactive to MOSI Inactive                        | t <sub>MLH</sub>   |                                 | 0                           |        |     | ns     |

| SCLK Input Pulse-Width<br>High/Low                    | tsch,<br>tscl      |                                 |                             | tsck/2 |     | ns     |

| SS Active to First Shift Edge                         | tsse               |                                 | 4tsysclk                    |        |     | ns     |

| MOSI Input Setup Time to<br>SCLK Sample Edge          | tsis               |                                 | 25                          |        |     | ns     |

| MOSI Input Hold Time After<br>SCLK Sample Edge        | tsih               |                                 | 25                          |        |     | ns     |

| MISO Output Valid After<br>SCLK Shift Edge Transition | tsov               |                                 |                             |        | 50  | ns     |

| SS Inactive Duration                                  | <sup>t</sup> SSH   |                                 | tsysclk + 25                |        |     | ns     |

| SCLK Inactive to SS Rising Edge                       | tsD                |                                 | tsysclk + 25                |        |     | ns     |

| FLASH PROGRAMMING                                     |                    |                                 |                             |        |     |        |

| Flash Erase Time                                      |                    | Mass erase                      | 200                         |        |     | ms     |

|                                                       |                    | Page erase (512 bytes per page) | 20                          |        |     | 1110   |

| Flash Programming Time                                |                    | 20µs per word                   | 657                         |        |     | ms     |

| Write/Erase Cycles                                    |                    |                                 | 10,000                      |        |     | Cycles |

| Data Retention                                        |                    | Average temperature = +85°C     | 15                          |        |     | Years  |

Note 1: Noise measured at bandpass filter output with ECHO+ and ECHO- shorted divided by the gain with fBPF = 50kHz.

Note 2: Gain adjust resolution typically ranges between 6.25% and 12.5%.

Note 3: LIN 2.0 specifies a maximim data rate of 20kbps. Higher data rates could be possible with compatible devices and suitable line conditions.

\_\_\_\_ /N/XI/N

# Typical Operating Characteristics

$(V_{DVDDIO} = +5V, V_{AVDD} = +3.3V, V_{DVDD} = +2.5V, f_{SYSCLK} = 16MHz, burst frequency = bandpass frequency = 50kHz, T_A = +25°C, unless otherwise noted.)$

# BANDPASS FILTER OUTPUT NOISE FLOOR vs. BANDPASS FILTER CENTER FREQUENCY

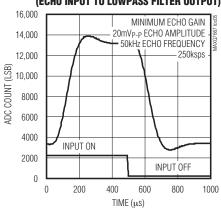

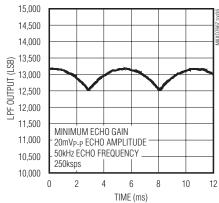

## **LOWPASS FILTER OUTPUT RIPPLE vs. TIME**

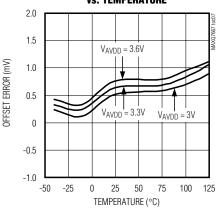

# SAR ADC OFFSET ERROR vs. Temperature

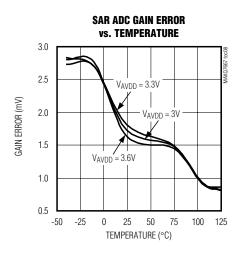

# Typical Operating Characteristics (continued)

$(V_{DVDDIO} = +5V, V_{AVDD} = +3.3V, V_{DVDD} = +2.5V, f_{SYSCLK} = 16MHz, burst frequency = bandpass frequency = 50kHz, T_A = +25°C, unless otherwise noted.)$

# Typical Operating Characteristics (continued)

$(V_{DVDDIO} = +5V, V_{AVDD} = +3.3V, V_{DVDD} = +2.5V, f_{SYSCLK} = 16MHz, burst frequency = bandpass frequency = 50kHz, T_A = +25^{\circ}C, t_{AVDD} = +3.3V, t_{AVDD} = +3.3V, t_{AVDD} = +2.5V, t_{AVDD} = +2.5V,$ unless otherwise noted.)

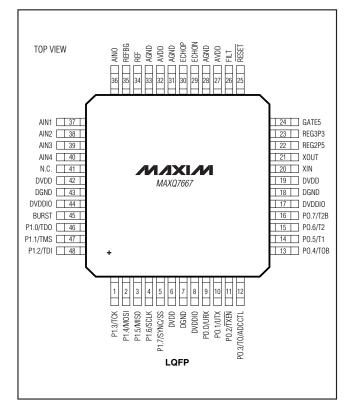

# **Pin Description**

| PIN       | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                                                             |

|-----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

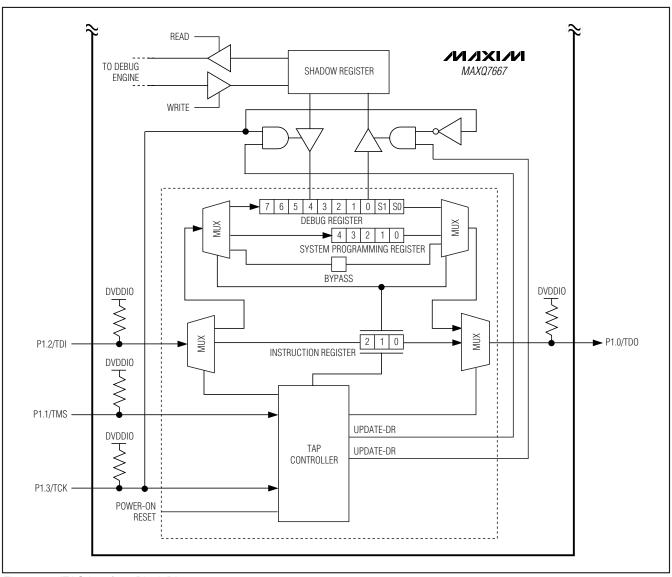

| 1         | P1.3/TCK           | Port 1 Data 3/JTAG Serial Clock Input. P1.3 is a general-purpose digital I/O. TCK is the JTAG serial test clock input. Refer to the MAXQ7667 User's Guide Sections 5 and 11.                                                                                                                                                                         |

| 2         | P1.4/MOSI          | Port 1 Data 4/SPI Serial Data Output. P1.4 is a general-purpose digital I/O. MOSI is the master output, slave input for the SPI interface. Refer to the MAXQ7667 User's Guide Sections 5 and 9.                                                                                                                                                      |

| 3         | P1.5/MISO          | Port 1 Data 5/SPI Serial Data Input. P1.5 is a general-purpose digital I/O. MISO is the master input, slave output for the SPI interface. Refer to the MAXQ7667 User's Guide Sections 5 and 9.                                                                                                                                                       |

| 4         | P1.6/SCLK          | Port 1 Data 6/SPI Serial Clock Output. P1.6 is a general-purpose digital I/O. SCLK is the serial clock for the SPI interface. SCLK is an input when operating as a slave and an output when operating as a master. Refer to the MAXQ7667 User's Guide Sections 5 and 9.                                                                              |

| 5         | P1.7/SYNC/SS       | Port 1 Data 7/Schedule Timer Sync Input/SPI Slave Select. P1.7 is a general-purpose digital I/O. A rising edge on the SYNC input resets the schedule timer. In SPI slave mode, SS is the SPI slave-select input. In SPI master mode, use SS or a GPIO to manually select an external slave. Refer to the MAXQ7667 User's Guide Sections 5, 7, and 9. |

| 6, 19, 42 | DVDD               | Digital Supply Voltage. Connect DVDD directly to a +2.5V external source or to REG2P5 output for single supply operation. Bypass DVDD to DGND with a 0.1µF capacitor as close as possible to the device. Connect all DVDD nodes together.                                                                                                            |

| 7, 18, 43 | DGND               | Digital Ground. Connect all DGND nodes together. Connect to AGND at a single point.                                                                                                                                                                                                                                                                  |

| 8, 17, 44 | DVDDIO             | Digital I/O Supply Voltage. DVDDIO powers all digital I/Os except for XIN and XOUT. Bypass DVDDIO to DGND with a 0.1µF capacitor as close as possible to the device. Connect all DVDDIO nodes together.                                                                                                                                              |

| 9         | P0.0/URX           | Port 0 Data 0/UART Receive Data Input. P0.0 is a general-purpose digital I/O. URX is a UART or LIN data receive input. Refer to the MAXQ7667 User's Guide Sections 5 and 8.                                                                                                                                                                          |

| 10        | P0.1/UTX           | Port 0 Data 1/UART Transmit Data Output. P0.1 is a general-purpose digital I/O. UTX is a UART or LIN data transmit output. Refer to the <i>MAXQ7667 User's Guide</i> Sections 5 and 8.                                                                                                                                                               |

| 11        | P0.2/TXEN          | Port 0 Data 2/UART Transmit Output. P0.2 is a general-purpose digital I/O. TXEN asserts low when the UART is transmitting. Use TXEN to enable an external LIN/UART transceiver. Refer to the MAXQ7667 User's Guide Sections 5 and 8.                                                                                                                 |

| 12        | P0.3/T0/<br>ADCCTL | Port 0 Data 3/Timer 0 I/O/ADC Control Input. P0.3 is a general-purpose digital I/O. T0 is the primary Type 2 timer/counter 0 output or input. ADCCTL is a sampling/conversion trigger input for the SAR ADC. Refer to the MAXQ7667 User's Guide Sections 5, 6, and 14.                                                                               |

| 13        | P0.4/T0B           | Port 0 Data 4/Timer 0B I/O/Comparator Output. P0.4 is a general-purpose digital I/O. T0B is the secondary Type 2 timer/counter 0 output or input. Refer to the <i>MAXQ7667 User's Guide</i> Sections 5 and 6.                                                                                                                                        |

| 14        | P0.5/T1            | Port 0 Data 5/Timer 1 I/O. P0.5 is a general-purpose digital I/O. T1 is the primary Type 2 timer/counter 1 output or input. Refer to the MAXQ7667 User's Guide Sections 5 and 6.                                                                                                                                                                     |

| 15        | P0.6/T2            | Port 0 Data 6/Timer 2 I/O. P0.6 is a general-purpose digital I/O. T2 is the primary Type 2 timer/counter 2 output or input. Refer to the MAXQ7667 User's Guide Sections 5 and 6.                                                                                                                                                                     |

| 16        | P0.7/T2B           | Port 0 Data 7/Timer 2B I/O. P0.7 is a general-purpose digital I/O. T2B is the secondary Type 2 timer/counter 2 output or input. Refer to the MAXQ7667 User's Guide Sections 5 and 6.                                                                                                                                                                 |

| 20        | XIN                | Crystal Oscillator Input. Connect an external crystal or resonator between XIN and XOUT. When using an external clock source drive XIN with 2.5V level clock while leaving XOUT unconnected. Connect XIN to DGND when an external clock source is not used.                                                                                          |

# Pin Description (continued)

| DIN        | NABAT    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN        | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 21         | XOUT     | Crystal Oscillator Output. Connect an external crystal or resonator between XIN and XOUT. Leave XOUT unconnected when driving XIN with a 2.5V level clock or when an external clock source is not used.                                                                                                                                                                                                                            |

| 22         | REG2P5   | +2.5V Voltage Regulator Output                                                                                                                                                                                                                                                                                                                                                                                                     |

| 23         | REG3P3   | +3.3V Voltage Regulator Output                                                                                                                                                                                                                                                                                                                                                                                                     |

| 24         | GATE5    | +5V DVDDIO Voltage Regulator Control Output. GATE5 controls an external npn or nMOS transistor that passes power to DVDDIO.                                                                                                                                                                                                                                                                                                        |

| 25         | RESET    | Reset Input/Output. RESET is open drain with an internal pullup resistor to DVDDIO. Internal circuitry pulls RESET low when VDVDDIO falls below its brownout reset value or watchdog reset is enabled and the watchdog timeout period expires. Force RESET low externally for manual reset.                                                                                                                                        |

| 26         | FILT     | PLL VCO Control Input. Connect external filter components on FILT for the internal PLL circuit. See the <i>Typical Application Circuit/Functional Diagram</i> .                                                                                                                                                                                                                                                                    |

| 27, 32     | AVDD     | Analog Supply Voltage. Connect all AVDD inputs directly to a +3.3V source or to REG3P3 for self-powered operation. Bypass each AVDD to AGND with a 0.1µF capacitor as close as possible to the device.                                                                                                                                                                                                                             |

| 28, 31, 33 | AGND     | Analog Ground. Connect all AGND nodes together. Connect to DGND at a single point.                                                                                                                                                                                                                                                                                                                                                 |

| 29         | ECHON    | Negative Echo Input. AC-couple ECHON to an ultrasonic transducer.                                                                                                                                                                                                                                                                                                                                                                  |

| 30         | ECHOP    | Positive Echo Input. AC-couple ECHOP to an ultrasonic transducer.                                                                                                                                                                                                                                                                                                                                                                  |

| 34         | REF      | ADC Reference Input/Reference Buffer Output. When using the internal reference, the buffered bandgap reference voltage (V <sub>REF</sub> ) is provided for both SAR and sigma-delta ADCs. When using an external reference, apply an external voltage source ranging between 1V and V <sub>AVDD</sub> at REF. Disable the reference buffer when applying an external reference at REF. Bypass REF to AGND with a 0.47µF capacitor. |

| 35         | REFBG    | +2.5V Reference Output/Reference Buffer Input. Bypass to AGND with a 0.47µF capacitor.                                                                                                                                                                                                                                                                                                                                             |

| 36         | AIN0     | SAR ADC Input 0. AIN0 pairs with AIN1 in differential mode.                                                                                                                                                                                                                                                                                                                                                                        |

| 37         | AIN1     | SAR ADC Input 1. AIN1 pairs with AIN0 in differential mode.                                                                                                                                                                                                                                                                                                                                                                        |

| 38         | AIN2     | SAR ADC Input 2. AIN2 pairs with AIN3 in differential mode.                                                                                                                                                                                                                                                                                                                                                                        |

| 49         | AIN3     | SAR ADC Input 3. AIN3 pairs with AIN2 in differential mode.                                                                                                                                                                                                                                                                                                                                                                        |

| 40         | AIN4     | SAR ADC Input 4                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 41         | N.C.     | No Connection. Internally connected. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                            |

| 45         | BURST    | Burst Output. Burst is the ultrasonic transducer excitation pulse output. BURST remains in three-state mode on power-up.                                                                                                                                                                                                                                                                                                           |

| 46         | P1.0/TDO | Port 1 Data 0/JTAG Output. P1.0 is a general-purpose digital I/O. TDO is the JTAG serial data output. Refer to the MAXQ7667 User's Guide Sections 5 and 11.                                                                                                                                                                                                                                                                        |

| 47         | P1.1/TMS | Port 1 Data 1/JTAG Test Mode-Select Input. P1.1 is a general-purpose digital I/O. TMS is the JTAG mode-select input. Refer to the MAXQ7667 User's Guide Sections 5 and 11.                                                                                                                                                                                                                                                         |

| 48         | P1.2/TDI | Port 1 Data 2/JTAG Input. P1.2 is a general-purpose digital I/O. TDI is the JTAG serial data input. Refer to the MAXQ7667 User's Guide Sections 5 and 11.                                                                                                                                                                                                                                                                          |

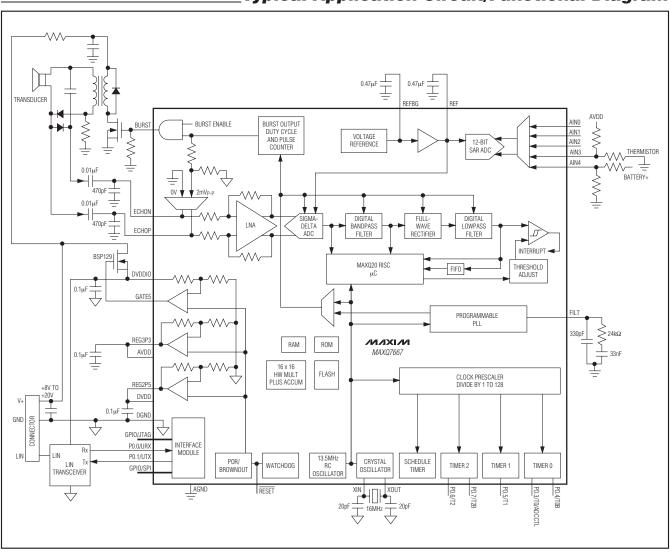

# Typical Application Circuit/Functional Diagram

## **Detailed Features**

♦ Smart Analog Peripherals

**Dedicated Ultrasonic Burst Generator**

**Echo Receiving Path**

Low-Noise Amplifier

**Time Variable Gain Amplifier**

16-Bit Sigma-Delta ADC

**Digital Bandpass Filter**

Full-Wave Rectifier and Digital Lowpass Filter 8-Deep, 16-Bit Wide FIFO Simplifies Real-Time Processing

**Magnitude Comparator**

5-Channel, 12-Bit SAR ADC with 250ksps Sampling Rate

Internal Bandgap Voltage Reference for the ADCs (Also Accepts External Voltage Reference)

♦ Timer/Digital I/O Peripherals

**SPI Interface**

Three 16-Bit (or Six 8-Bit) Programmable Type 2 Timers/Counters

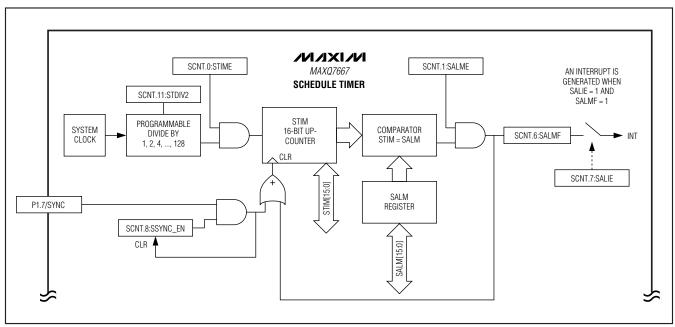

16-Bit Schedule Timer

**Programmable Watchdog Timer**

16 General-Purpose Digital I/Os with Multipurpose Capability

High-Performance, Low-Power, 16-Bit RISC Core

1MHz–16MHz Operation, Approaching 1MIPS per

1MHz

Low Power (< 2.5mA/MIPS, DVDD = +2.5V)

16-Bit Instruction Word, 16-Bit Data Bus

33 Instructions (Most Require Only One Clock

Cycle)

16-Level Hardware Stack

Three Independent Data Pointers with Automatic Increment/Decrement

- Program and Data Memory Internal 32KB Program Flash Internal 4KB Data RAM Internal 8KB Utility ROM

- ◆ Crystal/Clock Module 1MHz-16MHz External Crystal Oscillator 13.5MHz Internal RC Oscillator External Clock Source Operation

- ♦ 16 x 16 Hardware Multiplier with 48-Bit Accumulator, Single Clock Cycle Operation

- **♦ Power-Management Module**

Power-On Reset (POR)

Power-Supply Supervisor/Brownout Detection for All Supplies

On-Chip +5V, +3.3V, and +2.5V Regulators for Single Supply Operation

**♦ JTAG Interface**

Extensive Debug and Emulation Support In-System Test Capability Flash-Memory-Program Download

**♦ UART**

Synchronous and Asynchronous Transfers Independent Baud-Rate Generator 2-Wire Interface

**Transmit and Receive FIFOs**

♦ LIN

Supports LIN 1.3, LIN 2.0, and SAE J2602 Automatic Baud-Rate Detection and LIN Frame Synchronization

Up to 64 Bytes Frame Length Automatic Calculation of Standard (LIN 1.3) and Enhanced (LIN 2.0) Checksums

- ♦ 7mm x 7mm, 48-Pin LQFP Package

- ♦ -40°C to +125°C Operating Temperature Range

# **Detailed Description**

The ultrasonic distance-measurement peripherals in the MAXQ7667 include a burst signal generator for acoustic transmission and mixed signal circuits for amplifying and digitizing echo signals ranging between 25kHz and 100kHz. The burst signal is a square wave with adjustable duty cycle and pulse count. The burst is derived either directly from the system clock or from a programmable PLL locked to the system clock. The MAXQ7667 effectively digitizes the echo signals received at the ECHOP and ECHON inputs using an LNA, sigma-delta ADC with variable analog gain amplifier, noise-limiting digital bandpass filter, digital fullwave rectifier, and a digital lowpass filter (see the Typical Application Circuit/Functional Diagram). The device detects echo signals at the burst frequency with amplitudes ranging from 10µV<sub>P-P</sub> to 100mV<sub>P-P</sub>. Echoes greater than 100mVp-p and less than 2Vp-p are internally clipped but do not saturate the receiver. To optimize echo reception, the clock used for processing the echo locks to the burst frequency. The MAXQ7667's burst generator can generate higher frequencies, but the maximum usable frequency for the echo receive path is 100kHz. For applications requiring transducer frequencies above 100kHz, implement an external echo receive path. The SAR ADC can then digitize the filtered echo envelope.

An integrated 16-bit RISC  $\mu$ C (MAXQ20) provides timing control, signal processing, and data I/O. The 16-bit Harvard architecture RISC core executes most instructions in a single clock cycle from instruction fetch to cycle completion. The MAXQ20 provides optimal performance for noise-sensitive analog applications.

The MAXQ7667 includes a 13.5MHz RC oscillator, external crystal oscillator, watchdog timer, schedule timer, three general-purpose Type 2 timers/counters, two 8-bit GPIO ports, SPI interface, JTAG interface, LIN capable UART interface, 12-bit SAR ADC with five multiplexed input channels, supply-voltage monitors, and a voltage reference for communication, diagnostics, and miscellaneous support.

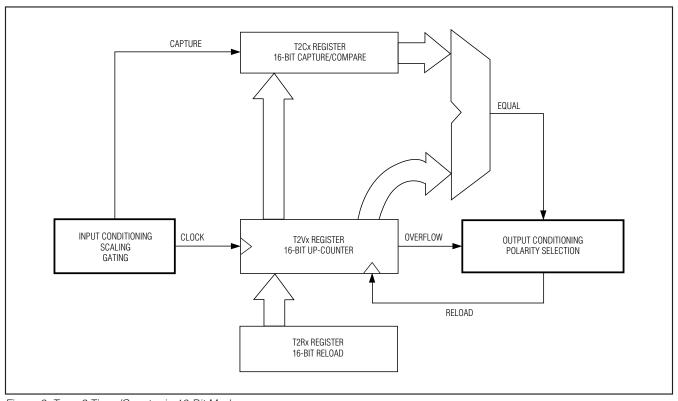

## **Burst Controller**

The MAXQ7667 provides a square-wave burst signal at the BURST output. Use the burst control to transmit an ultrasonic signal. Typical applications use the burst signal to switch an external transistor that drives a high-voltage transformer, which excites the transducer (see the *Typical Application Circuit/Functional Diagram*). Use software to configure the duty cycle, frequency, number of pulses, and drive current of the burst. See Section 17 of the *MAXQ7667 User's Guide*.

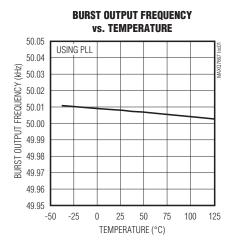

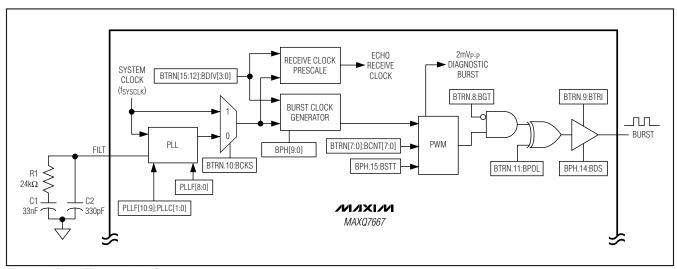

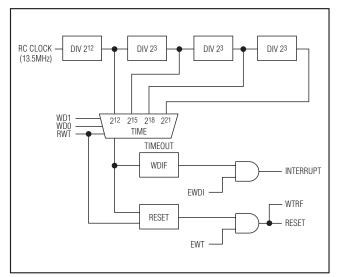

Derive the burst signal either directly from the system clock or from a programmable oscillator phase locked to the system clock (Figure 1). Using the system clock limits the burst frequency to one of 16 choices. Integer division of the system clock generates these 16 frequencies. The PLL allows a fractional division of the system clock. Any frequency within the PLL range is selectable to a resolution of 0.13% or better.

When using the internal PLL, connect external filter components (C1, R1, and C2) to FILT as shown in Figure 1. These components filter the analog voltage that controls the VCO in the PLL. The filter component values shown in the figure are suitable for the entire PLL frequency range.

Figure 1. Burst Transmission Stage

## **Echo Receive Path**

## Low-Noise Amplifier (LNA)

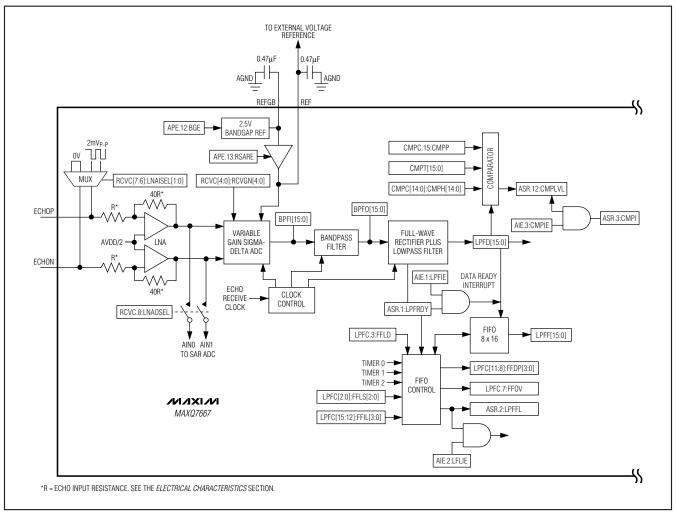

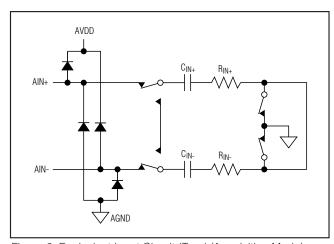

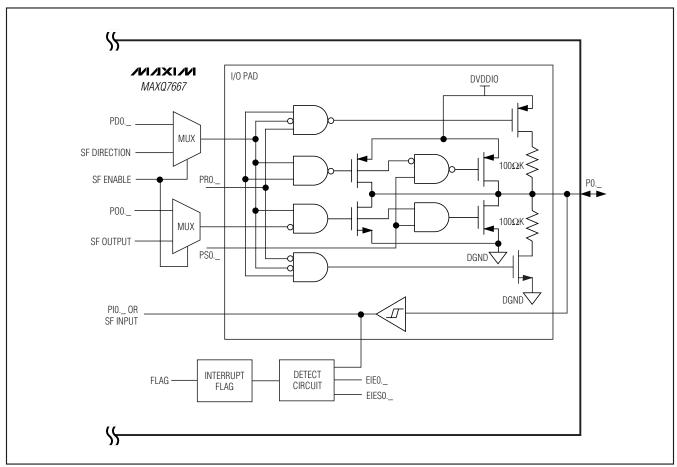

The LNA provides a 40V/V fixed gain to the input signal. The differential inputs of the LNA are ECHOP and ECHON. For proper biasing of the LNA, AC-couple the transducer or any external circuitry to ECHOP and ECHON. For a single-ended input signal, AC-couple the signal to ECHOP with a 0.01µF capacitor and connect ECHON to AGND through a 0.01µF capacitor placed as close as possible to the signal source. The outputs of the LNA connect to the inputs of a 16-bit sigma-delta ADC and can connect internally to the AINO and AIN1 inputs of the SAR ADC for external monitoring (Figure 2).

## Diagnostic Signals

An analog multiplexer located at the input of the LNA selects one of three possible signals for processing by the echo receive path; the normal echo signal AC-coupled to the ECHOP and ECHON inputs, 0V signal, or a 2mVP-P internally generated signal (Figure 2). The 2mVP-P square-wave signal, with frequency and duty cycle matching the burst signal, allows the echo receive chain to process a simulated echo.

Figure 2. Echo Receive Path

## Sigma-Delta ADC

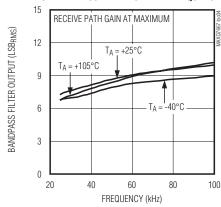

The MAXQ7667 features a 16-bit sigma-delta ADC with an analog gain adjustable from 38dB to 60dB (including the fixed LNA gain) with a maximum gain step of 12.5% (typical). Gain changes settle within one ADC conversion. Use software to create a virtual time variable gain amplifier. A digital bandpass and lowpass filters remove switching glitches and DC offset at the output of the ADC.

In a typical application, the software sets the gain to a low value when the burst is first sent and increases the gain as the time from when the burst was sent increases. As a result, strong echoes from nearby objects are processed without clipping while small signals from distant objects are processed with the maximum gain. The ADC samples the amplified echo signal from the LNA at 80 times the burst output frequency. The ADC provides conversion results at a data rate equal to 10 times the burst output frequency. The ADC conversion results also load to an 8-deep first-in-first-out (FIFO) at the native data rate or a separate time base without loading the CPU.

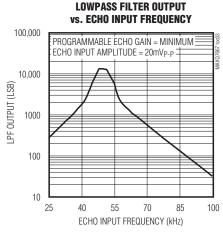

## Digital Bandpass Filter

The digital bandpass filter has a center frequency that tracks the burst output frequency. The bandpass width is 14% of the center frequency. The bandpass filter provides the 16-bit output data at a data rate equal to 10 times the burst output frequency.

## Full-Wave Rectifier

The full-wave rectifier detects the envelope of the digital bandwidth filter output to generate a DC output proportional to the peak-to-peak amplitude of the input signal. Full-wave rectification allows the digital lowpass filter to respond faster without excessive ripple.

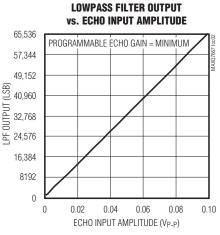

## Digital Lowpass Filter

The lowpass filter removes the ripple from the full-wave detector output. The output of the lowpass filter is available at a data rate equal to five times the burst output frequency. The corner frequency is 1/5 the burst frequency with approximately 40dB per decade rolloff. The 16-bit output data of the lowpass filter is stored in a FIFO register with a depth of eight samples. The MAXQ7667 allows data transfer from the lowpass filter

Figure 3. SAR ADC Block Diagram

output to the FIFO automatically each time the lowpass filter output updates, through the control of one of the timer outputs, or through software. The device includes a FIFO depth counter with programmable interrupt levels and generates an interrupt if a FIFO overflow condition occurs. The output of the digital lowpass filter connects to a digital comparator that can generate an interrupt for a specified echo signal level.

## Digital Comparator and Threshold Adjust

The digital comparator output asserts when the echo amplitude at the output of the digital lowpass filter crosses a given threshold. The comparator's threshold level, hysteresis, and interrupt polarity are programmable.

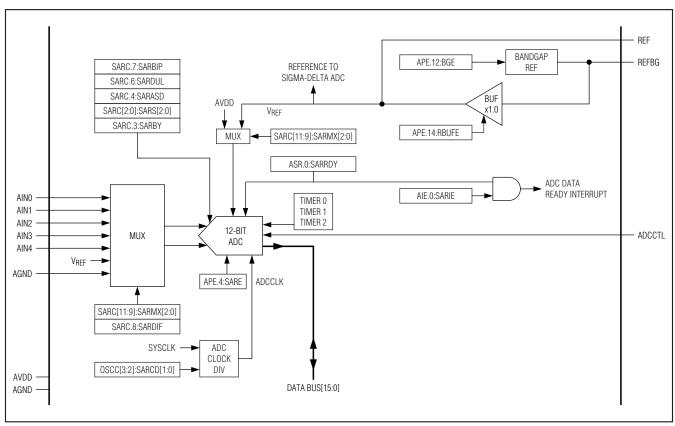

## SAR ADC

The MAXQ7667 incorporates a 12-bit unbuffered SAR ADC with sample-and-hold and conversion rate up to 250ksps. The ADC allows measurements of tempera-

ture, battery voltage, or other parameters using five single-ended or two fully differential analog inputs (AIN0-AIN4). All of the analog inputs have a range of 0 to VREF in unipolar mode and ±VREF/2 in bipolar mode.

The SAR ADC supports three different conversion start sources: timers, ADC control input (ADCCTL), and software write. The conversion start source triggers the ADC acquisition and conversion. The system clock provides the ADC clock frequency programmable to 1/2, 1/4, 1/8, or 1/16 of the system clock. Use internal bandgap reference, external reference, or AVDD for voltage reference of the SAR ADC. Figure 3 shows a simplified block diagram of the SAR ADC.

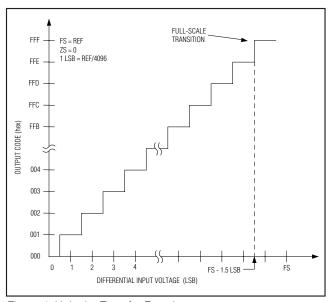

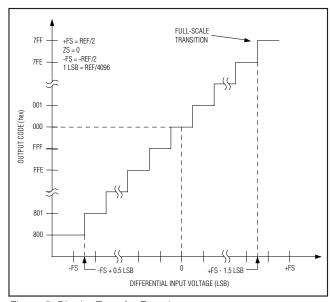

The output of the SAR ADC is straight binary in unipolar mode and two's complement in bipolar mode. Figures 4 and 5 show the ADC transfer functions in unipolar mode and bipolar mode.

Figure 4. Unipolar Transfer Function

Figure 5. Bipolar Transfer Function

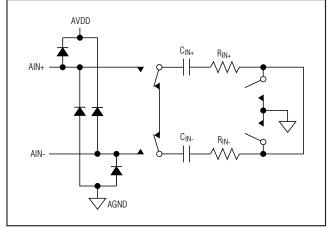

## SAR ADC Analog Input Track-and-Hold (T/H)

Figures 6 and 7 show the equivalent input circuit of the MAXQ7667 analog input architecture. During acquisition (track), a sampling capacitor charges to the positive input voltage at AIN0–AIN4 in single-ended mode or AIN0 and AIN2 in differential mode while a second sampling capacitor connects to AGND in single-ended mode or AIN1 and AIN3 in differential mode. The ADC conversion start source and the ADC dual mode selection bits control the T/H timing.

## **Voltage Reference**