Features

# Switch-Mode Lithium-Ion **Battery-Charger**

### **General Description**

The MAX745 provides all functions necessary for charging lithium-ion (Li+) battery packs. It provides a regulated charging current of up to 4A without getting hot, and a regulated voltage with only ±0.75% total error at the battery terminals. It uses low-cost, 1% resistors to set the output voltage, and a low-cost N-channel MOSFET as the power switch.

The MAX745 regulates the voltage set point and charging current using two loops that work together to transition smoothly between voltage and current regulation. The per-cell battery voltage regulation limit is set between 4V and 4.4V using standard 1% resistors, and then the number of cells is set from 1 to 4 by pin-strapping. Total output voltage error is less than ±0.75%.

For a similar device with an SMBus™ microcontroller interface and the ability to charge NiCd and NiMH cells. refer to the MAX1647 and MAX1648. For a low-cost Li+ charger using a linear-regulator control scheme, refer to the MAX846A.

### **Applications**

Li+ Battery Packs Desktop Cradle Chargers Cellular Phones Notebook Computers Hand-Held Instruments

#### ♦ Charges 1 to 4 Li+ Battery Cells

- ♦ ±0.75% Voltage-Regulation Accuracy **Using 1% Resistors**

- ♦ Provides up to 4A without Excessive Heating

- ♦ 90% Efficient

- ♦ Uses Low-Cost Set Resistors and **N-Channel Switch**

- ♦ Up to 24V Input

- ♦ Up to 18V Maximum Battery Voltage

- ♦ 300kHz Pulse-Width Modulated (PWM) Operation Low-Noise, Small Components

- ♦ Stand-Alone Operation—No Microcontroller Needed

## **Ordering Information**

| PART      | TEMP RANGE     | PIN-PACKAGE |

|-----------|----------------|-------------|

| MAX745C/D | 0°C to +70°C   | Dice*       |

| MAX745EAP | -40°C to +85°C | 20 SSOP     |

<sup>\*</sup>Dice are tested at  $T_A = +25$ °C.

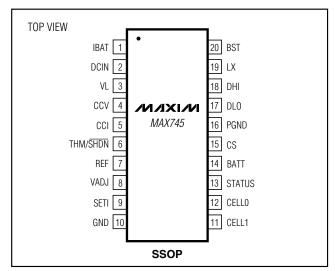

Pin Configuration appears at end of data sheet.

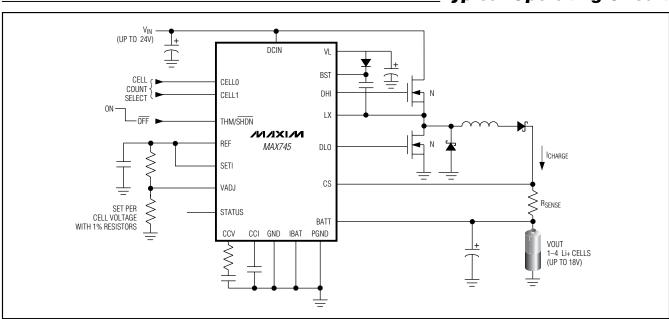

# **Typical Operating Circuit**

SMBus is a trademark of Intel Corp.

### **ABSOLUTE MAXIMUM RATINGS**

| DCIN to GND0.3V to 26V BST, DHI to GND0.3V to 30V BST to LX0.3V to 6V DHI to LX                                                                      | BATT, CS to GND0.3V to 20V PGND to GND0.3V to 0.3V VL Current50mA Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| LX to GND0.3V to (DCIN + 0.3V)  VL to GND0.3V to 6V  CELL0, CELL1, IBAT, STATUS, CCI, CCV, REF, SETI,  VADJ, DLO, THM/SHDN to GND0.3V to (VL + 0.3V) | SSOP (derate 8.00mW/°C above +70°C)                                                                                     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(V<sub>DCIN</sub> = 18V, V<sub>BATT</sub> = 8.4V, **T<sub>A</sub> = 0°C to +85°C**. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                     | CONDITIONS                                        | MIN   | TYP  | MAX   | UNITS |  |

|-------------------------------|---------------------------------------------------|-------|------|-------|-------|--|

| SUPPLY AND REFERENCE          |                                                   |       |      |       |       |  |

| DCIN Input Voltage Range      |                                                   | 6     |      | 24    | V     |  |

| DCIN Quiescent Supply Current | 6.0V < V <sub>DCIN</sub> < 24V, logic inputs = VL |       | 4    | 6     | mA    |  |

| VL Output Voltage             | 6.0V < V <sub>DCIN</sub> < 24V, no load           | 5.15  | 5.40 | 5.65  | V     |  |

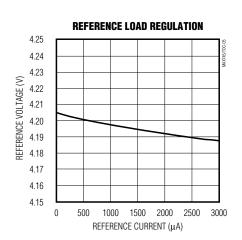

| REF Output Voltage            | T <sub>A</sub> = +25°C                            | 4.17  | 4.2  | 4.23  | V     |  |

| ner Output Voltage            | 6.0V < V <sub>DCIN</sub> < 24V                    | 4.16  | 4.2  | 4.24  |       |  |

| REF Output Load Regulation    | 0 < I <sub>REF</sub> < 1mA                        |       | 10   | 20    | mV/m/ |  |

| SWITCHING REGULATOR           |                                                   | •     |      |       |       |  |

| Oscillator Frequency          |                                                   | 270   | 300  | 330   | kHz   |  |

| DHI Maximum Duty Cycle        |                                                   | 89    | 93   |       | %     |  |

| DHI On-Resistance             | Output high or low                                |       | 4    | 7     | Ω     |  |

| DLO On-Resistance             | Output high or low                                |       | 6    | 14    | Ω     |  |

| DATT Input Current            | VL < 3.2V, V <sub>BATT</sub> = 12V                |       |      | 5     | μΑ    |  |

| BATT Input Current            | VL > 5.15V, V <sub>BATT</sub> = 12V               |       |      | 500   |       |  |

| CC locate Commont             | VL < 3.2V, V <sub>CS</sub> = 12V                  |       |      | 5     | μΑ    |  |

| CS Input Current              | VL > 5.15V, V <sub>CS</sub> = 12V                 |       |      | 400   |       |  |

| BATT, CS Input Voltage Range  | 4V < V <sub>BATT</sub> < 16V                      | 0     |      | 19    | V     |  |

| CS to BATT Offset Voltage     | (Note 1)                                          |       | ±1.5 |       | mV    |  |

| CS to BATT                    | SETI = V <sub>REF</sub> (full scale)              | 170   | 185  | 205   | mV    |  |

| Current-Sense Voltage         | SETI = 400mV                                      | 14    | 18   | 22    |       |  |

| Absolute Voltage Accuracy     | Not including VADJ resistor tolerance             | -0.65 |      | +0.65 | - %   |  |

| Absolute Voltage Accuracy     | With 1% tolerance VADJ resistors                  | -0.75 |      | +0.75 |       |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DCIN} = 18V, V_{BATT} = 8.4V, T_A = 0$ °C to +85°C. Typical values are at  $T_A = +25$ °C, unless otherwise noted.)

| PARAMETER                                        | CONDITIONS                                             | MIN  | TYP  | MAX              | UNITS |

|--------------------------------------------------|--------------------------------------------------------|------|------|------------------|-------|

| ERROR AMPLIFIERS                                 |                                                        |      |      |                  |       |

| GMV Amplifier Transconductance                   |                                                        |      | 800  |                  | μA/V  |

| GMI Amplifier Transconductance                   |                                                        |      | 200  |                  | μA/V  |

| GMV Amplifier Output Current                     |                                                        |      | ±130 |                  | μA    |

| GMI Amplifier Output Current                     |                                                        |      | ±320 |                  | μA    |

| CCI Clamp Voltage with Respect to CCV            | 1.1V < V <sub>CCV</sub> < 3.5V                         | 25   | 80   | 200              | mV    |

| CCV Clamp Voltage with Respect to CCI            | 1.1V < V <sub>CCI</sub> < 3.5V                         | 25   | 80   | 200              | mV    |

| CONTROL INPUTS/OUTPUTS                           |                                                        |      |      |                  |       |

| CELL0, CELL1 Input Bias Current                  |                                                        | -1   |      | +1               | μA    |

| SETI Input Voltage Range                         | (Note 1)                                               | 0    |      | V <sub>REF</sub> | V     |

| VADJ Adjustment Range                            |                                                        | 10   |      |                  | %     |

| SETI, VADJ Input Bias Current                    |                                                        | -10  |      | +10              | nA    |

| VADJ Input Voltage Range                         |                                                        | 0    |      | V <sub>REF</sub> | V     |

| THM/SHDN Rising Threshold                        |                                                        | 2.20 | 2.3  | 2.34             | V     |

| THM/SHDN Falling Threshold                       |                                                        | 2.01 | 2.1  | 2.19             | V     |

| STATUS Output Low Voltage                        | Charger in current-regulation mode, STATUS sinking 1mA |      |      | 0.2              | V     |

| STATUS Output Leakage Current                    | Charger in voltage-regulation mode,<br>VSTATUS = 5V    |      |      | 1                | μΑ    |

| IBAT Output Current vs.<br>Current-Sense Voltage | V <sub>IBAT</sub> = 2V                                 |      | 0.9  |                  | μΑ/mV |

| IBAT Compliance Voltage Range                    |                                                        | 0    |      | 2                | V     |

#### **ELECTRICAL CHARACTERISTICS**

(V<sub>DCIN</sub> = 18V, V<sub>BATT</sub> = 8.4V, **T<sub>A</sub> = -40°C to +85°C**, unless otherwise noted. Limits over temperature are guaranteed by design.)

| PARAMETER                                      | CONDITIONS                              | MIN  | TYP | MAX  | UNITS |  |  |  |

|------------------------------------------------|-----------------------------------------|------|-----|------|-------|--|--|--|

| SUPPLY AND REFERENCE                           | SUPPLY AND REFERENCE                    |      |     |      |       |  |  |  |

| VL Output Voltage                              | 6.0V < V <sub>DCIN</sub> < 24V, no load | 5.10 |     | 5.70 | V     |  |  |  |

| REF Output Voltage                             | 6.0V < VDCIN < 24V                      | 4.14 |     | 4.26 | V     |  |  |  |

| SWITCHING REGULATOR (Note 1)                   | SWITCHING REGULATOR (Note 1)            |      |     |      |       |  |  |  |

| Oscillator Frequency                           |                                         | 260  |     | 340  | kHz   |  |  |  |

| DHI On-Resistance                              | Output high or low                      |      |     | 7    | Ω     |  |  |  |

| DLO On-Resistance                              | Output high or low                      |      |     | 14   | Ω     |  |  |  |

| CS to BATT Full-Scale<br>Current-Sense Voltage |                                         | 165  |     | 205  | mV    |  |  |  |

| Absolute Voltage Accuracy                      | Not including VADJ resistors            | -1.0 |     | +1.0 | %     |  |  |  |

**Note 1:** When  $V_{SETI} = 0V$ , the battery charger turns off.

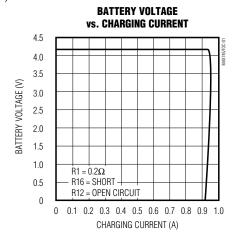

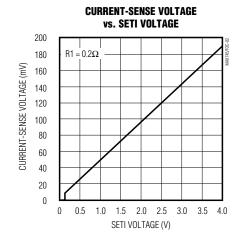

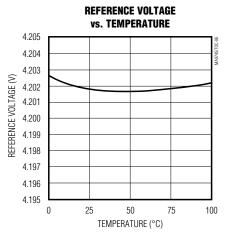

# **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, V_{DCIN} = 18V, V_{BATT} = 4.2V, CELL0 = CELL1 = GND, C_{VL} = 4.7 \mu F C_{REF} = 0.1 \mu F.$  Circuit of Figure 1, unless otherwise noted.)

## **Pin Description**

| PIN    | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                            |

|--------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | IBAT            | Current-Sense Amplifier's Analog Current-Source Output. See the <i>Monitoring Charge Current</i> section for a detailed description.                                                                                                                                                                                                |

| 2      | DCIN            | Charger Input Voltage. Bypass DCIN with a 0.1µF capacitor.                                                                                                                                                                                                                                                                          |

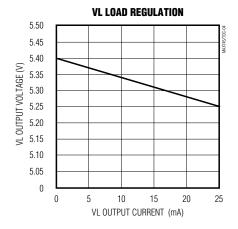

| 3      | VL              | Chip Power Supply. Output of the 5.4V linear regulator from DCIN. Bypass VL with a 4.7µF capacitor.                                                                                                                                                                                                                                 |

| 4      | CCV             | Voltage-Regulation-Loop Compensation Point                                                                                                                                                                                                                                                                                          |

| 5      | CCI             | Current-Regulation-Loop Compensation Point                                                                                                                                                                                                                                                                                          |

| 6      | THM/<br>SHDN    | Thermistor Sense-Voltage Input. THM/SHDN also performs the shutdown function. If pulled low, the charger turns off.                                                                                                                                                                                                                 |

| 7      | REF             | 4.2V Reference Voltage Output. Bypass REF with a 0.1µF or greater capacitor.                                                                                                                                                                                                                                                        |

| 8      | VADJ            | Voltage-Adjustment Pin. VADJ is tied to a 1% tolerance external resistor-divider to adjust the voltage set point by 10%, eliminating the need for precision 0.1% resistors. The input voltage range is 0V to V <sub>REF</sub> .                                                                                                     |

| 9      | SETI            | SETI is externally tied to the resistor-divider between REF and GND to set the charging current.                                                                                                                                                                                                                                    |

| 10     | GND             | Analog Ground                                                                                                                                                                                                                                                                                                                       |

| 11, 12 | CELL1,<br>CELL0 | Logic Inputs to Select Cell Count. See Table 1 for cell-count programming.                                                                                                                                                                                                                                                          |

| 13     | STATUS          | An open-drain MOSFET sinks current when in current-regulation mode, and is high impedance when in voltage-regulation mode. Connect STATUS to VL through a $1k\Omega$ to $100k\Omega$ pullup resistor. STATUS can also drive an LED for visual indication of regulation mode (see MAX745 EV kit). Leave STATUS floating if not used. |

| 14     | BATT            | Battery-Voltage-Sense Input and Current-Sense Negative Input                                                                                                                                                                                                                                                                        |

| 15     | CS              | Current-Sense Positive Input                                                                                                                                                                                                                                                                                                        |

| 16     | PGND            | Power Ground                                                                                                                                                                                                                                                                                                                        |

| 17     | DLO             | Low-Side Power MOSFET Driver Output                                                                                                                                                                                                                                                                                                 |

| 18     | DHI             | High-Side Power MOSFET Driver Output                                                                                                                                                                                                                                                                                                |

| 19     | LX              | Power Connection for the High-Side Power MOSFET Source                                                                                                                                                                                                                                                                              |

| 20     | BST             | Power Input for the High-Side Power MOSFET Driver                                                                                                                                                                                                                                                                                   |

## **Detailed Description**

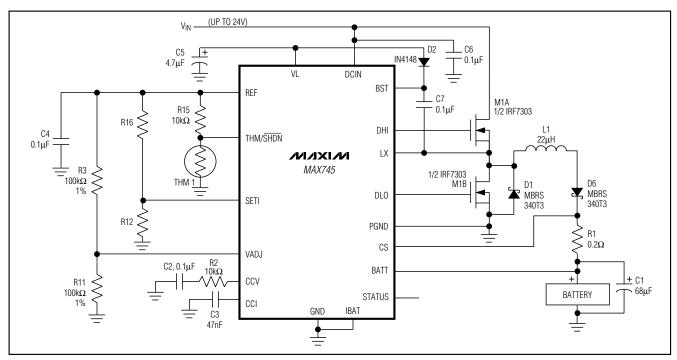

The MAX745 is a switch-mode, Li+ battery charger that can achieve 90% efficiency. The charge voltage and current are set independently by external resistor-dividers at SETI and VADJ, and at pin connections at CELL0 and CELL1. VADJ is connected to a resistor-divider to set the charging voltage. The output voltage-adjustment range is  $\pm 5\%$ , eliminating the need for 0.1% resistors while still achieving 0.75% set accuracy using 1% resistors.

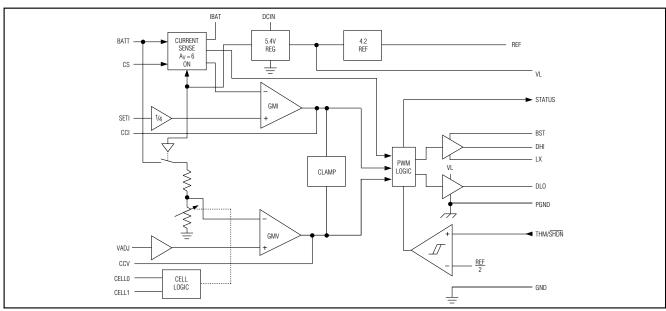

The MAX745 consists of a current-mode, pulse-width-modulated (PWM) controller and two transconductance error amplifiers: one for regulating current (GMI) and the other for regulating voltage (GMV) (Figure 2). The error amplifiers are controlled through the SETI and VADJ pins. Whether the MAX745 is controlling voltage or current at any time depends on the battery state. If the battery is discharged, the MAX745 output reaches

the current-regulation limit before the voltage limit, causing the system to regulate current. As the battery charges, the voltage rises to the point where the voltage limit is reached and the charger switches to regulating voltage. The STATUS pin indicates whether the charger is regulating current or voltage.

#### **Voltage Control**

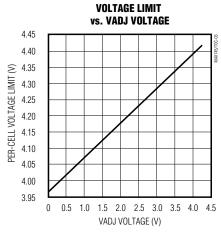

To set the voltage limit on the battery, connect a resistor- divider to VADJ from REF. A 0V to VREF change at VADJ sets a ±5% change in the battery limit voltage around 4.2V. Since the 0 to 4.2V range on VADJ results in only a 10% change on the voltage limit, the resistor-divider's accuracy does not need to be as high as the output voltage accuracy. Using 1% resistors for the voltage dividers typically results in no more than 0.1% degradation in output voltage accuracy. VADJ is internally buffered so that high-value resistors can be used to set the output voltage. When the voltage at VADJ is

V<sub>REF</sub> / 2, the voltage limit is 4.2V. Table 1 defines the battery cell count.

The battery limit voltage is set by the following:

$$V_{BATT} = (cell count) \times \left[ V_{REF} + \frac{\left( V_{ADJ} - \frac{1}{2} V_{REF} \right)}{9.523} \right]$$

Solving for V<sub>ADJ</sub>, we get:

$$V_{ADJ} = \frac{9.523 V_{BATT}}{\text{(cell count)}} - 9.023 V_{REF}$$

Set VaDJ by choosing a value for R11 (typically 100k $\Omega$ ), and determine R3 by:

$$R3 = [1 - (V_{ADJ} / V_{REF})] \times R11 (Figure 1)$$

**Table 1. Cell-Count Programming Table**

| CELL0 | CELL1 | CELL COUNT |

|-------|-------|------------|

| GND   | GND   | 1          |

| VL    | GND   | 2          |

| GND   | VL    | 3          |

| VL    | VL    | 4          |

where  $V_{REF} = 4.2V$  and cell count is 1, 2, 3, 4 (Table 1).

The voltage-regulation loop is compensated at the CCV pin. Typically, a series-resistor-capacitor combination can be used to form a pole-zero doublet. The pole introduced rolls off the gain starting at low frequencies. The zero of the doublet provides sufficient AC gain at mid-frequencies. The output capacitor (C1) rolls off the mid-frequency gain to below unity. This guarantees stability before encountering the zero introduced by the C1's equivalent series resistance (ESR). The GMV amplifier's output is internally clamped to between one-fourth and three-fourths of the voltage at REF.

#### **Current Control**

The charging current is set by a combination of the current-sense resistor value and the SETI pin voltage. The current-sense amplifier measures the voltage across the current-sense resistor, between CS and BATT. The current-sense amplifier's gain is 6. The voltage on SETI is buffered and then divided by 4. This voltage is compared to the current-sense amplifier's output. Therefore, full-scale current is accomplished by connecting SETI to REF. The full-scale charging current (IFS) is set by the following:

$$IFS = 185 \text{mV} / R1 \text{ (Figure 1)}$$

Figure 1. Standard Application Circuit

To set currents below full scale without changing R1, adjust the voltage at SETI according to the following formula:

A capacitor at CCI sets the current-feedback loop's dominant pole. While the current is in regulation, CCV voltage is clamped to within 80mV of the CCI voltage. This prevents the battery voltage from overshooting when the voltage setting is changed. The converse is true when the voltage is in regulation and the current setting is changed. Since the linear range of CCI or CCV is about 2V (1.5V to 3.5V), the 80mV clamp results in negligible overshoot when the loop switches from voltage regulation to current regulation, or vice versa.

#### **Monitoring Charge Current**

The battery-charging current can be externally monitored by placing a scaling resistor (RIBAT) between IBAT and GND. IBAT is the output of a voltage-controlled current source, with output current given by:

$$I_{IBAT} = \frac{0.9 \mu A}{mV} \times V_{SENSE}$$

where VSENSE is the voltage across the current-sense resistor (in millivolts) given by:

The voltage across RIBAT is then given by:

$$V_{IBAT} = 0.9 \times 1 \ 0^{-3} \ A_{V} \times I_{CHG} \times R1 \times R_{IBAT}$$

RIBAT must be chosen to limit VIBAT to voltages below 2V for the maximum charging current. Connect IBAT to GND if unused.

#### **PWM Controller**

The battery voltage or current is controlled by a current-mode, PWM DC/DC converter controller. This controller drives two external N-channel MOSFETs, which control power from the input source. The controller sets the switched voltages pulse width so that it supplies the desired voltage or current to the battery. Total component cost is reduced by using a dual, N-channel MOSFET.

The heart of the PWM controller is a multi-input comparator. This comparator sums three input signals to determine the switched signal's pulse width, setting the battery voltage or current. The three signals are the current-sense amplifier's output, the GMV or GMI error amplifier's output, and a slope-compensation signal that ensures that the current-control loop is stable.

The PWM comparator compares the current-sense amplifier's output to the lower output voltage of either the GMV or GMI amplifiers (the error voltage). This current-mode feedback reduces the effect of the inductor on the output filter LC formed by the output inductor (L1) and C1 (Figure 1). This makes stabilizing the circuit much easier, since the output filter changes to a first-order RC from a complex, second-order RLC.

Figure 2. Functional Diagram

#### **MOSFET Drivers**

The MAX745 drives external N-channel MOSFETs to switch the input source generating the battery voltage or current. Since the high-side N-channel MOSFET's gate must be driven to a voltage higher than the input source voltage, a charge pump is used to generate such a voltage. The capacitor (C7) charges through D2 to approximately 5V when the synchronous rectifier (M1B) turns on (Figure 1). Since one side of C7 is connected to LX (the source of M1A), the high-side driver (DHI) drives the gate up to the voltage at BST, which is greater than the input voltage while the high-side MOSFET is on.

The synchronous rectifier (M1B) behaves like a diode but has a smaller voltage drop, improving efficiency. A small dead time is added between the time when the high-side MOSFET is turned off and when the synchronous rectifier is turned on, and vice versa. This prevents crowbar currents during switching transitions. Place a Schottky rectifier from LX to ground (D1, across M1B's drain and source) to prevent the synchronous rectifier's body diode from conducting during the dead time. The body diode typically has slower switching-recovery times, so allowing it to conduct degrades efficiency. D1 can be omitted if efficiency is not a concern, but the resulting increased power dissipation in the synchronous rectifier must be considered.

Since the BST capacitor is charged while the synchronous rectifier is on, the synchronous rectifier may not be replaced by a rectifier. The BST capacitor will not fully charge without the synchronous rectifier, leaving the high-side MOSFET with insufficient gate drive to turn on. However, the synchronous rectifier can be replaced with a small MOSFET (such as a 2N7002) to guarantee that the BST capacitor is allowed to charge. In this case, the majority of the high charging currents are carried by D1, and not by the synchronous rectifier.

#### Internal Regulator and Reference

The MAX745 uses an internal low-dropout linear regulator to create a 5.4V power supply (VL), which powers its internal circuitry. The VL regulator can supply up to 25mA. Since 4mA of this current powers the internal circuitry, the remaining 21mA can be used for external circuitry. MOSFET gate-drive current comes from VL, which must be considered when drawing current for other functions. To estimate the current required to drive the MOSFETs, multiply the sum of the MOSFET gate charges by the switching frequency (typically 300kHz). Bypass VL with a 4.7µF capacitor to ensure stability.

The MAX745 internal 4.2V reference voltage must be bypassed with a  $0.1\mu F$  or greater capacitor.

#### **Minimum Input Voltage**

The input voltage to the charger circuit must be greater than the maximum battery voltage by approximately 2V so the charger can regulate the voltage properly. The input voltage can have a large AC-ripple component when operating from a wall cube. The voltage at the low point of the ripple waveform must still be approximately 2V greater than the maximum battery voltage.

Using components as indicated in Figure 1, the minimum input voltage can be determined by the following formula:

$$V_{IN} \times \frac{[V_{BATT} + V_{D6} + I_{CHG} (R_{DS(ON)} + R_L + R_1)]}{0.89}$$

where: VIN is the input voltage;

V<sub>D6</sub> is the voltage drop across D6

(typically 0.4V to 0.5V);

ICHG is the charging current;

R<sub>DS(ON)</sub> is the high-side MOSFET M1A's on-resistance;

RL is the the inductor's series resistance;

R1 is the current-sense resistor R1's value.

# Pin Configuration

# Chip Information

TRANSISTOR COUNT: 1695

SUBSTRATE CONNECTED TO GND