# **MIC2590B**

# **Dual-Slot PCI Hot Plug Controller**

# **General Description**

The MIC2590B is a power controller supporting power distribution requirements for Peripheral Component Interconnect (PCI) hot plug compliant systems incorporating the Intelligent Platform Management Interface (IPMI). The MIC2590B provides complete power control support for two PCI slots including the 3.3V<sub>AUX</sub> defined by the PCI 2.2 specification.

Support for +5V, +3.3V, +12V and -12V supplies is provided including programmable constant-current inrush limiting, voltage supervision, programmable current limit, fault reporting and circuit breaker functions which provide fault isolation.

The MIC2590B also incorporates a SMBus interface in which complete status and control of power within each slot is provided. Data such as voltage and current from each supply of each slot can be obtained for IPMI sensor records in addition to power status of each slot.

Data sheets and support documentation can be found on Micrel's web site at: www.micrel.com.

## **Features**

- Supports two independent PCI 2.2 slots

- SMBus interface for slot power control and status

- +5V, +3.3V, +12V, -12V, +3.3VAUX supplies supported per PCI specification 2.2

- Programmable inrush current-limiting

- Active current regulation controls inrush current

- Electronic circuit breaker

- Dual level fault detection for quick fault response without nuisance tripping

- . Thermal isolation between circuitry for slot A and slot B

# **Applications**

PCI hot-plug power distribution

# Ordering Information

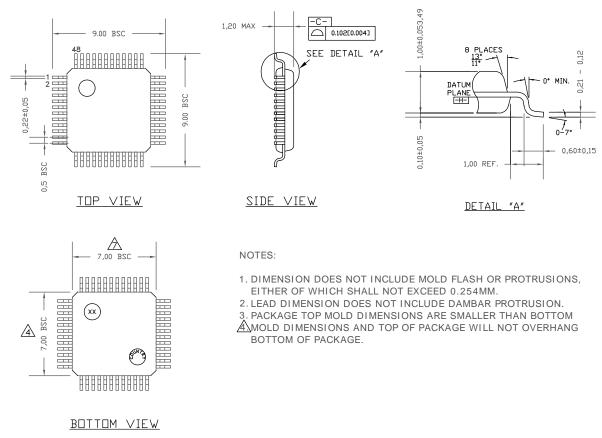

| Part Number    |                | 5V & 3V Fast-trip | +12V & -12V Fast-trip | Operating   | Package     |  |

|----------------|----------------|-------------------|-----------------------|-------------|-------------|--|

| Standard       | Pb-Free        | Threshold         | Threshold             | Temp. Range |             |  |

| MIC2590B-2BTQ  | MIC2590B-2YTQ  | 100mV             | 1.5A/0.4A             | 0° to +70°C | 48-Pin TQFP |  |

| MIC2590B-5BTQ* | MIC2590B-5YTQ* | Disabled          | 1.5A/0.4A             | 0° to +70°C | 48-Pin TQFP |  |

#### Note:

M9999-091808

<sup>\*</sup> Contact factory for availability.

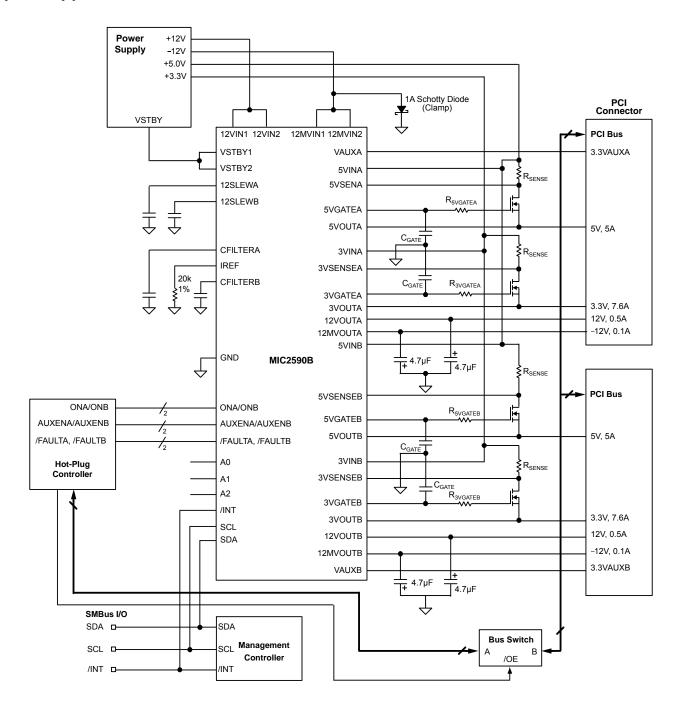

# **Typical Application**

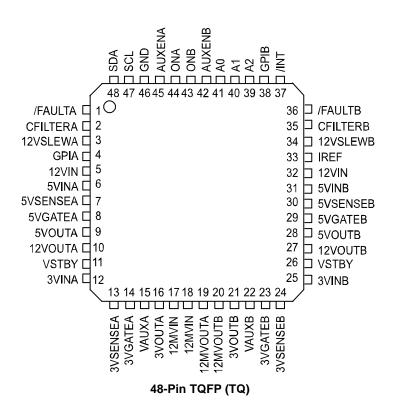

# **Pin Configuration**

# **Pin Description**

| Pin Number | Pin Name           | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

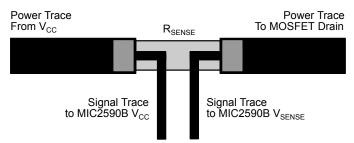

| 6, 31      | 5VINA, 5VINB       | 5V Supply Power and Sense Inputs [A/B]: Two pins are provided for Kelvin connection (one for each slot). Pin 6 is the Kelvin sense connection to the supply side of the sense resistor for 5V Slot A. Pin 31 is the Kelvin sense connection to the supply side of the sense resistor for 5V Slot B. These two pins must ultimately connect to each other within 10cm. An undervoltage lockout circuit (UVLO) prevents the switches from turning on while this input is less than its lockout threshold.    |

| 12, 25     | 3VINA, 3VINB       | 3.3V Supply Power and Sense Inputs [A/B]: Two pins are provided for Kelvin connection (one for each slot). Pin 12 is the Kelvin sense connection to the supply side of the sense resistor for 3V Slot A. Pin 25 is the Kelvin sense connection to the supply side of the sense resistor for 3V Slot B. These two pins must ultimately connect to each other within 10cm. An undervoltage lockout circuit (UVLO) prevents the switches from turning on while this input is less than its lockout threshold. |

| 5, 32      | 12VIN – 2 pins     | +12V Supply Input: An undervoltage lockout circuit prevents the switches from turning on while this input is less than its lockout threshold. Both pins must be tied together at the chip.                                                                                                                                                                                                                                                                                                                 |

| 17, 18     | 12VMIN – 2 pins    | -12V Supply Input: An undervoltage lockout circuit prevents the switches from turning on while this input is less than its lockout threshold. Both pins must be tied together at the chip.                                                                                                                                                                                                                                                                                                                 |

| 10, 27     | 12VOUTA, 12VOUTB   | 12V output [A/B]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 19, 20     | 12MVOUTA, 12MVOUTB | -12V output [A/B]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3, 34      | 12VSLEWA, 12VSLEWB | 12V Slew Rate Control [A/B]: Connect capacitors between these pins and ground to set output slew rates of the +12V and -12V supplies.                                                                                                                                                                                                                                                                                                                                                                      |

| Pin Number | Pin Name           | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 45, 42     | AUXENA, AUXENB     | AUX Enable Inputs [A/B]: Rising-edge sensitive enable inputs for VAUXA and VAUXB outputs. Taking AUXENA/AUXENB low after a fault resets the respective slot's Aux Output Fault Latch. Tie these pins to ground if using SMBus-mode power control.                                                                                                                                                                                                                                                          |  |

| 16, 21     | 3VOUTA, 3VOUTB     | 3.3V Power-Good Sense Inputs: Connect to 3.3V[A/B] outputs. Used to monitor the 3.3V output voltages for Power-Good status.                                                                                                                                                                                                                                                                                                                                                                                |  |

| 9, 28      | 5VOUTA, 5VOUTB     | 5V Power-Good Sense Inputs: Connect to 5V[A/B] outputs. Used to monitor the 5V output voltages for Power-Good status.                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 33         | IREF               | A resistor connected between this pin and ground sets the ADC current measurement gain. This resistor must be $20k\Omega \pm 1\%$ .                                                                                                                                                                                                                                                                                                                                                                        |  |

| 7, 30      | 5VSENSEA, 5VSENSEB | 5V Circuit Breaker Sense Input [A/B]: The current-limit thresholds are set by connecting sense resistors between these pins and 5VIN[A/B]. When the current-limit threshold of IR = 50mV is reached, the 5VGATE[A/B] pin is modulated to maintain a constant voltage across the sense resistor and therefore a constant current into the load. If the 50mV threshold is exceeded for $t_{\text{FLT}}$ , the circuit breaker is tripped and the GATE pin for the affected slot is immediately pulled low.   |  |

| 13, 24     | 3VSENSEA, 3VSENSEB | 3V Circuit Breaker Sense Input [A/B]: The current limit thresholds are set by connecting sense resistors between these pins and $3VIN[A/B]$ . When the current limit threshold of IR = $50mV$ is reached, the $3VGATE[A/B]$ pin is modulated to maintain a constant voltage across the sense resistor and therefore a constant current into the load. If the $50mV$ threshold is exceeded for $t_{FLT}$ , the circuit breaker is tripped and the GATE pin for the affected slot is immediately pulled low. |  |

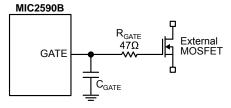

| 8, 29      | 5VGATEA, 5VGATEB   | 5V Gate Drive Outputs [A/B]: Each connects to the gate of an external N-Channel MOSFET. During power-up the $C_{GATE}$ and the gate of the MOSFETs are charged by a 20µA current source. This controls the value ofdv/dt seen at the source of the MOSFETs, and hence the current flowing into the load capacitance.                                                                                                                                                                                       |  |

|            |                    | During current limit events, the voltage at this pin is adjusted to maintain constant current through the switch for a period of $t_{\text{FLT}}$ . Whenever an overcurrent, thermal shutdown or input undervoltage fault condition occur sthe GATE pin for the affected slot is immediately brought low.                                                                                                                                                                                                  |  |

|            |                    | During power-down these pins are discharged by an internal current source.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 14, 23     | 3VGATEA, 3VGATEB   | 3V Gate Drive Outputs [A/B]: Each connects to the gate of an external N-Channel MOSFET. During power-up the $C_{\text{GATE}}$ and the gate of the MOSFETs are charged by a 20 $\mu$ A current source. This controls the value ofdv/dt seen at the source of the MOSFETs, and hence the current flowing into the load capacitance.                                                                                                                                                                          |  |

|            |                    | During current limit events, the voltage at this pin is adjusted to maintain constant current through the switch for a period of $t_{\text{FLT}}$ . Whenever an overcurrent, thermal shutdown or input undervoltage fault condition occurs the GATE pin for the affected slot is immediately brought low.                                                                                                                                                                                                  |  |

|            |                    | During power-down these pins are discharged by an internal current source.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 11, 26     | VSTBY – 2 pins     | 3.3V Standby input voltage required to support PCI 2.2 VAUX input: SMBus, internal registers and A/D converter run off of VSTBY to ensure chip access during standby modes. A UVLO circuit prevents turn-on of this supply until VSTBY rises above its UVLO threshold. Both pins must be tied together at the chip.                                                                                                                                                                                        |  |

| 15, 22     | VAUXA, VAUXB       | $V_{AUX}[A/B]$ output voltages to PCI card slots: These outputs connect the VAUX pin of the PCI 2. 2 Connectors VSTBY via internal $400m\Omega$ MOSFETs which are current-limited and protected against short circuit faults.                                                                                                                                                                                                                                                                              |  |

| 44, 43     | ONA, ONB           | Enable input for MAIN outputs: Rising-edge sensitive. Used to enable or disable MAIN (5V, 3.3V, +12V, –12V) outputs. Taking ONA/ONB low after a fault resets the respective slot's Main Output Fault Latch. Tie these pins to ground if using SMBus-mode power control.                                                                                                                                                                                                                                    |  |

| Pin Number | Pin Name           | Pin Function                                                                                                                                                                                                                             |  |

|------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 36      | /FAULTA, /FAULTB   | Open Drain, Active-Low: Asserted whenever the circuit breaker trips due to a fault condition.                                                                                                                                            |  |

|            |                    | /FAULT[A/B] is reset by bringing the faulted slot's ON pin low if /FAULT was asserted in response to a fault condition on one of the slot's MAIN outputs(+12V, +5V, +3.3V, or -12V).                                                     |  |

|            |                    | /FAULT[A/B] is reset by bringing the faulted slot's AUXEN pin low if /FAULT was asserted in response to a fault condition on the slot's VAUX output.                                                                                     |  |

|            |                    | If a fault condition occurred on both the MAIN and AUX outputs of the same slot, then both ON and AUXEN must be brought low to de-assert the /FAULT output.                                                                              |  |

| 2, 35      | CFILTERA, CFILTERB | Filter Capacitor [A/B]: Capacitors connected between these pins and ground set the duration of $t_{\text{FLT}}$ . $t_{\text{FLT}}$ is the amount of time for which a slot remains incurrent-limit before its circuit breaker is tripped. |  |

| 37         | /INT               | Interrupt Output: Open Drain, Active-low. Asserted whenever a power faulti s detected. Cleared by writing a logic 1 to the respective active bit into the Status Register.                                                               |  |

| 48         | SDA                | SMBus Data: Bidirectional SMBus data line.                                                                                                                                                                                               |  |

| 47         | SCL                | SMBus Clock: Input.                                                                                                                                                                                                                      |  |

| 39, 40, 41 | A2, A1, A0         | SMBus Address Select pins: Connect to ground or leave open in order to program device SMBus base address. There is an internal pull-up to VSTBY on each of these inputs.                                                                 |  |

| 4, 38      | GPIA, GPIB         | General Purpose Inputs: The state of these inputs are available by reading the Common Status Register.                                                                                                                                   |  |

| 46         | GND                | Ground                                                                                                                                                                                                                                   |  |

# **Absolute Maximum Ratings**(1)

| Supply Voltage                                     |     |

|----------------------------------------------------|-----|

| (12V <sub>IN</sub> )+1                             | I4V |

| (12MV <sub>IN</sub> )1                             |     |

| (5V <sub>IN</sub> )+                               | -7V |

| (3V <sub>IN</sub> ), (V <sub>STBY</sub> )+         | -7V |

| Any Logic Output Voltage0.5 (min)/+5.5V (m         |     |

| Any Logic Input Voltage0.5 (min)/+5.5V (n          | nax |

| Output Current (FAILT[A/B]#, /INT, SDA)10          | mΑ  |

| Lead Temperature                                   |     |

| IR Reflow, Peak Temperature235 +5/-(               | )°C |

| Storage Temperature (T <sub>s</sub> )–65°C to +150 | )°C |

| ESD Rating <sup>(3)</sup> 2                        | 2kV |

# Operating Ratings<sup>(2)</sup>

| +11.65V to +12.6V |

|-------------------|

| –11.0V to –13.2V  |

| +4.85V to 5.25V   |

| +3.1V to +3.6V    |

| +3.15V to 3.6V    |

| 0°C to +70°C      |

| 125°C             |

|                   |

| 56.5°C/W          |

|                   |

# Electrical Characteristics<sup>(4)</sup>

$12V_{IN}$  = 12V;  $12MV_{IN}$  = -12V;  $5V_{IN}$  = 5V;  $3V_{IN}$  = 3.3V;  $V_{STBY}$  = 3.3V;  $T_A$  =  $0^{\circ}C$  to  $70^{\circ}C$ ; unless noted.

# **Power Control and Logic Sections**

| Symbol                    | Parameter                                                                                                          | Condition                                   | Min                   | Тур        | Max               | Units |

|---------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------|------------|-------------------|-------|

| I <sub>CC12</sub>         | Supply Current                                                                                                     |                                             |                       | 0.6        | 2.0               | mA    |

| I <sub>CC5</sub>          |                                                                                                                    |                                             |                       | 1.2        | 2.0               | mA    |

| I <sub>CC33</sub>         |                                                                                                                    |                                             |                       | 0.5        | 0.7               | mA    |

| I <sub>CC12M</sub>        |                                                                                                                    |                                             |                       | -1.0       | -2.0              | mA    |

| I <sub>CCVSBY</sub>       |                                                                                                                    |                                             |                       | 2.5        | 5.0               | mA    |

| V <sub>UVLO</sub>         | Under Voltage Lockout                                                                                              | 12V <sub>IN</sub> increasing                | 8                     | 9          | 10                | V     |

|                           |                                                                                                                    | 3V <sub>IN</sub> increasing                 | 2.2                   | 2.5        | 2.75              | V     |

|                           |                                                                                                                    | 5V <sub>IN</sub> increasing                 | 3.7                   | 4.0        | 4.3               | V     |

|                           |                                                                                                                    | 12MV <sub>IN</sub> increasing               | -10                   | <b>–</b> 9 | -8                | V     |

|                           |                                                                                                                    | V <sub>STBY</sub> increasing                | 2.8                   | 2.9        | 3.0               | V     |

| V <sub>HYSUV</sub>        | Under Voltage Lockout Hysteresis -<br>12V <sub>IN</sub> , 12MV <sub>IN</sub> , 5V <sub>IN</sub> , 3V <sub>IN</sub> |                                             |                       | 180        |                   | mV    |

| V <sub>HYSSTBY</sub>      | Under-voltage Lockout Hysteresis - V <sub>STBY</sub>                                                               |                                             |                       | 50         |                   | mV    |

| V <sub>UVTH</sub>         | Power Good Under-Voltage Thresholds                                                                                |                                             |                       |            |                   |       |

| $V_{\text{UVTH(12V)}}$    | 12V <sub>ОUТ</sub> [А/В]                                                                                           | 12V <sub>OUT</sub> [A/B] decreasing         | 10.2                  | 10.5       | 10.8              | V     |

| $V_{\text{UVTH(12MV)}}$   | 12MV <sub>OUT</sub> [A/B]                                                                                          | 12MV <sub>OUT</sub> [A/B] decreasing        | -10.8                 | -10.6      | -10.2             | V     |

| $V_{\text{UVTH(3V)}}$     | 3V <sub>OUT</sub> [A/B]                                                                                            | 3V <sub>OUT</sub> [A/B] decreasing          | 2.7                   | 2.8        | 2.9               | V     |

| $V_{\text{UVTH(5V)}}$     | 5V <sub>OUT</sub> [A/B]                                                                                            | 5V <sub>OUT</sub> [A/B] decreasing          | 4.4                   | 4.5        | 4.7               | V     |

| $V_{\text{UVTH(VAUX)}}$   | V <sub>AUX</sub> [A/B]                                                                                             | V <sub>AUX</sub> [A/B] decreasing           | 2.7                   | 2.8        | 2.9               | V     |

| V <sub>HYSPG</sub>        | Power-Good Detect Hysteresis                                                                                       |                                             |                       | 30         |                   | mV    |

| $V_{GATE}$                | 5V <sub>GATE</sub> /3V <sub>GATE</sub> Voltage                                                                     |                                             | 12V <sub>IN</sub> -15 |            | 12V <sub>IN</sub> | V     |

| I <sub>GATE(SOURCE)</sub> | 5V <sub>GATE</sub> /3V <sub>GATE</sub> Output Source                                                               | start cycle                                 | 15                    | 25         | 35                | μA    |

| I <sub>GATE(SINK</sub> )  | 5V <sub>GATE</sub> /3V <sub>GATE</sub> Output Sink Fault<br>Current                                                | any fault condition, V <sub>GATE</sub> = 5V |                       | 70         |                   | mA    |

| Symbol                    | Parameter                                                     | Condition                                                                | Min                                | Тур      | Max  | Units |

|---------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------|----------|------|-------|

| V <sub>FILTER</sub>       | C <sub>FILTER</sub> Threshold Voltage                         |                                                                          | 1.20                               | 1.25     | 1.30 | V     |

| I <sub>FILTER</sub>       | C <sub>FILTER</sub> [A/B] Charge Current                      | $V_{[5/3]}V_{IN} - V_{[5/3]}V_{SENSE} > V_{THILIMIT}$                    | 1.80                               | 2.5      | 5.0  | μA    |

| I <sub>SLEW</sub>         | 12V <sub>SLEW</sub> [A/B] Charge Current                      | During turn-on only                                                      | 13                                 | 22       | 35   | μΑ    |

| V <sub>THILIMIT</sub>     | Current Limit Threshold Voltages                              |                                                                          |                                    |          |      |       |

|                           | 5V[A/B] Supplies                                              | V <sub>5VIN</sub> - V <sub>5VSENSE</sub>                                 | 35                                 | 50       | 65   | mV    |

|                           | 3.3V[A/B] Supplies                                            | V <sub>3VIN</sub> - V <sub>3</sub> VSENSE                                | 35                                 | 50       | 65   | mV    |

| V <sub>THFAST</sub>       | 5V <sub>OUT</sub> [A/B] and 3V <sub>OUT</sub> [A/B]           | MIC2590B-2                                                               | 90                                 | 113      | 135  | mV    |

|                           | Fast-Trip Thresholds                                          | MIC2590B-5                                                               |                                    | Disabled |      |       |

| V <sub>IL</sub>           | LOW-Level Input Voltage                                       |                                                                          |                                    |          | 8.0  | V     |

|                           | (SCL,SDA,ON[A/B],A[0-2],GPI[A/B])                             |                                                                          |                                    |          |      |       |

| V <sub>OL</sub>           | Output LOW Voltage                                            | I <sub>OL</sub> = 3mA                                                    |                                    |          | 0.4  | V     |

|                           | /FAULT[A/B], /INT, SDA                                        |                                                                          |                                    |          |      |       |

| V <sub>IH</sub>           | HIGH-Level Input Voltage                                      |                                                                          | 2.1                                |          |      | V     |

|                           | SCL,SDA,ON[A/B],A[0-2],                                       |                                                                          |                                    |          |      |       |

|                           | AUXEN[A/B],GPI[A/B])                                          |                                                                          |                                    |          |      |       |

| R <sub>PULL-UP</sub>      | Internal Pullups from A[0-2] to V <sub>STBY</sub>             |                                                                          |                                    | 40       |      | kΩ    |

| I <sub>IL</sub>           | Input Leakage Current                                         |                                                                          |                                    |          | ±5   | μΑ    |

|                           | SCL, ON[A/B],AUXEN[A/B], GP[A/B])                             |                                                                          |                                    |          |      |       |

| I <sub>LKG(OFF)</sub>     | Off-State Leakage Current                                     |                                                                          |                                    |          | ±5   | μA    |

|                           | SDA,/FAULT[A/B],/INT                                          |                                                                          |                                    |          |      |       |

| T <sub>OV</sub>           | Overtemperature Shutdown & Reset                              | T <sub>J</sub> Increasing, each slot, <b>Note 5</b>                      |                                    | 140      |      | °C    |

|                           | Thresholds, with overcurrent on slot                          | T <sub>J</sub> Decreasing, each slot, <b>Note 5</b>                      |                                    | 130      |      | °C    |

|                           | Overtemperature Shutdown & Reset                              | T <sub>J</sub> Increasing, both slots, <b>Note 5</b>                     |                                    | 160      |      | °C    |

|                           | Thresholds, all other conditions (all outputs will latch OFF) | T <sub>J</sub> Decreasing, both slots, <b>Note 5</b>                     |                                    | 150      |      | °C    |

| $R_{\text{OUT(ON)}}$      | Output MOSFET Resistance                                      |                                                                          |                                    |          |      |       |

| R <sub>OUT(12V)</sub>     | 12V MOSFET                                                    | I <sub>DS</sub> = 500mA, T <sub>J</sub> = 125°C                          |                                    |          | 500  | mΩ    |

| $R_{OUT(12MV)}$           | -12V MOSFET                                                   | I <sub>DS</sub> = 100mA, T <sub>J</sub> = 125°C                          |                                    |          | 2    | Ω     |

| $R_{OUT(AUX)}$            | V <sub>AUX</sub> MOSFET                                       | I <sub>DS</sub> = 375mA, T <sub>J</sub> = 125°C                          |                                    |          | 400  | mΩ    |

| $V_{OFF}$                 | Off-State Output Offset Voltage                               |                                                                          |                                    |          |      |       |

| $V_{OFF(+12V)}$           | 12V <sub>OUT</sub> [A/B]                                      | $12V_{OUT}[A/B] = Off, T_J = 125^{\circ}C$                               |                                    |          | 50   | mV    |

| $V_{OFF(-12V)}$           | 12MV <sub>OUT</sub> [A/B]                                     | $12MV_{OUT}[A/B] = Off, T_J = 125^{\circ}C$                              | -50                                |          |      | mV    |

| $V_{OFF(AUX)}$            | V <sub>AUX</sub> [A/B]                                        | $V_{AUX}[A/B] = Off, T_J = 125^{\circ}C$                                 |                                    |          | 50   | mV    |

| I <sub>THSLOW</sub>       | Current Limit Threshold                                       |                                                                          |                                    |          |      |       |

| I <sub>LIM(12)</sub>      | 12V MOSFET                                                    | 12V <sub>OUT</sub> [A/B] = 0V                                            | 0.52                               | 1.0      | 1.5  | Α     |

| I <sub>LIM(12M)</sub>     | –12V MOSFET                                                   | 12MV <sub>OUT</sub> [A/B] = 0V                                           | -0.11                              | -0.2     | -0.3 | Α     |

| I <sub>THFAST</sub>       | Fast-Trip Thresholds                                          | 12V <sub>OUT</sub> [A/B] (MIC2590B-2)                                    | 1.0                                | 2.15     | 3.0  | Α     |

|                           |                                                               | 12MV <sub>OUT</sub> [A/B] (MIC2590B-2)                                   | -0.20                              | -0.45    | -0.6 | Α     |

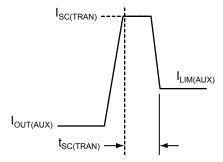

| I <sub>AUX</sub> (THRESH) | Auxiliary Output Current Limit Threshold Figure 4             | Current which must be drawn from V <sub>AUX</sub> to register as a fault |                                    | 0.84     |      | Α     |

| I <sub>SC(TRAN)</sub>     | Maximum Transient Short Circuit Current                       | V <sub>AUX</sub> Enabled, then Grounded                                  | $I_{MAX} = V_{STBY} / R_{DS(AUX)}$ |          | Α    |       |

| Symbol                     | Parameter                                                                            | Condition                                                                                 | Min   | Тур  | Max  | Units |

|----------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------|------|------|-------|

| I <sub>LIM(AUX)</sub>      | Regulated Current after Transient                                                    | From end of $I_{SC(TRAN)}$ to $C_{FILTER}$ Time Out                                       | 0.375 | 0.7  | 1.35 | Α     |

| R <sub>DISCH</sub>         | Output Discharge Resistance                                                          |                                                                                           |       |      |      |       |

| R <sub>(12V)</sub>         | 12V <sub>OUT</sub> [A/B]                                                             | 12V <sub>OUT</sub> [A/B] = 6.0V                                                           |       | 1600 |      | Ω     |

| R <sub>(12MV)</sub>        | 12MV <sub>OUT</sub> [A/B]                                                            | $12MV_{OUT}[A/B] = -6.0V$                                                                 |       | 600  |      | Ω     |

| R <sub>(3V)</sub>          | 3V <sub>OUT</sub> [A/B]                                                              | 3V <sub>OUT</sub> [A/B] = 1.65V                                                           |       | 150  |      | Ω     |

| R <sub>(5V)</sub>          | 5V <sub>OUT</sub> [A/B]                                                              | 5MV <sub>OUT</sub> [A/B] = 2.5V                                                           |       | 150  |      | Ω     |

| R <sub>(3VAUX)</sub>       | 3V <sub>AUX</sub> [A/B]                                                              | 5V <sub>OUT</sub> [A/B] = 1.65V                                                           |       | 430  |      | Ω     |

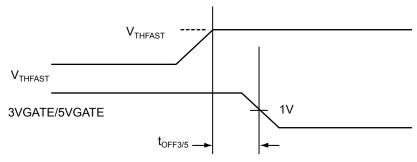

| t <sub>OFF(3)</sub>        | Current Limit Response Time for 3.3V and 5V Outputs, <b>Figure 2</b>                 | MIC2590B-2 with $C_{GATE} = 10nF$ ,<br>$V_{IN} - V_{SENSE} = 200mV$                       |       | 1    |      | μs    |

| T <sub>SC(TRAN)</sub>      | V <sub>AUX</sub> Current Limiter Response Time, <b>Figure 5</b>                      | V <sub>AUX</sub> [A/B] = 0V, <b>Note 5</b>                                                |       | 33   |      | μs    |

| t <sub>OFF(12)</sub>       | 12V Current Limit Response Time,<br>Figure 3                                         | 12V <sub>OUT</sub> [A/B] = 0V, <b>Note 5</b>                                              |       | 1    |      | μs    |

| t <sub>OFF(12M)</sub>      | -12V Current Limit Response Time, Figure 3                                           | 12MV <sub>OUT</sub> [A/B] = 0V, <b>Note 5</b>                                             |       | 1    |      | μs    |

| T <sub>PROP(3VFAULT)</sub> | Delay from 3V[A/B] overcurrent-limit to FAULT Output                                 | MIC2590B-2, V <sub>SENSE</sub> – V <sub>THLIMIT</sub> = 200mV, C <sub>FILTER</sub> = open |       | 1    |      | μs    |

| T <sub>PROP(5VFAULT)</sub> | Delay from 5V[A/B] overcurrent-limit to FAULT Output                                 | MIC2590B-2, V <sub>SENSE</sub> – V <sub>THLIMIT</sub> = 200mV, C <sub>FILTER</sub> = open |       | 1    |      | μs    |

| t <sub>W</sub>             | ON[A/B], AUXEN[A/B] Pulse Width                                                      | Note 5                                                                                    |       | 100  |      | ns    |

| t <sub>POR</sub>           | MIC2590B Power-On Reset Time after VSTBY becomes valid                               | Note 5                                                                                    |       |      | 500  | μs    |

| 8-Bit Analog to            | o Digital Converter                                                                  | •                                                                                         |       | 1    | •    | •     |

|                            | Total Unadjusted Error Voltage,                                                      |                                                                                           |       |      |      |       |

|                            | All Outputs                                                                          |                                                                                           | -3    |      | +3   | %     |

|                            | Current, 3V <sub>OUT</sub> [A/B]/5V <sub>OUT</sub> [A/B]                             | Measured as voltage across                                                                | -3    |      | +3   | %     |

|                            | Current, V <sub>AUX</sub> [A/B], 12V <sub>OUT</sub> [A/B], 12MV <sub>OUT</sub> [A/B] | corresponding external R <sub>SENSE</sub>                                                 |       | ±3   |      | %     |

| t <sub>CONV</sub>          | Conversion Time                                                                      |                                                                                           |       | 60   | 100  | ms    |

|                            | Resolution Specifications:                                                           |                                                                                           |       |      |      |       |

| $V_{AUXA}$                 | Full Scale Voltage                                                                   |                                                                                           |       | 3.85 |      | V     |

| $V_{AUXB}$                 | LSB of Voltage                                                                       |                                                                                           |       | 15.1 |      | mV    |

|                            | Full Scale Current                                                                   |                                                                                           |       | 375  |      | mA    |

|                            | LSB of Current                                                                       |                                                                                           |       | 1.47 |      | mA    |

| 3V <sub>OUTA</sub>         | Full Scale Voltage                                                                   |                                                                                           |       | 3.85 |      | V     |

| 3V <sub>OUTB</sub>         | LSB of Voltage                                                                       |                                                                                           |       | 15.1 |      | mV    |

|                            | Full Scale Current                                                                   | External $R_{SENSE} = 6.00 \text{m}\Omega$                                                |       | 11.6 |      | Α     |

|                            | LSB of Current                                                                       |                                                                                           |       | 45.5 |      | mA    |

| 5V <sub>OUTA</sub>         | Full Scale Voltage                                                                   |                                                                                           |       | 5.89 |      | V     |

| 5V <sub>OUTB</sub>         | LSB of Voltage                                                                       |                                                                                           |       | 23.1 |      | mV    |

|                            | Full Scale Current                                                                   | External $R_{SENSE} = 6.00 \text{m}\Omega$                                                |       | 6.96 |      | Α     |

|                            | LSB of Current                                                                       |                                                                                           |       | 27.3 |      | mA    |

| Symbol               | Parameter                          | Condition                 | Min | Тур   | Max | Units |

|----------------------|------------------------------------|---------------------------|-----|-------|-----|-------|

| 12V <sub>OUTA</sub>  | Full Scale Voltage                 |                           |     | 13.8  |     | V     |

| 12V <sub>OUTB</sub>  | LSB of Voltage                     |                           |     | 54.1  |     | mV    |

|                      | Full Scale Current                 |                           |     | 6.96  |     | mA    |

|                      | LSB of Current                     |                           |     | 27.3  |     | mA    |

| 12MV <sub>OUTA</sub> | Full Scale Voltage                 |                           |     | -13.6 |     | V     |

| 12MV <sub>OUTB</sub> | LSB of Voltage                     |                           |     | 53.5  |     | mV    |

|                      | Full Scale Current                 |                           |     | 100   |     | mA    |

|                      | LSB of Current                     |                           |     | 0.392 |     | mA    |

| SMBus Timir          | ng, Note 5                         |                           |     | •     |     |       |

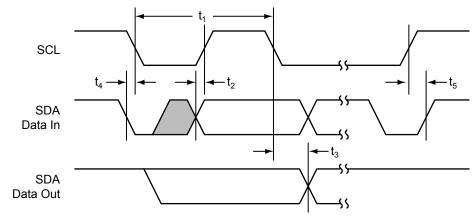

| t <sub>1</sub>       | SCL (Clock) Period                 | Figure 1                  | 2.5 |       |     | μs    |

| t <sub>2</sub>       | Data In Set-Up Time to SCL HIGH    | Figure 1                  | 100 |       |     | ns    |

| t <sub>3</sub>       | Data Out Stable after SCL LOW      | Figure 1                  | 300 |       |     | ns    |

| t <sub>4</sub>       | Data LOW Set-Up Time to SCL LOW    | Start Condition, Figure 1 | 100 |       |     | ns    |

| t <sub>5</sub>       | Data HIGH Hold Time after SCL HIGH | Start Condition, Figure 1 | 100 |       |     | ns    |

## Notes:

- 1. Exceeding the absolute maximum rating may damage the device.

- 2. The device is not guaranteed to function outside its operating rating.

- 3. Devices are ESD sensitive. Handling precautions recommended. Human body model,  $1.5k\Omega$  in series with 100pF.

- 4. See Applications section.

- 5. Parameters guaranteed by design. Not 100% production tested.

# **Test Circuit**

Figure 1. SMBus Timing

Figure 2. 3V/5V Current Limit Response Timing

Figure 3. +12V/-12V Current Limit Response Timing

Figure 4. VAUX Current Limit Threshold

Figure 5. VAUX Current Limit Response Timing

# **Functional Description**

#### **Hot Swap Insertion**

When circuit boards are inserted into systems carrying live supply voltages ("hot plugged"), high inrush currents often result due to the charging of bulk capacitance that resides across the circuit board's supply pins. This transient inrush current can cause the system's supply voltages to temporarily go out of regulation, causing data loss or system lock-up. In more extreme cases, the transients occurring during a hot plug event may cause permanent damage to connectors or on-board components.

The MIC2590B addresses these issues by limiting the inrush currents to the load (PCI Board), and thereby controlling the rate at which the load's circuits turn on. In addition, the MIC2590B offers input and output voltage supervisory functions and current-limiting to provide robust protection for both the host system and the PCI board.

### **System Interfaces**

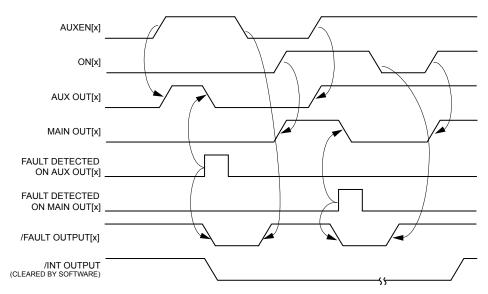

The MIC2590B employs two system interfaces. One is the hot plug Interface (HPI) which includes ON[A/B], AUXEN[A/B], and /FAULT[A/B]. The other is the System Management Interface (SMI) consisting of SDA, SCL and /INT, (whose signals conform to the specifications and format of Intel's SMBus standard). The MIC2590B can be operated exclusively from the SMI, or can employ the HPI for power control while continuing to use the SMI for access to all but the power control registers.

In addition to the basic power control features of the MIC2590B accessible by the HPI, the SMI also gives the host access to the following information from the part:

- Output voltage from each supply.

- 2. Output current from each supply.

- 3. Fault conditions occurring on each supply.

When using the System Management Interface for power control, do not use the hot plug Interface. Conversely, when using the HPI for power control, do not execute power control commands over the SMI bus (all other register accesses via the SMI bus remain permissible while in the HPI control mode). Note that if power control is performed via the SMIbus, the AUXENA, AUXENB, ONA and ONB pins should be tied to ground.

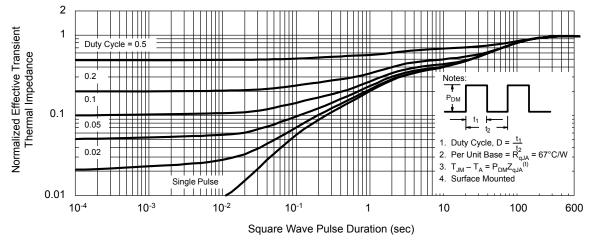

## Power-On Reset and Power Cycling

The MIC2590B utilizes  $V_{STBY}$  as the main supply input source. It is required for proper operation of the MIC2590B SMBus, registers and ADC and must be applied at all times. A Power-On Reset (POR) cycle is initiated after  $V_{STBY}$  rises above its UVLO threshold and remains valid at that voltage for 500 $\mu$ s. All internal registers except RESULT are cleared after POR. If  $V_{STBY}$  is recycled the MIC2590B enters a new power-on reset cycle.  $V_{STBY}$  must be the first supply input applied.

Following the POR interval, the MAIN supply inputs of  $12V_{IN}$ ,  $12MV_{IN}$ ,  $5V_{IN}$  and  $3V_{IN}$  may be applied in any order. The SMBus is ready for access at the end of the POR interval. During  $t_{POR}$  all outputs are off.

## **Power-Up Cycle (See Typical Application Circuit)**

When a slot is off, the 5V<sub>GATE</sub> and 3V<sub>GATE</sub> pins are held low with an internal pull-down current source. When a slot's main outputs are enabled, and all input voltages are above their respective undervoltage lockout thresholds, all four main supplies execute a controlled turn on. At this time, the GATE voltages of the 5V and 3.3V MOSFETs are ramped at a controlled rate from 0V to approximately 11.5V. This is sufficient to fully enhance the external MOSFETs for lowest possible DC losses. The ramp rate is controlled by 25µA (typ.) current sources from the GATE pins charging each C<sub>GATE</sub>. The magnitude and slew rate of the output current is proportional to the value of C<sub>GATE</sub> and the load capacitance. The minimum value of C<sub>GATE</sub> is selected to ensure that during start-up the load current does not exceed the current-limit threshold. The following equation is used to determine the value of C<sub>GATE</sub> (min):

$$C_{GATE}(min) = \frac{I_{GATE}}{I_{LIM}} \times C_{LOAD}$$

Where  $C_{LOAD}$  is the load capacitance connected to the 3.3V and 5V outputs and  $I_{LIM}$  and  $I_{GATE}$  are respectively the current-limit and gate charge current specifications as given in the Electrical Characteristics table. The output slew rate dv/dt is computed by:

$$dv/dt(load) = \frac{I_{GATE}}{C_{GATE} \times 10^6}$$

| I <sub>SLEW</sub> = 25μA |              |  |  |  |  |

|--------------------------|--------------|--|--|--|--|

| C <sub>GATE</sub>        | dv/dt (load) |  |  |  |  |

| 0.001µF                  | 25000V/s     |  |  |  |  |

| 0.01μF                   | 2500V/s      |  |  |  |  |

| 0.1µF                    | 250V/s       |  |  |  |  |

| 1μF                      | 25V/s        |  |  |  |  |

Table 1. 3.3V/5V Output Slew Rate Selection

For the +12V and -12V supplies, the output slew rate is controlled by capacitors connected to the  $12V_{SLEWA}$  and  $12V_{SLEWB}$  pins. To determine the minimum value of the slew rate capacitor, ( $C_{SLEW}$ ), connected to  $12V_{SLEW}$ [A/B], the following equation is used:

$$C_{SLEW} (min) = \frac{I_{SLEW}}{I_{LIM}} \times C_{LOAD}$$

where  $C_{\text{LOAD}}$  is the load capacitance connected to the +12V and -12V outputs, and  $I_{\text{LIM}}$  and  $I_{\text{SLEW}}$  are respectively the current-limit and slew rate charge current values found in the Electrical Characteristics table. The

equation above computes the minimum value to guarantee the device does not enter into current limit. The slew rate dv/dt is computed by:

$$dv/dt \text{ at load} = \frac{I_{SLEW}}{C_{SLEW} \times 10^6}$$

By appropriate selection of the value of  $C_{SLEW}$ , it can be ensured that the magnitude of the inrush current never exceeds the current limit for a given load capacitance. Since one capacitor fixes the slew rate for both +12V and -12V, the capacitor value should be chosen to provide the slower slew rate of the two. Table 2 depicts the output slew rate for various values of  $C_{SLEW}$ .

| $I_{SLEW} = 25\mu A$ |              |  |  |  |  |

|----------------------|--------------|--|--|--|--|

| C <sub>GATE</sub>    | dv/dt (load) |  |  |  |  |

| 0.001µF              | 22000V/s     |  |  |  |  |

| 0.01µF               | 2200V/s      |  |  |  |  |

| 0.1µF                | 220V/s       |  |  |  |  |

| 1µF                  | 22V/s        |  |  |  |  |

Table 2. ±12V Output Slew Rate Selection

#### **Power Down Cycle**

When a slot is turned off, internal switches are connected to each of the outputs to discharge the PCI board's bypass capacitors to ground.

#### Standby Mode

Standby mode is entered when any one (or more) enabled MAIN supply input(s) (12V<sub>IN</sub>, 12MV<sub>IN</sub>, 5V<sub>IN</sub> and 3V<sub>IN</sub>) drops below its respective UVLO threshold. The MIC2590B supplies two 3.3V auxiliary outputs, VALIX[A/B], satisfying PCI 2.2 specifications. These outputs are fed via the V<sub>STBY</sub> input, and controlled by the AUXEN[A/B] inputs or via their SMI bus Control Registers. These outputs are independent of the MAIN outputs: should one or more of the MAIN supply inputs move below its UVLO thresholds,  $V_{AUX}[A/B]$  still function as long as  $V_{STBY}$  is present. Prior to entering standby mode, ONA and ONB (or the MAINA and MAINB bits in the Control Registers) inputs should be de-asserted. If this is not done, the MIC2590B will assert /FAULT, and also /INT if interrupts enabled, when the MIC2590B detects undervoltage condition on a supply input.

#### **Circuit Breaker Functions**

The MIC2590B provides an electronic circuit breaker function that protects against excessive loads such as short circuits at each supply. When the current from one or more of a slot's MAIN outputs exceeds the current limit threshold (50mV/R<sub>SENSE</sub> for 3.3V and 5V, 1.0A for +12V, and/or 0.2Afor –12V) for a duration greater than  $t_{\rm FLT}$ , the circuit breaker is tripped and all MAIN supplies (all outputs except  $V_{\rm AUX}[A/B]$ ) are shut off. Should the load current exceed  $I_{\rm THFAST}$  (+12V and –12V), or cause a MAIN

output's  $V_{\text{SENSE}}$  to exceed  $V_{\text{THFAST}}$  (+3.3V and +5V), the outputs are shut off with no delay. Undervoltage conditions on the MAIN supply inputs also trip the circuit breaker, but only when the MAIN outputs are enabled (to signal a supply input brown-out condition).

The  $V_{AUX}[A/B]$  outputs have their own separate circuit breaker functions.  $V_{AUX}$  [A/B] do not incorporate a fast-trip threshold, but instead regulate the output current into a fault to avoid exceeding their operating current limit. The circuit breaker will trip due to overcurrents on  $V_{AUX}$  [A/B] when the fault timer expires. This use of the  $t_{FLT}$  timer prevents the circuit breaker from tripping prematurely due to brief current transients.

Following a fault condition, the outputs can be turned on again via the ON inputs (if the fault occurred on one of the MAIN outputs), via the AUXEN inputs (if the fault occurred on the AUX outputs), or by cycling both ON and AUXEN (if faults occurred on both the MAIN and AUX outputs). A fault condition can alternatively be cleared under SMI control of the ENABLE bits in the  $C_{NTRL}[A/B]$  registers. When the circuit breaker trips, /FAULT[A/B] will be asserted if the outputs were enabled through the hot plug Interface (non-SMI mode) inputs. At the same time, /INT will be asserted (unless interrupts are masked). Note that /INT is de-asserted by writing a logic 1 back into the respective fault bit position(s) in the STAT[A/B] register or the Common Status Register.

$t_{\text{FLT}}$  is set by external capacitors,  $C_{\text{FIL}}[A/B]$ , connected to the  $C_{\text{FILTER}}[A/B]$  pins. The equation below can be used to determine the capacitor value for a given duration of  $t_{\text{FLT}}$ :

$$C_{FIL} \cong 2.0 \mu. \times \left( \frac{t_{FLT}}{1 \text{second}} \right)$$

#### **Thermal Shutdown**

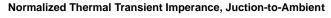

The internal +12V, -12V and VAUX MOSFETs are protected against damage not only by current limiting, but by dual-mode over-temperature protection as well. Each slot controller on the MIC2590B is thermally isolated from the other. Should an overcurrent condition raise the junction temperature of one slot's controller and internal pass elements to 140°C, all of the outputs for that slot (including V<sub>AUX</sub>) will be shut off, and the slot's /FAULT output will be asserted. The other slot's operation will remain unaffected. However, should the MIC2590B's overall die temperature exceed 160°C, both slots (all outputs, including  $V_{\text{AUXA}}$  and  $V_{\text{AUXB}}$ ) will be shut off, whether or not a current-limit condition exists. A 160°C overtemperature condition additionally overtemperature bit (OT INT) in the Common Status Register.

## A/D Converter

The MIC2590B has a 20-channel, 8-bit A/D converter capable of monitoring the output voltage and current of each supply. This information is available via the System Management Interface. The information is particularly

intended for use by systems that support the IPMI standard, but may be used for any desired purpose.

## **Interrupt Generation**

In the MIC2590B, the /INT pin can be asserted (driven low) whenever a fault condition trips the circuit breaker. The MIC2590B can thus operate in either polled mode or interrupt mode. In the polled mode, the Interrupt Mask bit in the Common Status Register should be set, to prevent the /INT pin from being asserted. Upon a circuit breaker fault event the appropriate status bit is also set in the corresponding status registers. In order to clear the status bit the system must write a logic 1 back to same bit in the status register. Upon occurrence of the write the /INT pin will be de-asserted (if interrupts were enabled), if no other interrupts are pending. This method of "echo reset" allows data to be retained in the status registers until such time as the system software is ready to deal with that data, and then to control the earliest time at which the next interrupt might occur.

### System Management Interface (SMI)

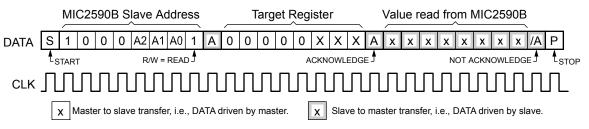

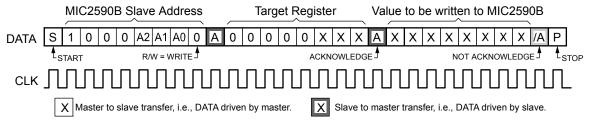

The MIC2590B's System Management Interface uses the Read\_Byte and Write\_Byte subset of the SMBus protocols to communicate with its host via the System Management Interface bus. Additionally, the /INT output signals the controlling processor that one or more events need attention, if an interrupt-driven architecture is used. Note that theMIC2590B does not participate in the SMBus Alert Response Address (ARA) portion of the SMBus protocol.

The SMBus Read\_Byte operation consists of sending the device's slave address, followed by the target register's internal address, and then clocking out the byte to be read

from the target register. Similarly, the Write\_Byte operation consists of sending the device's slave address, followed by the target register's internal address, and then clocking in the byte to be written to the target register. The target register addresses for the MIC2590B are given in Table 4.

### MIC2590B SMBus Address Configuration

The MIC2590B responds to its own unique address which is assigned using A2, A1 and A0. These represent the 3 LSBs of its 7-bit address, as shown in Table 3. These address bits are assigned only during power up of the  $V_{STBY}$  supply input. These three bits allow up to eight MIC2590B devices in a single system. These pins are either grounded or left unconnected to specify a logical 0 or 1 respectively. A pin designated as a logical 1 may also be pulled up to  $V_{STBY}$ .

|    | Inputs | 1  | MIC2590B Sla          | ve Addresses    |

|----|--------|----|-----------------------|-----------------|

| A2 | A1     | A0 | Binary                | Hex             |

| 0  | 0      | 0  | 1000 000 <sub>b</sub> | 80 <sub>h</sub> |

| 0  | 0      | 1  | 1000 001 <sub>b</sub> | 82 <sub>h</sub> |

| 0  | 1      | 0  | 1000 010 <sub>b</sub> | 84 <sub>h</sub> |

| 0  | 1      | 1  | 1000 011 <sub>b</sub> | 86 <sub>h</sub> |

| 1  | 0      | 0  | 1000 100 <sub>b</sub> | 88 <sub>h</sub> |

| 1  | 0      | 1  | 1000 101 <sub>b</sub> | 8A <sub>h</sub> |

| 1  | 1      | 0  | 1000 110 <sub>b</sub> | 8C <sub>h</sub> |

| 1  | 1      | 1  | 1000 111 <sub>b</sub> | 8E <sub>h</sub> |

Table 3. MIC2590B SMBus Addressing

Figure 6. Hot Plug Interface Mode Operation

Figure 7. READ\_BYTE Protocol

Figure 8. WRITE\_BYTE Protocol

## Register Set and Programmer's Model

| Tar     |                                   | mon<br>Value    | Power-On<br>Default |                 |

|---------|-----------------------------------|-----------------|---------------------|-----------------|

| Label   | Description                       | Read            | Write               |                 |

| RESULT  | ADC Conversion<br>Result Register | 00h             | n/a                 | n/a             |

| ADCNTRL | ADC Control<br>Register           | 01 <sub>h</sub> | 01 <sub>h</sub>     | 00 <sub>h</sub> |

| CNTRLA  | Control Register<br>Slot A        | 02 <sub>h</sub> | 02 <sub>h</sub>     | 00 <sub>h</sub> |

| CNTRLB  | Control Register<br>Slot B        | 03 <sub>h</sub> | 03 <sub>h</sub>     | 00 <sub>h</sub> |

| STATA   | Slot A Status                     | 04 <sub>h</sub> | 04 <sub>h</sub>     | 00 <sub>h</sub> |

| STATB   | Slot B Status                     | 05 <sub>h</sub> | 05 <sub>h</sub>     | 00 <sub>h</sub> |

| STAT    | Common Status<br>Register         | 06 <sub>h</sub> | 06 <sub>h</sub>     | 00 <sub>h</sub> |

## **Detailed Register Descriptions below:**

| Conversion Result Register (RESULT), 8-Bits Read Only |                   |                   |                   |                   |                   |                   |                   |

|-------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| D[7]<br>read-only                                     | D[6]<br>read-only | D[5]<br>read-only | D[4]<br>read-only | D[3]<br>read-only | D[2]<br>read-only | D[1]<br>read-only | D[0]<br>read-only |

| Voltage or Current Data from ADC                      |                   |                   |                   |                   |                   |                   |                   |

| Bit    | Function              | Operation |

|--------|-----------------------|-----------|

| D[7:0] | Measure data from ADC | Read Only |

Power-Up Default Value: Undefined following POR Read Command Byte: Undefined  $0000 \ 0000_b = 00_h$

| (AI               | (ADC Control Register ADCNTRL), 8-Bits Read/Write |                   |                        |                        |                        |                        |                        |

|-------------------|---------------------------------------------------|-------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| D[7]<br>read-only | D[6]<br>read-only                                 | D[5]<br>read-only | D[4]<br>read-<br>write | D[3]<br>read-<br>write | D[2]<br>read-<br>write | D[1]<br>read-<br>write | D[0]<br>read-<br>write |

| Busy              | Reserved                                          | Reserved          | SEL                    | PAR                    |                        | pply Sel<br>SUP[2:0    |                        |

| Bit(s)   | Function                                 | Operation                                                                                                                    |

|----------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| BUSY     | ADC Status                               | 0 = ADC Quiescent<br>1 = ADC Busy                                                                                            |

| D[6]     | Reserved                                 | Always Read as Zero                                                                                                          |

| D[5]     | Reserved                                 | Always Read as Zero                                                                                                          |

| SEL      | A/D Slot Select                          | Specifies Channel for A/D Conversion 0 = Slot A 1 = Slot B                                                                   |

| PAR      | Parameter Control Bit for ADC Conversion | 0 = Current<br>1 = Voltage                                                                                                   |

| SUP[2:0] | Supply Select for ADC<br>Conversion      | 000 = No Conversion<br>001 = 3.3V Supply<br>010 = 5.0V Supply<br>011 = +12V Supply<br>100 = -12V Supply<br>101 = VAUX Supply |

Power-Up Default Value:  $0000\ 0000_b = 00_h$ Command Byte (R/W):  $0000\ 0001_b = 01_h$

To operate the ADC the ADCNTRL register must first be initialized by selecting a slot, specifying whether voltage or current is to be measured and then specifying the specific supply that is to be monitored. The software must then wait 100ms, or poll the BUSY bit until it is zero. The RESULT register will then contain the valid result of the conversion.

| Control Register, Slot A (CNTRLB), 8-Bits Read/Write |                   |                   |                   |                   |                   |                    |                    |

|------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| D[7]<br>read-only                                    | D[6]<br>read-only | D[5]<br>read-only | D[4]<br>read-only | D[3]<br>read-only | D[2]<br>read-only | D[1]<br>read-write | D[0]<br>read-write |

| AUXAPG                                               | MAINAPG           | Reserved          | Reserved          | Reserved          | Reserved          | MAINA              | AUXA               |

| Bit(s)  | Function                                  | Operation                                                                       |

|---------|-------------------------------------------|---------------------------------------------------------------------------------|

| AUXAPG  | AUX Output Power-<br>Good Status, Slot A  | 1 = Power-Good<br>(VAUXA output is<br>above its V <sub>UVTH</sub><br>threshold) |

| MAINAPG | MAIN Output Power-<br>Good Status, Slot A | 1 = Power-Good<br>(MAINA output is<br>above its V <sub>UVTH</sub><br>threshold) |

| D[5]    | Reserved                                  | Always Read as Zero                                                             |

| D[4]    | Reserved                                  | Always Read as Zero                                                             |

| D[3]    | Reserved                                  | Always Read as Zero                                                             |

| D[2]    | Reserved                                  | Always Read as Zero                                                             |

| MAINA   | MAIN Enable Control,<br>Slot A            | 0 = OFF, 1 = ON                                                                 |

| VAUXA   | VAUX Enable Control,<br>Slot A            | 0 = OFF, 1 = ON                                                                 |

Power-Up Default Value:  $0000\ 0000_b = 00_h$ Command Byte (R/W):  $0000\ 0010_b = 02_h$

The power-up default value is 00h. Slot A is disabled upon power-up, i.e., all supply outputs are off.

| Control Register, Slot B (CNTRLB), 8-Bits Read/Write |                   |                   |                   |                   |                   |                    |                    |

|------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| D[7]<br>read-only                                    | D[6]<br>read-only | D[5]<br>read-only | D[4]<br>read-only | D[3]<br>read-only | D[2]<br>read-only | D[1]<br>read-write | D[0]<br>read-write |

| AUXBPG                                               | MAINBPG           | Reserved          | Reserved          | Reserved          | Reserved          | MAINB              | AUXB               |

| Bit(s)  | Function                                  | Operation                                                                       |

|---------|-------------------------------------------|---------------------------------------------------------------------------------|

| AUXBPG  | AUX Output Power-<br>Good Status, Slot B  | 1 = Power-Good<br>(VAUXB output is<br>above its V <sub>UVTH</sub><br>threshold) |

| MAINBPG | MAIN Output Power-<br>Good Status, Slot B | 1 = Power-Good<br>(MAINB output is<br>above its V <sub>UVTH</sub><br>threshold) |

| D[5]    | Reserved                                  | Always Read as Zero                                                             |

| D[4]    | Reserved                                  | Always Read as Zero                                                             |

| D[3]    | Reserved                                  | Always Read as Zero                                                             |

| D[2]    | Reserved                                  | Always Read as Zero                                                             |

| MAINB   | MAIN Enable Control,<br>Slot B            | 0 = OFF, 1 = ON                                                                 |

| VAUXB   | VAUX Enable Control,<br>Slot B            | 0 = OFF, 1 = ON                                                                 |

Power-Up Default Value:  $0000\ 0000_b = 00_h$ Command Byte (R/W):  $0000\ 0011_b = 03_h$

The power-up default value is 00h. Slot B is disabled upon power-up, i.e., all supply outputs are off.

| Status Register, Slot A (STATA), 8-Bits Read Only |                   |                   |                        |                        |                        |                        |                        |

|---------------------------------------------------|-------------------|-------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| D[7]<br>read-only                                 | D[6]<br>read-only | D[5]<br>read-only | D[4]<br>read-<br>write | D[3]<br>read-<br>write | D[2]<br>read-<br>write | D[1]<br>read-<br>write | D[0]<br>read-<br>write |

| FAULTA                                            | MAINA             | VAUXA             | VAUXAF                 | 12MVAF                 | 12VAF                  | 5VAF                   | 3VAF                   |

| Bit(s) | Function                         | Operation                                                                                                                                                         |

|--------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FALUTA | FAULT Pin Status, Slot<br>A      | Notes 1 & 2                                                                                                                                                       |

| MAINA  | MAIN Enable Status,<br>Slot A    | Represents actual<br>state (on/off) of the<br>four main power<br>outputs for Slot A.<br>(+12V, +5V, +3.3V<br>and -12V)<br>1 = MAIN Power On<br>0 = MAIN Power Off |

| VAUXA  | VAUX Enable Status,<br>Slot A    | Represents actual<br>state (on/off) of the<br>auxiliary power<br>outputs for Slot A.<br>1 = MAIN Power On<br>0 = MAIN Power Off                                   |

| VAUXFA | Overcurrent Fault VAUX Supply    | 1 = Fault<br>0 = No Fault                                                                                                                                         |

| 12MVFA | Overcurrent Fault<br>-12V Supply | 1 = Fault<br>0 = No Fault                                                                                                                                         |

| 12VFA  | Overcurrent Fault<br>12V Supply  | 1 = Fault<br>0 = No Fault                                                                                                                                         |

| 5VFA   | Overcurrent Fault 5V Supply      | 1 = Fault<br>0 = No Fault                                                                                                                                         |

| 3VFA   | Overcurrent Fault 3V Supply      | 1 = Fault<br>0 = No Fault                                                                                                                                         |

Power-Up Default Value:  $0000\ 0000_b = 00_h$ Read Command Byte (R/W):  $0000\ 0100_b = 04_h$

The power-up default value is 00h. The slot is disabled upon power-up, i.e., all supply outputs are off. In response to an overcurrent fault condition, writing a logical 1 back into the active (or set) bit position will clear the bit and deassert /INT. The status of the /FAULTA pin is not affected by reading the Status Register.

| Status Register, Slot B (STATB), 8-Bits Read Only |                   |                   |                        |                        |                        |                        |                        |

|---------------------------------------------------|-------------------|-------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| D[7]<br>read-only                                 | D[6]<br>read-only | D[5]<br>read-only | D[4]<br>read-<br>write | D[3]<br>read-<br>write | D[2]<br>read-<br>write | D[1]<br>read-<br>write | D[0]<br>read-<br>write |

| FAULTB                                            | MAINB             | VAUXB             | VAUXBF                 | 12MVBF                 | 12VBF                  | 5VBF                   | 3VBF                   |

| Bit(s) | Function                        | Operation                                                                                                                                    |

|--------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| FALUTB | FAULT Pin Status, Slot<br>B     | Notes 1 & 2                                                                                                                                  |

| MAINB  | MAIN Enable Status,<br>Slot B   | Represents actual state (on/off) of the four main power outputs for Slot B. (+12V, +5V, +3.3V and -12V) 1 = MAIN Power On 0 = MAIN Power Off |

| VAUXB  | VAUX Enable Status,<br>Slot B   | Represents actual state (on/off) of the auxiliary power outputs for Slot B.  1 = MAIN Power On 0 = MAIN Power Off                            |

| VAUXFB | Overcurrent Fault VAUX Supply   | 1 = Fault<br>0 = No Fault                                                                                                                    |

| 12MVFB | Overcurrent Fault -12V Supply   | 1 = Fault<br>0 = No Fault                                                                                                                    |

| 12VFB  | Overcurrent Fault<br>12V Supply | 1 = Fault<br>0 = No Fault                                                                                                                    |