# 8-Channel, 60V Driver with Push-Pull Output, 3 Wire Interface

#### **Features**

- Eight (8) Outputs Rated at 60V, ±80mA

- Push-Pull Driver Configuration

- 6V to 60V Driver Supply Range

- 2.7V to 5.5V Logic Supply Range

- 3-Wire Serial Interface plus Chip Select

- · Captures Serial & Parallel Input Data

- · Outputs Can Be Paralleled

- 28-Lead QFN Package

### **Applications**

- White Goods

- ATE

- Industrial Equipment

### **Description**

The MX877 is an 8-channel, high voltage switch with 8-bit parallel or serial input control. The MX877 connects directly to a microprocessor through a standard 3-wire serial interface. The push-pull output configuration can drive up to 60 volts at 80mA. Outputs can be paralleled for increased drive current up to a device total of 400mA, sink or source.

The MX877 is designed to operate over a temperature range of -40 $^{\circ}$ C to +85 $^{\circ}$ C, and is available in a 28-lead QFN Package.

### **Ordering Information**

| Part     | Description                    |

|----------|--------------------------------|

| MX877R   | QFN-28 (73/Tube)               |

| MX877RTR | QFN-28 Tape & Reel (2500/Reel) |

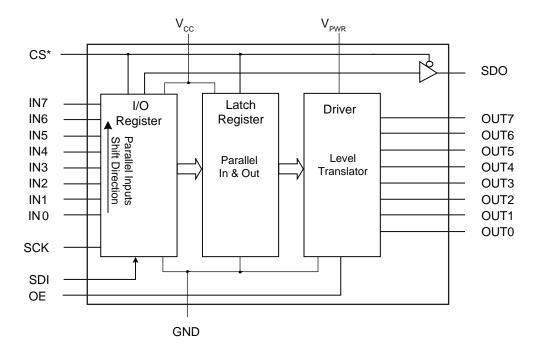

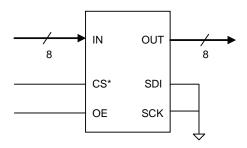

#### **Functional Block Diagram**

| Specifications                              | 3  |

|---------------------------------------------|----|

| 1.1 Package Pinout                          | 3  |

| 1.2 Pin Description                         |    |

| 1.3 Absolute Maximum Ratings                |    |

| 1.4 DC Electrical Characteristics           |    |

|                                             |    |

| 1.5 Dynamic Electrical Characteristics.     |    |

| 1.6 Serial Timing                           |    |

| 1.7 Parallel Timing                         | 6  |

|                                             | _  |

| Functional Description                      |    |

| Application Examples                        |    |

|                                             |    |

| 3.1 Parallel In / Parallel Out Application. |    |

| 3.2 Serial Cascade Application              |    |

| 3.3 Control System Application              |    |

|                                             |    |

| Manufacturing Information                   | 10 |

| 4.1 Moisture Sensitivity                    | 10 |

| 4.2 ESD Sensitivity                         | 10 |

| 4.3 Reflow Profile                          |    |

| 4.4 Mechanical Dimensions                   |    |

## 1 Specifications

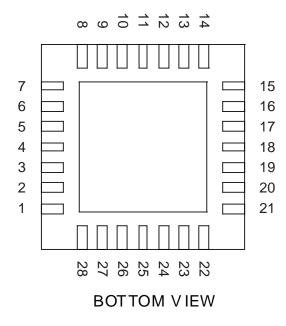

### 1.1 Package Pinout

### 1.2 Pin Description

| Pin# | Name             | Description                     |  |

|------|------------------|---------------------------------|--|

| 1    | OUT7             | Parallel Output                 |  |

| 2    | N/C              | No Connection                   |  |

| 3    | GND              | Ground                          |  |

| 4    | $V_{PWR}$        | High Voltage Supply (6V to 60V) |  |

| 5    | N/C              | No Connection                   |  |

| 6    | V <sub>CC</sub>  | Logic Supply (2.7V to 5.5V)     |  |

| 7    | SDO              | Serial Data Output              |  |

| 8    | IN7              | Parallel Input                  |  |

| 9    | IN6              | Parallel Input                  |  |

| 10   | IN5              | Parallel Input                  |  |

| 11   | IN4              | Parallel Input                  |  |

| 12   | IN3              | Parallel Input                  |  |

| 13   | IN2              | Parallel Input                  |  |

| 14   | IN1              | Parallel Input                  |  |

| 15   | IN0              | Parallel Input                  |  |

| 16   | SCK              | Serial Clock                    |  |

| 17   | V <sub>PWR</sub> | High Voltage Supply (6V to 60V) |  |

| 18   | SDI              | Serial Data Input               |  |

| 19   | CS*              | Chip Select (Active Low)        |  |

| 20   | OE               | Output Enable                   |  |

| 21   | GND              | Ground                          |  |

| 22   | OUT0             | Parallel Output                 |  |

| 23   | OUT1             | Parallel Output                 |  |

| 24   | OUT2             | Parallel Output                 |  |

| 25   | OUT3             | Parallel Output                 |  |

| 26   | OUT4             | Parallel Output                 |  |

| 27   | OUT5             | Parallel Output                 |  |

| 28   | OUT6             | Parallel Output                 |  |

### 1.3 Absolute Maximum Ratings

| Parameter                                | Symbol            | Min         | Max  | Units |

|------------------------------------------|-------------------|-------------|------|-------|

| V <sub>PWR</sub> Supply Voltage          | $V_{PWR}$         | -           | 60   | ٧     |

| Logic Supply Voltage                     | V <sub>CC</sub>   | -           | 6    | ٧     |

| Input Pin Voltage                        | VIN               | -           | 6    | ٧     |

| Continuous Output Current<br>OUT0 - OUT7 | I <sub>OUTn</sub> | •           | ±100 | mA    |

| Operating Junction Temperature           | T <sub>J</sub>    | -           | 150  | °C    |

| Thermal Resistance (Junction to Ambient) | $R_{	heta JA}$    | 110 Typical |      | °C/W  |

| Operating Temperature                    | T <sub>A</sub>    | -40         | 85   | °C    |

| Storage Temperature                      | T <sub>STG</sub>  | -55         | 150  | °C    |

Absolute maximum electrical ratings are at 25℃

Absolute Maximum Ratings are stress ratings. Stresses in excess of these ratings can cause permanent damage to the device. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this data sheet is not implied. Exposure of the device to the absolute maximum ratings for an extended period may degrade the device and affect its reliability.

Voltages with respect to GND=0V.

**ESD Warning:** ESD (electrostatic discharge) sensitive device. Although the MX877 features proprietary ESD protection circuitry, permanent damage may be sustained if subjected to high energy electrostatic discharges. Proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

#### 1.4 DC Electrical Characteristics

$V_{CC}$ =5V,  $V_{PWR}$ =42V,  $T_A$ =25°C, unless otherwise specified.

| Parameter                          | Conditions                     | Symbol            | Minimum              | Typical | Maximum | Units |

|------------------------------------|--------------------------------|-------------------|----------------------|---------|---------|-------|

| Logic Supply Voltage               | -                              | V <sub>CC</sub>   | 2.7                  | -       | 5.5     | V     |

| Logic Supply Current               | f <sub>SCK</sub> =5MHz         | I <sub>CC</sub>   | -                    | 50      | -       | μΑ    |

| Quiescent Logic Supply Current     | f <sub>SCK</sub> =0            | I <sub>CC</sub>   | -                    |         | 1       | μΑ    |

| V <sub>PWR</sub> Voltage           | -                              | V <sub>PWR</sub>  | 6                    |         | 60      | V     |

| V <sub>PWR</sub> Current           | Total of all Outputs           | I <sub>PWR</sub>  | -                    | -       | 400     | mA    |

| GND Current                        | Total of all Outputs           | -                 | -                    | -       | 400     | mA    |

| Quiescent V <sub>PWR</sub> Current | V <sub>PWR</sub> =42V, No Load | I <sub>PWR</sub>  | -                    | 0.75    | -       | mA    |

| High Level Input Voltage           | IN0-IN7, SCK, SDI, OE, CS*     | V <sub>IH</sub>   | V <sub>CC</sub> -0.5 |         | -       | V     |

| Low Level Input Voltage            | -                              | V <sub>IL</sub>   | -                    | -       | 0.5     | ٧     |

| Input Leakage Current              | -                              |                   | -                    | -       | 1       | μΑ    |

| SDO Tri-State Leakage Current      | CS*=Logic High                 |                   | -                    | -       | 1       | μΑ    |

| OUT0-OUT7 Current                  | Any One Output, Sink or Source | I <sub>OUTn</sub> | -                    |         | ±80     | mA    |

| OUT0-OUT7 ON Resistance            | V <sub>PWR</sub> =42V          | R <sub>OUTn</sub> | -                    | 9       | -       | Ω     |

| OUT0-7 Tri-State Leakage Current   | OE=Logic Low                   | I <sub>OUTn</sub> | -                    | -       | 1       | μΑ    |

**Notes:** To avoid unwanted output during V<sub>PWR</sub> application and system initialization, keep OE at a logic low until CS\* has completed one cycle.

Thermal Resistance is measured in still air with the device soldered to a 6 square inch board without a ground plane. Applications may require derating of the specified maximum currents to avoid exceeding the maximum operation junction temperature.

1.5 Dynamic Electrical Characteristics  $V_{CC}$ =5V,  $V_{PWR}$ =42V,  $T_A$ =25°C, unless otherwise specified.

| Parameter                        | Conditions                      | Symbol | Minimum | Typical | Maximum | Units |

|----------------------------------|---------------------------------|--------|---------|---------|---------|-------|

| SCK Period                       | -                               | -      | 100     |         | DC      | ns    |

| SCK High Time                    | -                               | -      | 40      | -       | -       | ns    |

| SCK Low Time                     | -                               | -      | 40      | -       | -       | ns    |

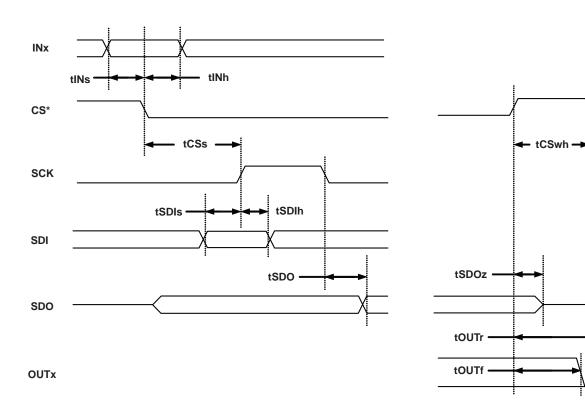

| CS* High Time                    | -                               | tCSwh  | 50      | -       | -       | ns    |

| CS* Falling to SCK Rising        | Setup Time                      | tCSs   | 150     | -       | -       | ns    |

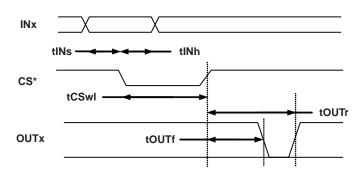

| CS* Low Time                     | SCK Low (Parallel Input Mode)   | tCSwl  | 150     | -       | -       | ns    |

| INx to CS Falling (SETUP TIME)   | -                               | tlNs   | 15      | -       | -       | ns    |

| INx to CS Falling (HOLD TIME)    | -                               | tlNh   | 30      | -       | -       | ns    |

| SDI to SCK Rising (SETUP TIME)   | -                               | tSDIs  | 20      | -       | -       | ns    |

| SDI to SCK Rising (HOLD TIME)    | -                               | tSDIh  | 25      | -       | -       | ns    |

| SCK Falling to to SDO Data Valid | -                               | tSDO   | -       | 10      | -       | ns    |

| CS* Rising to SDO High Z         | -                               | tSDOz  | -       | 12      | -       | ns    |

| CS* Rising to OUTx Rising        | To 50%, C(OUTx)=1000pF          | tOUTr  | -       | 750     | -       | ns    |

| CS* Rising to OUTx Falling       | To 50%, C(OUTx)=1000pF          | tOUTf  | -       | 570     | -       | ns    |

| OUTx Rise Time                   | From 10% to 90%, C(OUTx)=1000pF | -      | -       | 110     | -       | ns    |

| OUTx Fall Time                   | From 10% to 90%, C(OUTx)=1000pF | -      | -       | 75      | -       | ns    |

| OE Rising to OUTx Rising         | To 90%                          | -      | -       | 580     | -       | ns    |

| OE Rising to OUTx Falling        | To 90%                          | -      | -       | 390     | -       | ns    |

| OE Falling to OUTx High Z        | To 10%, OUTx High               | -      | -       | 130     | -       | ns    |

|                                  | To 10%, OUTx Low                | -      | -       | 90      | -       | ns    |

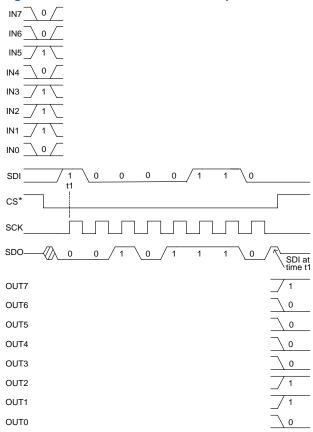

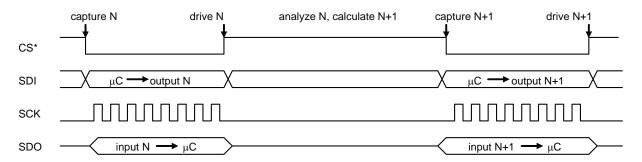

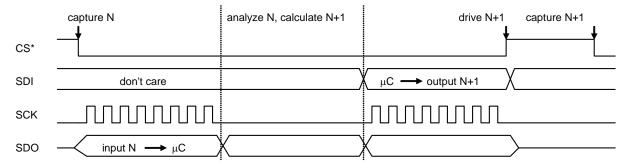

### 1.6 Serial Timing

### 1.7 Parallel Timing

### 2 Functional Description

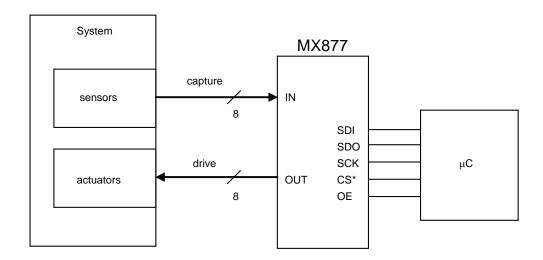

The MX877 is an 8 channel high voltage driver with 8-bit input control. The MX877 interfaces to a microprocessor through a standard 3 wire serial interface and an active-low chip select, or can be used in a parallel-in, parallel-out configuration.

Parallel data is transferred to the I/O register of the MX877 through the parallel input pins, IN0 through IN7 on the falling edge of the chip select pin, CS\*. When CS\* is in a logic low state, serial data can be transferred to the I/O register through the serial input pin, SDI, and from the I/O register through the serial output pin, SDO. Parallel or serial input data is transferred from the I/O register to the latch and high voltage output drivers, OUT0 through OUT7, on the positive edge of CS\*. This data remains latched until the next positive edge of CS\*.

The 8-bit I/O shift register is clocked by the serial clock pin, SCK. Serial data presented at the SDI pin is transferred to the shift register on the positive edge of SCK. Data shifts out of the register through the SDO pin on the negative edge of SCK. SDI and SCK are ignored, and SDO transitions to a high impedance condition when CS\* is at a logic high state.

Serial data is received by the MX877 through the SDI pin. This data is accepted on the rising edge of SCK. A specific output is programmed to a logic high state if SDI is at a logic high state during the rising edge of SCK. Conversely, a specific output is programmed to a logic low state if SDI is at a logic low state during the rising edge of SCK. Outputs transition to their programmed states on the positive edge of CS\* if the output enable pin, OE is in a logic high state.

The MSB input data (IN7) is presented at the serial output pin, SDO on the falling edge of CS\*. Input data from IN6 through IN0 is sequentially presented at SDO on negative SCK transitions if CS\* remains in a logic low state. If CS\* is at a logic low state beyond 8 cycles of SCK, SDI data that has propagated through the I/O register will then be presented at SDO. The SDO pin transitions to a high impedance state when CS\* is in a logic level high state, thus allowing multiple serial peripherals to share the microprocessor data pin.

Figure 1. Serial Data Transfer Example

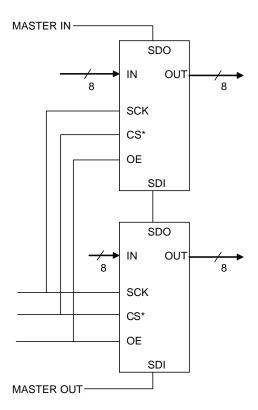

Devices may be serially cascaded by connecting SDO to SDI of the next device. Pins SCK and CS\* are common to all devices in serial cascade. For n-cascaded devices the CS\* should remain low for 8n cycles of SCK.

An output enable pin, OE enables the driver outputs OUT0 through OUT7 when logic high. A logic low level on OE forces the OUT0 through OUT7 outputs to a high impedance state.

The MX877 can also operate as a parallel-in, parallel-out level shifter and driver. SCK must remain at a logic low state when operating in this mode. Parallel input data presented to IN0 through IN7 is captured on the falling edge of CS\*. This data is transferred to OUT0 through OUT7 on the rising edge of CS\*, and remains latched until the next rising edge of CS\*.

## **3 Application Examples**

### 3.1 Parallel In / Parallel Out Application

### 3.2 Serial Cascade Application

8

### 3.3 Control System Application

### Type 1 timing:

Type 2 timing:

July 29, 2011 **www.clare.com** 9

### 4 Manufacturing Information

### **4.1 Moisture Sensitivity**

All plastic encapsulated semiconductor packages are susceptible to moisture ingression. Clare classified all of its plastic encapsulated devices for moisture sensitivity according to the latest version of the joint industry standard, **IPC/JEDEC J-STD-020**, in force at the time of product evaluation. We test all of our products to the maximum conditions set forth in the standard, and guarantee proper operation of our

devices when handled according to the limitations and information in that standard as well as to any limitations set forth in the information or standards referenced below.

Failure to adhere to the warnings or limitations as established by the listed specifications could result in reduced product performance, reduction of operable life, and/or reduction of overall reliability.

This product carries a **Moisture Sensitivity Level (MSL) rating** as shown below, and should be handled according to the requirements of the latest version of the joint industry standard **IPC/JEDEC J-STD-033**.

| Device | Moisture Sensitivity Level (MSL) Rating |

|--------|-----------------------------------------|

| MX877R | MSL 3                                   |

#### 4.2 ESD Sensitivity

This product is **ESD Sensitive**, and should be handled according to the industry standard **JESD-625**.

#### 4.3 Reflow Profile

This product has a maximum body temperature and time rating as shown below. All other guidelines of **J-STD-020** must be observed.

| Device | Maximum Temperature x Time |

|--------|----------------------------|

| MX877R | 260°C for 30 seconds       |

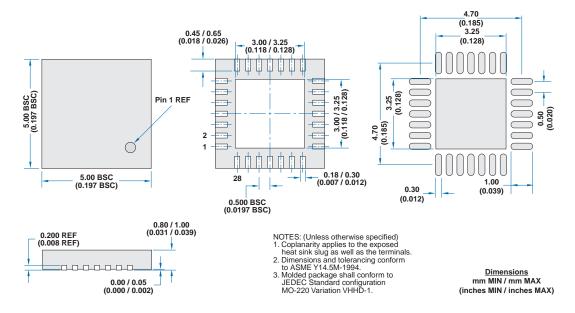

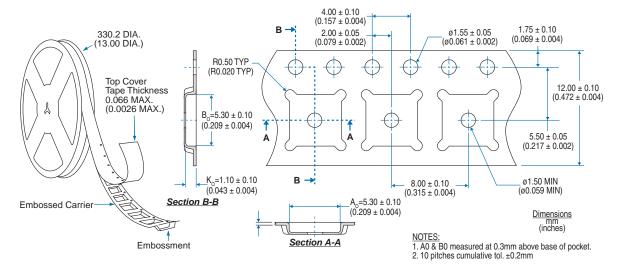

#### 4.4 Mechanical Dimensions

#### 4.4.1 QFN-28 Package & Recommended PCB Land Pattern

#### 4.4.2 Tape & Reel Dimensions

### For additional information please visit our website at: www.clare.com

Clare, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. Neither circuit patent licenses nor indemnity are expressed or implied. Except as set forth in Clare's Standard Terms and Conditions of Sale, Clare, Inc. assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

The products described in this document are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or where malfunction of Clare's product may result in direct physical harm, injury, or death to a person or severe property or environmental damage. Clare, Inc. reserves the right to discontinue or make changes to its products at any time without notice.

Specification: DS-MX877-20110729 ©Copyright 2011, Clare, Inc. All rights reserved. Printed in USA. 7/29/2011