#### STMUX1800E

# 16-bit to 8-bit MUX/DEMUX for gigabit Ethernet LAN switch with LED switch and enhanced ESD protection

#### **Features**

■ Low R<sub>ON</sub>: 4.0 Ω typical

■ V<sub>CC</sub> operating range: 3.0 to 3.6 V

■ Enhanced ESD protection: > 8 kV (contact) and 15 kV (HBM)

Low power mode for minimum power consumption

■ Channel on capacitance: 9.5 pF typical

■ Switching time speed: 9 ns

Near to zero propagation delay: 250 ps

Very low crosstalk: -45 dB at 250 MHz

■ Bit-to-bit skew: 200 ps

>600 MHz -3 dB typical bandwidth (or data frequency)

■ Three SPDT switches for LED support

Rail-to-rail switching on data I/O ports (0 V to 5 V)

Package: QFN42

■ Lead-free

#### **Applications**

■ 10/100/1000 Mbit Ethernet switching

Audio/video switching

#### **Description**

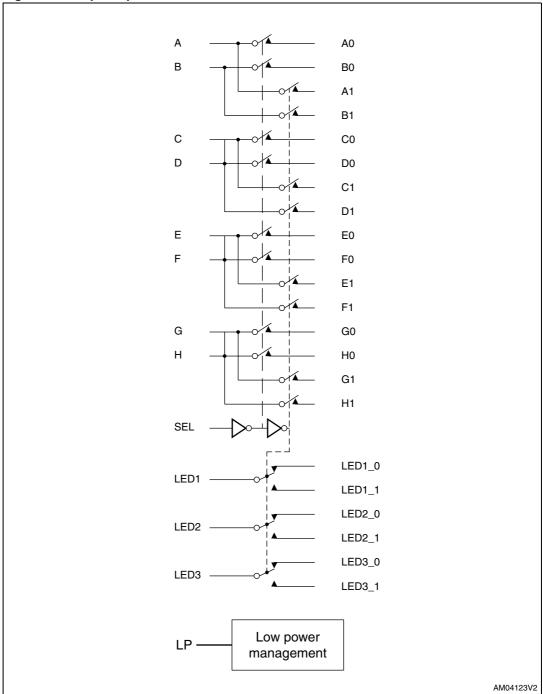

The STMUX1800E is a 16 to 8-bit multiplexer/demultiplexer low  $R_{ON}$  bidirectional LAN switch designed for various standards, such as 10/100/1000 Ethernet. It is designed for very low crosstalk, low bit-to-bit skew and low I/O capacitance.

The differential signal from the Gigabit Ethernet transceiver is multiplexed into one of two selected outputs while the unselected switch goes to Hi-Z status.

The device integrates three SPDT (single pole dual throw) switches, for LED support.

The device can be put into low power mode consuming minimum power.

Table 1. Device summary

| Order code    | Package | Packing       |

|---------------|---------|---------------|

| STMUX1800EQTR | QFN42   | Tape and reel |

Contents STMUX1800E

### **Contents**

| 1 | Pin description            | 5  |

|---|----------------------------|----|

| 2 | Maximum rating             | 8  |

| 3 | Electrical characteristics | 9  |

| 4 | Package mechanical data    | 20 |

| 5 | Revision history           | 25 |

STMUX1800E List of tables

### List of tables

| Table 1.  | Device summary                                                          | 1  |

|-----------|-------------------------------------------------------------------------|----|

| Table 2.  | Pin description                                                         | 5  |

| Table 3.  | LAN switch function table                                               | 7  |

| Table 4.  | LED switch function table                                               | 7  |

| Table 5.  | Absolute maximum ratings                                                | 8  |

| Table 6.  | Recommended operating conditions                                        | 8  |

| Table 7.  | DC electrical characteristics for Gigabit Ethernet LAN8/16MUX/DEMUX     |    |

|           | (V <sub>CC</sub> = 3.3 V ±10%)                                          | 9  |

| Table 8.  | DC electrical characteristics for 10/100 Ethernet LAN8/16MUX/DEMUX      |    |

|           | (V <sub>CC</sub> = 3.3 V ±10)                                           | 11 |

| Table 9.  | Capacitance (T <sub>A</sub> = 25 °C, f = 1 MHz)                         | 12 |

| Table 10. | Power supply characteristics                                            | 12 |

| Table 11. | Dynamic electrical characteristics (V <sub>CC</sub> = 3.3 V ±10%)       | 12 |

| Table 12. | Switching characteristics ( $T_A = 25$ °C, $V_{CC} = 3.3$ V $\pm 10$ %) | 13 |

| Table 13. | ESD performance                                                         |    |

| Table 14. | Mechanical data for QFN42 (3.5 x 9 x 0.75) - pitch 0.5 mm               | 21 |

| Table 15. | Document revision history                                               | 25 |

List of figures STMUX1800E

# **List of figures**

| Pin connection (top through view)                                  | . 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input equivalent circuit                                           | . 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Diagram for suggested V <sub>CC</sub> decoupling                   | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Test circuit for leakage current (I <sub>OFF</sub> )               | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

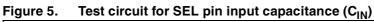

| Test circuit for SEL pin input capacitance (C <sub>IN</sub> )      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

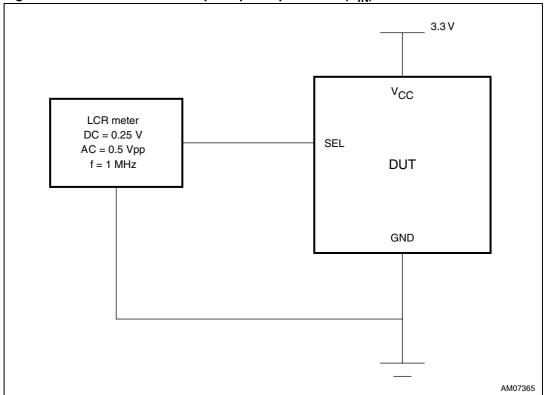

| Test circuit for switch off capacitance (C <sub>OFF</sub> )        | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

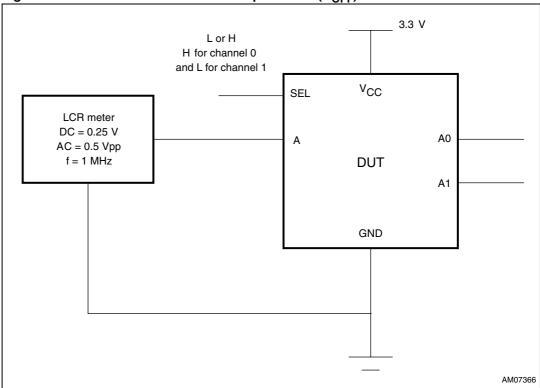

| Test circuit for switch on capacitance (C <sub>ON</sub> )          | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Test circuit for bandwidth measurement (BW)                        | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Test circuit for crosstalk measurement (x <sub>talk</sub> )        | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Test circuit for off isolation measurement (O <sub>IRR</sub> )     | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Package outline for QFN42 (3.5 x 9 x 0.75) - pitch 0.5 mm          | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Footprint recommendation for QFN42 (3.5 x 9 x 0.75) - pitch 0.5 mm | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Carrier tape information for QFN42 (3.5 x 9 x 0.75) - pitch 0.5 mm | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Reel information for QFN42 (3.5 x 9 x 0.75) - pitch 0.5 mm         | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                    | Input equivalent circuit  Diagram for suggested $V_{CC}$ decoupling  Test circuit for leakage current ( $I_{OFF}$ )  Test circuit for SEL pin input capacitance ( $C_{IN}$ )  Test circuit for switch off capacitance ( $C_{OFF}$ )  Test circuit for switch on capacitance ( $C_{ON}$ )  Test circuit for bandwidth measurement (BW)  Test circuit for crosstalk measurement ( $x_{talk}$ )  Test circuit for off isolation measurement ( $O_{IRR}$ )  Package outline for QFN42 (3.5 x 9 x 0.75) - pitch 0.5 mm  Footprint recommendation for QFN42 (3.5 x 9 x 0.75) - pitch 0.5 mm  Carrier tape information for QFN42 (3.5 x 9 x 0.75) - pitch 0.5 mm |

STMUX1800E Pin description

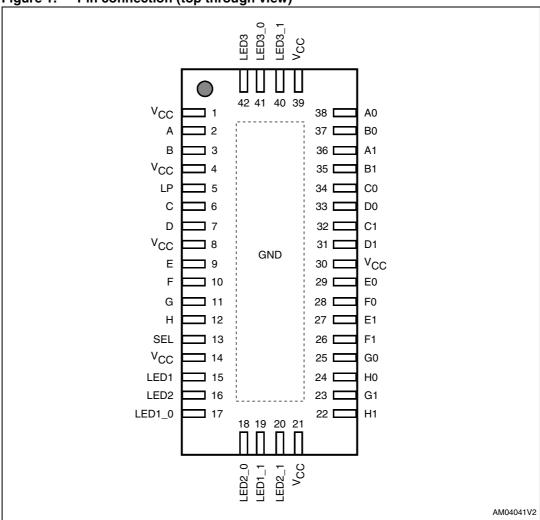

### 1 Pin description

Table 2. Pin description

| Pin                            | Symbol                                            | Name and function            |

|--------------------------------|---------------------------------------------------|------------------------------|

| 2, 3, 6, 7, 9, 10, 11, 12      | A, B, C, D, E, F, G, H                            | 8-bit bus                    |

| 38, 37, 34, 33, 29, 28, 25, 24 | A0, B0, C0, D0, E0, F0, G0, H0                    | 8-bit multiplexed to bus 0   |

| 36, 35, 32, 31, 27, 26, 23, 22 | A1, B1, C1, D1, E1, F1, G1, H1                    | 8-bit multiplexed to bus 1   |

| 5                              | LP                                                | Low power mode enable        |

| 13                             | SEL                                               | Bus and LED switch selection |

| 15, 16, 42                     | LED1, LED2, LED3                                  | LED switch input             |

| 17, 18, 41, 19, 20, 40         | LED1_0, LED2_0, LED3_0,<br>LED1_1, LED2_1, LED3_1 | LED switch output            |

| 1, 4, 8, 14, 21, 30, 39        | V <sub>CC</sub>                                   | Supply voltage               |

Pin description STMUX1800E

Figure 2. Input equivalent circuit

STMUX1800E Pin description

Table 3. LAN switch function table

| LP | SEL | Function                             |

|----|-----|--------------------------------------|

| L  | L   | 8-bit bus to 8-bit multiplexed bus 0 |

| L  | Н   | 8-bit bus to 8-bit multiplexed bus 1 |

| Н  | Х   | Bus 0 and 1 in Hi-Z                  |

Table 4. LED switch function table

| LP | SEL | Function                                            |  |

|----|-----|-----------------------------------------------------|--|

| L  | L   | LED switch input connected to LED switch output X_0 |  |

| L  | Н   | LED switch input connected to LED switch output X_1 |  |

| Н  | Х   | Output X_0 and X_1 in Hi-Z                          |  |

Maximum rating STMUX1800E

#### 2 Maximum rating

Stressing the device above the rating listed in *Table 5: Absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in *Table 6: Recommended operating conditions* of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 5. Absolute maximum ratings

| Symbol           | Parameter                        | Value       | Unit |

|------------------|----------------------------------|-------------|------|

| V <sub>CC</sub>  | Supply voltage to ground         | -0.5 to 4.6 | V    |

| V <sub>IO</sub>  | DC input output voltage          | -0.5 to 4.6 | V    |

| V <sub>IC</sub>  | DC control input voltage         | -0.5 to 4.6 | V    |

| Io               | DC output current <sup>(1)</sup> | 120         | mA   |

| P <sub>D</sub>   | Power dissipation                | 0.5         | W    |

| T <sub>stg</sub> | Storage temperature              | -65 to 150  | °C   |

| TL               | Lead temperature (10 seconds)    | 300         | °C   |

<sup>1.</sup> If  $V_{IO} \times I_{O}$  does not exceed the maximum limit of  $P_{D}$ .

#### **Recommended operating conditions**

Table 6. Recommended operating conditions

| Symbol          | Parameter                          |      | Unit |                 |       |

|-----------------|------------------------------------|------|------|-----------------|-------|

| Syllibol        | Farameter                          | Min. | Тур. | Max.            | Oilit |

| V <sub>CC</sub> | Supply voltage to ground           | 3    | _    | 3.6             | V     |

| V <sub>IC</sub> | DC control input voltage (SEL, LP) | 0    | _    | V <sub>CC</sub> | V     |

| V <sub>IO</sub> | DC input/output voltage            | 0    | _    | V <sub>CC</sub> | V     |

| T <sub>A</sub>  | Operating temperature              | -40  | _    | 85              | °C    |

### 3 Electrical characteristics

Table 7. DC electrical characteristics for Gigabit Ethernet LAN8/16MUX/DEMUX ( $V_{CC} = 3.3 \text{ V} \pm 10\%$ )

| Symbol                              | Parameter                                                                   | Test condition                                                                                                                                                                                              | -40 to 85 °C |      |      | Unit |

|-------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|------|

|                                     |                                                                             |                                                                                                                                                                                                             | Min.         | Тур. | Max. |      |

| V <sub>IH</sub>                     | Voltage input high (SEL, LP)                                                | High level guaranteed                                                                                                                                                                                       | 2.4          | _    | _    | V    |

| V <sub>IL</sub>                     | Voltage input low<br>(SEL, LP)                                              | Low level guaranteed                                                                                                                                                                                        | -0.5         | _    | 0.8  | V    |

| V <sub>IK</sub>                     | Clamp diode voltage<br>(SEL, LP)                                            | V <sub>CC</sub> = 3.6 V<br>I <sub>IN</sub> = -18 mA                                                                                                                                                         | _            | -0.8 | -1.2 | V    |

| I <sub>IH</sub>                     | Input high current (SEL, LP)                                                | $V_{CC} = 3.6 \text{ V}$ $V_{IN} = V_{CC}$                                                                                                                                                                  | _            | _    | ±5   | μΑ   |

| I <sub>IL</sub>                     | Input low current (SEL, LP)                                                 | $V_{CC} = 3.6 \text{ V}$<br>$V_{IN} = \text{GND}$                                                                                                                                                           | _            | _    | ±5   | μΑ   |

| IOFF <sub>(SW)</sub> <sup>(1)</sup> | Leakage current through the switch common terminals (A to H) (LED1 to LED3) | $V_{CC} = 3.6 \text{ V}$ A to H = $V_{CC}$ LED1 to LED3 = $V_{CC}$ A0 to H0 = 0 V A1 to H1 = floating LEDx_0 = 0 V LEDx1 = floating SEL = $V_{CC}$ LP = GND                                                 | _            | _    | ±1   | μΑ   |

| loff(sw_LP)                         | Leakage current through the switch in LP mode                               | $\begin{split} &V_{CC}=3.6 \text{ V; A to H}=V_{CC};\\ &\text{LED1 to LED3}=V_{CC}; \text{ A0 to H0,}\\ &\text{A1 to H1}=0 \text{V; LEDx\_0,}\\ &\text{LEDx\_1}=0 \text{V}\\ &\text{LP}=V_{CC} \end{split}$ |              |      | ±10  | μА   |

| IOFF <sub>(SEL)</sub>               | SEL pin leakage current                                                     | V <sub>CC</sub> = 0 V<br>SEL = 0 to 3.6 V                                                                                                                                                                   | _            | _    | ±1   | μΑ   |

| R <sub>ON</sub>                     | Switch ON resistance <sup>(2)</sup>                                         | $V_{CC} = 3.0 \text{ V}$ $V_{IN} = 1.5 \text{ to } V_{CC}$ $I_{IN} = -40 \text{ mA}$                                                                                                                        | _            | 4.0  | 6.5  | Ω    |

Table 7. DC electrical characteristics for Gigabit Ethernet LAN8/16MUX/DEMUX ( $V_{CC} = 3.3 \text{ V} \pm 10\%$ ) (continued)

|                   | Parameter                                                                                                  | Test condition                                                                       |              | Unit |      |   |

|-------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------|------|------|---|

| Symbol            |                                                                                                            |                                                                                      | -40 to 85 °C |      |      |   |

|                   |                                                                                                            |                                                                                      | Min.         | Тур. | Max. |   |

| R <sub>FLAT</sub> | ON resistance flatness <sup>(2), (3)</sup>                                                                 | $V_{CC}$ = 3.0 V $V_{IN}$ at 1.5 and $V_{CC}$ $I_{IN}$ = -40 mA                      | _            | 0.5  | _    | Ω |

| $\Delta R_{ON}$   | ON resistance match between channel $\Delta R_{\text{ON}} = R_{\text{ONMAX}} - R_{\text{ONMIN}}^{(2),(4)}$ | $V_{CC} = 3.0 \text{ V}$ $V_{IN} = 1.5 \text{ to } V_{CC}$ $I_{IN} = -40 \text{ mA}$ | _            | 0.4  | 1    | Ω |

<sup>1.</sup> Refer to Figure 4: Test circuit for leakage current (I<sub>OFF</sub>) on page 15.

<sup>2.</sup> Measured by voltage drop between channels at indicated current through the switch. ON resistance is determined by the lower of the voltages.

<sup>3.</sup> Flatness is defined as the difference between the  $R_{ONMAX}$  and  $R_{ONMIN}$  of ON resistance over the specified range.

<sup>4.</sup>  $\Delta R_{ON}$  measured at the same  $V_{CC},$  temperature and voltage level.

Table 8. DC electrical characteristics for 10/100 Ethernet LAN8/16MUX/DEMUX ( $V_{CC} = 3.3 \text{ V} \pm 10$ )

|                                     | (V <sub>CC</sub> = 3.3 V ±10)                                                        |                                                                                                                                                                                                       |              | Value | !    |      |

|-------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|------|------|

| Symbol                              | Parameter                                                                            | Test condition                                                                                                                                                                                        | -40 to 85 °C |       |      | Unit |

|                                     |                                                                                      |                                                                                                                                                                                                       | Min.         | Тур.  | Max. |      |

| V <sub>IH</sub>                     | Voltage input high (SEL, LP)                                                         | High level guaranteed                                                                                                                                                                                 | 2.4          | _     | _    | V    |

| V <sub>IL</sub>                     | Voltage input low (SEL, LP)                                                          | Low level guaranteed                                                                                                                                                                                  | -0.5         | _     | 0.8  | V    |

| V <sub>IK</sub>                     | Clamp diode voltage (SEL, LP)                                                        | V <sub>CC</sub> = 3.6 V<br>I <sub>IN</sub> = -18 mA                                                                                                                                                   | _            | -0.7  | -1.2 | V    |

| I <sub>IH</sub>                     | Input high current (SEL, LP)                                                         | $V_{CC} = 3.6 \text{ V}$ $V_{IN} = V_{CC}$                                                                                                                                                            | _            | _     | ±5   | μΑ   |

| I <sub>IL</sub>                     | Input low current (SEL, LP)                                                          | V <sub>CC</sub> = 3.6 V<br>V <sub>IN</sub> = GND                                                                                                                                                      | _            | _     | ±5   | μΑ   |

| IOFF <sub>(SW)</sub> <sup>(1)</sup> | Leakage current through the switch common terminals (A to H) (LED1 to LED3)          | $V_{CC} = 3.6 \text{ V}$ A to H = $V_{CC}$ LED1 to LED3 = $V_{CC}$ A0 to H0 = 0 V A1 to H1 = floating LEDx_0 = 0 V LEDx1 = floating SEL = $V_{CC}$ LP = GND                                           | _            | _     | ±1   | μА   |

| loff(sw_LP)                         | Leakage current through the switch in LP mode                                        | $\begin{split} &V_{CC}=3.6 \text{ V; A to H}=V_{CC};\\ &\text{LED1 to LED3}=V_{CC};\\ &\text{A0 to H0,}\\ &\text{A1 to H1}=0 \text{ V; LEDx\_0, LEDx\_1}=0 \text{ V}\\ &\text{LP}=V_{CC} \end{split}$ |              |       | ±10  | μΑ   |

| IOFF <sub>(SEL)</sub>               | SEL pin leakage current                                                              | V <sub>CC</sub> = 0 V<br>SEL = 0 to 3.6 V                                                                                                                                                             | _            | _     | ±1   | μΑ   |

| R <sub>ON</sub>                     | Switch ON resistance <sup>(2)</sup>                                                  | $V_{CC} = 3.0 \text{ V}$ $V_{IN} = 1.5 \text{ to } V_{CC}$ $I_{IN} = -10 \text{ to } -30 \text{ mA}$                                                                                                  | _            | 4.0   | 6.5  | Ω    |

| R <sub>FLAT</sub>                   | ON resistance flatness <sup>(2) (3)</sup>                                            | $V_{CC}$ = 3.0 V $V_{IN}$ at 1.5 and $V_{CC}$ $I_{IN}$ = -10 to -30 mA                                                                                                                                | _            | 0.5   | _    | Ω    |

| $\Delta$ R <sub>ON</sub>            | ON resistance match between channel $\Delta R_{ON} = R_{ONMAX} - R_{ONMIN}^{(2)(4)}$ | $V_{CC} = 3.0 \text{ V}$ $V_{IN} = 1.5 \text{ to } V_{CC}$ $I_{IN} = -10 \text{ to } -30 \text{ mA}$                                                                                                  | _            | 0.4   | 1    | Ω    |

<sup>1.</sup> Refer to Figure 4: Test circuit for leakage current ( $I_{OFF}$ ) on page 15.

Measured by voltage drop between channels at indicated current through the switch. ON resistance is determinate by the lower of the two voltages.

<sup>3.</sup> Flatness is defined as the difference between the  $R_{ONMAX}$  and  $R_{ONMIN}$  of ON resistance over the specified range.

<sup>4.</sup>  $\Delta R_{ON}$  measured at the same  $V_{CC}$ , temperature and voltage level.

| Table 3. Capacitatice (1) = 23 C. 1 = 1 Willz | Table 9. | Capacitance | $(T_{\Delta} = 25  ^{\circ}C, f = 1  MHz)$ |

|-----------------------------------------------|----------|-------------|--------------------------------------------|

|-----------------------------------------------|----------|-------------|--------------------------------------------|

| Symbol           | Parameter                                | Test condition                                       | Value |      |      | Unit |

|------------------|------------------------------------------|------------------------------------------------------|-------|------|------|------|

|                  |                                          |                                                      | Min.  | Тур. | Max. | Oill |

| C <sub>IN</sub>  | SEL pin input capacitance <sup>(1)</sup> | DC = 0.25 V<br>AC = 0.5 V <sub>PP</sub><br>f = 1 MHz | _     | 2    | 3    | pF   |

| C <sub>OFF</sub> | Switch off capacitance <sup>(2)</sup>    | DC = 0.25 V<br>AC = 0.5 V <sub>PP</sub><br>f = 1 MHz |       | 4    | 5    | pF   |

| C <sub>ON</sub>  | Switch on capacitance <sup>(3)</sup>     | DC = 0.25 V<br>AC = 0.5 V <sub>PP</sub><br>f = 1 MHz | _     | 9.5  | 11   | pF   |

- 1. Refer to Figure 5: Test circuit for SEL pin input capacitance  $(C_{IN})$  on page 15.

- 2. Refer to Figure 6: Test circuit for switch off capacitance (C<sub>OFF</sub>) on page 16.

- 3. Refer to Figure 7: Test circuit for switch on capacitance ( $C_{ON}$ ) on page 16.

Table 10. Power supply characteristics

|        |                                     |                                                                             | Value |             |      |      |

|--------|-------------------------------------|-----------------------------------------------------------------------------|-------|-------------|------|------|

| Symbol | Parameter                           | Test condition                                                              | -     | 40 to 85 °C |      | Unit |

|        |                                     |                                                                             | Min.  | Тур.        | Max. |      |

| 1      | Active mode power supply current    | $V_{CC} = 3.6 \text{ V}, V_{IN} = V_{CC} \text{ or }$<br>GND, LP = GND      | _     | 150         | 500  | μΑ   |

| Icc    | Low power mode power supply current | $V_{CC} = 3.6 \text{ V}, V_{IN} = V_{CC} \text{ or }$<br>GND, LP = $V_{CC}$ | _     | 10          | 50   | μΑ   |

Table 11. Dynamic electrical characteristics ( $V_{CC} = 3.3 \text{ V} \pm 10\%$ )

|                   |                                |                                      |      | Value       |      |      |

|-------------------|--------------------------------|--------------------------------------|------|-------------|------|------|

| Symbol            | Parameter                      | Test condition                       | -    | 40 to 85 °C | ;    | Unit |

|                   |                                |                                      | Min. | Тур.        | Max. |      |

| X <sub>talk</sub> | Crosstalk <sup>(1)</sup>       | $R_L$ = 100 Ω f = 250 MHz            | _    | -45         | _    | dB   |

| O <sub>IRR</sub>  | Off isolation <sup>(2)</sup>   | $R_L$ = 100 Ω f = 250 MHz            | _    | -37         | _    | dB   |

| BW                | -3 dB bandwidth <sup>(3)</sup> | $R_L$ = 100 Ω $0 < V_{IN} \le 3.6 V$ | _    | 600         | _    | MHz  |

- 1. Refer to Figure 9: Test circuit for crosstalk measurement ( $x_{talk}$ ) on page 18.

- 2. Refer to Figure 10: Test circuit for off isolation measurement ( $O_{IRR}$ ) on page 19.

- 3. Refer to Figure 8: Test circuit for bandwidth measurement (BW) on page 17.

Table 12. Switching characteristics ( $T_A = 25$  °C,  $V_{CC} = 3.3$  V ±10%)

| Symbol                                 | Parameter                                                                                  | Test condition               | Value |      |      | Unit  |

|----------------------------------------|--------------------------------------------------------------------------------------------|------------------------------|-------|------|------|-------|

| Syllibol                               |                                                                                            | rest condition               | Min.  | Тур. | Max. | Oille |

| t <sub>PD</sub>                        | Propagation delay                                                                          | V <sub>CC</sub> = 3 to 3.6 V |       | 0.25 |      | ns    |

| t <sub>PZH</sub> ,<br>t <sub>PZL</sub> | Line enable time, SE to x to x0 or x to x1                                                 | V <sub>CC</sub> = 3 to 3.6 V | 0.5   | 6.5  | 15   | ns    |

| t <sub>PHZ</sub> ,<br>t <sub>PLZ</sub> | Line disable time, SE to x to x0 or x to x1                                                | V <sub>CC</sub> = 3 to 3.6 V | 0.5   | 6.5  | 8.5  | ns    |

| t <sub>SK(O)</sub>                     | Output skew<br>between center port<br>to any other port                                    | V <sub>CC</sub> = 3 to 3.6 V | _     | 0.1  | 0.2  | ns    |

| t <sub>SK(P)</sub>                     | Skew between opposite transition of the same output (t <sub>PHL</sub> , t <sub>PLH</sub> ) | V <sub>CC</sub> = 3 to 3.6 V |       | 0.1  | 0.2  | ns    |

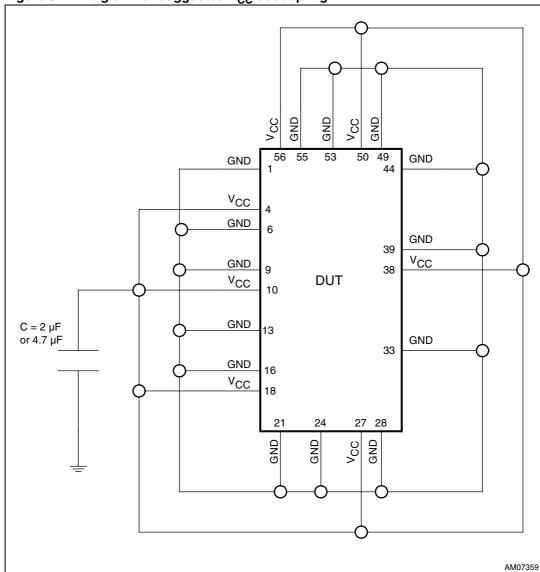

Table 13. ESD performance

| Symbol | Test condition                                   | Value |      |      | Unit |

|--------|--------------------------------------------------|-------|------|------|------|

| Symbol | rest condition                                   | Min.  | Тур. | Max. |      |

| ESD    | Contact discharge <sup>(1)</sup><br>IEC61000-4-2 | _     | ±8   | _    | kV   |

| E3D    | Human body model<br>(MIL-STD-883)                | _     | ±15  | _    | kV   |

<sup>1.</sup> Refer to Figure 3: Diagram for suggested  $V_{CC}$  decoupling on page 14.

Figure 3. Diagram for suggested  $V_{CC}$  decoupling

- 1. Applicable for system level ESD test.

- 2. 100 nF capacitors must be used as local bypass capacitors between the adjacent  $V_{CC}$  and GND pairs (total 7).

- 3.6 V  $v_{CC}$ I<sub>OFF</sub> (SW) A0 Α1 FLOAT -3.6 V 3.6 V — SEL GND AM07364

Test circuit for leakage current (I<sub>OFF</sub>) Figure 4.

Figure 6. Test circuit for switch off capacitance (C<sub>OFF</sub>)

Figure 7. Test circuit for switch on capacitance (C<sub>ON</sub>)

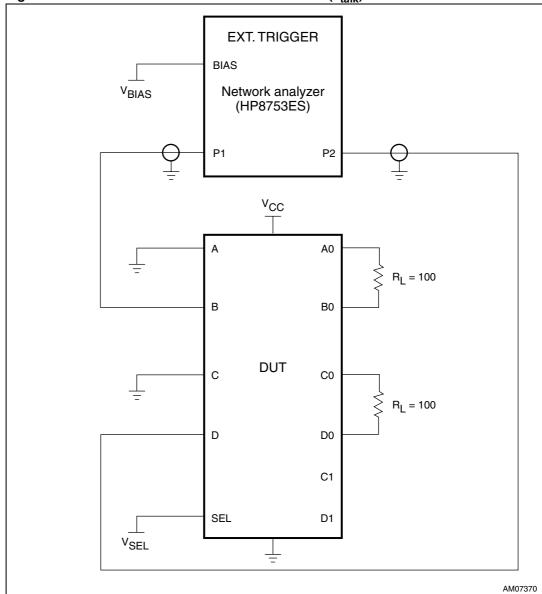

Figure 8. Test circuit for bandwidth measurement (BW)

1.  $C_L$  includes probe and jig capacitance.

Frequency response is measured at the output of the ON channel. For example, when  $V_{SEL} = 0$  and A is the input, the output is measured at A0. All unused analog I/O ports are left open.

HP8753ES setup:

Average = 4

$R_{BW} = 3 \text{ kHz}$

$V_{BIAS} = 0.35 V$

ST = 2 s

P1 = 0 dBm

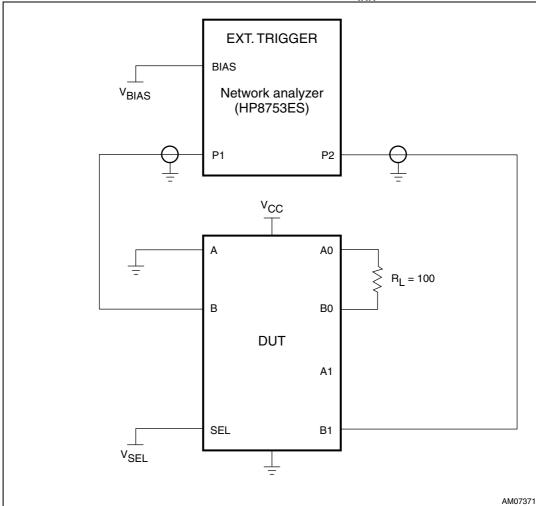

Figure 9. Test circuit for crosstalk measurement (x<sub>talk</sub>)

- 1. C<sub>L</sub> includes probe and jig capacitance.

- 2. A 50  $\Omega$  termination resistor is needed to match the loading of the network analyzer.

Crosstalk is measured at the output of the non-adjacent ON channel. For example, when  $V_{SEL} = 0$ , and B is the input, the output is measured at D. All unused analog input ports are connected to GND and output ports are left open.

#### HP8753ES setup:

Average = 4

$R_{BW} = 3 \text{ kHz}$

$V_{BIAS} = 0.35 V$

ST = 2 s

P1 = 0 dBm

Figure 10. Test circuit for off isolation measurement (O<sub>IRR</sub>)

- 1.  $C_L$  includes probe and jig capacitance.

- 2. A 50  $\Omega\,\text{termination}$  resistor is needed to match the loading of the network analyzer.

Off isolation is measured at the output of the OFF channel. For example, when  $V_{SEL}=0$ , and B is the input, the output is measured at B1. All unused analog input ports are connected to GND and output ports are left open.

HP8753ES setup:

Average = 4

$R_{BW} = 3 \text{ kHz}$

$V_{BIAS} = 0.35 V$

ST = 2 s

P1 = 0 dBm

### 4 Package mechanical data

#### **ECOPACK**®

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

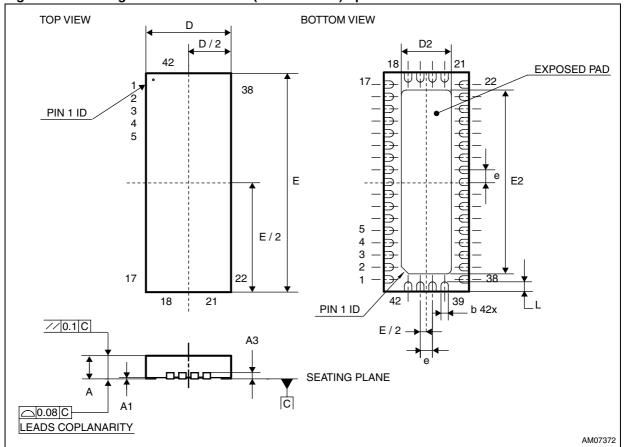

Figure 11. Package outline for QFN42 (3.5 x 9 x 0.75) - pitch 0.5 mm

Table 14. Mechanical data for QFN42 (3.5 x 9 x 0.75) - pitch 0.5 mm

| Symbol | millimeters |      |      |  |  |

|--------|-------------|------|------|--|--|

| Symbol | Min.        | Тур. | Max. |  |  |

| А      | 0.70        | 0.75 | 0.80 |  |  |

| A1     | 0           | 0.02 | 0.05 |  |  |

| A3     | _           | 0.20 | _    |  |  |

| b      | 0.20        | 0.25 | 0.30 |  |  |

| D      | 3.40        | 3.50 | 3.60 |  |  |

| D2     | 2           | 2.05 | 2.10 |  |  |

| Е      | 8.90        | 9    | 9.10 |  |  |

| E2     | 7.50        | 7.55 | 7.60 |  |  |

| е      | _           | 0.50 | _    |  |  |

| L      | 0.30        | 0.40 | 0.50 |  |  |

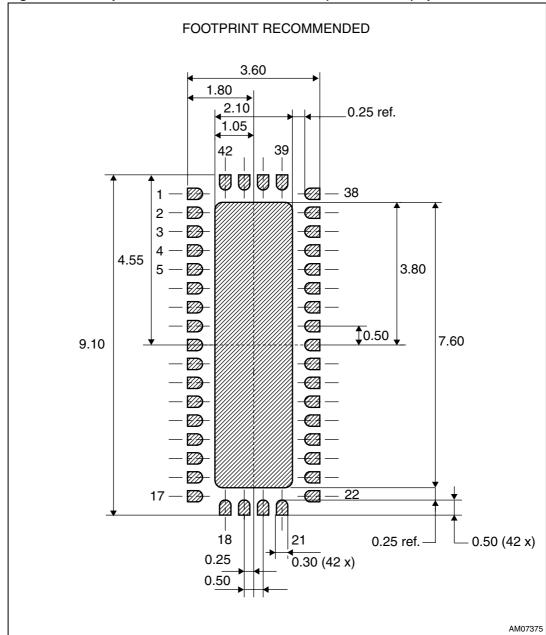

Figure 12. Footprint recommendation for QFN42 (3.5 x 9 x 0.75) - pitch 0.5 mm

**577**

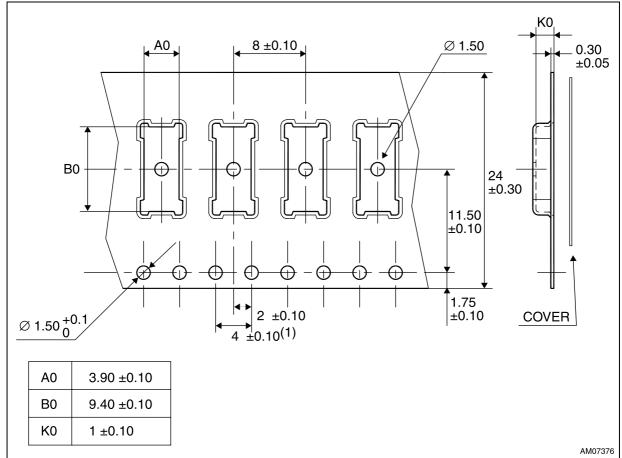

Figure 13. Carrier tape information for QFN42 (3.5 x 9 x 0.75) - pitch 0.5 mm

1. 10 sprocket hole pitch cumulative tolerance  $\pm 0.20$ .

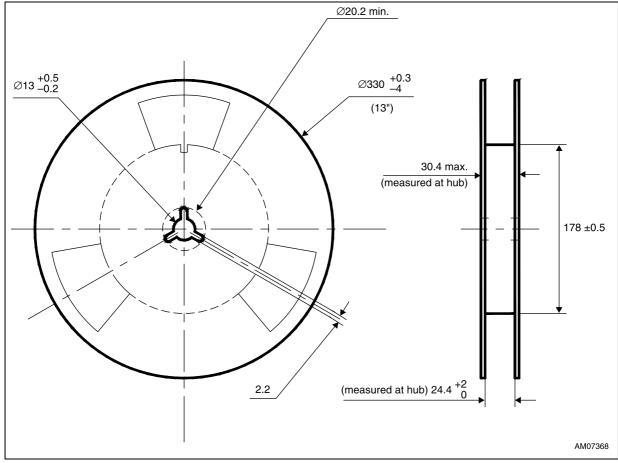

Figure 14. Reel information for QFN42 (3.5 x 9 x 0.75) - pitch 0.5 mm

STMUX1800E Revision history

# 5 Revision history

Table 15. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                              |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09-Dec-2009 | 1        | Initial release.                                                                                                                                                                                                     |

| 11-Oct-2010 | 2        | Document reformatted, updated <i>Features</i> and "max. low power mode" in <i>Table 10.</i> , replaced V <sub>DD</sub> by V <sub>CC</sub> , corrected typo in <i>Figure 1</i> , <i>Figure 3</i> to <i>Figure 7</i> . |

| 09-Nov-2011 | 3        | Corrected order code in <i>Table 1</i> , updated <i>Section 2</i> and Disclaimer, minor text corrections throughout document.                                                                                        |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2011 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 16772 Rev 3 26/26