# AMC-D1F1-1200

## DATASHEET

A state of the art signal processing card which combines a DSP and FPGA on a single width, mid-height AMC

Flexible processing and interconnect for high performance applications in military, industrial and medical

Also suitable for wireless baseband solutions including WiMax and LTE

10 Gbps data paths around the card and externally to chassis and front panel

### **KEY FEATURES**

- 1.2 GHz TI TMS320C6455 DSP

- Xilinx Virtex-4 FX100 FPGA, fully customer programmable

- Over 256 MB memory

- 10 Gbps 4x Serial RapidIO infrastructure

- Full Gigabit Ethernet infrastructure

- SRIO and programmable front panel I/O

- Connectors and space for addition of a mezzanine board

- Single width, mid-height PICMG AMC.0 R2.0 Advanced Mezzanine Card

- Software and firmware library support

- Developed for use in OEM products

- Fully supported with customisation options and OEM lifecycle services

#### **RESULTING BENEFITS**

- + Fastest available DSP resource

- + additional I/O, pre-processing or signal processing resource

- + extensive data storage

- + dependable high-bandwidth interconnect

- + industry standard interconnect

- + fast and flexible links to external data

- + additional custom I/O or processing resource can be added if required

- + flexible to work with Industry standard MicroTCA and AdvancedTCA systems

- + fast route to application code porting

- + reduces integration risk and speeds time to market

- + allows a detailed fit to specific OEM requirements

The CommAgility AMC-D1F1-1200 is a single width, mid-height Advanced Mezzanine Card offering unprecedented signal processing performance and bandwidth in a highly compact package, for wireless telecom, medical imaging, and other high performance applications. Using the fastest available DSP along with a large FPGA enables an application to be balanced and optimised for most effective use of resources and development time.

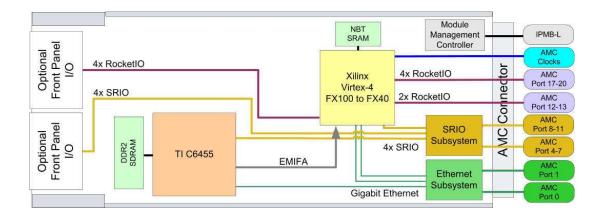

A full 10 Gbps SRIO infrastructure based on the PICMG AMC.4 standard provides the deterministic bandwidth needed for radio or other raw data transfers on and off card. Separate AMC.2 Gigabit Ethernet is provided for control, management and delivery of baseband or other processed data streams. Additional I/O is provided to the backplane or front panel via multiple high-speed serial ports.

Should modifications be required to make this product fit your OEM requirements, CommAgility are fully set up to support your needs through customisation of the hardware architecture or providing additional software and firmware.

Tel: +44 1509 228866 Fax: +44 8452 991150

#### HARDWARE SPECIFICATIONS

**DSP:** 1 x 1.2GHz TMS320C6455 DSP

- 256MB x32 DDR2-500 SDRAM

- Direct FPGA EMIF connection: 64bit/150MHz

- Connection to XDS510<sup>™</sup> emulator

- SRIO, Ethernet, HPI, McBSP & MMC connections

FPGA: Xilinx Virtex-4 FX100 FPGA:

- Dedicated DSP EMIF slave interface

- 9MB x36 200MHz SRAM

- 10Gbps 4x SRIO

- 2 Full-duplex Gigabit Ethernet ports

- 10Gbps Front Panel RocketIO<sup>™</sup>

RocketIO<sup>™</sup> connections to AMC ports 12-13 and 17-20

- Xilinx parallel cable connection

- Optional Chipscope header

Serial RapidIO: 10Gbps 4x infrastructure using Tundra TSI578

- AMC.4 compliant connections to AMC ports 4-7 and 8-11

- Dedicated 10Gbps 4x link to DSP

- Dedicated 10Gbps 4x link to FPGA

- Front Panel 10Gbps 4x Connector

**Ethernet:** Gigabit Ethernet infrastructure using Broadcom BCM5389:

- AMC.2 (1000BASE-BX) compliant connections to AMC Ports 0 & 1

- Full-duplex 1Gbps links

- 9300 byte Jumbo Packet support

- FPGA & AMC Fabric port pairs capable of bandwidth aggregation

IPMI: Atmega128 IPMI controller:

- AMC.0 IPMB L interface

- FRU EEPROM data

- Power and reset control

- · Real-time health monitoring

Form Factor: Advanced Mezzanine Card

- AMC.0 Rev 2.0 compliant

- Mid-height, single-width

- Usable in both AdvancedTCA<sup>TM</sup> and MicroTCA<sup>TM</sup> systems.

- AMC.2 Gigabit Ethernet

- AMC.4 4x Serial RapidIO

- Hot swap support

#### **CONFIGURATION AND DEBUG**

- DSP boot: EEPROM, Ethernet or SRIO

- FPGA loaded from DSP via SelectMap

- On-board debug LEDs for DSP, FPGA, power and Ethernet ports

- Debug connector and breakout board for XDS-510, Xilinx platform cable, DSP and MMC serial ports

#### **ENVIRONMENTAL/EMC/SAFETY**

- Operating temperature: 0-40 °C ambient

- Power consumption: up to 30W, dependent on software and FPGA load

- Designed for NEBS and ETSI compliance when used in appropriate chassis

- 2004/108/EC and FCC EMC compliant

- 2002/95/EC RoHS compliant

- 2002/96/EC WEEE compliant

- 2006/95/EC Low Voltage Directive compliant

#### **SOFTWARE SPECIFICATIONS**

**DSP library:** support for controlling board functions, interfaces and self test. TCP/IP stack also available for the DSP

**FPGA:** to demonstrate configuration and functionality; Xilinx ISE project

MMC: full management suite based on PigeonPoint BMR software

sales@commagility.com www.commagility.com

Tel: +44 1509 228866 Fax: +44 8452 991150

#### **OEM PARTNERSHIP SERVICES:**

#### IN DEVELOPMENT

support and training;

#### IN MANUFACTURE

components or prod-ucts; extended war-ranty and repair; quick turn repairs and/or spares stock-ing. Licensing of designs considered for

#### **DURING LIFECYCLE**

agement; guaranteed lifecycle; design infor-