# SN55450B - SN55454B, SN75451B - SN75454B

## **Dual Peripheral Drivers**

Series 55450B/75451B dual peripheral drivers are a family of versatile devices designed for use in systems that employ TTL logic. This family is functionally interchangeable with and replaces the 75450 family and the 75450A family of devices. The speed of 55450B/75451B family is equal to that of the 75450 family, and the parts have been designed to ensure freedom from latch-up. Diode clamped inputs simplify circuit design.

Typical applications include high-speed logic buffers, power drivers, relay drivers, lamp drivers, MOS drivers, line drivers, and memory drivers.

# **Rochester Electronics Manufactured Components**

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- · Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

91D 75850

Ď

SN55450B THRU SN55454B SN75451B THRU SN75454B DUAL PERIPHERAL DRIVERS

D2217, DECEMBER 1976-REVISED SEPTEMBER 1986

#### PERIPHERAL DRIVERS FOR HIGH-CURRENT SWITCHING AT VERY HIGH SPEEDS

- Characterized for Use to 300 mA

- High-Voltage Outputs

- No Output Latch-Up at 20 V (After Conducting 300 mA)

- High-Speed Switching

- Circuit Flexibility for Varied Applications

- TTL-Compatible Diode-Clamped inputs

- Standard Supply Voltages

- New Plastic DIP (P) with Copper Lead Frame Provides Cooler Operation and Improved Reliability

#### SUMMARY OF SERIES 55450B/75451B

| DEVICE   | LOGIC OF<br>COMPLETE CIRCUIT | PACKAGES |

|----------|------------------------------|----------|

| SN55450B | AND <sup>†</sup>             | FK,J     |

| SN55451B | AND                          | FK,JG    |

| SN55452B | NAND                         | FK,JG    |

| SN55453B | OR                           | FK,JG    |

| SN55454B | NOR                          | FK,JG    |

| SN75451B | ÄND                          | D,P      |

| SN75452B | NAND                         | D,P      |

| SN75453B | OR                           | D,P      |

| SN75454B | NOR                          | D,P      |

<sup>†</sup>With output transistor base connected externally to output of gate.

#### description

Series 55450B/75451B dual peripheral drivers are a family of versatile devices designed for use in systems that employ TTL logic. This family is functionally interchangeable with and replaces the 75450 family and the 75450A family devices manufactured previously. The speed of the 55450B/75451B family is equal to that of the 75450 family, and the parts have been designed to ensure freedom from latch-up. Diode-clamped inputs simplify circuit design.

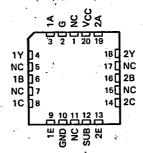

| SN55450B J PACKAGE<br>(TOP VIEW) |                              |  |  |  |  |  |  |

|----------------------------------|------------------------------|--|--|--|--|--|--|

| G [ 1 (                          | 714∏V <sub>CC</sub><br>13∏2A |  |  |  |  |  |  |

| 1Y 3                             | 13 1 2 A<br>12 2 Y           |  |  |  |  |  |  |

| 1B                               | 11                           |  |  |  |  |  |  |

| 1E []8                           | 9 2E                         |  |  |  |  |  |  |

| GND [7_                          | 8] SUB                       |  |  |  |  |  |  |

SN55450B . . . FK PACKAGE (TOP VIEW)

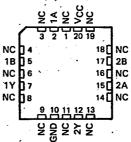

SN65451B, SN65452B, SN55453B, SN55454B . . . JG PACKAGE SN75451B, SN75452B, SN75453B, SN75454B . . . D OR P PACKAGE (TOP VIEW)

| 1A 🗌          | 1 | U <sub>8</sub> | ∐ vc          | С |

|---------------|---|----------------|---------------|---|

| 18 □          | 2 | 7              | <u>Б</u> 2в ́ |   |

| 1Y [<br>GND [ | 3 | 6              | 7 2A          |   |

| GND 🗔         | 4 | 5              | <b>5</b> 2 ₹  |   |

\$N55451B, \$N55452B, \$N55453B, \$N55454B, . . . FK PACKAGE (TQP VIEW)

NC-No internal connection

PRODUCTION DATA documents centain information current as of publication date. Products conform to specifications per the terms of Texas Instruments stendard warrenty. Production processing does not necessarily include testing of all parameters.

Copyright © 1981, Texas Instruments Incorporated

5-81

POST OFFICE BOX 855012 • DALLAS, TEXAS 76265

91D 75851

## SN55450B THRU SN55454B SN75451B THRU SN75454B **DUAL PERIPHERAL DRIVERS**

## description (cont'd) -

Typical applications include high-speed logic buffers, power drivers, relay drivers, lamp drivers. MOS drivers, line drivers, and memory drivers.

The SN55450B is a unique general-purpose device, featuring two standard Series 54 TTL gates and two uncommitted, high-current, high-voltage n-p-n transistors. The device offers the system designer the flexibility of tailoring the circuit to the application.

The SN55451B/SN75451B, SN55452B/SN75452B, SN55453B/SN75453B, and SN55454B/SN75454B are dual peripheral AND, NAND, OR, and NOR drivers, respectively, (assuming positive logic), with the output of the logic gates internally connected to the bases of the n-p-n output transistors.

Series 55450B drivers are characterized for operation over the full military range of -55°C to 125°C. Series 75451B drivers are characterized for operation from 0°C to 70°C.

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

|                                                                                          | •               |             | SN55451B   | SN75451B                                         | -                |

|------------------------------------------------------------------------------------------|-----------------|-------------|------------|--------------------------------------------------|------------------|

|                                                                                          |                 | SN55450B    | SN55452B   | SN75452B                                         | UNIT             |

|                                                                                          |                 | 0.1.001.000 | SN55453B   | SN75453B                                         | ONII             |

|                                                                                          |                 | SN55454B    | SN75454B   |                                                  |                  |

| Supply voltage, VCC (see Note 1)                                                         |                 | 7           | 7          | 7                                                | v                |

| Input voltage                                                                            |                 | 5.5         | 5.5        | 5.5                                              | V                |

| Interemitter voltage (see Note 2)                                                        |                 | 5.5         | 5.5        | 5,5                                              | v                |

| VCC-to-substrate voltage                                                                 |                 | 35          |            |                                                  | V                |

| Collector-to-substrate voltage                                                           |                 | 35          |            |                                                  | v                |

| Collector-base voltage                                                                   |                 | 35          |            |                                                  | v                |

| Collector-emitter voltage (see Note 3)                                                   |                 | 30          | <b> </b>   | <del>                                     </del> | v                |

| Emitter-base voltage                                                                     |                 | 5           | · · ·      |                                                  | <del>`</del>     |

| Off-state output voltage                                                                 |                 |             | 30         | 30                                               | <del>- v</del> - |

| Continuous collector or output current (see N                                            | lote 4)         | 400         | 400        | 400                                              | mA               |

| Peak collector or output current<br>(t <sub>W</sub> ≤ 10 ms, duty cycle ≤ 50%, (see Note | 500             | 500         | 500        | mA                                               |                  |

| • • • •                                                                                  | D package       |             |            | 725                                              |                  |

| Continuous total dissipation at (or below)                                               | FK package      | 1375        | 1375       |                                                  |                  |

| 25 °C free-air temperature (see Note 5)                                                  | J package       | 1375        |            |                                                  | mW               |

| 1100 all temperature (300 140(8 8)                                                       | JG package      |             | 1050       |                                                  |                  |

|                                                                                          | P package       |             |            | 1200                                             |                  |

| Operating free-air temperature range                                                     |                 | -55 to 125  | -55 to 125 | 0 to 70                                          | °C               |

| Storage temperature range                                                                |                 | -65 to 150  | -65 to 150 | -65 to 150                                       | • <u>c</u>       |

| Case temperature for 60 seconds                                                          | FK package      | 260         | 260.       |                                                  | °C               |

| ead temperature 1,6 mm<br>1/16 inch) from case for 60 seconds                            | J or JG package | 300         | 300        |                                                  | °C               |

| ead temperature 1,6 mm<br>1/16 inch) from case for 10 seconds                            | D or P package  |             |            | 260                                              | °C               |

Voltage values are with respect to the network ground terminal unless otherwise specified.

This is the voltage between two emitters of a multiple-emitter transistor.

This value applies when the base-emitter resistance (RgE) is equal to or less than 500 Ω.

Both halves of these dual circuits may conduct rated current simultaneously; however, power dissipation averaged over a short time interval must fall within the continuous dissipation rating.

For operation above 25 °C free-air temperature, refer to the Dissipation Derating Table.

91D 75852

n

SN55450B THRU SN55454B SN75451B THRU SN75454B DUAL PERIPHERAL DRIVERS

| DIS     | SIPATION DE     | RATING TABLE       |                         |

|---------|-----------------|--------------------|-------------------------|

| PACKAGE | POWER<br>RATING | DERATING<br>FACTOR | ABOVE<br>T <sub>A</sub> |

| D       | 725 mW          | 5.8 mW/°C          | 25°C                    |

| FK      | 1375 mW         | 11.0 mW/°C         | 25°C                    |

| .1      | 1376 mW         | 11.0 mW//90        | 25.00                   |

8.4 mW/°C

9.6 mW/°C

25°C

25°C

1050 mW

1200 mW

サー5セー17

## recommended operating conditions (see Note 6)

|                                    | SI  | SERIES 55450B |     |      | SERIES 76451B |      |      |

|------------------------------------|-----|---------------|-----|------|---------------|------|------|

|                                    | MIN | NOM           | MAX | MIN  | NOM           | MAX  | UNIT |

| Supply voltage, VCC                | 4.5 | 5             | 5.5 | 4.75 | 5             | 5.25 | v    |

| High-level input voltage, VIH      | 2.2 |               |     | 2    |               |      | V    |

| Low-level input voltage, VIL       | ·   |               | 8.0 |      |               | 0.8  | v    |

| Operating free-air temperature, TA | -55 |               | 125 | 0    |               | 70   | °C   |

NOTE 6: For the SN55450B only, the substrate (pin 8) must always be at the most negative device voltage for proper operation.

Peripheral Drivers/Actuators

91D 75853

T-5a-17

Đ

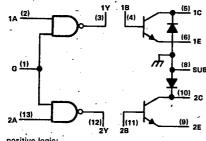

## SN55450B **DUAL PERIPHERAL POSITIVE AND DRIVER**

8961724 TEXAS INSTR (LIN/INTFC)

logic symbol† (4) 18 (5) 1C (6) 1E G (1) (12) 2Y (11) 28 (10) 2C 2A (13) (9) 2E

†This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

## logic diagram (positive logic)

positive logic:

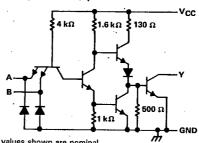

$Y = \overline{AG}$  or  $\overline{A} + \overline{G}$  (gate only) C = AG or  $\overline{A} + \overline{G}$  (gate and transistor)

Pin numbers shown are for the J package.

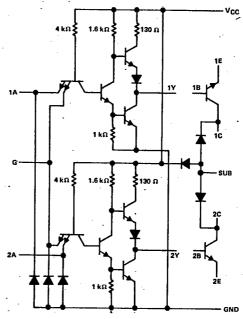

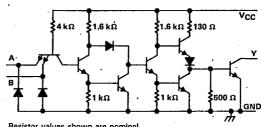

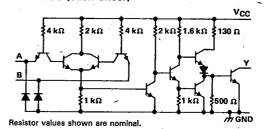

#### schematic

Resistor values shown are nominal.

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

### TTL gates

| PARAMETER |                                           |         | TEST SON                                            | TEST CONDITIONS          |     | SN55450B |      |      |

|-----------|-------------------------------------------|---------|-----------------------------------------------------|--------------------------|-----|----------|------|------|

| <u> </u>  | PARAMETER                                 |         | IEST CON                                            | DITIONS*                 | MIN | TYP§     | MAX  | UNIT |

| VIK       | Input clamp voltage                       |         | V <sub>CC</sub> = MIN,                              | lj = -12 mA              |     | -1.2     | -1.5 | V    |

| VoH       | High-level output voltage                 |         | V <sub>CC</sub> = MIN,<br>I <sub>OH</sub> = -400 μA | V <sub>IL</sub> = 0.8 V, | 2.4 | 3.3      | ·    | V    |

| VOL       | Low-level output voltage                  |         | V <sub>CC</sub> = MIN,<br>I <sub>OL</sub> = 16 mA   | V <sub>IH</sub> = MIN,   |     | 0.25     | 0.5  | V    |

|           | Input current at maximum<br>input voltage | input A |                                                     |                          |     |          | 1    |      |

| <u> </u>  |                                           | input G | V <sub>CC</sub> = MAX,                              | $V_i = 5.5 V$            |     |          | 2    | mA   |

|           |                                           | input A |                                                     |                          | -   |          | 40   |      |

| ļiH       | High-level input current                  | input G | VCC = MAX,                                          | $V_1 = 2.4 V$            |     |          | 80   | μΑ   |

|           |                                           | input A |                                                     |                          |     |          | -1.6 |      |

| IL        | Low-level input current                   | input G | VCC = MAX,                                          | V <sub>j</sub> = 0.4 V   |     |          | -3.2 | mA   |

| os        | Short-circuit output current¶             |         | VCC = MAX, -                                        | V <sub>O</sub> = 0       | -18 | -35      | -55  | mA   |

| ССН       | Supply current, outputs high              |         | VCC = MAX,                                          | V <sub>I</sub> = 0       |     | 2.8      | 4    | mA   |

| CCL       | Supply current, outputs low               |         | VCC = MAX,                                          | V <sub>I</sub> = 5 V     |     | 7        | 11   | mA   |

For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions. All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

Not more than one output should be shorted at a time.

POST OFFICE BOX 655012 . DALLAS, TEXAS 75265

91D 75854

## SN55450B **DUAL PERIPHERAL POSITIVE-AND DRIVER**

electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

## output transistors

|                      | PARAMETER                                              | 7507 0011011011                                  | TEST COMPLETIONS |     | SN55450B |     |      |  |

|----------------------|--------------------------------------------------------|--------------------------------------------------|------------------|-----|----------|-----|------|--|

|                      | PARAMETER                                              | TEST CONDITION                                   | ST               | MIN | TYP#     | MAX | UNIT |  |

| V <sub>(BR)CBO</sub> | Collector-base<br>breakdown voltage                    | I <sub>C</sub> = 100 μA, I <sub>E</sub> = 0      |                  | 35  |          |     | v    |  |

| V <sub>(BR)CER</sub> | Collector-emitter<br>breakdown voltage                 | I <sub>C</sub> = 100 μA, R <sub>BE</sub> = 500 Ω |                  | 30  |          |     | v    |  |

| V <sub>(BR)EBO</sub> | Emitter-base<br>breakdown voltage                      | I <sub>E</sub> = 100 μA, I <sub>C</sub> = 0      |                  | 5   |          |     | v    |  |

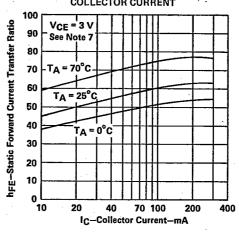

| · -                  |                                                        | VCE = 3 V, TA = 25°C                             | IC = 100 mA      | 25  |          |     |      |  |

| h                    | Static forward current                                 | See Note 7                                       | IC = 300 mA      | 30  |          |     | 1 .  |  |

| pŁE                  | transfer ratio                                         | VCE = 3 V, TA = MIN,                             | Ic = 100 mA      | 10  |          |     | 1    |  |

|                      |                                                        | See Note 7                                       | Ic = 300 mA      | 15  |          |     | 1 '  |  |

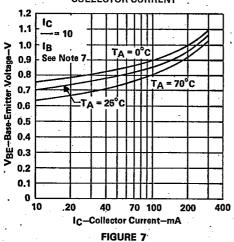

| VBE                  | Base-emitter voltage                                   | IB = 10 mA, IC = 100 mA,                         | See Note 7       |     | 0.85     | 1.2 |      |  |

| ABE                  | base-emitter voitage                                   | $I_B = 30 \text{ mA}, I_C = 300 \text{ mA},$     | See Note 7       |     | 1        | 1.4 | \ \  |  |

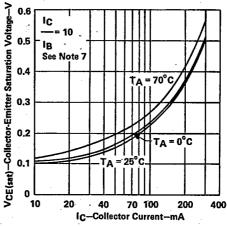

| Voc                  | Collector-emitter                                      | IB = 10 mA, IC = 100 mA,                         | See Note 7       |     | 0.25     | 0.5 |      |  |

| V <sub>CE(sat)</sub> | saturation voltage IB = 30 mA, IC = 300 mA, See Note 7 |                                                  | See Note 7       |     | 0.45     | 0.8 | l v  |  |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.  $^{\ddagger}$  All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C. NOTE 7: These parameters must be measured using pulse techniques.  $t_{W}$  = 300  $\mu$ s, duty cycle  $\leq$  2%.

## switching characteristics, VCC = 5 V, TA = 25 °C

## TTL gates

| PARAMETER                     | TE                      | MIN                  | TYP          | MAX | UNIT |   |      |

|-------------------------------|-------------------------|----------------------|--------------|-----|------|---|------|

| Propagation delay time,       | ,                       |                      |              |     |      |   |      |

| tPLH low-to-high-level output | 0 45.5                  | $R_L = 400 \Omega$ , |              | 12  |      | ļ | ns . |

| Propagation delay time,       | C <sub>L</sub> = 15 pF, |                      | See Figure 1 |     |      |   |      |

| tpHL high-to-low-level output |                         |                      |              |     | . 8  | 1 | ns   |

## output transistors

|    | PARAMETER    | TEST CONDITIONS <sup>§</sup>                                            | MIN | TYP MAX | UNIT |

|----|--------------|-------------------------------------------------------------------------|-----|---------|------|

| td | Delay time   | IC = 200 mA, IR(1) = 20 mA, IR(2) = -40 mA,                             |     | 8       | nş   |

| tr | Rise time    | 0(1)                                                                    |     | 12      | ns   |

| ts | Storage time | $V_{BE(off)} = -1 V$ , $C_L = 15 pF$ , $R_L = 50 \Omega$ , See Figure 2 |     | 7       | ns   |

| tf | Fall time    | occ riguio 2                                                            |     | 6       | ns   |

<sup>§</sup> Voltage and current values shown are nominal; exact values vary slightly with transistor parameters.

## gate and transistors combined

| PARAMETER                                             | TEST CON                                           | MIN                          | TYP                 | MAX | UNIT |    |

|-------------------------------------------------------|----------------------------------------------------|------------------------------|---------------------|-----|------|----|

| tplH Propagation delay time, low-to-high-level output |                                                    |                              |                     | 20  | 30   | ns |

| tpн_ Propagation delay time, high-to-low-level output | IC ≈ 200 mA,                                       | Cլ = 15 pF,                  |                     | 20  | 30   | ns |

| tTLH Transition time, low-to-high-level output        | $R_L = 50 \Omega_r$                                | See Figure 3                 |                     | .7  | 12   | ns |

| tTHL Transition time, high-to-low-level output        |                                                    |                              |                     | 9   | 15   | กร |

| VOH High-level output voltage after switching         | V <sub>S</sub> = 20 V,<br>R <sub>BE</sub> = 500 Ω, | IC ≈ 300 mA,<br>See Figure 4 | V <sub>S</sub> -6.5 |     |      | mV |

## SN55451B, SN75451B **DUAL PERIPHERAL POSITIVE-AND DRIVERS**

T-52-17

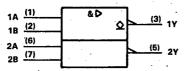

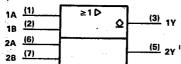

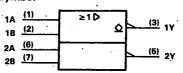

logic symbol†

<sup>†</sup>This symbol is in accordance with ANSI/IEEE STD 91-1984 and IEC Publication 617-12.

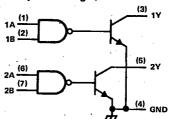

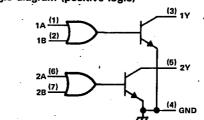

## logic diagram (positive logic)

FUNCTION TABLE (EACH DRIVER)

|   | Α | В | Υ             |

|---|---|---|---------------|

|   | L | L | L (on state)  |

| j | L | H | L (on state)  |

|   | H | L | L (on state)  |

|   | Н | Н | H (off state) |

sitive logic: = AB or A+B

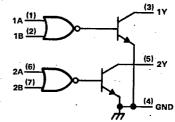

schematic (each driver)

Resistor values shown are nominal.

Peripheral Drivers/Actuators

Pin numbers shown are for D, JG, and P packages.

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                               | PARAMETER '                                        | TEST CONDITIONS‡                                   |                          | SN55451B |      |      | SN75451B |      |      |       |

|-------------------------------|----------------------------------------------------|----------------------------------------------------|--------------------------|----------|------|------|----------|------|------|-------|

|                               |                                                    |                                                    |                          | MIN TYPS |      | MAX  | MIN TYPS |      | MAX  | UNIT  |

| VIK                           | Input clamp voltage                                | V <sub>CC</sub> = MIN,                             | I <sub>I</sub> = -12 mA  |          | -1.2 | -1.5 |          | -1.2 | ~1.5 | l v   |

| ЮН                            | High-level output current                          | V <sub>CC</sub> = MIN,<br>V <sub>OH</sub> = 30 V   | VIH = MIN,               |          |      | 300  |          |      | 100  | μА    |

| Vol. Low-level output voltage | V <sub>CC</sub> = MIN,<br>I <sub>OL</sub> = 100 mA | V <sub>IL</sub> = 0.8 V,                           |                          | 0.25     | 0.5  |      | 0.25     | 0.4  | .:   |       |

|                               | AOF rom-level ontbut holtage                       | V <sub>CC</sub> = MIN,<br>I <sub>OL</sub> = 300 mA | V <sub>IL</sub> = 0.8 V, |          | 0.5  | 8.0  |          | 0.5  | 0.7  | \ \ \ |

| 4                             | Input current at maximum input voltage             | V <sub>CC</sub> = MAX,                             | $V_1 = 5.5 \text{ V}$    |          |      | 1    |          |      | 1    | mA    |

| lН                            | High-level Input current                           | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 2.4 V   |          |      | 40   |          |      | 40   | μА    |

| կլ                            | Low-level input current                            | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 0.4 V   |          | - 1  | -1.6 |          | -1   | 1,6  | mA    |

| ССН                           | Supply current, outputs high                       | VCC = MAX,                                         | V <sub>I</sub> = 5 V     |          | 7    | 11   |          | 7    | 11   | mA    |

| ICCL                          | Supply current, outputs low                        | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 0       |          | 52   | 65   |          | 52   | 65   | mA    |

$^{\ddagger}$  For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.  $^{\ddagger}$  All typical values are at VCC = 5 V, TA = 25 °C.

## switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_A = 25 \,^{\circ}\text{C}$

| PARAMETER                                                  | TEST CONDITIONS                                                    | MIN      | TYP | MAX | UNIT |

|------------------------------------------------------------|--------------------------------------------------------------------|----------|-----|-----|------|

| tpLH Propagation delay time, low-to-high-level output      |                                                                    |          | 18  | 25  | ns   |

| tphL Propagation delay time, high-to-low-level output      | $I_0 \approx 200 \text{ mA},  C_L = 15 \text{ pF},$                |          | 18  | 25  | ns   |

| tŢĹĦ Transition time, low-to-high-level output             | $R_1 = 50 \Omega$ , See Figure 3                                   | <u> </u> | 5   |     | ns   |

| t <sub>THL</sub> Transition time, high-to-low-level output |                                                                    | <u> </u> | 7   | 12  | ns   |

| VOH High-level output voltage after switching              | $V_S = 20 \text{ V}$ , $I_O \approx 300 \text{ mA}$ , See Figure 4 | VS-6.5   |     |     | mV   |

Texas VI

91D 75856

## SN55452B. SN75452B **DUAL PERIPHERAL POSITIVE-NAND DRIVERS**

T-52-17

## logic symbol†

<sup>†</sup>This symbol is in accordance with ANSI/IEEE STD 91-1984 and IEC Publication 617-12.

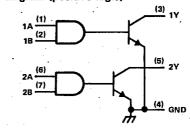

## logic diagram (positive logic)

#### **FUNCTION TABLE** (EACH DRIVER)

| Α | В | Υ             |

|---|---|---------------|

| L | L | H (off state) |

| L | Н | H (off state) |

| Н | L | H (off state) |

| Н | н | L (on state)  |

positive logic: Y = AB or A+B

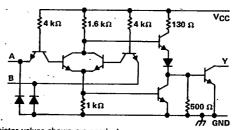

#### schematic (each driver)

Pin numbers shown are for D, JG, and P packages.

Resistor values shown are nominal.

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                  |                                        | TEGT 001                                           | IDITIONO <sup>‡</sup>    | SN | 55452    | В    | SN75452B |      |       | UNIT |

|------------------|----------------------------------------|----------------------------------------------------|--------------------------|----|----------|------|----------|------|-------|------|

| İ                | PARAMETER                              | 1E9 LCOM                                           | TEST CONDITIONS          |    | MIN TYPS |      | MIN      | TYP§ | MAX   |      |

| ΛίΚ              | Input clamp voltage                    | V <sub>CC</sub> = MIN,                             | lı = -12 mA              |    | ÷1.2     | -1.5 |          | 1.2  | -1.5  | V    |

| ļон              | High-level output current              | V <sub>CC</sub> = MIN,<br>V <sub>OH</sub> = 30 V   | V <sub>IL</sub> = 0.8 V, |    |          | 300  |          |      | 100   | μА   |

| Voi              | VOL Low-level output voltage           | V <sub>CC</sub> = MIN,<br>I <sub>OL</sub> = 100 mA | VIH = MIN,               |    | 0.25     | 0.5  |          | 0.25 | 0.4   | V    |

|                  | - Constitution output voltage          | V <sub>CC</sub> = MIN,<br>I <sub>OL</sub> = 300 mA | V <sub>IH</sub> = MIN,   |    | 0.5      | 0.8  |          | 0.5  | . 0.7 | ] `  |

| ij               | Input current at maximum input voltage | VCC = MAX,                                         | V <sub>I</sub> = 5.5 V   |    |          | . 1  |          |      | 1     | mA   |

| I <sub>I</sub> H | High-level input current               | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 2.4 V   |    |          | 40   |          |      | 40    | μΑ   |

| IIL.             | Low-level input current                | VCC = MAX,                                         | V <sub>I</sub> = 0.4 V   |    | -1.1     | -1.6 |          | -1.1 | -1.6  | mA   |

| Іссн             | Supply current, outputs high           | VCC = MAX,                                         | V <sub>1</sub> = 0       |    | 11       | 14   |          | 11   | 14    | mA   |

| CCL              | Supply current, outputs low            | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 5 V     |    | 56       | 71   |          | .56  | 71    | mA   |

For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.  $^{\S}$ All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25 ^{\circ}\text{C}$ .

## switching characteristics, VCC = 5 V, TA = 25 °C

| PARAMETER                                                  | TEST CONDITIONS                                                 | MIN | TYP | MAX | UNIT |

|------------------------------------------------------------|-----------------------------------------------------------------|-----|-----|-----|------|

| tpLH Propagation delay time, low-to-high-level output      |                                                                 | 7   | 26  | 35  | ns   |

| tpHL Propagation delay time, high-to-low-level output      | Jo ≈ 200 mA, C <sub>L</sub> = 15 pF,                            |     | 24  | 35  | ns   |

| t <sub>TLH</sub> Transition time, low-to-high-level output | $R_L = 60 \Omega$ , See Figure 3                                |     | 5   | 8   | ns   |

| t <sub>THL</sub> Transition time, high-to-low-level output |                                                                 |     | 7   | 12  | ns   |

| VOH High-level output voltage after switching              | V <sub>S</sub> = 20 V, I <sub>O</sub> ≈ 300 mA,<br>See Figure 4 | Vs- | 6.5 |     | mV   |

91D 75857 D

## SN55453B, SN75453B **DUAL PERIPHERAL POSITIVE-OR DRIVERS**

T-52-17

## logic symbol†

<sup>†</sup>This symbol is in accordance with ANSI/IEEE STD 91-1984 and IEC Publication 617-12.

## logic diagram (positive logic)

#### **FUNCTION TABLE** (EACH DRIVER)

| I | Α | В   | Y             |

|---|---|-----|---------------|

| I | L | L   | L (on state)  |

| 1 | Ļ | Н   | H (off state) |

| ١ | Н | ٠ ٢ | H (off state) |

| L | Н | н   | H (off state) |

positive logic:  $Y = A + B \text{ or } \overline{AB}$

schematic (each driver)

Resistor values shown are nominal.

# Pin numbers shown are for D, JG, and P packages.

# electrical characteristics over recommended operating free-air temperature range (unless otherwise

| •    | PARAMETER                              | TEST CON                                           | TEST CONDITIONS <sup>‡</sup> |           | SN55453B |          |     | SN75453B |      |      |

|------|----------------------------------------|----------------------------------------------------|------------------------------|-----------|----------|----------|-----|----------|------|------|

|      |                                        | 1231 CON                                           |                              |           | MIN TYPS |          | MIN | TYPS     | MAX  | UNIT |

| ViK  | Input clamp voltage                    | V <sub>CC</sub> = MIN,                             | I <sub>1</sub> = -12 mA      | -1.2 -1.5 |          | -1.2 -1, |     | ~1.5     | V    |      |

| юн   | High-level output current              | V <sub>CC</sub> = MIN,<br>V <sub>OH</sub> = 30 V   | V <sub>IH</sub> = MIN,       |           |          | 300      |     |          | 100  | μА   |

| Vol  | Low-level output voltage               | V <sub>CC</sub> = MIN,<br>I <sub>OL</sub> = 100 mA | V <sub>IL</sub> = 0.8 V,     |           | 0.25     | 0.5      |     | 0.25     | 0.4  |      |

|      | AOL row-level output voltage           | V <sub>CC</sub> = MIN,<br>I <sub>OL</sub> = 300 mA | V <sub>IL</sub> = 0.8 V,     |           | 0.5      | 0.8      |     | 0.5      | 0.7  | ^    |

| 1    | Input current at maximum input voltage | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 5.5 V       |           |          | 1        |     |          | 1    | mA   |

| lн   | High-level input current               | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 2.4 V       |           | •        | 40       |     | -        | 40   | μА   |

| ΙL   | Low-level input current                | VCC = MAX,                                         | V <sub>i</sub> = 0.4 V       |           | -1       | -1.6     |     | -1       | -1.6 | mA   |

| ССН  | Supply current, outputs high           | VCC = MAX,                                         | V <sub>I</sub> = 5 V         |           | 8        | 11       |     | 8        | 11   | mA   |

| ICCL | Supply current, outputs low            | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 0           | ·         | 54       | 68       |     | 54       | 68   | mA   |

‡For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions. § All typical values are at VCC = 5 V, TA = 25 °C.

## switching characteristics, VCC = 5 V, TA = 25 °C

| PARAMETER                                             | TEST CON                                                                            | IDITIONS                                 | MIN                     | TYP | MAX | UNIT |

|-------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------|-------------------------|-----|-----|------|

| tplH Propagation delay time, low-to-high-level output |                                                                                     |                                          |                         | 18  | 25  | ns   |

| tpнլ Propagation delay time, high-to-low-level output | but $I_{O} \approx 200 \text{ mA}$ , $R_{L} = 60 \Omega$ , $V_{S} = 20 \text{ V}$ . | C <sub>L</sub> =, 15 pF,<br>See Figure 3 |                         | 16  | 25  | ns   |

| tŢĹĦ Transition time, low-to-high-level output        |                                                                                     |                                          |                         | 5   | 8   | ns   |

| tTHL Transition time, high-to-low-level output        | · · · · · · · · · · · · · · · · · · ·                                               | -                                        |                         | 7.  | 12  | ns   |

| VOH High-level output voltage after switching         | V <sub>S</sub> = 20 V,<br>See Figure 4                                              | IO ≈ 300 mA,                             | 7 · V <sub>S</sub> -8.5 |     | :   | mV   |

5-88

T-52-17

logic symbol†

8961724 TEXAS INSTR (LIN/INTFC)

<sup>†</sup>This symbol is in accordance with ANSI/IEEE STD 91-1984 and IEC Publication 617-12.

## logic diagram (positive logic)

**FUNCTION TABLE** (EACH DRIVER)

| Α  | В | Y             |

|----|---|---------------|

| L  | L | H (off state) |

| L  | Н | L (on state)  |

| Н. | L | L (on state)  |

| Н  | н | L (on state)  |

positive logic:  $Y = \overline{A + B}$  or  $\overline{AB}$  schematic (each driver)

Pin numbers shown are for D,-JG, and P packages.

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                              | PARAMETER                              | TEST CON                                           | DITIONE#                 | SN5545   | 4B   | SN75454  |      |      |

|------------------------------|----------------------------------------|----------------------------------------------------|--------------------------|----------|------|----------|------|------|

|                              | · AIDANE I EII                         | TEST CONDITIONS.                                   |                          | MIN TYPS | MAX  | MIN TYPS | MAX  | UNIT |

| VIK                          | input clamp voltage                    | V <sub>CC</sub> = MIN,                             | I <sub>I</sub> = -12 mA  | -1.2     | -1.5 | 1.2      | -1.5 | V    |

| ЮН                           | High-level output current              | V <sub>CC</sub> = MIN,<br>V <sub>OH</sub> = 30 V   | V <sub>IL</sub> = 0.8 V, | -        | 300  |          | 100  | μA   |

| Voi Low-level output voltage | Low-level output voltage               | V <sub>CC</sub> = MIN,<br>I <sub>OL</sub> = 100 mA | V <sub>IH</sub> = MIN,   | 0.25     | 0.5  | 0.25     | 0.4  | V    |

| -02                          |                                        | V <sub>CC</sub> = MIN,<br>I <sub>OL</sub> = 300 mA | VIH = MIN,               | 0.5      | 8.0  | 0.5      | 0.7  | 1    |

| Į(                           | Input current at maximum input voltage | VCC = MAX,                                         | V <sub>I</sub> = 5.5 V   |          | 1    |          | 1    | mA   |

| <u>Чн</u>                    | High-level input current               | VCC = MAX,                                         | V <sub>I</sub> = 2.4 V   |          | 40   |          | 40   | μA   |

| ηL                           | Low-level input current                | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 0.4 V   | -1       | -1.6 | -1       | -1.6 | mA   |

| ССН                          | Supply current, outputs high           | VCC = MAX,                                         | V <sub>I</sub> = 0       | 13       | 17   | 13       | 17   | mA   |

| CCL                          | Supply current, outputs low            | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 5 V     | 61       | 79   | 61       | 79   | mA   |

For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions. SAII typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25 \,^{\circ}\text{C}$ .

## switching characteristics, VCC = 5 V, TA = 25 °C

| PARAMETER                                                  | TEST CONDITIONS |              |     | TYP   | MAX | UNIT |

|------------------------------------------------------------|-----------------|--------------|-----|-------|-----|------|

| tpLH Propagation delay time, low-to-high-level output      |                 |              |     | 27    | 35  | ns   |

| tpHL Propagation delay time, high-to-low-level output      | Output          | CL = 15 pF,  | .   | 24    | 35  | ns   |

| tŢĹĦ Transition time, low-to-high-level output             |                 | See Figure 3 |     | 5     | 8   | ns   |

| t <sub>THL</sub> Transition time, high-to-low-level output |                 |              | 7   | 12    | ns  |      |

| VOH High-level output voltage after switching              | •               | IO ≈ 300 mA, | Vs- | - 6.5 |     | mV   |

POST OFFICE BOX 655012 . DALLAS, TEXAS 75265

SN55450B **DUAL PERIPHERAL DRIVER**

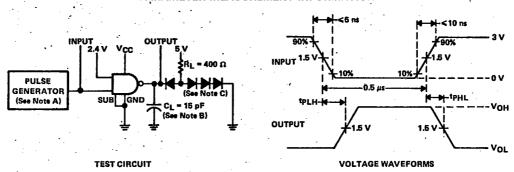

## PARAMETER MEASUREMENT INFORMATION

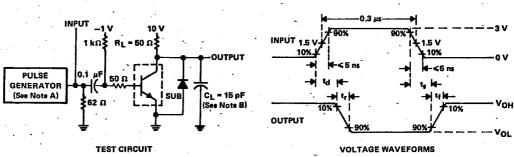

NOTES: A. The pulse generator has the following characteristics: PRR  $\leq$  1 MHz, Z $_{

m out}$  = 50  $\Omega$ .

B. CL includes probe and jig capacitance.

C. All diodes are 1N3084.

## FIGURE 1. PROPAGATION DELAY TIMES, EACH GATE (SN55450B ONLY)

NOTES: A. The pulse generator has the following characteristics: duty cycle  $\leq$  1%, Z<sub>out</sub>  $\approx$  50  $\Omega$ . B. Ct includes probe and jig capacitance.

FIGURE 2. SWITCHING TIMES, EACH TRANSISTOR (SN55450B ONLY)

TEST CIRCUIT.

**VOLTAGE WAVEFORMS**

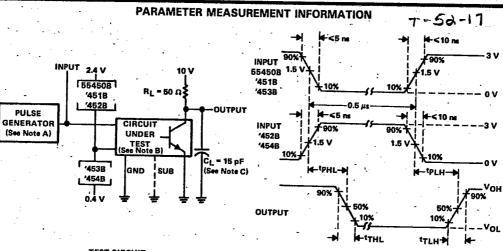

- NOTES: A. The pulse generator has the following characteristics: PRR ≤ 1 MHZ, Z<sub>out</sub> ≈ 50 Ω.

B. When testing SN55450B, connect output Y to transistor base and ground the substrate terminal.

C. C<sub>L</sub> includes probe and jig capacitance.

## FIGURE 3. SWITCHING TIMES OF COMPLETE DRIVERS

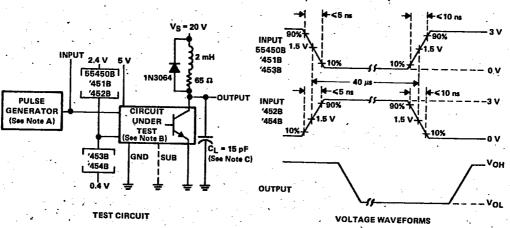

- NOTES: A. The pulse generator has the following characteristics: PRR  $\leq$  12.5 kHz, Z<sub>out</sub> = 50  $\Omega$ .

- B. When testing SN55450B, connect output Y to transistor base with a 500-Ω resistor from there to ground, and ground the substrate terminal.

- C. CL includes probe and jig capacitance.

FIGURE 4. LATCH-UP TEST OF COMPLETE DRIVERS

POST OFFICE BOX 655012 + DALLAS, TEXAS 75265

Peripheral Drivers/Actuators

**SN55450B THRU SN55454B** SN75451B THRU SN75454B **DUAL PERIPHERAL DRIVERS**  T-52-17

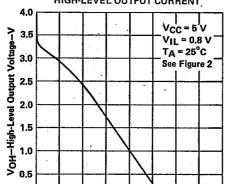

## TYPICAL CHARACTERISTICS

HIGH-LEVEL OUTPUT VOLTAGE

HIGH-LEVEL OUTPUT CURRENT

IOH-High Level Output Current-mA FIGURE 5

-5 -10 -15 -20 -25 -30 -35

TRANSISTOR **BASE-EMITTER VOLTAGE**

VS COLLECTOR CURRENT

TRANSISTOR STATIC FORWARD CURRENT TRANSFER RATIO

COLLECTOR CURRENT

FIGURE 6

#### TRANSISTOR **COLLECTOR-EMITTER SATURATION VOLTAGE**

COLLECTOR CURRENT

FIGURE 8

NOTE 7: These parameters must be measured using pulse techniques,  $t_{\rm W} = .300~\mu s$ , duty cycle  $\le 2\%$ .

TEXAS 💖 INSTRUMENTS

POST OFFICE BOX 655012 • DALLAS, TEXAS 75265

Peripheral Drivers/Actuators

5-92