## **ICL7660S**

## Super Voltage Converter

The ICL7660S Super Voltage Converter is a monolithic CMOS voltage conversion IC that guarantees significant performance advantages over other similar devices. It is a direct replacement for the industry standard ICL7660 offering an extended operating supply voltage range up to 12V, with lower supply current. No external diode is needed for the ICL7660S. In addition, a Frequency Boost pin has been incorporated to enable the user to achieve lower output impedance despite using smaller capacitors. All improvements are highlighted in the Electrical Specifications section. Critical parameters are guaranteed over the entire commercial, industrial and military temperature ranges.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- · Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

Data Sheet January 2004 FN3179.3

## Super Voltage Converter

The ICL7660S Super Voltage Converter is a monolithic CMOS voltage conversion IC that guarantees significant performance advantages over other similar devices. It is a direct replacement for the industry standard ICL7660 offering an **extended** operating supply voltage range up to 12V, with **lower** supply current. **No external diode** is needed for the ICL7660S. In addition, a **Frequency Boost pin** has been incorporated to enable the user to achieve lower output impedance despite using smaller capacitors. All improvements are highlighted in the Electrical Specifications section. **Critical parameters are guaranteed over the entire commercial, industrial and military temperature ranges.**

The ICL7660S performs supply voltage conversion from positive to negative for an input range of 1.5V to 12V, resulting in complementary output voltages of -1.5V to -12V. Only 2 non-critical external capacitors are needed for the charge pump and charge reservoir functions. The ICL7660S can be connected to function as a voltage doubler and will generate up to 22.8V with a 12V input. It can also be used as a voltage multiplier or voltage divider.

The chip contains a series DC power supply regulator, RC oscillator, voltage level translator, and four output power MOS switches. The oscillator, when unloaded, oscillates at a nominal frequency of 10kHz for an input supply voltage of 5.0V. This frequency can be lowered by the addition of an external capacitor to the "OSC" terminal, or the oscillator may be over-driven by an external clock.

The "LV" terminal may be tied to GND to bypass the internal series regulator and improve low voltage (LV) operation. At medium to high voltages (3.5V to 12V), the LV pin is left floating to prevent device latchup.

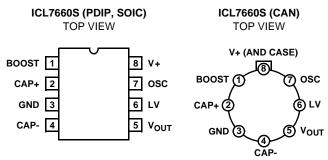

### **Pinouts**

### **Features**

- Guaranteed Lower Max Supply Current for All Temperature Ranges

- Wide Operating Voltage Range 1.5V to 12V

- 100% Tested at 3V

- No External Diode Over Full Temperature and Voltage Range

- Boost Pin (Pin 1) for Higher Switching Frequency

- Guaranteed Minimum Power Efficiency of 96%

- Improved Minimum Open Circuit Voltage Conversion Efficiency of 99%

- Improved SCR Latchup Protection

- Simple Conversion of +5V Logic Supply to±5V Supplies

- Simple Voltage Multiplication \( \frac{1}{2} \) UT = (-)nVIN

- Easy to Use Requires Only2 External Non-Critical Passive Components

- Improved Direct Replacement for Industry Standard ICL7660 and Other Second Source Devices

- Available in Lead Free

## **Applications**

- Simple Conversion of +5V to±5V Supplies

- Voltage Multiplication Y<sub>UT</sub> = ±nV<sub>IN</sub>

- Negative Supplies for DataAcquisition Systems and Instrumentation

- RS232 Power Supplies

- Supply Splitter, \( \forall UT = \pm V\_S/2 \)

## **Ordering Information**

| •                         |                     |                                            |               |

|---------------------------|---------------------|--------------------------------------------|---------------|

| PART#                     | TEMP.<br>RANGE (°C) | PACKAGE                                    | PKG.<br>DWG.# |

| ICL7660SCBA               | 0 to 70             | 8 Ld SOIC (N)                              | M8.15         |

| ICL7660SCPA               | 0 to 70             | 8 Ld PDIP                                  | E8.3          |

| ICL7660SIBA               | -40 to 85           | 8 Ld SOIC (N)                              | M8.15         |

| ICL7660SIBAZ<br>(Note 1)  | -40 to 85           | 8 Ld SOIC (N)<br>(lead-free)               | M8.15         |

| ICL7660SIBAZT<br>(Note 1) | -40 to 85           | 8 Ld SOIC (N)<br>(lead-free) Tape and Reel | M8.15         |

| ICL7660SIPA               | -40 to 85           | 8 Ld PDIP                                  | E8.3          |

| ICL7660SMTV<br>(Note 2)   | -55 to 125          | 8 Pin Metal Can                            | T8.C          |

### NOTES:

- Intersil Lead Free products employ special lead free material sets; molding compounds / die attach materials and 100% matte tin plate termination finish, which is compatible with both SnPb and lead free soldering operations. Intersil Lead Free products are MSL classified at lead free peak reflow temperatures that meet or exceed the lead free requirements of IPC/JEDEC J Std-020B.

- 2. Add /883B to part number if 883B processing is required.

### **Absolute Maximum Ratings**

| Supply Voltage                         | / |

|----------------------------------------|---|

| LV and OSC Input Voltage (Note 3)      |   |

| V+ < 5.5V0.3V to V+ + 0.3\             | / |

| V+ > 5.5V                              | / |

| Current into LV (Note 3)               |   |

| V+ > 3.5V                              | ١ |

| Output Short Duration                  |   |

| V <sub>SUPPLY</sub> ≤ 5.5VContinuous   | s |

| Storage Temperature Range65°C to 150°C | ) |

### **Thermal Information**

| Thermal Resistance (Typical, Note 4)  | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|---------------------------------------|------------------------|------------------------|

| PDIP                                  | 110                    | N/A                    |

| Plastic SOIC                          | 160                    | N/A                    |

| Metal Can                             | 160                    | 70                     |

| Maximum Lead Temperature (Soldering 1 | 0s)                    | 300°C                  |

| (SOIC - Lead Tips Only)               |                        |                        |

### **Operating Conditions**

| Temperature Range |                                         |

|-------------------|-----------------------------------------|

| ICL7660SM         | 55 <sup>0</sup> C to 125 <sup>0</sup> C |

| ICL7660SI         | 40 <sup>o</sup> C to 85 <sup>o</sup> C  |

| ICL7660SC         | 0 <sup>o</sup> C to 70 <sup>o</sup> C   |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

### NOTES:

- 3. Connecting any terminal to voltages greater than V+ or less than GND may cause destructive latchup. It is recommended that no inputs from sources operating from external supplies be applied prior to "power up" of ICL7660S.

- 4.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

## **Electrical Specifications** V+ = 5V, T<sub>A</sub> = 25°C, OSC = Free running, Test Circuit Figure 12, Unless Otherwise Specified

| PARAMETER                            | SYMBOL               | TEST CONDITIONS                                                                     | MIN | TYP  | MAX | UNITS |  |

|--------------------------------------|----------------------|-------------------------------------------------------------------------------------|-----|------|-----|-------|--|

| Supply Current (Note 7)              | l+                   | $R_L = \infty$ , $25^{\circ}C$                                                      | =   | 80   | 160 | μΑ    |  |

|                                      |                      | $0^{\circ}\text{C} < \text{T}_{\text{A}} < +70^{\circ}\text{C}$                     | =   | -    | 180 | μΑ    |  |

|                                      |                      | -40°C < T <sub>A</sub> < 85°C                                                       | -   | -    | 180 | μА    |  |

|                                      |                      | -55°C < T <sub>A</sub> < 125°C                                                      | -   | -    | 200 | μА    |  |

| Supply Voltage Range - High (Note 8) | V+ <sub>H</sub>      | R <sub>L</sub> = 10K, LV Open, T <sub>MIN</sub> < T <sub>A</sub> < T <sub>MAX</sub> | 3.0 | -    | 12  | V     |  |

| Supply Voltage Range - Low           | V+L                  | $R_L = 10K$ , LV to GND, $T_{MIN} < T_A < T_{MAX}$                                  | 1.5 | -    | 3.5 | V     |  |

| Output Source Resistance             | R <sub>OUT</sub>     | I <sub>OUT</sub> = 20mA                                                             | -   | 60   | 100 | Ω     |  |

|                                      |                      | $I_{OUT} = 20$ mA, $0$ <sup>o</sup> C < $T_A < 70$ <sup>o</sup> C                   | -   | -    | 120 | Ω     |  |

|                                      |                      | $I_{OUT} = 20$ mA, $-25$ <sup>o</sup> C $< T_A < 85$ <sup>o</sup> C                 | -   | -    | 120 | Ω     |  |

|                                      |                      | I <sub>OUT</sub> = 20mA, -55°C < T <sub>A</sub> < 125°C                             | -   | -    | 150 | Ω     |  |

|                                      |                      | I <sub>OUT</sub> = 3mA, V+ = 2V, LV = GND,<br>0°C < T <sub>A</sub> < 70°C           | -   | -    | 250 | Ω     |  |

|                                      |                      | $I_{OUT} = 3mA, V+ = 2V, LV = GND,$<br>-40°C < T <sub>A</sub> < 85°C                | -   | -    | 300 | Ω     |  |

|                                      |                      | I <sub>OUT</sub> = 3mA, V+ = 2V, LV = GND,<br>-55°C < T <sub>A</sub> < 125°C        | -   | -    | 400 | Ω     |  |

| Oscillator Frequency (Note 7)        | fosc                 | C <sub>OSC</sub> = 0, Pin 1 Open or GND                                             | 5   | 10   | -   | kHz   |  |

|                                      |                      | C <sub>OSC</sub> = 0, Pin 1 = V+                                                    | -   | 35   | -   | kHz   |  |

| Power Efficiency                     | P <sub>EFF</sub>     | $R_L = 5k\Omega$                                                                    | 96  | 98   | -   | %     |  |

|                                      |                      | $T_{MIN} < T_A < T_{MAX} R_L = 5k\Omega$                                            | 95  | 97   | -   | -     |  |

| Voltage Conversion Efficiency        | V <sub>OUT</sub> EFF | $R_L = \infty$                                                                      | 99  | 99.9 | -   | %     |  |

Electrical Specifications V+ = 5V, T<sub>A</sub> = 25°C, OSC = Free running, Test Circuit Figure 12, Unless Otherwise Specified (Continued)

| PARAMETER            | SYMBOL | TEST CONDITIONS | MIN | TYP | MAX | UNITS |

|----------------------|--------|-----------------|-----|-----|-----|-------|

| Oscillator Impedance | Zosc   | V+ = 2V         | -   | 1   | -   | МΩ    |

|                      |        | V+ = 5V         | -   | 100 | -   | kΩ    |

### NOTES:

- 5. Derate linearly above 50°C by 5.5mW/°C

- 6. In the test circuit, there is no external capacitor applied to pin 7. However, when the device is plugged into a test socket, there is usually a very small but finite stray capacitance present, of the order of 5pF.

- 7. The Intersil ICL7660S can operate without an external diode over the full temperature and voltage range. This device will function in existing designs which incorporate an external diode with no degradation in overall circuit performance.

- 8. All significant improvements over the industry standard ICL7660 are highlighted.

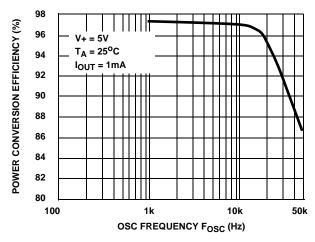

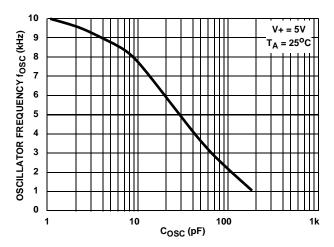

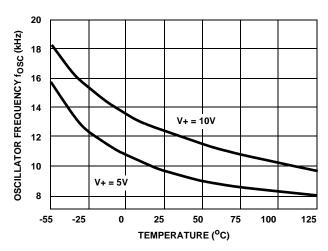

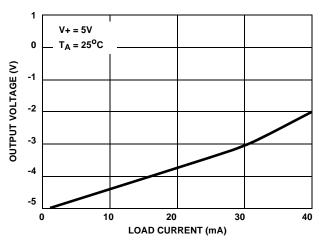

## Typical Performance Curves (Test Circuit Figure 12)

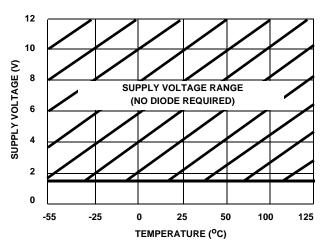

FIGURE 1. OPERATING VOLTAGE AS A FUNCTION OF TEMPERATURE

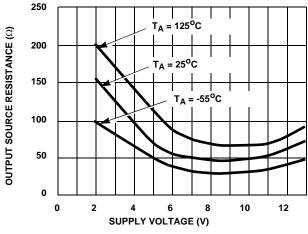

FIGURE 2. OUTPUT SOURCE RESISTANCE AS A FUNCTION OF SUPPLY VOLTAGE

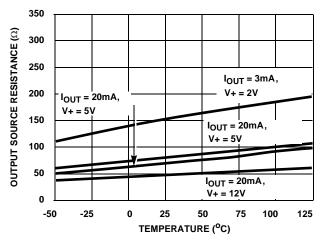

FIGURE 3. OUTPUT SOURCE RESISTANCE AS A FUNCTION OF TEMPERATURE

FIGURE 4. POWER CONVERSION EFFICIENCY AS A FUNCTION OF OSCILLATOR FREQUENCY

## Typical Performance Curves (Test Circuit Figure 12) (Continued)

FIGURE 5. FREQUENCY OF OSCILLATION AS A FUNCTION OF EXTERNAL OSCILLATOR CAPACITANCE

FIGURE 6. UNLOADED OSCILLATOR FREQUENCY AS A FUNCTION OF TEMPERATURE

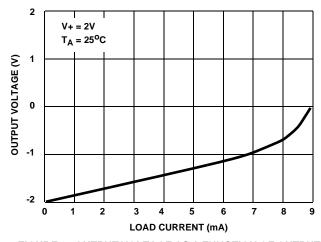

FIGURE 7. OUTPUT VOLTAGE AS A FUNCTION OF OUTPUT CURRENT

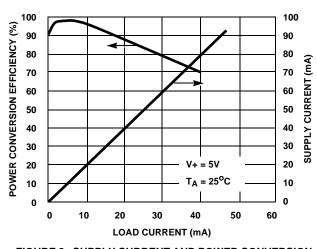

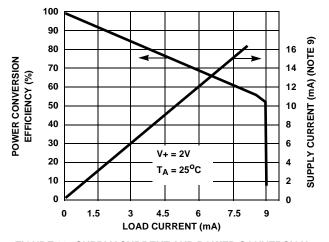

FIGURE 8. SUPPLY CURRENT AND POWER CONVERSION EFFICIENCY AS A FUNCTION OF LOAD CURRENT

FIGURE 9. OUTPUT VOLTAGE AS A FUNCTION OF OUTPUT CURRENT

FIGURE 10. SUPPLY CURRENT AND POWER CONVERSION EFFICIENCY AS A FUNCTION OF LOAD CURRENT

### Typical Performance Curves (Test Circuit Figure 12) (Continued)

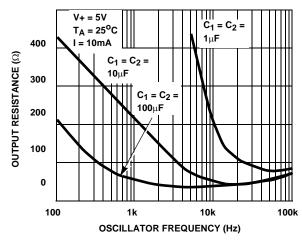

FIGURE 11. OUTPUT SOURCE RESISTANCE AS A FUNCTION OF OSCILLATOR FREQUENCY

NOTE:

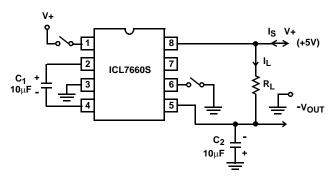

9. These curves include in the supply current that current fed directly into the load R<sub>L</sub> from the V+ (See Figure 12). Thus, approximately half the supply current goes directly to the positive side of the load, and the other half, through the ICL7660S, to the negative side of the load. Ideally, V<sub>OUT</sub> ~ 2V<sub>IN</sub>, I<sub>S</sub> ~ 2I<sub>L</sub>, so V<sub>IN</sub> x I<sub>S</sub> ~ V<sub>OUT</sub> x I<sub>L</sub>.

## **Detailed Description**

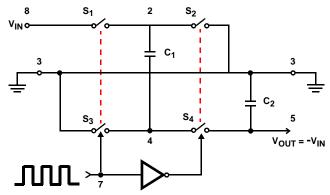

The ICL7660S contains all the necessary circuitry to complete a negative voltage converter, with the exception of 2 external capacitors which may be inexpensive  $10\mu F$  polarized electrolytic types. The mode of operation of the device may be best understood by considering Figure 13, which shows an idealized negative voltage converter. Capacitor  $C_1$  is charged to a voltage, V+, for the half cycle when switches  $S_1$  and  $S_3$  are closed. (Note: Switches  $S_2$  and  $S_4$  are open during this half cycle.) During the second half cycle of operation, switches  $S_2$  and  $S_4$  are closed, with  $S_1$  and  $S_3$  open, thereby shifting capacitor  $C_1$  to  $C_2$  such that the voltage on  $C_2$  is exactly V+, assuming ideal switches and no load on  $C_2$ . The ICL7660S approaches this ideal situation more closely than existing non-mechanical circuits.

NOTE: For large values of  $C_{OSC}$  (>1000pF) the values of  $C_1$  and  $C_2$  should be increased to 100µF.

### FIGURE 12. ICL7660S TEST CIRCUIT

In the ICL7660S, the 4 switches of Figure 13 are MOS power switches; S<sub>1</sub> is a P-Channel devices and S<sub>2</sub>, S<sub>3</sub> and

$S_4$  are N-Channel devices. The main difficulty with this approach is that in integrating the switches, the substrates of  $S_3$  and  $S_4$  must always remain reverse biased with respect to their sources, but not so much as to degrade their "ON" resistances. In addition, at circuit start up, and under output short circuit conditions ( $V_{OUT} = V_+$ ), the output voltage must be sensed and the substrate bias adjusted accordingly. Failure to accomplish this would result in high power losses and probable device latchup.

This problem is eliminated in the ICL7660S by a logic network which senses the output voltage ( $V_{OUT}$ ) together with the level translators, and switches the substrates of  $S_3$  and  $S_4$  to the correct level to maintain necessary reverse bias.

The voltage regulator portion of the ICL7660S is an integral part of the anti-latchup circuitry, however its inherent voltage drop can degrade operation at low voltages. Therefore, to improve low voltage operation "LV" pin should be connected to GND, disabling the regulator. For supply voltages greater than 3.5V the LV terminal must be left open to insure latchup proof operation, and prevent device damage.

## Theoretical Power Efficiency Considerations

In theory a voltage converter can approach 100% efficiency if certain conditions are met:

- 1. The drive circuitry consumes minimal power.

- The output switches have extremely low ON resistance and virtually no offset.

- 3. The impedance of the pump and reservoir capacitors are negligible at the pump frequency.

The ICL7660S approaches these conditions for negative voltage conversion if large values of  $C_1$  and  $C_2$  are used. **ENERGY IS LOST ONLY IN THE TRANSFER OF CHARGE BETWEEN CAPACITORS IF A CHANGE IN VOLTAGE OCCURS.** The energy lost is defined by:

$$E = \frac{1}{2}C_1 (V_1^2 - V_2^2)$$

where  $V_1$  and  $V_2$  are the voltages on  $C_1$  during the pump and transfer cycles. If the impedances of  $C_1$  and  $C_2$  are relatively high at the pump frequency (refer to Figure 13) compared to the value of  $R_L$ , there will be substantial difference in the voltages  $V_1$  and  $V_2$ . Therefore it is not only desirable to make  $C_2$  as large as possible to eliminate output voltage ripple, but also to employ a correspondingly large value for  $C_1$  in order to achieve maximum efficiency of operation.

FIGURE 13. IDEALIZED NEGATIVE VOLTAGE CONVERTER

### Do's and Don'ts

- 1. Do not exceed maximum supply voltages.

- 2. Do not connect LV terminal to GND for supply voltage greater than 3.5V.

- 3. Do not short circuit the output to V<sup>+</sup> supply for supply voltages above 5.5V for extended periods, however, transient conditions including start-up are okay.

- When using polarized capacitors, the + terminal of C<sub>1</sub> must be connected to pin 2 of the ICL7660S and the + terminal of C<sub>2</sub> must be connected to GND.

- 5. If the voltage supply driving the ICL7660S has a large source impedance ( $25\Omega$   $30\Omega$ ), then a 2.2 $\mu$ F capacitor from pin 8 to ground may be required to limit rate of rise of input voltage to less than  $2V/\mu$ s.

- User should insure that the output (pin 5) does not go more positive than GND (pin 3). Device latch up will occur under these conditions.

A 1N914 or similar diode placed in parallel with  $C_2$  will prevent the device from latching up under these conditions. (Anode pin 5, Cathode pin 3).

## Typical Applications

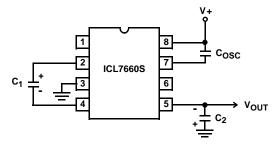

### Simple Negative Voltage Converter

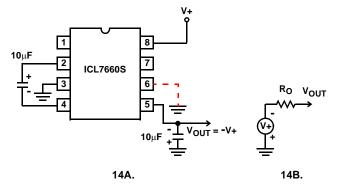

The majority of applications will undoubtedly utilize the ICL7660S for generation of negative supply voltages. Figure 14 shows typical connections to provide a negative supply where a positive supply of +1.5V to +12V is available. Keep in mind that pin 6 (LV) is tied to the supply negative (GND) for supply voltage below 3.5V.

FIGURE 14. SIMPLE NEGATIVE CONVERTER AND ITS OUTPUT EQUIVALENT

The output characteristics of the circuit in Figure 14 can be approximated by an ideal voltage source in series with a resistance as shown in Figure 14B. The voltage source has a value of -(V+). The output impedance (R<sub>O</sub>) is a function of the ON resistance of the internal MOS switches (shown in Figure 13), the switching frequency, the value of C<sub>1</sub> and C<sub>2</sub>, and the ESR (equivalent series resistance) of C<sub>1</sub> and C<sub>2</sub>. A good first order approximation for R<sub>O</sub> is:

$$\begin{array}{l} R_O \cong 2(R_{SW1} + R_{SW3} + ESR_{C1}) + 2(R_{SW2} + R_{SW4} + ESR_{C1}) \\ + \\ \hline 1 \\ \hline f_{PUMP} \times \\ C_1 \end{array}$$

$$(f_{PUMP} = \frac{f_{OSC}}{2}$$

,  $R_{SWX} = MOSFET$  switch resistance)

Combining the four  $R_{\mbox{\scriptsize SWX}}$  terms as  $R_{\mbox{\scriptsize SW}},$  we see that:

$$R_0 \cong 2 \times R_{SW} + \frac{1}{f_{PUMP} \times G_1} + 4 \times ESR_{C1} + ESR_{C2}\Omega$$

$R_{SW}$ , the total switch resistance, is a function of supply voltage and temperature (See the Output Source Resistance graphs), typically  $23\Omega$  at  $25^{o}C$  and 5V. Careful selection of  $C_{1}$  and  $C_{2}$  will reduce the remaining terms, minimizing the output impedance. High value capacitors will reduce the  $1/(f_{PUMP}\ x\ C_{1})$  component, and low ESR capacitors will lower the ESR term. Increasing the oscillator frequency will reduce the  $1/(f_{PUMP}\ x\ C_{1})$  term, but may have the side effect of a net

increase in output impedance when  $C_1 > 10\mu F$  and is not long enough to fully charge the capacitors every cycle. In a typical application where  $f_{OSC} = 10kHz$  and  $C = C_1 = C_2 = 10\mu F$ :

$$R_{O} \cong 2 \times 23 + \frac{1}{(5 \times 10^{3} \times 10 \times 10^{-6})} + 4 \times ESR_{C1} + ESR_{C2}$$

$R_{O} \cong 46 + 20 + 5 \times ESR_{C}\Omega$

Since the ESRs of the capacitors are reflected in the output impedance multiplied by a factor of 5, a high value could potentially swamp out a low  $1/f_{PUMP} \times C_1$ ) term, rendering an increase in switching frequency or filter capacitance ineffective. Typical electrolytic capacitors may have ESRs as high as  $10\Omega$ .

### **Output Ripple**

ESR also affects the ripple voltage seen at the output. The total ripple is determined by 2 voltages, A and B, as shown in Figure 15. Segment A is the voltage drop across the ESR of  $C_2$  at the instant it goes from being charged by  $C_1$  (current flowing into  $C_2$ ) to being discharged through the load (current flowing out of  $C_2$ ). The magnitude of this current change is 2 x  $I_{OUT}$ , hence the total drop is 2 x  $I_{OUT}$  x  $ESR_{C2}V$ . Segment B is the voltage change across  $C_2$  during time  $t_2$ , the half of the cycle when  $C_2$  supplies current the load. The drop at B is  $I_{OUT}$  x  $t_2/C_2V$ . The peak-to-peak ripple voltage is the sum of these voltage drops:

$$V \\ RIPPLE \cong \left(\frac{1}{2 \times f_{PUMP \times C_2}} + 2 ESRC_2 \times I_{OUT}\right)$$

Again, a low ESR capacitor will result in a higher performance output.

### Paralleling Devices

Any number of ICL7660S voltage converters may be paralleled to reduce output resistance. The reservoir capacitor,  $C_2$ , serves all devices while each device requires its own pump capacitor,  $C_1$ . The resultant output resistance would be approximately:

$$R_{OUT} = \frac{R_{OUT} \text{ (of ICL7660S)}}{\text{n (number of devices)}}$$

### **Cascading Devices**

The ICL7660S may be cascaded as shown to produce larger negative multiplication of the initial supply voltage. However, due to the finite efficiency of each device, the practical limit is 10 devices for light loads. The output voltage is defined by:

$$V_{OUT} = -n(V_{IN}),$$

where n is an integer representing the number of devices cascaded. The resulting output resistance would be approximately the weighted sum of the individual ICL7660S  $R_{OUT}$  values.

### Changing the ICL7660S Oscillator Frequency

It may be desirable in some applications, due to noise or other considerations, to alter the oscillator frequency. This can be achieved simply by one of several methods described below.

By connecting the Boost Pin (Pin 1) to V+, the oscillator charge and discharge current is increased and, hence, the oscillator frequency is increased by approximately  $3^1/_2$  times. The result is a decrease in the output impedance and ripple. This is of major importance for surface mount applications where capacitor size and cost are critical. Smaller capacitors, e.g.  $0.1\mu F$ , can be used in conjunction with the Boost Pin in order to achieve similar output currents compared to the device free running with  $C_1 = C_2 = 10\mu F$  or  $100\mu F$ . (Refer to graph of Output Source Resistance as a Function of Oscillator Frequency).

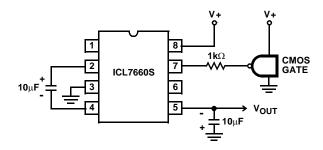

Increasing the oscillator frequency can also be achieved by overdriving the oscillator from an external clock, as shown in Figure 18. In order to prevent device latchup, a  $1 \mathrm{k}\Omega$  resistor must be used in series with the clock output. In a situation where the designer has generated the external clock frequency using TTL logic, the addition of a  $10\mathrm{k}\Omega$  pullup resistor to V+ supply is required. Note that the pump frequency with external clocking, as with internal clocking, will be  $^1/_2$  of the clock frequency. Output transitions occur on the positive going edge of the clock.

FIGURE 15. EXTERNAL CLOCKING

It is also possible to increase the conversion efficiency of the ICL7660S at low load levels by lowering the oscillator frequency. This reduces the switching losses, and is shown in Figure 19. However, lowering the oscillator frequency will cause an undesirable increase in the impedance of the pump (C<sub>1</sub>) and reservoir (C<sub>2</sub>) capacitors; this is overcome by increasing the values of C<sub>1</sub> and C<sub>2</sub> by the same factor that the frequency has been reduced. For example, the addition of a 100pF capacitor between pin 7 (OSC and V+ will lower the oscillator frequency to 1kHz from its nominal frequency of 10kHz (a multiple of 10), and thereby necessitate corresponding increase in the value of C<sub>1</sub> and C<sub>2</sub> (from  $10\mu F$  to  $100\mu F$ ).

FIGURE 16. LOWERING OSCILLATOR FREQUENCY

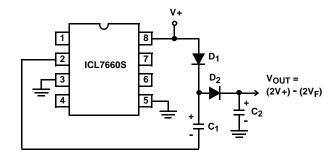

### Positive Voltage Doubling

The ICL7660S may be employed to achieve positive voltage doubling using the circuit shown in Figure 20. In this application, the pump inverter switches of the ICL7660S are used to charge  $C_1$  to a voltage level of V+ -V<sub>F</sub> (where V+ is the supply voltage and V<sub>F</sub> is the forward voltage on  $C_1$  plus the supply voltage (V+) is applied through diode  $D_2$  to capacitor  $C_2$ . The voltage thus created on  $C_2$  becomes (2V+) -  $(2V_F)$  or twice the supply voltage minus the combined forward voltage drops of diodes  $D_1$  and  $D_2$ .

The source impedance of the output ( $V_{OUT}$ ) will depend on the output current, but for V+ = 5V and an output current of 10mA it will be approximately  $60\Omega$ .

NOTE: D<sub>1</sub> and D<sub>2</sub> can be any suitable diode.

FIGURE 17. POSITIVE VOLTAGE DOUBLER

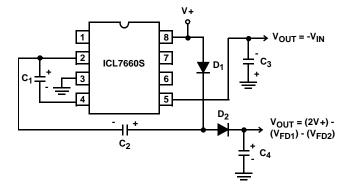

## Combined Negative Voltage Conversion and Positive Supply Doubling

Figure 21 combines the functions shown in Figure 14 and Figure 20 to provide negative voltage conversion and positive voltage doubling simultaneously. This approach would be, for example, suitable for generating +9V and -5V from an existing +5V supply. In this instance capacitors  $C_1$  and  $C_3$  perform the pump and reservoir functions respectively for the generation of the negative voltage, while capacitors  $C_2$  and  $C_4$  are pump and reservoir respectively for the doubled positive voltage. There is a penalty in this configuration which combines both functions, however, in that the source impedances of the generated supplies will be somewhat higher due to the finite impedance of the common charge pump driver at pin 2 of the device.

FIGURE 18. COMBINED NEGATIVE VOLTAGE CONVERTER

AND POSITIVE DOUBLER

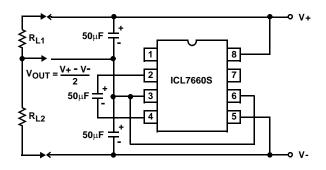

## **Voltage Splitting**

The bidirectional characteristics can also be used to split a high supply in half, as shown in Figure 22. The combined load will be evenly shared between the two sides, and a high value resistor to the LV pin ensures start-up. Because the switches share the load in parallel, the output impedance is much lower than in the standard circuits, and higher currents can be drawn from the device. By using this circuit, and then the circuit of Figure 17, +15V can be converted (via +7.5, and -7.5 to a nominal -15V, although with rather high series output resistance (~250 $\Omega$ ).

FIGURE 19. SPLITTING A SUPPLY IN HALF

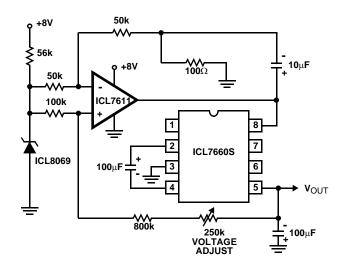

### Regulated Negative Voltage Supply

In Some cases, the output impedance of the ICL7660S can be a problem, particularly if the load current varies substantially. The circuit of Figure 23 can be used to overcome this by controlling the input voltage, via an ICL7611 low-power CMOS op amp, in such a way as to maintain a nearly constant output voltage. Direct feedback is inadvisable, since the ICL7660S's output does not respond instantaneously to change in input, but only after the switching delay. The circuit shown supplies enough delay to accommodate the ICL7660S, while maintaining adequate feedback. An increase in pump and storage capacitors is desirable, and the values shown provides an output impedance of less than  $5\Omega$  to a load of 10mA.

FIGURE 20. REGULATING THE OUTPUT VOLTAGE

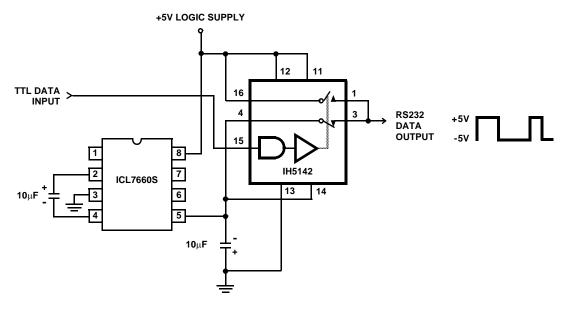

FIGURE 21. RS232 LEVELS FROM A SINGLE 5V SUPPLY

## Other Applications

Further information on the operation and use of the ICL7660S may be found in AN051 "Principles and Applications of the ICL7660 CMOS Voltage Converter".

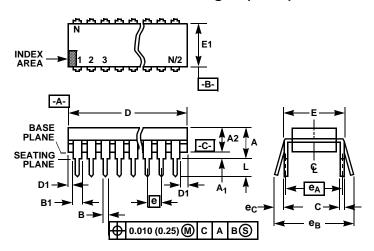

## Dual-In-Line Plastic Packages (PDIP)

### NOTES:

- Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- E and eA are measured with the leads constrained to be perpendicular to datum -C-.

- 7.  $e_B$  and  $e_C$  are measured at the lead tips with the leads unconstrained.  $e_C$  must be zero or greater.

- B1 maximum dimensions do not include dambar protrusions.

Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

E8.3 (JEDEC MS-001-BA ISSUE D) 8 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INC   | INCHES MILLIMETERS |          |         |       |

|----------------|-------|--------------------|----------|---------|-------|

| SYMBOL         | MIN   | MAX                | MIN      | MIN MAX |       |

| Α              | -     | 0.210              | -        | 5.33    | 4     |

| A1             | 0.015 | -                  | 0.39     | -       | 4     |

| A2             | 0.115 | 0.195              | 2.93     | 4.95    | -     |

| В              | 0.014 | 0.022              | 0.356    | 0.558   | -     |

| B1             | 0.045 | 0.070              | 1.15     | 1.77    | 8, 10 |

| С              | 0.008 | 0.014              | 0.204    | 0.355   | -     |

| D              | 0.355 | 0.400              | 9.01     | 10.16   | 5     |

| D1             | 0.005 | -                  | 0.13     | -       | 5     |

| Е              | 0.300 | 0.325              | 7.62     | 8.25    | 6     |

| E1             | 0.240 | 0.280              | 6.10     | 7.11    | 5     |

| е              | 0.100 | BSC                | 2.54 BSC |         | -     |

| e <sub>A</sub> | 0.300 | BSC                | 7.62 BSC |         | 6     |

| e <sub>B</sub> | -     | 0.430              | -        | 10.92   | 7     |

| L              | 0.115 | 0.150              | 2.93     | 3.81    | 4     |

| N              | 8     | 3                  | 8        |         | 9     |

Rev. 0 12/93

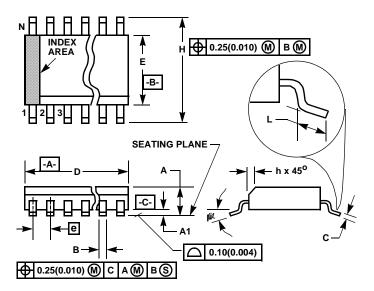

## Small Outline Plastic Packages (SOIC)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M8.15 (JEDEC MS-012-AA ISSUE C) 8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INC    | INCHES         |          | MILLIMETERS |   |

|--------|--------|----------------|----------|-------------|---|

| SYMBOL | MIN    | MAX            | MIN      | MIN MAX     |   |

| Α      | 0.0532 | 0.0688         | 1.35     | 1.75        | - |

| A1     | 0.0040 | 0.0098         | 0.10     | 0.25        | - |

| В      | 0.013  | 0.020          | 0.33     | 0.51        | 9 |

| С      | 0.0075 | 0.0098         | 0.19     | 0.25        | - |

| D      | 0.1890 | 0.1968         | 4.80     | 5.00        | 3 |

| Е      | 0.1497 | 0.1574         | 3.80     | 4.00        | 4 |

| е      | 0.050  | BSC            | 1.27 BSC |             | - |

| Н      | 0.2284 | 0.2440         | 5.80     | 6.20        | - |

| h      | 0.0099 | 0.0196         | 0.25     | 0.50        | 5 |

| L      | 0.016  | 0.050          | 0.40     | 1.27        | 6 |

| N      | 8      | 3              | 8        |             | 7 |

| α      | 0°     | 8 <sup>0</sup> | 0°       | 8°          | - |

Rev. 0 12/93

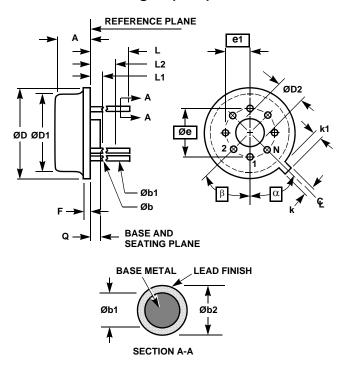

## Metal Can Packages (Can)

#### NOTES:

- (All leads) Øb applies between L1 and L2. Øb1 applies between L2 and 0.500 from the reference plane. Diameter is uncontrolled in L1 and beyond 0.500 from the reference plane.

- 2. Measured from maximum diameter of the product.

- 3.  $\alpha$  is the basic spacing from the centerline of the tab to terminal 1 and  $\beta$  is the basic spacing of each lead or lead position (N -1 places) from  $\alpha$ , looking at the bottom of the package.

- 4. N is the maximum number of terminal positions.

- 5. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 6. Controlling dimension: INCH.

**T8.C** MIL-STD-1835 MACY1-X8 (A1) 8 LEAD METAL CAN PACKAGE

|        | INC             | INCHES    |                 | MILLIMETERS |       |

|--------|-----------------|-----------|-----------------|-------------|-------|

| SYMBOL | MIN             | MAX       | MIN             | MAX         | NOTES |

| Α      | 0.165           | 0.185     | 4.19            | 4.70        | -     |

| Øb     | 0.016           | 0.019     | 0.41            | 0.48        | 1     |

| Øb1    | 0.016           | 0.021     | 0.41            | 0.53        | 1     |

| Øb2    | 0.016           | 0.024     | 0.41            | 0.61        | -     |

| ØD     | 0.335           | 0.375     | 8.51            | 9.40        | -     |

| ØD1    | 0.305           | 0.335     | 7.75            | 8.51        | -     |

| ØD2    | 0.110           | 0.160     | 2.79            | 4.06        | -     |

| е      | 0.200           | 0.200 BSC |                 | BSC         | -     |

| e1     | 0.100           | 0.100 BSC |                 | BSC         | -     |

| F      | -               | 0.040     | -               | 1.02        | -     |

| k      | 0.027           | 0.034     | 0.69            | 0.86        | -     |

| k1     | 0.027           | 0.045     | 0.69            | 1.14        | 2     |

| L      | 0.500           | 0.750     | 12.70           | 19.05       | 1     |

| L1     | -               | 0.050     | -               | 1.27        | 1     |

| L2     | 0.250           | -         | 6.35            | -           | 1     |

| Q      | 0.010           | 0.045     | 0.25            | 1.14        | -     |

| α      | 45° BSC         |           | 45 <sup>0</sup> | BSC         | 3     |

| β      | 45 <sup>0</sup> | BSC       | 45 <sup>0</sup> | BSC         | 3     |

| N      | 8               |           | 8               |             | 4     |

Rev. 0 5/18/94

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com