# HI-516

# 16-Channel/Differential 8-Channel, CMOS High Speed Analog Multiplexer

The HI-516 is a monolithic, dielectrically isolated, high-speed, high-performance CMOS analog multiplexer. It offers unique built-in channel selection decoding plus an inhibit for disabling all channels. The dual function of address input  $A_3$  enables the HI-516 to be user programmed either as a single ended 16-Channel multiplexer by connecting 'out A' to 'out B' and using  $A_3$  as a digital address input, or as an 8-Channel differential multiplexer by connecting A3 to the V- supply. The substrate leakages and parasitic capacitances are reduced substantially by using the Harris Dielectric Isolation process to achieve optimum performance in both high and low level signal applications. The low output leakage current ( $I_{D(OFF)}$  < 100pA at 25C) and fast settling ( $I_{SETTLE}$  = 800ns to 0.01%) characteristics of the device make it an ideal choice for high speed data acquisition systems, precision instrumentation, and industrial process control.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

Data Sheet June 1999 File Number 3146.2

# 16-Channel/Differential 8-Channel, CMOS High Speed Analog Multiplexer

The HI-516 is a monolithic, dielectrically isolated, highspeed, high-performance CMOS analog multiplexer. It offers unique built-in channel selection decoding plus an inhibit input for disabling all channels. The dual function of address input A<sub>3</sub> enables the HI-516 to be user programmed either as a single ended 16-Channel multiplexer by connecting 'out A' to 'out B' and using A3 as a digital address input, or as an 8-Channel differential multiplexer by connecting A<sub>3</sub> to the V- supply. The substrate leakages and parasitic capacitances are reduced substantially by using the Harris Dielectric Isolation process to achieve optimum performance in both high and low level signal applications. The low output leakage current (I<sub>D(OFF)</sub> < 100pA at 25°C) and fast settling (t<sub>SETTLE</sub> = 800ns to 0.01%) characteristics of the device make it an ideal choice for high speed data acquisition systems, precision instrumentation, and industrial process

For MIL-STD-883 compliant parts, request the HI-516/883 data sheet.

# Ordering Information

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE      | PKG.<br>NO. |

|-------------|---------------------|--------------|-------------|

| HI3-0516-5  | 0 to 75             | 28 Ld PDIP   | E28.6       |

| HI1-0516-2  | -55 to 125          | 28 Ld CERDIP | F28.6       |

#### Features

| Access Time (Typical)                          |

|------------------------------------------------|

| • Settling Time                                |

| • Low Leakage (Typical)  - I <sub>S(OFF)</sub> |

| • Low Capacitance (Max)  - C <sub>S(OFF)</sub> |

| Off Isolation at 500kHz                        |

| Low Charge Injection Error                     |

| Single Ended to Differential Selectable (SDS)  |

| Logic Level Selectable (LLS)                   |

# **Applications**

- · Data Acquisition Systems

- · Precision Instrumentation

- · Industrial Control

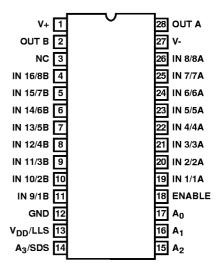

#### **Pinout**

# HI-516 (CERDIP, PDIP) TOP VIEW

# Truth Tables

## HI-516 USED AS A 16-CHANNEL MULTIPLEXER OR **DUAL 8-CHANNEL MULTIPLEXER (NOTE 1)**

| USE A <sub>3</sub> AS | ON CHAN        | NEL TO        |   |       |       |      |

|-----------------------|----------------|---------------|---|-------|-------|------|

| ENABLE                | A <sub>3</sub> | $A_2 A_1 A_0$ |   | OUT A | OUT B |      |

| L                     | Х              | Х             | х | х     | None  | None |

| Н                     | L              | L             | L | L     | 1A    | None |

| Н                     | L              | L             | L | Н     | 2A    | None |

| Н                     | L              | L             | Н | L     | зА    | None |

| Н                     | L              | L             | Н | Н     | 4A    | None |

| Н                     | L              | Н             | L | L     | 5A    | None |

| Н                     | L              | Н             | L | Н     | 6A    | None |

| Н                     | L              | Н             | Н | L     | 7A    | None |

| Н                     | L              | Н             | Н | Н     | 8A    | None |

| Н                     | Н              | L             | L | L     | None  | 1B   |

| Н                     | Н              | L             | L | Н     | None  | 2B   |

| Н                     | Н              | L             | Н | L     | None  | 3B   |

| Н                     | Н              | L             | Н | Н     | None  | 4B   |

| Н                     | Н              | Н             | L | L     | None  | 5B   |

| Н                     | Н              | Н             | L | Н     | None  | 6B   |

| Н                     | Н              | Н             | Н | L     | None  | 7B   |

| Н                     | Н              | Н             | Н | Н     | None  | 8B   |

#### NOTE:

#### HI-516 USED AS A DIFFERENTIAL 8-CHANNEL MULTIPLEXER

| A <sub>3</sub> CONNE | CTED T         | ON CHA         | NNEL TO        |       |       |

|----------------------|----------------|----------------|----------------|-------|-------|

| ENABLE               | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | OUT A | OUT B |

| L                    | Х              | Х              | Х              | None  | None  |

| Н                    | L              | L              | L              | 1A    | 1B    |

| Н                    | L              | L              | Н              | 2A    | 2B    |

| Н                    | L              | Н              | L              | ЗА    | 3B    |

| Н                    | L              | Н              | Н              | 4A    | 4B    |

| Н                    | Н              | L              | L              | 5A    | 5B    |

| Н                    | Н              | L              | Н              | 6A    | 6B    |

| Н                    | Н              | Н              | L              | 7A    | 7B    |

| Н                    | Н              | Н              | Н              | 8A    | 8B    |

<sup>1.</sup> For 16-channel single-ended function, tie 'out A' to 'out B'; for dual 8-channel function use the  $A_3$  address pin to select between MUX A and MUX B, where MUX A is selected with A<sub>3</sub> low.

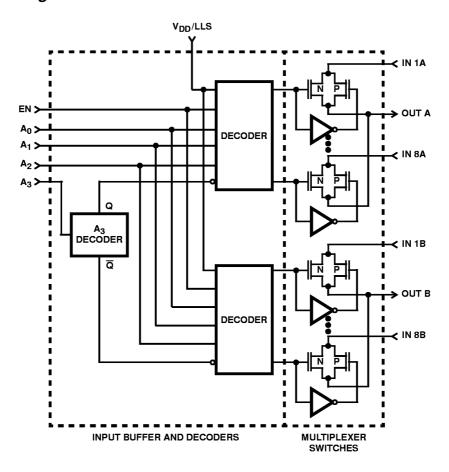

# Functional Block Diagram

| A <sub>3</sub> DECODE |   |   |  |  |  |  |  |

|-----------------------|---|---|--|--|--|--|--|

| A <sub>3</sub>        | Q | Ø |  |  |  |  |  |

| Н                     | Н |   |  |  |  |  |  |

| L                     | L | н |  |  |  |  |  |

| V-                    | L | L |  |  |  |  |  |

# **Absolute Maximum Ratings**

| V+ to V-       33V         Analog Signal       (V <sub>IN</sub> , V <sub>OUT</sub> ) |

|--------------------------------------------------------------------------------------|

| (V-) -2V to (V+) +2V                                                                 |

| Digital Input Voltage:                                                               |

| TTL Levels Selected (V <sub>DD</sub> /LLS Pin = GND or Open)                         |

| V <sub>A0-2</sub> 6V to +6V                                                          |

| V <sub>A3/SDS</sub> (V-) -2V to (V+) +2V                                             |

| CMOS Levels Selected (VDD/LLS Pin = VDD)                                             |

| V <sub>A0-3</sub> 2V to (V+) +2V                                                     |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 2)  | θ <sub>JA</sub> ( <sup>o</sup> C/W) | θ <sub>JC</sub> (°C/W)               |

|---------------------------------------|-------------------------------------|--------------------------------------|

| PDIP Package                          | 60                                  | N/A                                  |

| CERDIP Package                        |                                     | 18                                   |

| Maximum Junction Temperature          |                                     |                                      |

| Ceramic Package                       |                                     | 175 <sup>0</sup> C                   |

| Plastic Package                       |                                     | 150 <sup>0</sup> C                   |

| Maximum Storage Temperature Range     | 65                                  | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 1 | 0s)                                 | 300°C                                |

## **Operating Conditions**

| remperature Hanges |                |

|--------------------|----------------|

| HI-516-2           | -55°C to 125°C |

| HI-516-5           | 0°C to 75°C    |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

2.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

Supplies = +15V, -15V;  $V_{AH}$  (Logic Level High) = 2.4V,  $V_{AL}$  (Logic Level Low) = 0.8V;  $V_{DD}/LLS$  = GND. (Note 3) Unless Otherwise Specified **Electrical Specifications**

|                                                   | TEST                          | TEMP |                    | -2   |                    |                    | -5   |                    |       |

|---------------------------------------------------|-------------------------------|------|--------------------|------|--------------------|--------------------|------|--------------------|-------|

| PARAMETER                                         | CONDITIONS                    | (°C) | MIN                | TYP  | МАХ                | MIN                | TYP  | MAX                | UNITS |

| DYNAMIC CHARACTERISTICS                           |                               |      |                    |      |                    |                    |      |                    |       |

| Access Time, t <sub>A</sub>                       |                               | 25   | -                  | 130  | 175                | -                  | 130  | 175                | ns    |

|                                                   |                               | Full | -                  | -    | 225                | -                  | -    | 225                | ns    |

| Break-Before-Make Delay, t <sub>OPEN</sub>        |                               | 25   | 10                 | 20   | -                  | 10                 | 20   | -                  | ns    |

| Enable Delay (ON), t <sub>ON(EN)</sub>            |                               | 25   | -                  | 120  | 175                | -                  | 120  | 175                | ns    |

| Enable Delay (OFF), t <sub>OFF(EN)</sub>          |                               | 25   | -                  | 140  | 175                | -                  | 140  | 175                | ns    |

| Settling Time                                     | To 0.1%                       | 25   | -                  | 250  | -                  | -                  | 250  | -                  | ns    |

|                                                   | To 0.01%                      | 25   | -                  | 800  | -                  | -                  | 800  | -                  | ns    |

| Charge Injection Error                            | Note 6                        | 25   | -                  | -    | 20                 | -                  | -    | 20                 | mV    |

| Off Isolation                                     | Note 7                        | 25   | 55                 | -    | -                  | 55                 | -    | -                  | dB    |

| Channel Input Capacitance,<br>C <sub>S(OFF)</sub> |                               | 25   | -                  | -    | 10                 | -                  | -    | 10                 | pF    |

| Channel Output Capacitance, CD(OFF)               |                               | 25   | -                  | -    | 25                 | -                  | -    | 25                 | pF    |

| Digital Input Capacitance, CA                     |                               | 25   | -                  | -    | 10                 | -                  | -    | 10                 | pF    |

| Input to Output Capacitance,<br>CDS(OFF)          |                               | 25   | -                  | 0.02 | -                  | -                  | 0.02 | -                  | pF    |

| DIGITAL INPUT CHARACTERISTIC                      | DIGITAL INPUT CHARACTERISTICS |      |                    |      |                    |                    |      |                    |       |

| Input Low Threshold, V <sub>AL</sub> (TTL)        | Note 3                        | Full | -                  | -    | 0.8                | -                  | -    | 0.8                | ٧     |

| Input High Threshold, V <sub>AH</sub> (TTL)       | Note 3                        | Full | 2.4                | -    | -                  | 2.4                | -    | -                  | ٧     |

| Input Low Threshold, V <sub>AL</sub> (CMOS)       | Note 3                        | Full |                    | -    | 0.3V <sub>DD</sub> | -                  | -    | 0.3V <sub>DD</sub> | ٧     |

| Input High Threshold, V <sub>AH</sub> (CMOS)      | Note 3                        | Full | 0.7V <sub>DD</sub> | -    | -                  | 0.7V <sub>DD</sub> | -    | -                  | ٧     |

## **Electrical Specifications**

$Supplies = +15 V, -15 V; V_{AH} \ (Logic \ Level \ High) = 2.4 V, V_{AL} \ (Logic \ Level \ Low) = 0.8 V; \\ V_{DD}/LLS = GND. \ (Note 3) \ Unless \ Otherwise \ Specified \ \ \textbf{(Continued)}$

|                                              | TEST 1                       | TEMP | -2  |      |       | -5  |      |       |       |

|----------------------------------------------|------------------------------|------|-----|------|-------|-----|------|-------|-------|

| PARAMETER                                    | CONDITIONS                   | (°C) | MIN | TYP  | MAX   | MIN | TYP  | MAX   | UNITS |

| Input Leakage Current, IAH (High)            |                              | Full | -   | -    | 1     | -   | -    | 1     | μА    |

| Input Leakage Current, I <sub>AL</sub> (Low) |                              | Full | -   | -    | 25    | -   | -    | 25    | μА    |

| ANALOG CHANNEL CHARACTER                     | RISTICS                      |      |     |      |       |     |      |       |       |

| Analog Signal Range, V <sub>IN</sub>         | Note 4                       | Full | -14 | -    | +14   | -15 | -    | +15   | ٧     |

| On Resistance, r <sub>ON</sub>               | Note 5                       | 25   | -   | 620  | 750   | -   | 620  | 750   | Ω     |

|                                              |                              | Full | -   | -    | 1,000 | -   | -    | 1,000 | Ω     |

| Off Input Leakage Current, IS(OFF)           |                              | 25   | -   | 0.01 | -     | -   | 0.01 | -     | nA    |

|                                              |                              | Full | -   | -    | 50    | -   | -    | 50    | nA    |

| Off Output Leakage Current,                  |                              | 25   | -   | 0.03 | -     | -   | 0.03 | -     | nA    |

| ID(OFF)                                      |                              | Full | -   | -    | 100   | -   | -    | 100   | nA    |

| On Channel Leakage Current, ID(ON)           |                              | 25   | -   | 0.04 | -     | -   | 0.04 | -     | nA    |

| POWER SUPPLY CHARACTERIST                    | POWER SUPPLY CHARACTERISTICS |      |     |      |       |     |      |       |       |

| Power Dissipation, P <sub>D</sub>            |                              | Full | -   | -    | 750   | -   | -    | 900   | mW    |

| I+, Current                                  | V <sub>EN</sub> = 2.4V       | Full | -   | -    | 25    | -   | -    | 30    | mA    |

| I-, Current                                  |                              | Full | -   | -    | 25    | -   | -    | 30    | mA    |

# NOTES:

- 3.  $V_{DD}/LLS$  pin = open or grounded for TTL compatibility.  $V_{DD}/LLS$  pin =  $V_{DD}$  for CMOS compatibility.

- 4. At temperatures above  $90^{\circ}$ C, care must be taken to assure  $V_{IN}$  remains at least 1V below the  $V_{SUPPLY}$  for proper operation.

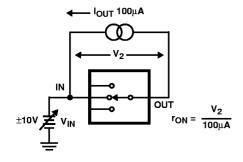

- 5.  $V_{IN} = \pm 10V$ ,  $I_{OUT} = -100\mu A$ .

- 6.  $V_{IN} = 0V$ ,  $C_L = 100pF$ , enable input pulse = 3V, f = 500kHz.

- 7.  $V_{EN}$  = 0.8V,  $V_{IN}$  = 3 $V_{RMS}$ , f = 500kHz,  $C_L$  = 40pF,  $R_L$  = 1K, Pin 3 grounded.

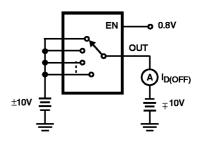

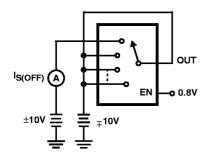

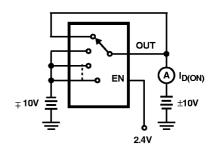

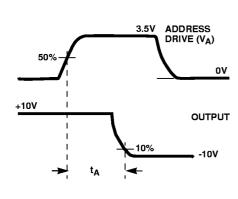

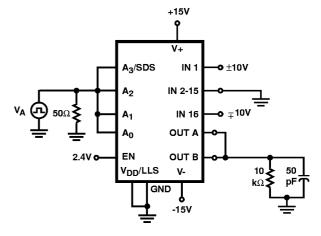

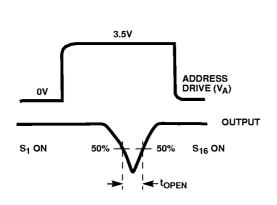

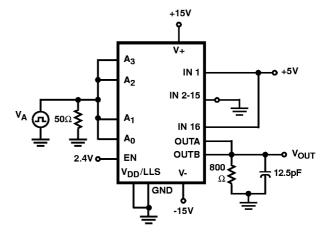

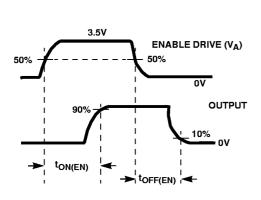

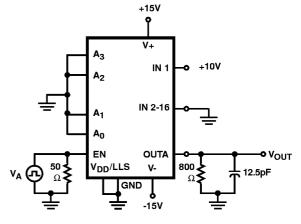

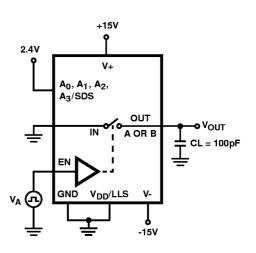

# **Test Circuits and Waveforms** V<sub>DD</sub>/LLS = GND, Unless Otherwise Specified.

FIGURE 1. ON RESISTANCE TEST CIRCUIT

FIGURE 2. ID(OFF) TEST CIRCUIT (NOTE 8)

FIGURE 3. I<sub>S(OFF)</sub> TEST CIRCUIT (NOTE 8)

FIGURE 4. ID(ON) TEST CIRCUIT (NOTE 8)

FIGURE 5A. MEASUREMENT POINTS

FIGURE 5B. TEST CIRCUIT

FIGURE 5. ACCESS TIME

#### NOTE:

8. Two measurements per channel:  $\pm 10V$  and  $\mp 10V$ . (Two measurements per device for  $I_{D(OFF)} \pm 10V$  and  $\mp 10V$ ).

# $\textit{Test Circuits and Waveforms} \ \, \text{$V_{DD}/\text{LLS} = GND$, Unless Otherwise Specified.} \ \, \textit{$(\textbf{Continued})$}$

FIGURE 6A. MEASUREMENT POINTS

FIGURE 6B. TEST CIRCUIT

FIGURE 6. BREAK-BEFORE-MAKE DELAY

FIGURE 7A. MEASUREMENT POINTS

FIGURE 7B. TEST CIRCUIT

FIGURE 7. ENABLE DELAYS

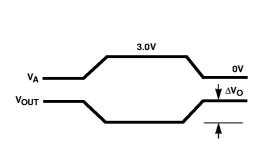

#### FIGURE 8A. MEASUREMENT POINTS

FIGURE 8B. TEST CIRCUIT

$\Delta V_O$  is the measured voltage error due to charge injection. The error in coulombs is Q =  $C_L \times \Delta V_O$ .

#### FIGURE 8. CHARGE INJECTION

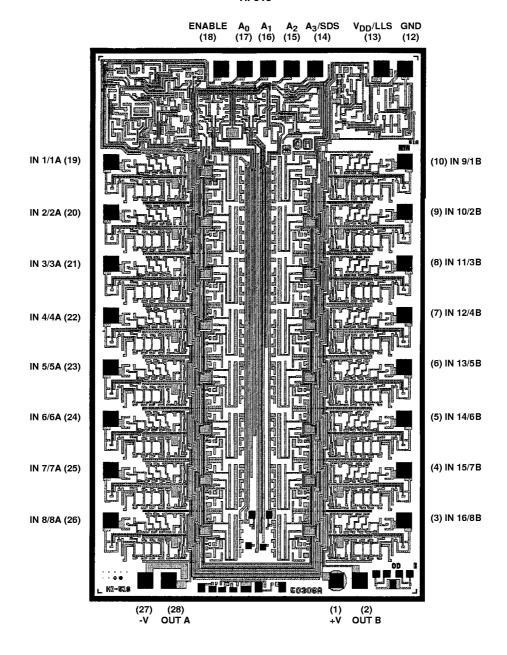

# Die Characteristics

#### **DIE DIMENSIONS:**

2250µm x 3720µm x 485µm

#### **METALLIZATION:**

Type: CuAl

Thickness: 16kÅ ±2kÅ

#### **PASSIVATION:**

Type: Nitride Over Silox Nitride Thickness: 3.5kÅ ±1kÅ Silox Thickness: 12kÅ ±2kÅ

## **WORST CASE CURRENT DENSITY:**

1.64 x 10<sup>5</sup> A/cm<sup>2</sup>

# Metallization Mask Layout

#### HI-516