# F81485

## **5V Low Power RS-485 Interface Transceiver**

Release Date: March, 2013

Version: V0.14P

### F81485 Datasheet Revision History

| Version | Date    | Page | Revision History                                                |

|---------|---------|------|-----------------------------------------------------------------|

| V0.10P  | 2011/12 | -    | Preliminary                                                     |

|         |         |      | Made Clarification and Correction                               |

| V0.11P  | 2012/01 | -    | Update Top Marking Specification                                |

|         |         |      | Update Differential Input Threshold Spec.                       |

| V0.12P  | 2012/02 |      | Made Clarification and Correction.                              |

| VU.12P  | 2012/02 | _    | Update Operating Temperature                                    |

|         |         |      | Made Clarification and Correction.                              |

| V0.13P  | 2012/03 | -    | Update Electrical Characteristics (Add Symbol, Testing Figures, |

|         |         |      | spec)                                                           |

| \/O.44D | 2042/02 |      | Made Clarification and Correction.                              |

| V0.14P  | 2013/03 | _    | Update ESD spec. to ±15KV Contact                               |

Please note that all data and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this data sheet belong to their respective owners.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Fintek for any damages resulting from such improper use or sales.

## **Table of Content**

| 1 | General Description        | 4 |

|---|----------------------------|---|

|   | Feature List               |   |

| 3 | Pin Configuration          | 5 |

|   | Pin Description            |   |

|   | Electrical Characteristics |   |

|   | Ordering Information       |   |

|   | Top Marking Specification  |   |

| 8 | Package Spec.              |   |

| 9 | Application Circuit        |   |

### 1 General Description

The F81485 is a CMOS design, features with single 5 V power supply, and low power differential bus/line transceiver suitable for the multipoint data transmission EIA standard RS485 and RS422 applications. The extended common-mode range is –7 V to +12 V. Both the driver and the receiver can be enabled independently. The driver and receiver feature three-state outputs, with the driver outputs maintaining high impedance over the entire common-mode range. Excessive power dissipation caused by the bus contention or faults is prevented by a thermal shutdown circuit which forces the driver outputs into a high impedance state. The receiver contains a fail-safe feature that results in a logic high output state if the inputs are unconnected (floating). Up to 32 transceivers can be connected simultaneously on a bus, but only one driver should be enabled at any time. The F81485 features extremely fast switching speeds. Minimal driver propagation delays permit transmission at data rates up to 10 Mbps while low skew minimizes EMI interference. All inputs and outputs contain protection against ESD; all driver outputs feature high source and sink current capability. An epitaxial layer is used to guard against latch-up.

### 2 Feature List

- Single 5V Supply

- Meets EIA RS-485 Standard

- High Speed, Low Power CMOS

- -7V to 12V Bus Common-Mode Range Permits

- ±7V Ground Difference Between Devices on the Bus

- ESD IEC 61000-4-2 ±15KV Contact Discharge Testing

- 70mV Typical Input Hysteresis

- Driver propagation delay: 40 ns typical

- Receiver propagation delay: 70 ns typical

- High-Z outputs with power off

- 8 Pin SOP Packaging

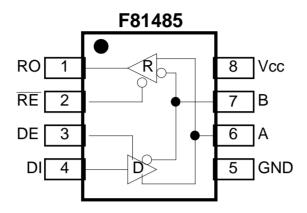

# 3 Pin Configuration

## 4 Pin Description

| IN <sub>t</sub> | - TTL level input pin.        |

|-----------------|-------------------------------|

| $O_4$           | - Output pin with 4mA driver. |

| Р               | - Power.                      |

#### 4.1. Power Pin

| Pin | Pin Name | Туре | Description                                    |

|-----|----------|------|------------------------------------------------|

| 5   | GND      | Р    | GND.                                           |

| 8   | VCC      | Р    | 4.75V< VCC < 5.25V power supply voltage input. |

#### 4.2. Transceiver

| Pin | Pin Name | Type            | Description                                                                                                                                                                                |

|-----|----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RO       | O <sub>4</sub>  | Receiver Output. When enabled (RE# is low), then if A > B by 200 mV, RO is high. A < B by 200 mV, RO is low.                                                                               |

| 2   | RE#      | IN <sub>t</sub> | Active Low Receiver Output Enable pin. A low level enables the receiver output, RO. A high level places it in a high impedance state.                                                      |

| 3   | DE       | IN <sub>t</sub> | Active High Driver Output Enable. A high level enables the driver differential outputs, A and B. The chip will function as a line driver. A low level places it in a high impedance state. |

| 4   | DI       | IN <sub>t</sub> | Driver Input. When the driver is enabled (DE is high), a logic low on DI forces A low and B high, while a logic high on DI forces A high and B low.                                        |

| 6   | А        | I/O             | Non-inverting Receiver Input A/Driver Output A.                                                                                                                                            |

| 7   | В        | I/O             | Inverting Receiver Input B/Driver Output B.                                                                                                                                                |

### 5 Electrical Characteristics

5.1 Absolute Maximum Ratings

| PAR                               | RAMETER      | RATING           | UNIT |

|-----------------------------------|--------------|------------------|------|

|                                   | Vcc          | 6                | V    |

|                                   | Logic        | -0.3 to Vcc +0.5 | V    |

| Input Voltage                     | Drivers      | -0.3 to Vcc +0.5 | V    |

|                                   | Receivers    | ±15              |      |

|                                   | Logic        | -0.3 to Vcc +0.5 | V    |

| Output Voltage                    | Drivers      | ±15              | V    |

|                                   | Receivers    |                  |      |

| Storage Tempreature               |              | -65 to +150      | °C   |

| Lead Temperature (soldering, 10s) |              | +300             | °C   |

| Powe                              | r Disspation | 500              | mW   |

Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the device

Test condition: VCC = 5V

| PARAMETER                 | SYMBOL | MIN. | TYP. | MAX  | UNIT    | CONDITIONS |

|---------------------------|--------|------|------|------|---------|------------|

| Supply Voltage            | Vcc    | 4.75 |      | 5.25 | V       |            |

| Supply Current            | Icc    |      | 900  |      | $\mu$ A | No Load    |

| Operating Temperature (1) | Т      | -40  |      | 85   | · C     |            |

Note (1): Design Guarantee -40 °C ≤ T ≤ 85 °C

#### 5.2 Driver Section

Test condition: VCC = 5V

| PARAMETER                                                                 | SYMBOL                | MIN. | TYP. | MAX | UNIT    | CONDITIONS                        |  |  |

|---------------------------------------------------------------------------|-----------------------|------|------|-----|---------|-----------------------------------|--|--|

|                                                                           | DC Characteristics    |      |      |     |         |                                   |  |  |

|                                                                           |                       | GND  |      | Vcc | V       | Unloaded, R= ∞                    |  |  |

| Differential Output Voltage                                               | $V_{OD}$              | 2    |      | Vcc | V       | With load, $R = 50\Omega$ (RS422) |  |  |

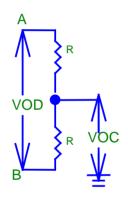

| (See Figure 1)                                                            |                       | 1.5  |      | Vcc | V       | With load, $R = 27\Omega$ (RS485) |  |  |

| Differential Output Voltage<br>for Complimentary States<br>(See Figure 1) | $\DeltaV_{\text{OD}}$ |      |      | 0.2 | V       | $R = 27\Omega$ or $R = 50\Omega$  |  |  |

| Driver Common-Mode<br>Output Voltage<br>(See Figure 1)                    | V <sub>oc</sub>       |      |      | 3   | V       | $R = 27\Omega$ or $R = 50\Omega$  |  |  |

| Input High Voltage                                                        | $V_{INH}$             | 2.0  |      |     | V       | Applies to DE, DI, RE#            |  |  |

| Input Low Voltage                                                         | $V_{INL}$             |      |      | 0.8 | V       | Applies to DE, DI, RE#            |  |  |

| Input Current                                                             | I <sub>IN</sub>       |      |      | ±10 | $\mu$ A | Applies to DE, DI, RE#            |  |  |

| Driver Chart Current                                                      |                       | 35   |      | 250 | mA      | VOUT = High, -7V ≤ Vo<br>≤ +12V   |  |  |

| Driver Short Current                                                      | I <sub>DSC</sub>      | 35   |      | 250 | mA      | VOUT = Low, -7V ≤ Vo ≤<br>+12V    |  |  |

| PARAMETER                                       | SYMBOL                                | MIN. | TYP. | MAX | UNIT | CONDITIONS                                                    |  |  |

|-------------------------------------------------|---------------------------------------|------|------|-----|------|---------------------------------------------------------------|--|--|

| AC Characteristics                              |                                       |      |      |     |      |                                                               |  |  |

| Maximum Data Rate                               | -                                     | 10   |      |     | Mbps | RE# = 5V, DE = 5V                                             |  |  |

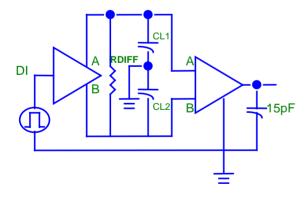

| Driver Input to Output                          | t <sub>DPLH</sub> , t <sub>DPHL</sub> | 20   | 40   | 60  | ns   | $t_{PLH}$ ; $R_{DIFF} = 54\Omega$ , $C_{L1} = C_{L2} = 100pF$ |  |  |

| (See Figure 3)                                  | t <sub>DPLH</sub> , t <sub>DPHL</sub> | 20   | 40   | 60  | ns   | $t_{PHL}; R_{DIFF} = 54\Omega, C_{L1} = C_{L2} = 100pF$       |  |  |

| Driver Skew                                     | t <sub>DPLH</sub> — t <sub>DPHL</sub> |      | 5    | 10  | ns   | $t_{SKEW} =  t_{DPLH} - t_{DPHL} $                            |  |  |

| Driver Rise or Fall Time                        | $t_R$ , $t_F$                         | 3    | 15   | 40  | ns   | 10% to 90%, $R_{DIFF} = 54\Omega$ , $C_{L1} = C_{L2} = 100pF$ |  |  |

| Driver Enable to Output<br>High (See Figure 4)  | t <sub>DZH</sub>                      |      | 40   | 70  | ns   | C <sub>L1</sub> = 100pF                                       |  |  |

| Driver Enable to Output Low (See Figure 4)      | t <sub>DZL</sub>                      |      | 40   | 70  | ns   | C <sub>L1</sub> = 100pF                                       |  |  |

| Driver Disable Time from<br>Low (See Figure 4)  | t <sub>DLZ</sub>                      |      | 40   | 70  | ns   | C <sub>L1</sub> = 100pF                                       |  |  |

| Driver Disable Time from<br>High (See Figure 4) | t <sub>DHZ</sub>                      |      | 40   | 70  | ns   | C <sub>L1</sub> = 100pF                                       |  |  |

#### 5.3 Receiver Section

Test condition: VCC = 5V

| PARAMETER                                      | SYMBOL                   | MIN. | TYP. | MAX  | UNIT    | CONDITIONS                                      |  |  |

|------------------------------------------------|--------------------------|------|------|------|---------|-------------------------------------------------|--|--|

|                                                | DC Characteristics       |      |      |      |         |                                                 |  |  |

| Differential Input Threshold                   | $V_{TH}$                 | -300 |      | +0   | mV      | $-7V \le V_{CM} \le +12V$                       |  |  |

| Input Hysteresis                               | $\Delta$ V <sub>TH</sub> |      | 70   |      | mV      | V <sub>CM</sub> = 0V                            |  |  |

| Output Voltage High                            | $V_{OH}$                 | 3.5  |      |      | V       | $I_0 = -4mA, V_{ID} = +200mV$                   |  |  |

| Output Voltage Low                             | $V_{OL}$                 |      |      | 0.4  | V       | $I_0 = +4mA, V_{ID} = -200mV$                   |  |  |

| Output Current                                 | Icc                      |      |      | ±1   | $\mu$ A | 0.4V ≤ Vo ≤ 2.4V, RE# =<br>-5V                  |  |  |

| Input Resistance                               | R <sub>IN</sub>          | 12   | 15   |      | ΚΩ      | $-7V \le V_{CM} \le +12V$                       |  |  |

| Input Current (A,B), V <sub>IN</sub> = 12V     | I <sub>IN</sub>          |      |      | +1.0 | mA      | DE = 0V, $V_{cc}$ = 0V or 5.25V, $V_{IN}$ = 12V |  |  |

| Input Current (A,B), V <sub>IN</sub> = -<br>7V | I <sub>IN</sub>          |      |      | -0.8 | mA      | DE = 0V, $V_{cc}$ = 0V or 5.25V, $V_{IN}$ = -7V |  |  |

| Short Circuit Current                          | I <sub>scc</sub>         | 7    |      | 95   | mA      | $0V \le V_{CM} \le V_{cc}$                      |  |  |

| PARAMETER                         | SYMBOL                              | MIN. | TYP. | MAX | UNIT | CONDITIONS                                                  |  |  |

|-----------------------------------|-------------------------------------|------|------|-----|------|-------------------------------------------------------------|--|--|

| AC Characteristics                |                                     |      |      |     |      |                                                             |  |  |

| Maximum Data Rate                 | -                                   | 10   |      |     | Mbps | RE# = 0V, DE = 0V                                           |  |  |

| Receiver Input to Output          | t <sub>PHL</sub> , t <sub>PLH</sub> | 60   | 70   | 200 | ns   | $t_{PLH}; R_{DIFF} = 54\Omega, C_{L1} = C_{L2} = 100pF$     |  |  |

| (See Figure 3)                    | t <sub>PHL</sub> , t <sub>PLH</sub> | 60   | 70   | 200 | ns   | $t_{PHL}; R_{DIFF} = 54\Omega, C_{L1} = C_{L2} = 100pF$     |  |  |

| Receiver Skew                     | t <sub>PHL -</sub> t <sub>PLH</sub> |      | 15   |     | ns   | t <sub>SKEW</sub> =   t <sub>DPLH</sub> - t <sub>DPHL</sub> |  |  |

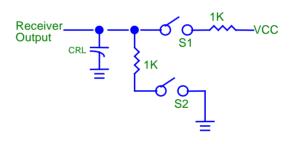

| Receiver Enable to Output<br>Low  | $t_{ZL}$                            |      | 20   | 50  | ns   | C <sub>RL</sub> = 15pF, See<br>Figure 2                     |  |  |

| Receiver Enable to Output<br>High | t <sub>zH</sub>                     |      | 20   | 50  | ns   | C <sub>RL</sub> = 15pF, See<br>Figure 2                     |  |  |

| Receiver Disable Time from Low    | t <sub>LZ</sub>                     |      | 20   | 50  | ns   | C <sub>RL</sub> = 15pF, See<br>Figure 2                     |  |  |

| Receiver Disable Time from High   | t <sub>HZ</sub>                     |      | 20   | 50  | ns   | C <sub>RL</sub> = 15pF, See<br>Figure 2                     |  |  |

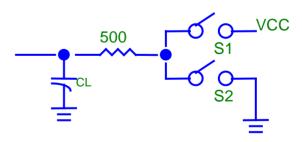

Figure 1: RS-485 Driver Test Load Circuit

Figure 2: Receiver Timing Test Load Circuit

Figure 3: RS-485 Driver/Receiver Timing Test Circuit

Figure 4: RS-485 Driver Timing Test Load Circuit

## 6 Ordering Information

| Part Number | Package Type        |

|-------------|---------------------|

| F81485S     | 8-SOP Green Package |

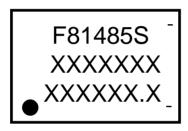

## 7 Top Marking Specification

The version identification is shown as the bold red characters. Please refer to below for detail:

1st Line: Fintek Logo

2<sup>nd</sup> Line: Device Name → **F81485S**, where S means 8-SOP package

2<sup>nd</sup> Line: Assembly Plant Code (X) + Assembled Year Code (X) + Week Code (XX) + Fintek Internal Code (XX) + IC Version (X) where A means version A, B means version B, ...

3<sup>rd</sup> Line: Wafer Fab Code (XXXX...XX)

: Pin 1 Identifier

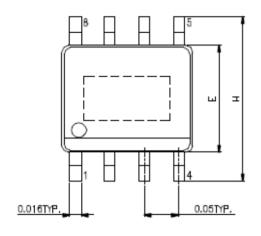

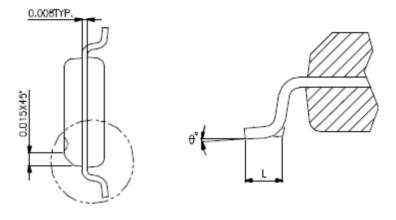

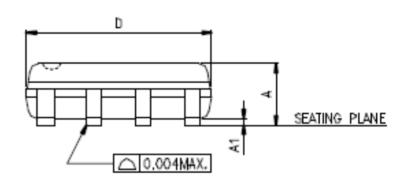

# 8 Package Spec.

#### 8-SOP Package

E.P. VERSION ONLY

| SYMBOLS | MIN.  | MAX.  |  |  |

|---------|-------|-------|--|--|

| Α       | 0.053 | 0.069 |  |  |

| A1      | 0.004 | 0.010 |  |  |

| D       | 0.189 | 0.196 |  |  |

| Е       | 0.150 | 0.157 |  |  |

| Н       | 0.228 | 0.244 |  |  |

| L       | 0.016 | 0.050 |  |  |

| а       | 0     | 8     |  |  |

UNIT: INCH

#### NOTES:

- 1.JEDEC OUTLINE : MS-012 AA / E.P. VERSION : N/A

- 2.DIMENSIONS "D" DOES NOT INCLUDE WOLD FLASH, PROTRUSIONS OR GATE BURRS, WOLD FLASH, PROTRUSIONS AND GATE BURRS SHALL NOT EXCEED .15mm (.006in) PER SIDE.

- 3.D MENSIONS "E" DOES NOT INCLUDE INTER-LEAD FLASH, OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED .25mm (.010in) PER SIDE.

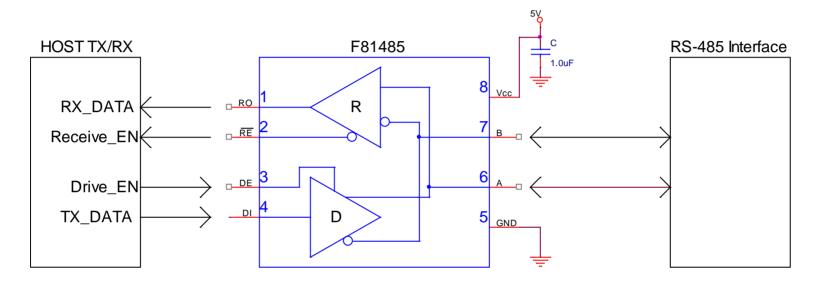

# 9 Application Circuit

#### MODE SELECTION

| /RE | DE | MODE           |  |

|-----|----|----------------|--|

| 0   | 0  | RS485 Recieve  |  |

| 1   | 1  | RS485 Drive    |  |

| 0   | 1  | RS485 LoopBack |  |

| 1   | 0  | Dis_RS485      |  |

| Title     |                           |       |   |    |   |          |

|-----------|---------------------------|-------|---|----|---|----------|

| Size<br>B | Document Number<br>F81485 |       |   |    |   | Rev<br>A |

| Date:     | Friday, November 18, 2011 | Sheet | 1 | of | 1 |          |