# swissbit\*

Product data sheet

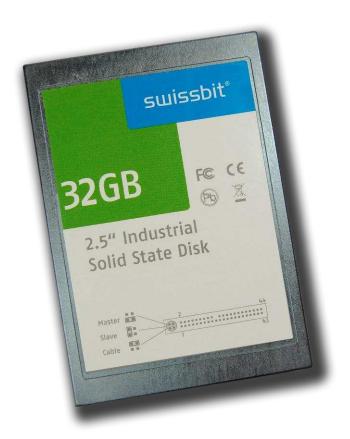

# Parallel ATA (PATA) 2.5"-Solid State Drive

# P-120 Series

up to UDMA4 / MDMA2 / PIO4

Standard and industrial temperature grade

BU: Swissbit Group

Date: 28 September 2010

Revision: 1.00

File:

P-120\_data\_sheet\_PA-QxB0\_Rev100.doc

# Parallel ATA (PATA) 2.5-inch Solid State Drive (SSD) 2 to 32GByte, 5V (or 3.3V) supply

# 1 Feature summary

- 2.5-inch ATA Solid State Drive (SSD)

- o 100.2mm x 70.0mm x 9.0mm

- Replacement of a standard IDE/ATA-compliant Hard Disk Drive (HDD)

- Highly-integrated memory controller

- True IDE mode compatible

- max. UDMA4 supported

- o max. PIO mode 4, MDMA2 supported

- Hardware RS-code ECC (4 Bytes/528 Bytes correction)

- fix drive configuration

- Low-power CMOS technology

- 3.3V / 5.oV power supply

- Power saving mode (with automatic wake-up)

- No mechanical noise

- Wear Leveling: equal wear leveling of static and dynamic data

The wear leveling assures that dynamic data as well as static data is balanced evenly across the memory. With that the maximum write endurance of the device is guaranteed.

- Data retention 10 years @ 25°C

- S.M.A.R.T. support

- Host Protected Area (HPA) support

- Security Feature set support

- Write endurance: Due to intelligent wear leveling an even use of the entire flash is guaranteed, regardless how much "static" (OS) data is stored.

Example: If the average file size is 10MByte and the total capacity is 8GByte, 80Mio write cycles can be performed.

- · patented power-off reliability

- No data loss of older sectors

- Max. 32 sectors data loss (old data kept) if power off before card is not ready after last write command.

- High reliability

- MTBF > 2.500.000 hours

- o Data reliability: < 1 non-recoverable error per 1014 bits read

- Number of connector insertions/removals: >1,000

- High performance

- Up to 66MB/s burst transfer rate in UDMA4

- Sustained Write performance: up to 35MB/s

- Sustained Read Performance: up to 4oMB/s

- Available densities

- o 2 to 32GBytes

- Controlled BOM

- RoHS compatible

# **2 Contents**

| 1 FEATURE SUMMARY                                                                            | 2              |

|----------------------------------------------------------------------------------------------|----------------|

| 2 CONTENTS                                                                                   | 3              |

| 3 ORDER INFORMATION                                                                          | 5              |

| 3.1 OFFERED OEM OPTIONS                                                                      | 5              |

| 4 PRODUCT SPECIFICATION                                                                      | 6              |

| 4.1 System Performance                                                                       | 6              |

| 4.1 STSTEM PERFORMANCE                                                                       |                |

| 4.3 PHYSICAL DIMENSIONS                                                                      |                |

| 4.4 RELIABILITY                                                                              |                |

| 4.5 Drive geometry / CHS parameter                                                           |                |

| 4.6 PHYSICAL DESCRIPTION                                                                     |                |

| 5 ELECTRICAL INTERFACE                                                                       | 9              |

| 5.1 ELECTRICAL DESCRIPTION                                                                   |                |

| 5.2 Master-Slave configuration                                                               | 10             |

| 5.3 ELECTRICAL SPECIFICATION                                                                 | 11             |

| 6 COMMAND INTERFACE                                                                          | 12             |

| 6.1 PIO Mode                                                                                 | 12             |

| 6.2 MDMA Mode                                                                                |                |

| 6.3 Ultra DMA Mode                                                                           | 14             |

| 7 SOFTWARE INTERFACE                                                                         | 32             |

| 7.1 ATA Drive Register Set Definition and Protocol                                           | 32             |

| 7.2 TRUE IDE MODE ADDRESSING                                                                 |                |

| 7.3 Data Register                                                                            | 32             |

| 7.4 Error Register                                                                           | 32             |

| 7.5 FEATURE REGISTER                                                                         |                |

| 7.6 Sector Count Register                                                                    |                |

| 7.7 SECTOR NUMBER (LBA 7-0) REGISTER                                                         |                |

| 7.8 CYLINDER LOW (LBA 15-8) REGISTER                                                         |                |

| 7.9 CYLINDER HIGH (LBA 23–16) REGISTER                                                       |                |

| 7.10 DRIVE/HEAD (LBA 27–24) REGISTER                                                         |                |

| 7.12 DEVICE CONTROL REGISTER                                                                 |                |

| 7.13 DRIVE (DRIVE) ADDRESS REGISTER                                                          |                |

| 8 ATA COMMAND DESCRIPTION                                                                    |                |

|                                                                                              |                |

| 8.1 CHECK POWER MODE (98H OR E5H)                                                            |                |

| 8.3 EXECUTE DRIVE DIAGNOSTIC (90H)                                                           |                |

| 8.4 Flush Cache (E7H)                                                                        |                |

| 8.5 FORMAT TRACK (50H)                                                                       |                |

| 8.6 Identify Device (ECH)                                                                    |                |

| 8.7 IDLE (97H OR E3H)                                                                        | 47             |

| 8.8 IDLE IMMEDIATE (95H OR E1H)                                                              | 47             |

| 8.9 Initialize Drive Parameters (91H)                                                        | 47             |

| 8.10 MEDIA LOCK/MEDIA UNLOCK (DEH/DFH)                                                       |                |

| 8.11 NOP (00H)                                                                               |                |

| 8.12 READ BUFFER (E4H)                                                                       |                |

| 8.13 READ DMA (C8H)                                                                          |                |

| 8.15 READ NATIVE MAX ADDRESS (F8H)                                                           | 49<br>49       |

| 8.16 READ SECTOR(S) (20H OR 21H)                                                             | 50             |

| 8.17 READ VERIFY SECTOR(S) (40H OR 41H)                                                      |                |

| Swissbit AG Swissbit reserves the right to change products or specifications without notice. | Revision: 1.00 |

| 8.18 Recalibrate (1XH)                             |    |

|----------------------------------------------------|----|

| 8.19 REQUEST SENSE (03H)                           |    |

| 8.20 Security Disable Password (F6H)               |    |

| 8.21 SECURITY ERASE PREPARE (F3H)                  |    |

| 8.22 SECURITY ERASE UNIT (F4H)                     |    |

| 8.23 SECURITY FREEZE LOCK (F5H)                    |    |

| 8.24 SECURITY SET PASSWORD (F1H)                   |    |

| 8.25 SECURITY UNLOCK (F2H)                         | 53 |

| 8.26 SEEK (7XH)                                    |    |

| 8.27 Set Features (EFH)                            | 54 |

| 8.28 SET MAX ADDRESS (F9H)                         | 56 |

| 8.29 SET MULTIPLE MODE (C6H)                       | 57 |

| 8.30 SET SLEEP MODE (99H OR E6H)                   | 57 |

| 8.31 S.M.A.R.T. (Вон)                              | 57 |

| 8.32 STANDBY (96H OR E2)                           |    |

| 8.33 STANDBY IMMEDIATE (94H OR EOH)                |    |

| 8.34 Translate Sector (87H)                        |    |

| 8.35 WEAR LEVEL (F5H)                              |    |

| 8.36 Write Buffer (E8H)                            |    |

| 8.37 Write DMA (CAH)                               |    |

| 8.38 Write Multiple Command (C5H)                  |    |

| 8.39 WRITE MULTIPLE WITHOUT ERASE (CDH)            |    |

| 8.40 Write Sector(s) (30H or 31H)                  |    |

| 8.41 Write Sector(s) without Erase (38h)           |    |

| 8.42 Write Verify (3CH)                            |    |

|                                                    |    |

| 9 S.M.A.R.T. FUNCTIONALITY                         | 62 |

| 9.1 S.M.A.R.T. Enable / Disable operations         | 62 |

| 9.2 S.M.A.R.T. ENABLE / DISABLE ATTRIBUTE AUTOSAVE |    |

| 9.3 S.M.A.R.T. READ DATA                           |    |

| 9.4 S.M.A.R.T. READ ATTRIBUTE THRESHOLDS           |    |

| 9.5 S.M.A.R.T. RETURN STATUS                       |    |

| 9.6 S.M.A.R.T. READ REMAP DATA                     |    |

| 9.7 S.M.A.R.T. READ WEAR LEVEL DATA                |    |

|                                                    |    |

| 10 PACKAGE MECHANICAL                              |    |

| 11 DECLARATION OF CONFORMITY                       | 70 |

| 12 ROHS AND WEEE UPDATE FROM SWISSBIT              | 71 |

|                                                    |    |

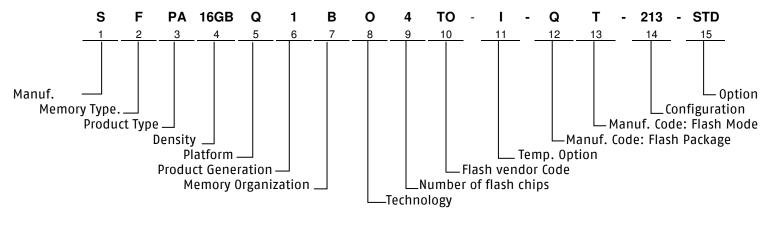

| 13 PART NUMBER DECODER                             |    |

| 13.1 MANUFACTURER                                  | 73 |

| 13.2 MEMORY TYPE                                   | 73 |

| 13.3 PRODUCT TYPE                                  | 73 |

| 13.4 DENSITY                                       | 73 |

| 13.5 PLATFORM                                      | 73 |

| 13.6 PRODUCT GENERATION                            |    |

| 13.7 MEMORY ORGANIZATION                           |    |

| 13.8 TECHNOLOGY                                    |    |

| 13.9 NUMBER OF FLASH CHIP                          |    |

| 13.10 FLASH CODE.                                  |    |

| 13.11 TEMP. OPTION                                 |    |

| 13.12 DIE CLASSIFICATION                           |    |

| 13.13 PIN Mode                                     |    |

| 13.14 DRIVE CONFIGURATION XYZ                      |    |

| 13.15 OPTION                                       |    |

|                                                    |    |

| 14 SWISSBIT SSD MARKING SPECIFICATION              | 75 |

| 14.1 TOP VIEW                                      | 75 |

| 15 REVISION HISTORY                                |    |

# **3 Order Information**

# **Available Standard part numbers**

FIX / PIO4, MDMA2, UDMA4 / o°C - 70°C

| Density | Part Number                  |

|---------|------------------------------|

| 2GB     | SFPA2048QxB02TO-C-MS-2y3-STD |

| 4GB     | SFPA4096QxBO2TO-C-DT-2y3-STD |

| 8GB     | SFPA8192QxBO2TO-C-QT-2y3-STD |

| 16GB    | SFPA16GBQxBO4TO-C-QT-2y3-STD |

| 32GB    | SFPA32GBQxB08T0-C-QT-2y3-STD |

Table 1: Standard temperature product list

x depends on product generation, y depends on the firmware generation

# FIX / PIO4, MDMA2, UDMA4 / -40°C - +85°C

| Density | Part Number                  |

|---------|------------------------------|

| 2GB     | SFPA2048QxB02T0-I-MS-2y3-STD |

| 4GB     | SFPA4096QxBO2TO-I-DT-2y3-STD |

| 8GB     | SFPA8192QxBO2TO-I-QT-2y3-STD |

| 16GB    | SFPA16GBQxB04T0-I-QT-2y3-STD |

| 32GB    | SFPA32GBQxB08T0-I-QT-2y3-STD |

Table 2: Industrial temperature product list

x depends on product generation, y depends on the firmware generation

# 3.1 Offered OEM options

- Disabling MDMA and/or UDMA modes

- Customer specified drive size and drive geometry (C/H/S cylinder/head/sector)

- Customer specified drive ID (Strings)

- Preload service (also images with any file system)

- Customized labels

- 2 Temperature ranges

- o Commercial Temperature range 0 ... +70°C o Industrial Temperature range −40 ... +85°C

- ROM mode (write protected with uploaded software)

- Special Firmware solutions for additional customer requirements

- ...

# **4 Product Specification**

The Solid State Drive (SSD) is a small form factor non-volatile memory drive which provides high capacity data storage.

The drive with the IDE interface (2.00mm pitch) operates in three transfer modes:

UDMA (Ultra Direct Memory Access) up to Mode 4 66MB/s burst

MDMA (Multi Word Direct Memory Access) up to Mode 2 16MB/s burst

PIO (Programmed Input / Output) up to Mode 4 16MB/s burst

The drive behaves as a standard ATA (IDE) disk drive. It can be set as master or slave by a jumper. The drive has an internal **intelligent controller** which manages interface protocols, data storage and retrieval as well as hardware RS-code **Error Correction Code (ECC)**, **defect handling**, **diagnostics and clock control**.

The **wear leveling** mechanism assures an equal usage of the Flash memory cells to extend the life time.

The hardware RS-code ECC allows to detect and correct 4 symbols per 528 Bytes.

The drive has a **voltage detector** and a powerful **power-loss management feature** to prevent data corruption after power-down.

The specification has been realized and approved by the ATA/ATAPI-7 specification.

The system highlights are shown in Table 3 ... Table 10.

#### **Related Documentation**

- Parallel Transport Protocols and Physical Interconnect (ATA/ATAPI-7)

- AT Attachment Interface Document, American National Standards Institute, X3.221-1994

# 4.1 System Performance

Table 3: System Performance

| System Performance                                              |       | Typ.                 | Max.              | Unit  |

|-----------------------------------------------------------------|-------|----------------------|-------------------|-------|

| Sleep to write                                                  |       |                      | 5                 |       |

| Sleep to read                                                   |       |                      | 5                 | me    |

| Power-on to Ready <sup>(3)</sup>                                |       | <500                 | 1000              | ms    |

| Reset to Ready (3)                                              |       |                      | 500               |       |

| Data transfer Rate (UDMA4 burst)                                |       |                      | 66 <sup>(1)</sup> |       |

| Sustained Sequential Read (measured) UDMA4<br>128kB Block size  | 232GB | 37 <sup>(1)(2)</sup> | 40 <sup>(1)</sup> | MB/s  |

| Sustained Sequential Write (measured) UDMA4<br>128kB Block size | 232GB | 32 <sup>(1)(2)</sup> | 35 <sup>(1)</sup> |       |

| Sustained Random Read (measured) UDMA4<br>4kB Block size        | 232GB | 11 <sup>(1)(2)</sup> | 15 <sup>(1)</sup> | MB/s  |

| Sustained Random Write (measured) UDMA4<br>4kB Block size       | 232GB | 0.12 (1)(2)          | 0.2 (1)           | IMB/S |

| Command to DRO                                                  | Read  | 100                  | 2000              | II.C  |

| בטווווומווע נט שאע                                              | Write | 30                   | 1000              | μs    |

<sup>1.</sup> All values refer to Toshiba flash chips in UDMA4 mode with Sequential write/read test (256 sectors multiple commands) or Random write/read test (8 sectors multiple commands) with Firmware 090617.

<sup>2.</sup> Sustained Speed depends on flash type and number, file size, and burst speed

<sup>3.</sup> In case of IDE-Master with no slave drive additional max. 500ms

In case of IDE-Master with additional slave drive depending on the slave handshaking (max. 31s)

# 4.2 Environmental Specifications

# 4.2.1 Recommended Operating Conditions

Table 4: Recommended Operating Conditions

| Parameter                        | Value                      |

|----------------------------------|----------------------------|

| Commercial Operating Temperature | o°C to 70°C                |

| Industrial Operating Temperature | -40°C to 85°C              |

| Power Supply VCC Voltage (5V)    | 4.5V to 5.5V - 5.0V ±10%   |

| Power Supply VCC Voltage (3.3V)  | 2.97V to 3.63V - 3.3V ±10% |

Table 5: Current consumption (1)

| Current Consumption (type)    | 5V      | Unit |

|-------------------------------|---------|------|

| Read (typ/max)                | 145/160 |      |

| Write (typ/max)               | 140/160 | mA   |

| Sleep/Idle Mode (typ/max) (2) | 7/10    |      |

- 1. All values are typical at 25° C and nominal supply voltage and refer to 8GByte SSD.

- 2. The card goes to Sleep/idle mode 20ms (default) after last host command.

# 4.2.2 Recommended Storage Conditions

**Table 6: Recommended Storage Conditions**

| Parameter                      | Value          |

|--------------------------------|----------------|

| Commercial Storage Temperature | -50°C to 100°C |

| Industrial Storage Temperature | -50°C to 100°C |

# 4.2.3 Shock, Vibration, and Humidity

Table 7: Shock, Vibration, and Humidity

| Parameter                 | Value                                               |  |  |

|---------------------------|-----------------------------------------------------|--|--|

| Humidity (non-condensing) | 85% RH 85°C, 1000 hrs (JEDEC JESD22, method A101-B) |  |  |

| Vibration                 | 20G Peak, 102000Hz                                  |  |  |

| Shock                     | 1500G, 0.5ms duration, half sine wave               |  |  |

# 4.3 Physical Dimensions

**Table 8: Physical Dimensions**

| Table 0.1 Hysical Difficultions |            |      |

|---------------------------------|------------|------|

| Physical Dimensions             |            | Unit |

| Length                          | 100.20±0.2 |      |

| Width                           | 69.85±0.2  | mm   |

| Thickness                       | 9.00±0.1   |      |

| Weight (typ.)                   | 85         | g    |

# 4.4 Reliability

Table 9: System Reliability and Maintenance (1)

| Table 3. System Renability and Maintenance (1) |                                                          |  |  |  |

|------------------------------------------------|----------------------------------------------------------|--|--|--|

| Parameter                                      | Value                                                    |  |  |  |

| MTBF (at 25°C)                                 | > 3,000,000 hours                                        |  |  |  |

| Insertions/Removals                            | > 10,000                                                 |  |  |  |

| Data Reliability                               | < 1 Non-Recoverable Error per 10 <sup>14</sup> bits Read |  |  |  |

| Data Retention                                 | 10 years                                                 |  |  |  |

1. Dependent on final system qualification data.

# 4.5 Drive geometry / CHS parameter

Table 10: SSD capacity specification

| Capacity | Default_cylinders | Default_heads | Default_sectors<br>_track | Sectors_drive | Total addressable capacity (Byte) |

|----------|-------------------|---------------|---------------------------|---------------|-----------------------------------|

| 4GB      | 7,732             | 16            | 63                        | 7,793,856     | 3,990,454,272                     |

| 8GB      | 15,880            | 16            | 63                        | 15,621,984    | 7,998,455,808                     |

| 16GB     | 16,383*)          | 16            | 63                        | 31,277,232    | 16,013,942,784                    |

| 32GB     | 16,383*)          | 16            | 63                        | 62,586,720    | 32,044,400,640                    |

<sup>\*)</sup> The CHS access is limited to about 8GB. Above 8GB the drive must be addressed in LBA mode.

# 4.6 Physical description

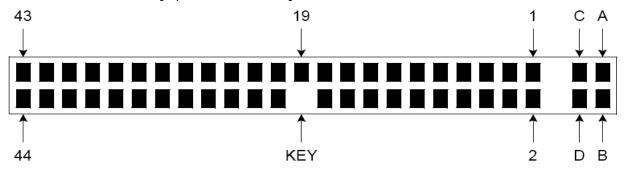

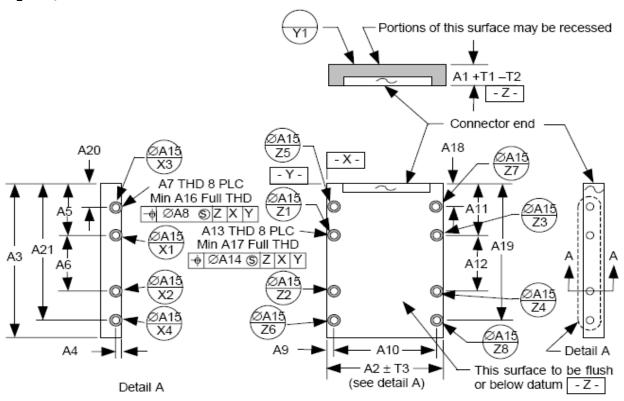

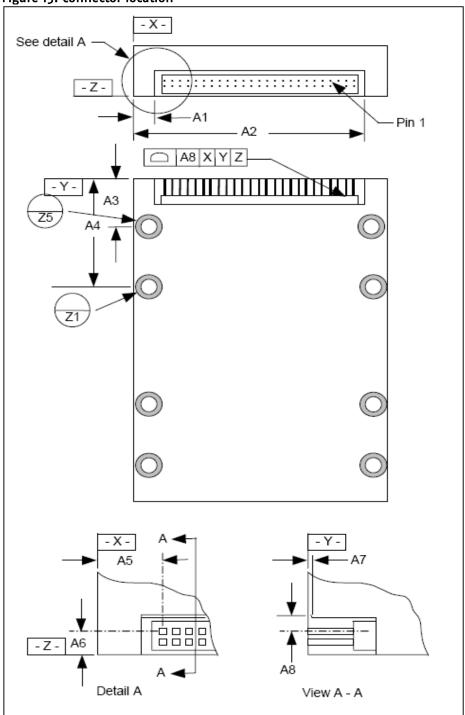

The Solid State Drive (SSD) contains a single chip controller and Flash memory modules. The controller interfaces with a host system allowing data to be written to and read from the Flash memory modules. The SSD is offered in a 2.5" package with a standard 2.0mm pitch 44-pin connector consisting of two rows of 22 male contacts with a key pin. Beside the connector the SSD can configured with a Jumper as Master/Slave/Cable Select. Figure 14 and Figure 15 show SSD dimensions and connector location.

# **5 Electrical interface**

# 5.1 Electrical description

The SSD is connected with a standard IDE 44 pin connector (pitch 2.00mm). The power is connected at pin 41-44. The Master card can be configured as Master or slave with a jumper at pins A – D.

The signal/pin assignments and descriptions are listed in Table 11 Low active signals have a '-' prefix. Pin types are Input, Output or Input/Output. Inputs are signals sourced from the host while Outputs are signals sourced from the Drive.

The configuration of the SSD is controlled using the standard IDE configuration registers starting at address 200h in the Attribute Memory space of the memory drive.

Table 11: Pin Assignment, Type, and description

| Signal description                                                                                                                                                                                                                                                         | Pin<br>Type | Signal<br>Name                   | Pin | Num | Signal<br>Name | Pin<br>Type | Signal description                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------|-----|-----|----------------|-------------|---------------------------------------------------------------|

| Reset signal from host. Reset is active on power up and inactive thereafter.                                                                                                                                                                                               | I           | -RESET                           | 1   | 2   | GND            |             | Ground                                                        |

|                                                                                                                                                                                                                                                                            | 1/0         | Do7                              | 3   | 4   | Do8            | 1/0         |                                                               |

| Pins 3 through 18 (16 lines (15-                                                                                                                                                                                                                                           | 1/0         | Do6                              | 5   | 6   | D09            | 1/0         |                                                               |

| o) carry the data between the                                                                                                                                                                                                                                              | 1/0         | Do5                              | 7   | 8   | D10            | 1/0         | Pins 3 through 18 (16 lines (15-0) carry the data between the |

| controller and the host. The                                                                                                                                                                                                                                               | 1/0         | Do4                              | 9   | 10  | D11            | 1/0         | controller and the host. The low 8                            |

| low 8 lines transfer commands and the ECC information                                                                                                                                                                                                                      | 1/0         | Do3                              | 11  | 12  | D12            | 1/0         | lines transfer commands and the                               |

| between the host and the                                                                                                                                                                                                                                                   | 1/0         | D02                              | 13  | 14  | D13            | 1/0         | ECC information between the host and the controller.          |

| controller.                                                                                                                                                                                                                                                                | 1/0         | D01                              | 15  | 16  | D14            | 1/0         |                                                               |

|                                                                                                                                                                                                                                                                            | 1/0         | Doo                              | 17  | 18  | D15            | 1/0         |                                                               |

| Ground                                                                                                                                                                                                                                                                     |             | GND                              | 19  | 20  | Key            |             | Connector key                                                 |

| Not used.                                                                                                                                                                                                                                                                  | 0           | DMARQ                            | 21  | 22  | GND            |             | Ground                                                        |

| This I/O Write strobe pulse is used to clock I/O data or commands on the drive data bus into the drive controller registers when the drive is configured to use the I/O interface. The clocking will occur on the negative to positive edge of the signal (trailing edge). | I           | -IOWR/<br>STOP                   | 23  | 24  | GND            |             | Ground                                                        |

| This is a Read strobe generated by the host. The signal gates I/O data or status on the host bus and strobes the data from the controller into the host on the low to high transition (trailing edge).                                                                     | I           | -IORD<br>HSTROBE<br>-<br>HDMARDY | 25  | 26  | GND            |             | Ground                                                        |

| Signal description                                                                                                                         | Pin<br>Type | Signal<br>Name                   | Pin | Num | Signal<br>Name | Pin<br>Type | Signal description                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------|-----|-----|----------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| This is IORDY from the card from the drive to the host                                                                                     | 0           | IORDY<br>-<br>DDMARDY<br>DSTROBE | 27  | 28  | CSEL           | I           | This internally pulled up signal is used to configure the drives as the Primary or the Secondary device. When the pin is grounded, the device is configured as the Primary device (master). When the pin is open, the device is configured as a Secondary device (slave). |

| Not used.                                                                                                                                  | - 1         | -DMACK                           | 29  | 30  | GND            |             | Ground                                                                                                                                                                                                                                                                    |

| This is an interrupt request from the drive to the host, asking for service. This signal is the active high Interrupt Request to the host. | 0           | INTRQ                            | 31  | 32  | (IOCS16)       | 0           | Not used.                                                                                                                                                                                                                                                                 |

| The address lines A1 and A0 are used to select one of eight registers in the controller Task                                               | ı           | A1                               | 33  | 34  | -PDIAG         | 1/0         | After an Executive diagnostic command to indicate that the Primary device has passed its diagnostics, this bi-directional open drain signal is asserted by the Secondary device.                                                                                          |

| riie.                                                                                                                                      | I           | Ао                               | 35  | 36  | A2             | I           | The address line A2 is used to select one of eight registers in the controller Task File.                                                                                                                                                                                 |

| The chip select signal used to select the Task File register.                                                                              | _           | -cso                             | 37  | 38  | -CS1           | 1           | The chip select signal used to select<br>the Alternate Status register and<br>the Device Control register.                                                                                                                                                                |

| This input/output is the Disk Active/Secondary Present signal in the Primary/ Secondary handshake protocol.                                | 0           | -DASP                            | 39  | 40  | GND            |             | Ground                                                                                                                                                                                                                                                                    |

| 5V Power Supply                                                                                                                            |             | VCC                              | 41  | 42  | VCC            |             | 5V Power Supply                                                                                                                                                                                                                                                           |

| Ground                                                                                                                                     |             | GND                              | 43  | 44  | NC             |             |                                                                                                                                                                                                                                                                           |

# 5.2 Master-Slave configuration

The SSD can be configured as IDE Master or Slave Device with a Jumper beside the 44-pin connector (pins A, B, C, and D).

Table 12: Master Slave configuration

| Jumper    | Device configuration |  |

|-----------|----------------------|--|

| No Jumper |                      |  |

| A to C    | Master               |  |

| C to D    |                      |  |

| A to B    | Slave                |  |

| B to D    | Cable Select*        |  |

<sup>\*)</sup> The Device is master, if it is connected at the end, or slave, if it is connected at the middle connector of a standard IDE cable

# 5.3 Electrical Specification

Table 15 - Table 18 define the DC Characteristics SSD. Unless otherwise stated, conditions are:

- Vcc = 5V ± 10%

- o°C to +70°C

The current is measured by connecting an amp meter in series with the Vcc supply. The meter should be set to the 2A scale range, and have a fast current probe with an RC filter with a time constant of 0.1ms. Current measurements are taken while looping on a data transfer command with a sector count of 128. Current consumption values for both read and write commands are not to exceed the Maximum Average RMS Current specified in Table 14.

Table 13: Absolute Maximum Conditions

| Parameter                                         | Symbol | Conditions        |

|---------------------------------------------------|--------|-------------------|

| Input Power                                       | VCC    | -0.3V to 6.5V     |

| Voltage on any pin except VCC with respect to GND | V      | -0.5V to VCC+0.5V |

Table 14: Input Power write and read tests

|       | par                         |            |

|-------|-----------------------------|------------|

| Mode  | Maximum Average RMS Current | Conditions |

| UDMA4 | 140mA                       | -40 +85 °C |

| MDMA2 | 110mA                       | -40 +85 °C |

Table 15: Input Leakage current(1)

| Type | Parameter             | Symbol | Conditions            | Min. | Тур. | Max. | Units |

|------|-----------------------|--------|-----------------------|------|------|------|-------|

| IxZ  | Input Leakage Current | IL     | VIH =VCC<br>VIL = GND | -1   |      | 1    | μА    |

| IxU  | Pull Up Resistor      | RPU1   | Vcc = 5.0V            | 50   |      | 500  | k0hm  |

| IxD  | Pull Down Resistor    | RPD1   | Vcc = 5.0V            | 50   |      | 500  | k0hm  |

<sup>1.</sup> x refers to the characteristics described in Table 16 For example, I1U indicates a pull up resistor with a type 1 input characteristic.

Table 16: Input characteristics

| Туре | Parameter                          | Symbol      | Min. | Тур. | Max. | Units |

|------|------------------------------------|-------------|------|------|------|-------|

| 1    | Input Voltage CMOS                 | <b>V</b> IH | 2.0  |      | 5.3  | V     |

| ı    | Input Voltage CMOS                 | VIL         | -0.3 |      | 0.8  | V     |

| 2    | Input Voltago CMOS                 | <b>V</b> IH | 2.0  |      | 5.3  | V     |

| 2    | Input Voltage CMOS                 | VIL         | -0.3 |      | 0.8  | V     |

| 2    | Input Voltago CMOS Schmitt Trigger | <b>V</b> TH | 2.0  |      | 5.3  | V     |

| 5    | Input Voltage CMOS Schmitt Trigger | <b>V</b> TL | -0.3 | _    | 0.8  | V     |

Table 17: Output Drive Type(1)

| Туре | Output Type           | Valid Conditions |

|------|-----------------------|------------------|

| 0tx  | Totempole             | Іон & Іог        |

| 0zx  | Tri-State N-P Channel | Іон & Іог        |

| 0px  | P-Channel Only        | Iон only         |

| 0nx  | N-Channel Only        | lot only         |

<sup>1.</sup> x refers to the characteristics described in Table 16 For example, OT3 refers to totem pole output with a type 3 output drive characteristic.

**Table 18: Output Drive Characteristics**

| Type | Parameter       | Symbol      | Conditions             | Min.            | Typ. | Max. | Units |

|------|-----------------|-------------|------------------------|-----------------|------|------|-------|

| 1    | Output Voltage  | <b>V</b> oH | Iон= -1mA              | 2.4             |      |      | V     |

|      |                 | <b>V</b> 0L | $I_{OL} = 4mA$         |                 |      | 0.45 | V     |

| 2    | Output Voltage  | <b>V</b> oH | I <sub>0H</sub> = −1mА | 2.4             |      |      | V     |

|      |                 | <b>V</b> 0L | $I_{OL} = 4mA$         |                 |      | 0.45 | V     |

| 3    | Output Voltage  | <b>V</b> oH | Iон= −1mA              | 2.4             |      |      | V     |

|      |                 | <b>V</b> 0L | $I_{OL} = 4mA$         |                 |      | 0.45 | V     |

|      | Tri-State       | loz         | Vo∟= Gnd               | <del>-</del> 10 |      | 10   | μА    |

| Х    | Leakage Current | 102         | $V_{OH} = V_{CC}$      | -10             |      | 10   | μА    |

# **6 Command Interface**

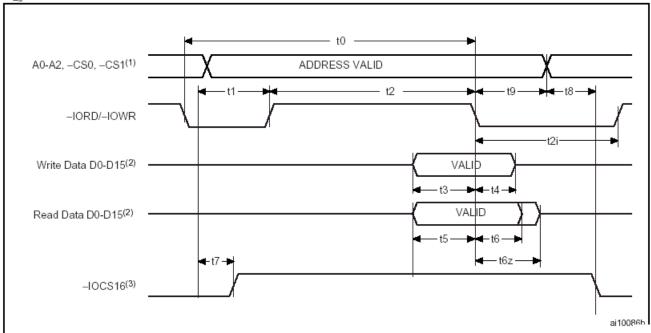

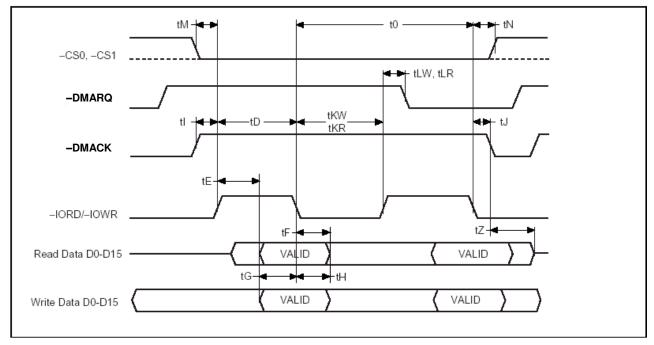

There are two types of bus cycles and timing sequences that occur in the IDE interface, PIO and Multi-Word DMA (MDMA) as well as Ultra DMA (UDMA).

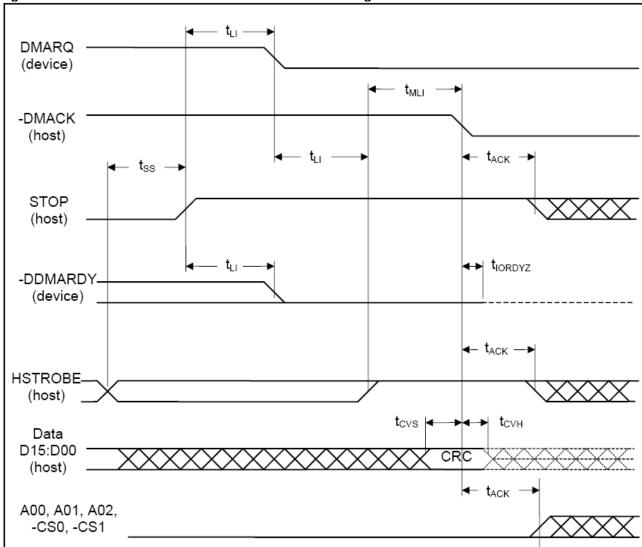

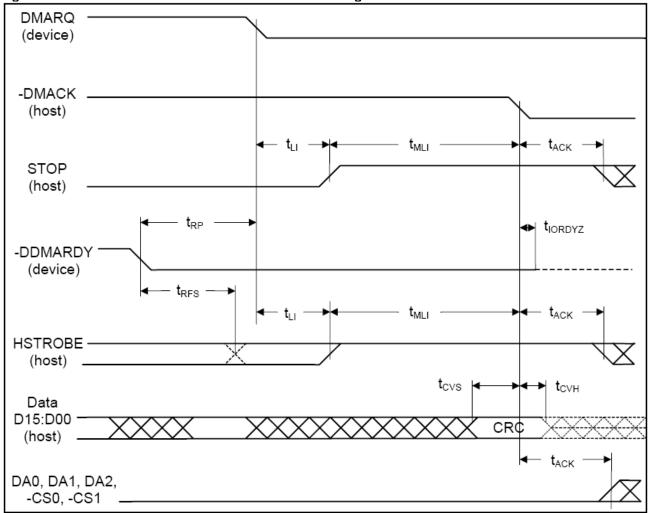

Figure 1 and Figure 2 show the read and write timing diagrams. Table 19, and Table 20 specify the read and write timing parameters for PIO and MDMA mode, respectively.

# 6.1 PIO Mode

The timing waveforms for True IDE mode and True IDE DMA mode of operation in this section are drawn using the conventions in the ATA-7 specification. Signals are shown with their asserted state as High regardless of whether the signal is actually negative or positive true. Consequently, the -IORD, the -IOWR and the -IOCS16 signals are shown in the waveforms inverted from their electrical states on the bus.

Figure 1: True IDE PIO mode Read/Write waveforms

- 1. The device addresses consists of -CSo, -CS1, and A2-Ao.

- 2. The Data I/O consist of D15-Do (16-bit) or D7-Do (8 bit).

- 3. -IOCS16 is shown for PIO modes o, 1 and 2. For other modes, this signal is ignored.

Table 19: True IDE PIO mode Read/Write timing(1)

| Parameter                                | Symbol                         | Mode o<br>(ns) | 1<br>(ns) | 2<br>(ns) | 3<br>(ns) | 4<br>(ns) |

|------------------------------------------|--------------------------------|----------------|-----------|-----------|-----------|-----------|

| Cycle time (min)                         | $t_0^{(2)}$                    | 600            | 383       | 240       | 180       | 120       |

| Address Valid to -IORD/-IOWR setup (min) | $t_1$                          | 70             | 50        | 30        | 30        | 25        |

| -IORD/-IOWR (min)                        | t <sub>2</sub> <sup>(2)</sup>  | 165            | 125       | 100       | 80        | 70        |

| -IORD/-IOWR (min) Register (8 bit)       | t <sub>2</sub> <sup>(2)</sup>  | 290            | 290       | 290       | 80        | 70        |

| -IORD/-IOWR recovery time (min)          | t <sub>2i</sub> <sup>(2)</sup> | _              | -         | _         | 70        | 25        |

| -IOWR data setup (min)                   | $t_3$                          | 60             | 45        | 30        | 30        | 20        |

| -IOWR data hold (min)                    | t <sub>4</sub>                 | 30             | 20        | 15        | 10        | 10        |

| -IORD data setup (min)                   | t <sub>5</sub>                 | 50             | 35        | 20        | 20        | 20        |

| -IORD data hold (min)                    | t <sub>6z</sub> <sup>(3)</sup> | 5              | 5         | 5         | 5         | 5         |

| -IORD data tri-state (max)               | t <sub>7</sub> <sup>(4)</sup>  | 30             | 30        | 30        | 30        | 30        |

| Address valid to -IOCS16 assertion (max) | t <sub>8</sub> <sup>(4)</sup>  | 90             | 50        | 40        | NA        | NA        |

| Address valid to -IOCS16 released (max)  | t <sub>7</sub>                 | 60             | 45        | 30        | NA        | NA        |

| -IORD/-IOWR to address valid hold        | t <sub>9</sub>                 | 20             | 15        | 10        | 10        | 10        |

- The maximum load on -IOCS16 is 1 LSTTL with a 50pF total load.

- $t_o$  is the minimum total cycle time,  $t_o$  is the minimum command active time, and  $t_o$  is the minimum command recovery time or command inactive time. The actual cycle time equals the sum of the actual command inactive time. The three timing requirements of to,  $t_2$ , and  $t_{2i}$  have to be met. The requirement is greater than the sum of  $t_2$  and  $t_{2i}$ . This means a host implementation can ensure that to is equal to or greater than the value reported in the devices identify drive implementation should support any legal host implementation.

- This parameter specifies the time from the falling edge of -10RD to the moment when the drive (tri-state).  $t_7$  and  $t_8$  apply only to modes 0, 1 and 2. The -10CS16 signal is not valid for other modes.

#### 6.2 MDMA Mode

Figure 2: True IDE Multi-Word DMA Mode Read/Write waveforms

Table 20: True IDF Multi-Word DMA Mode Read/Write timing

| Parameter                          | Symbol                         | Mode o<br>(ns) | 1<br>(ns) | 2<br>(ns) |

|------------------------------------|--------------------------------|----------------|-----------|-----------|

| Cycle time (min)                   | t <sub>0</sub> <sup>(1)</sup>  | 480            | 150       | 120       |

| -IORD / -IOWR asserted width (min) | t <sub>D</sub> <sup>(1)</sup>  | 215            | 80        | 70        |

| -IORD data access (max)            | t <sub>E</sub>                 | 150            | 60        | 50        |

| -IORD data hold (min)              | t <sub>F</sub>                 | 5              | 5         | 5         |

| -IORD/-IOWR data setup (min)       | $t_{G}$                        | 100            | 30        | 20        |

| -IOWR data hold (min)              | t <sub>H</sub>                 | 20             | 15        | 10        |

| DMACK to -IORD/-IOWR setup (min)   | tı                             | 0              | 0         | 0         |

| -IORD / -IOWR to -DMACK hold (min) | t,                             | 20             | 5         | 5         |

| -IORD Low width (min)              | t <sub>KR</sub> <sup>(1)</sup> | 50             | 50        | 25        |

| -IOWR Low width (min)              | t <sub>KW</sub> <sup>(1)</sup> | 215            | 50        | 25        |

| -IORD to DMARQ delay (max)         | t <sub>LR</sub>                | 120            | 40        | 35        |

| -IOWR to DMARQ delay (max)         | t <sub>LW</sub>                | 40             | 40        | 35        |

| CS(1:0) valid to –IORD / -IOWR     | t <sub>M</sub>                 | 50             | 30        | 25        |

| CS(1:0) hold                       | t <sub>N</sub>                 | 15             | 10        | 10        |

| -DMACK                             | t <sub>Z</sub>                 | 20             | 25        | 25        |

<sup>1.</sup>  $t_0$  is the minimum total cycle time.  $T_D$  is the minimum command active time.  $T_{KR}$  and  $t_{KW}$  are the minimum command recovery time or command inactive time for input and output cycles, respectively. The actual cycle time is the sum of the actual command active time and the actual command inactive time. The timing requirements of to, to, tkr, and tkw must be respected.  $T_0$  is higher than  $t_D + t_{KR}$  or  $t_D + t_{KW}$ , for input and output cycles respectively. This means the host can lengthen either  $t_0$  or  $t_{KR}/t_{KW}$ , or both, to ensure that  $t_0$  is equal to or higher than the value reported in the devices identify device data. A Drive implementation shall support any legal host implementation.

# 6.3 Ultra DMA Mode

### 6.3.1 Ultra DMA Overview

Ultra DMA is an optional data transfer protocol used with the READ DMA, and WRITE DMA, commands. When this protocol is enabled, the Ultra DMA protocol shall be used instead of the Multiword DMA protocol when these commands are issued by the host. This protocol applies to the Ultra DMA data burst only. When this protocol is used there are no changes to other elements of the ATA protocol (e.g., Command Block Register access).

The usage of signals in each of the modes is shown in Table 21: Signal Usage in PIO/MDMA vs. UDMA Mode

Table 21: Signal Usage in PIO/MDMA vs. UDMA Mode

| UDMA Signal              | Pin        | Type   | PIO /<br>MDMA | UDMA                                                         | Remark                     |

|--------------------------|------------|--------|---------------|--------------------------------------------------------------|----------------------------|

| DMARQ                    | 21         | Output |               | DMARQ                                                        |                            |

| DMACK                    | 29         | Input  |               | -DMACK                                                       |                            |

| STOP                     | 23         | Input  | -IOWR         | STOP 1                                                       |                            |

| HDMARDY(R)<br>HSTROBE(W) | 25         | Input  | -IORD         | -HDMARDY(R) <sup>1, 2</sup><br>HSTROBE(W) <sup>1, 3, 4</sup> | UDMA write clock from host |

| DDMARDY(W)<br>DSTROBE(R) | 27         | Output | IORDY         | -DDMARDY(W) 1,3<br>DSTROBE(R) 1.2.4                          | UDMA read clock from drive |

| DATA                     | 3 - 18     | Bidir  |               | D[15:00]                                                     |                            |

| ADDRESS                  | 33, 35, 36 | Input  |               | A[02:00]                                                     |                            |

| CSEL                     | 28         | Input  |               | -CSEL                                                        |                            |

| INTRQ                    | 31         | Output | INTRQ         |                                                              |                            |

| Card Select              | 37, 38     | Input  |               | -CS0, -CS1                                                   |                            |

#### Notes:

- 1. The UDMA interpretation of this signal is valid only during an Ultra DMA data burst.

- 2. The UDMA interpretation of this signal is valid only during and Ultra DMA data burst during a DMA Read command.

- The UDMA interpretation of this signal is valid only during an Ultra DMA data burst during a DMA Write command.

- 4. The HSTROBE and DSTROBE signals are active on both the rising and the falling edge.

Several signal lines are redefined to provide different functions during an Ultra DMA burst. These lines assume these definitions when:

- 1. an Ultra DMA mode is selected, and

- 2. a host issues a READ DMA, or a WRITE DMA command requiring data transfer, and

- 3. the device asserts (-)DMARQ, and

- 4. the host asserts -DMACK.

These signal lines revert back to the definitions used for non-Ultra DMA transfers upon the negation of - DMACK by the host at the termination of an Ultra DMA burst.

With the Ultra DMA protocol, the STROBE signal that latches data from D[15:00] is generated by the same agent (either host or device) that drives the data onto the bus. Ownership of D[15:00] and this data strobe signal are given either to the device during an Ultra DMA data-in burst or to the host for an Ultra DMA data-out burst.

During an Ultra DMA burst a sender shall always drive data onto the bus, and, after a sufficient time to allow for propagation delay, cable settling, and setup time, the sender shall generate a STROBE edge to latch the data. Both edges of STROBE are used for data transfers so that the frequency of STROBE is limited to the same frequency as the data.

Words in the IDENTIFY DEVICE data indicate support of the Ultra DMA feature and the Ultra DMA modes the device is capable of supporting. The Set transfer mode subcommand in the SET FEATURES command shall be used by a host to select the Ultra DMA mode at which the system operates. The Ultra DMA mode selected by a host shall be less than or equal to the fastest mode of which the device is capable. Only one Ultra DMA mode shall be selected at any given time. All timing requirements for a selected Ultra DMA mode shall be satisfied. Devices supporting any Ultra DMA mode shall also support all slower Ultra DMA modes. An Ultra DMA capable device shall retain the previously selected Ultra DMA mode after executing a software reset sequence or the sequence caused by receipt of a DEVICE RESET command if a SET FEATURES disable reverting to defaults command has been issued. The device may revert to a Multiword DMA mode if a SET FEATURES enable reverting to default has been issued. An Ultra DMA capable device shall clear any

previously selected Ultra DMA mode and revert to the default non-Ultra DMA modes after executing a power-on or hardware reset.

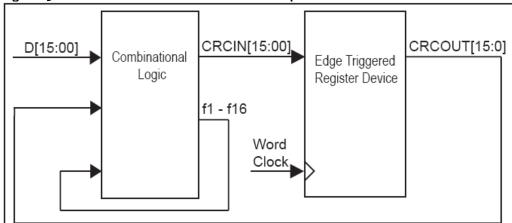

Both the host and device perform a CRC function during an Ultra DMA burst. At the end of an Ultra DMA burst the host sends its CRC data to the device. The device compares its CRC data to the data sent from the host. If the two values do not match, the device reports an error in the error register. If an error occurs during one or more Ultra DMA bursts for any one command, the device shall report the first error that occurred. If the device detects that a CRC error has occurred before data transfer for the command is complete, the device may complete the transfer and report the error or abort the command and report the error.

NOTE – If a data transfer is terminated before completion, the assertion of INTRQ should be passed through to the host software driver regardless of whether all data requested by the command has been transferred.

# 6.3.1.1 UDMA Address and Card Select Signals

The Card Select signals -CSo and -CS1) shall remain negated during Ultra DMA data bursts. The Address bus (A[2:0]) shall not transition unnecessarily during the UDMA command and shall remain fixed during an Ultra DMA data burst. In True IDE mode, the address lines (A[2:0]) shall be held to all zeros. This will reduce unnecessary noise during the UDMA command.

# 6.3.1.2 Task File registers shall not be written during an Ultra DMA command

The task file registers shall not be written after an Ultra DMA command is issued by the host and before the command completes. Writing to the device control register is permitted between bursts, but is expected to occur only to reset the drive after an unrecoverable protocol error.

# 6.3.1.3 Ultra DMA transfers shall be 16 bits wide

All transfers during an Ultra DMA data burst are 16 bit wide transfers. The Set Features command that controls the bus width for PIO transfers does not affect the width of Ultra DMA transfers.

#### 6.3.2 Ultra DMA Phases of Operation

An Ultra DMA data transfer is accomplished through a series of Ultra DMA data-in or data-out bursts. Each Ultra DMA burst has three mandatory phases of operation: the initiation phase, the data transfer phase, and the Ultra DMA burst termination phase. In addition, an Ultra DMA burst may be paused during the data transfer phase (see: 6.3.2.4, for the detailed protocol descriptions for each of these phases. Table 22: Ultra DMA Data Burst Timing Requirements and Table 23: Ultra DMA Data Burst Timing Descriptions define the specific timing requirements). In the following rules –DMARDY is used in cases that could apply to either –DDMARDY or –HDMARDY, and STROBE is used in cases that could apply to either DSTROBE or HSTROBE. The following are general Ultra DMA rules.

- 1. An Ultra DMA burst is defined as the period from an assertion of -DMACK by the host to the subsequent negation of -DMACK.

- 2. When operating in Ultra DMA modes 2, 1, or 0 a recipient shall be prepared to receive up to two data words whenever an Ultra DMA burst is paused. When operating in Ultra DMA modes 6, 5, 4, or 3 a recipient shall be prepared to receive up to three data words whenever an Ultra DMA burst is paused.

# 6.3.2.1 Ultra DMA Burst Initiation Phase Rules

- 1. An Ultra DMA burst initiation phase begins with the assertion of DMARQ by a device and ends when the sender generates a STROBE edge to transfer the first data word.

- 2. An Ultra DMA burst shall always be requested by a device asserting DMARQ.

- 3. When ready to initiate the requested Ultra DMA burst, the host shall respond by asserting -DMACK.

- 4. A host shall never assert -DMACK without first detecting that DMARQ is asserted.

- 5. For Ultra DMA data-in bursts: a device may begin driving D[15:00] after detecting that -DMACK is asserted, STOP negated, and -HDMARDY is asserted.

- 6. After asserting DMARQ or asserting -DDMARDY for an Ultra DMA data-out burst, a device shall not negate either signal until the first STROBE edge is generated.

- 7. After negating STOP or asserting -HDMARDY for an Ultra DMA data-in burst, a host shall not change the state of either signal until the first STROBE edge is generated.

# 6.3.2.2 Ultra DMA Data transfer phase rules

- The data transfer phase is in effect from after Ultra DMA burst initiation until Ultra DMA burst termination.

- 2. A recipient pauses an Ultra DMA burst by negating -DMARDY and resumes an Ultra DMA burst by reasserting -DMARDY.

- 3. A sender pauses an Ultra DMA burst by not generating STROBE edges and resumes by generating STROBE edges.

- 4. A recipient shall not signal a termination request immediately when the sender stops generating STROBE edges. In the absence of a termination from the sender the recipient shall always negate DMARDY and wait the required period before signaling a termination request.

- 5. A sender may generate STROBE edges at greater than the minimum period specified by the enabled Ultra DMA mode. The sender shall not generate STROBE edges at less than the minimum period specified by the enabled Ultra DMA mode. A recipient shall be able to receive data at the minimum period specified by the enabled Ultra DMA mode.

### 6.3.2.3 Ultra DMA Burst Termination Phase Rules

- 1. Either a sender or a recipient may terminate an Ultra DMA burst.

- 2. Ultra DMA burst termination is not the same as command completion. If an Ultra DMA burst termination occurs before command completion, the command shall be completed by initiation of a new Ultra DMA burst at some later time or aborted by the host issuing a hardware or software reset or DEVICE RESET command if implemented by the device.

- 3. An Ultra DMA burst shall be paused before a recipient requests a termination.

- 4. A host requests a termination by asserting STOP. A device acknowledges a termination request by negating DMARQ.

- 5. A device requests a termination by negating DMARQ. A host acknowledges a termination request by asserting STOP.

- 6. Once a sender requests a termination, the sender shall not change the state of STROBE until the recipient acknowledges the request. Then, if STROBE is not in the asserted state, the sender shall return STROBE to the asserted state. No data shall be transferred on this transition of STROBE.

- 7. A sender shall return STROBE to the asserted state whenever the sender detects a termination request from the recipient. No data shall be transferred nor CRC calculated on this edge of DSTROBE.

- 8. Once a recipient requests a termination, the responder shall not change DMARDY from the negated state for the remainder of an Ultra DMA burst.

- 9. A recipient shall ignore a STROBE edge when DMARQ is negated or STOP is asserted.

# 6.3.2.4 Ultra DMA Data Transfers Timing

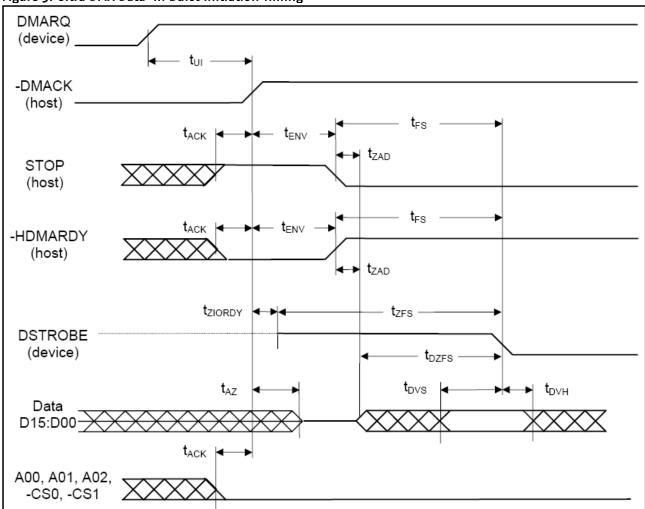

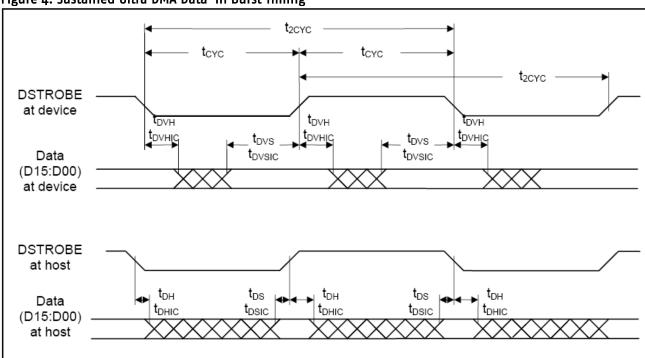

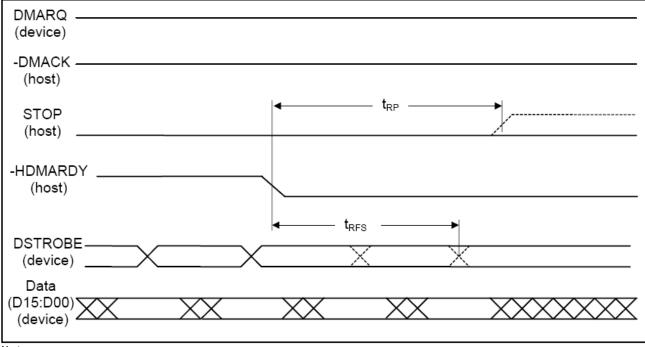

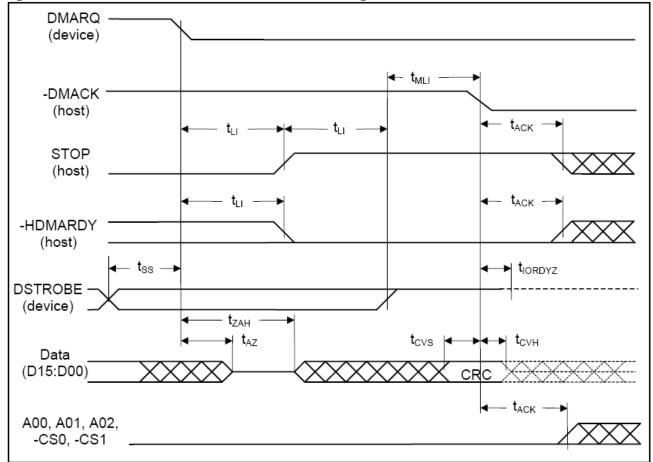

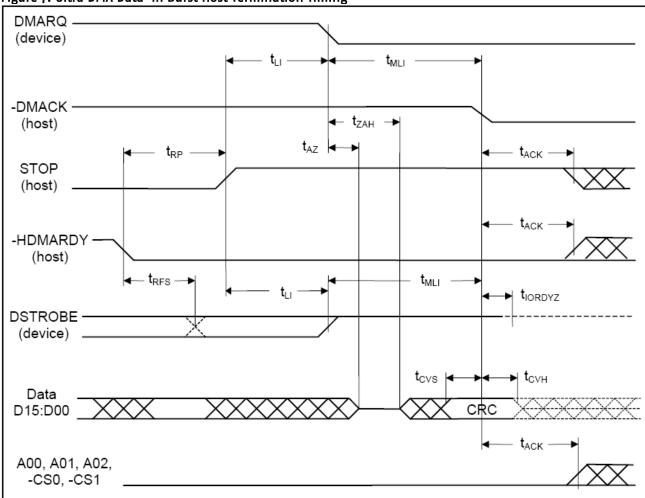

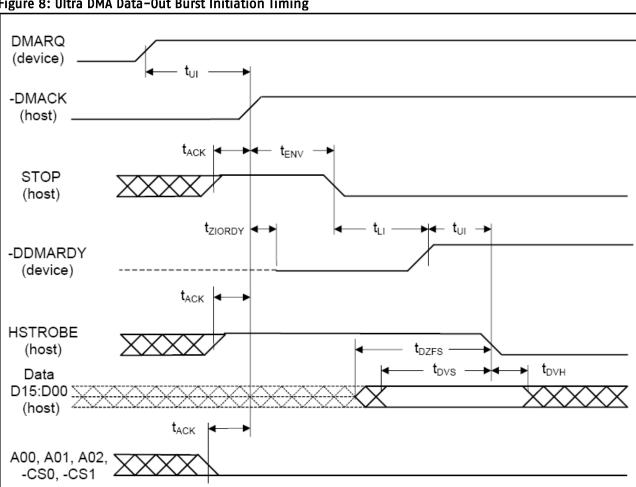

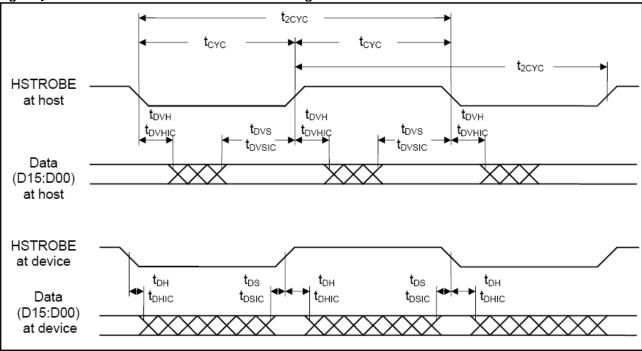

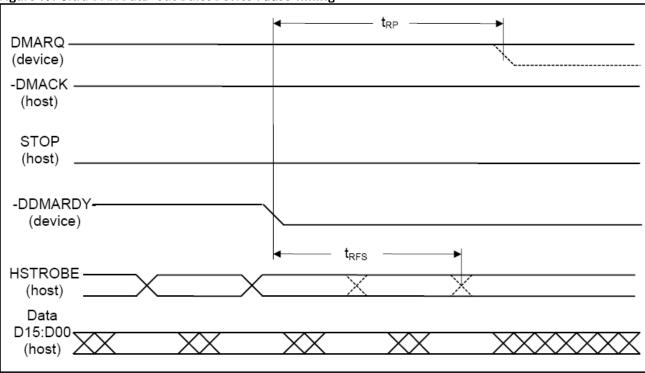

Table 22 and Table 23 define the timings associated with all phases of Ultra DMA bursts.

Table 22: Ultra DMA Data Burst Timing Requirements

| Name                 | Mod<br>(n | le o<br>s) | UDMA<br>Mode 1<br>(ns) |     | Mod<br>(n | MA<br>de 2<br>is) | Mod<br>(r | MA<br>de 3<br>is) | Mod<br>(n | MA<br>de 4<br>is) | Measurement location<br>(See Note 2) |

|----------------------|-----------|------------|------------------------|-----|-----------|-------------------|-----------|-------------------|-----------|-------------------|--------------------------------------|

|                      | Min       | Max        | Min                    | Max | Min       | Max               | Min       | Max               | Min       | Max               |                                      |

| t <sub>2CYCTYP</sub> | 240       |            | 160                    |     | 120       |                   | 90        |                   | 60        |                   | Sender                               |

| t <sub>cyc</sub>     | 112       |            | 73                     |     | 54        |                   | 39        |                   | 25        |                   | Note 3                               |

| t <sub>2CYC</sub>    | 230       |            | 153                    |     | 115       |                   | 86        |                   | 57        |                   | Sender                               |

| t <sub>DS</sub>      | 15.0      |            | 10.0                   |     | 7.0       |                   | 7.0       |                   | 5.0       |                   | Recipient                            |

| t <sub>DH</sub>      | 5.0       |            | 5.0                    |     | 5.0       |                   | 5.0       |                   | 5.0       |                   | Recipient                            |

| t <sub>DVS</sub>     | 70.0      |            | 48.0                   |     | 31.0      |                   | 20.0      |                   | 6.7       |                   | Sender                               |

| $t_DVH$              | 6.2       |            | 6.2                    |     | 6.2       |                   | 6.2       |                   | 6.2       |                   | Sender                               |

| t <sub>cs</sub>      | 15.0      |            | 10.0                   |     | 7.0       |                   | 7.0       |                   | 5.0       |                   | Device                               |

| $t_CH$               | 5.0       |            | 5.0                    |     | 5.0       |                   | 5.0       |                   | 5.0       |                   | Device                               |

| t <sub>cvs</sub>     | 70.0      |            | 48.0                   |     | 31.0      |                   | 20.0      |                   | 6.7       |                   | Host                                 |

| t <sub>cvH</sub>     | 6.2       |            | 6.2                    |     | 6.2       |                   | 6.2       |                   | 6.2       |                   | Host                                 |

| $t_{ZFS}$            | 0         |            | 0                      |     | 0         |                   | 0         |                   | 0         |                   | Device                               |

| $t_{DZFS}$           | 70.0      |            | 48.0                   |     | 31.0      |                   | 20.0      |                   | 6.7       |                   | Sender                               |

| t <sub>FS</sub>      |           | 230        |                        | 200 |           | 170               |           | 130               |           | 120               | Device                               |

| t <sub>LI</sub>      | 0         | 150        | 0                      | 150 | 0         | 150               | 0         | 100               | 0         | 100               | Note 4                               |

| t <sub>MLI</sub>     | 20        |            | 20                     |     | 20        |                   | 20        |                   | 20        |                   | Host                                 |

| t <sub>UI</sub>      | 0         |            | 0                      |     | 0         |                   | 0         |                   | 0         |                   | Host                                 |

| t <sub>AZ</sub>      |           | 10         |                        | 10  |           | 10                |           | 10                |           | 10                | Note 5                               |

| t <sub>ZAH</sub>     | 20        |            | 20                     |     | 20        |                   | 20        |                   | 20        |                   | Host                                 |

| t <sub>ZAD</sub>     | 0         |            | 0                      |     | 0         |                   | 0         |                   | 0         |                   | Device                               |

| t <sub>ENV</sub>     | 20        | 70         | 20                     | 70  | 20        | 70                | 20        | 55                | 20        | 55                | Host                                 |

| t <sub>RFS</sub>     |           | 75         |                        | 70  |           | 60                |           | 60                |           | 60                | Sender                               |

| t <sub>RP</sub>      | 160       |            | 125                    |     | 100       |                   | 100       |                   | 100       |                   | Recipient                            |

| t <sub>IORDYZ</sub>  |           | 20         |                        | 20  |           | 20                |           | 20                |           | 20                | Device                               |

| t <sub>ZIORDY</sub>  | 0         |            | 0                      |     | 0         |                   | 0         |                   | 0         |                   | Device                               |

| t <sub>ACK</sub>     | 20        |            | 20                     |     | 20        |                   | 20        |                   | 20        |                   | Host                                 |

| t <sub>SS</sub>      | 50        |            | 50                     |     | 50        |                   | 50        |                   | 50        |                   | Sender                               |

#### Notes:

- 1. All timing measurement switching points (low to high and high to low) shall be taken at 1.5 V.

- 2. All signal transitions for a timing parameter shall be measured at the connector specified in the measurement location column. For example, in the case of tRFS, both STROBE and -DMARDY transitions are measured at the sender connector.

- 3. The parameter tCYC shall be measured at the recipient's connector farthest from the sender.

- 4. The parameter tLI shall be measured at the connector of the sender or recipient that is responding to an incoming transition from the recipient or sender respectively. Both the incoming signal and the outgoing response shall be measured at the same connector.

- 5. The parameter tAZ shall be measured at the connector of the sender or recipient that is driving the bus but must release the bus the allow for a bus turnaround.

- 6. See the AC Timing requirements in Table 23: Ultra DMA Data Burst Timing Descriptions.

Table 23: Ultra DMA Data Burst Timing Descriptions

| Name                 | Comment                                                                                                                                  | Notes |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------|

| t <sub>2CYCTYP</sub> | Typical sustained average two cycle time                                                                                                 |       |

| t <sub>CYC</sub>     | Cycle time allowing for asymmetry and clock variations (from STROBE edge to STROBE edge)                                                 |       |

| t <sub>2CYC</sub>    | Two cycle time allowing for clock variations (from rising edge to next rising edge or from falling edge to next falling edge of STROBE)  |       |

| t <sub>DS</sub>      | Data setup time at recipient (from data valid until STROBE edge)                                                                         | 2, 5  |

| t <sub>DH</sub>      | Data hold time at recipient (from STROBE edge until data may become invalid)                                                             | 2, 5  |

| t <sub>DVS</sub>     | Data valid setup time at sender (from data valid until STROBE edge)                                                                      | 3     |

| t <sub>DVH</sub>     | Data valid hold time at sender (from STROBE edge until data may become invalid)                                                          | 3     |

| tcs                  | CRC word setup time at device                                                                                                            | 2     |

| t <sub>CH</sub>      | CRC word hold time device                                                                                                                | 2     |

| tcvs                 | CRC word valid setup time at host (from CRC valid until -DMACK negation)                                                                 | 3     |

| t <sub>CVH</sub>     | CRC word valid hold time at sender (from -DMACK negation until CRC may become invalid)                                                   | 3     |

| t <sub>zfs</sub>     | Time from STROBE output released-to-driving until the first transition of critical timing.                                               |       |

| t <sub>DZFS</sub>    | Time from data output released-to-driving until the first transition of critical timing.                                                 |       |

| t <sub>FS</sub>      | First STROBE time (for device to first negate DSTROBE from STOP during a data in burst)                                                  |       |

| t∟ı                  | Limited interlock time                                                                                                                   | 1     |

| t <sub>мы</sub>      | Interlock time with minimum                                                                                                              | 1     |

| tuı                  | Unlimited interlock time                                                                                                                 | 1     |

| t <sub>AZ</sub>      | Maximum time allowed for output drivers to release (from asserted or negated)                                                            |       |

| t <sub>ZAH</sub>     | Minimum delay time required for output                                                                                                   |       |

| t <sub>ZAD</sub>     | drivers to assert or negate (from released)                                                                                              |       |

| t <sub>ENV</sub>     | Envelope time (from -DMACK to STOP and -HDMARDY during data in burst initiation and from DMACK to STOP during data out burst initiation) |       |

| t <sub>RFS</sub>     | Ready-to-final-STROBE time (no STROBE edges shall be sent this long after negation of -DMARDY)                                           |       |

| t <sub>RP</sub>      | Ready-to-pause time (that recipient shall wait to pause after negating -DMARDY)                                                          |       |

| tiordyz              | Maximum time before releasing IORDY                                                                                                      |       |

| tziordy              | Minimum time before driving IORDY                                                                                                        | 4     |

| t <sub>ACK</sub>     | Setup and hold times for -DMACK (before assertion or negation)                                                                           |       |

| t <sub>ss</sub>      | Time from STROBE edge to negation of DMARQ or assertion of STOP (when sender terminates a burst)                                         |       |

#### Notes:

- 1. The parameters  $t_{\text{UI}}$ ,  $t_{\text{MLI}}$  (in Figure 6: Ultra DMA Data-In Burst Device Termination Timing and Figure 7: Ultra DMA Data-In Burst Host Termination Timing), and  $t_{\text{LI}}$  indicate sender-to-recipient or recipient-to-sender interlocks, i.e., one agent (either sender or recipient) is waiting for the other agent to respond with a signal before proceeding.  $t_{\text{UI}}$  is an unlimited interlock that has no maximum time value.  $t_{\text{MLI}}$  is a limited time-out that has a defined maximum.

- 2. 80-conductor cabling shall be required in order to meet setup ( $t_{DS}$ ,  $t_{CS}$ ) and hold ( $t_{DH}$ ,  $t_{CH}$ ) times in modes greater than 2.

- 3. Timing for t<sub>DVS</sub>, t<sub>DVH</sub>, t<sub>CVS</sub> and t<sub>CVH</sub> shall be met for lumped capacitive loads of 15 and 40 pF at the connector where the Data and STROBE signals have the same capacitive load value. Due to reflections on the cable, these timing measurements are not valid in a normally functioning system.

- 4. For all modes the parameter  $t_{ZIORDY}$  may be greater than  $t_{ENV}$  due to the fact that the host has a pull-up on IORDY- giving it a known state when released.

- 5. The parameters  $t_{DS}$ , and  $t_{DH}$  for mode 5 are defined for a recipient at the end of the cable only in a configuration with a single device located at the end of the cable. This could result in the minimum values for  $t_{DS}$  and  $t_{DH}$  for mode 5 at the middle connector being 3.0 and 3.9 ns respectively.

Table 24: Ultra DMA Sender and Recipient IC Timing Requirements

| Name               | Comments                                                                                           |      | UDMA<br>Mode o<br>(ns) |      | UDMA<br>Mode 1<br>(ns) |      | UDMA<br>Mode 2<br>(ns) |      | UDMA<br>Mode 3<br>(ns) |     | UDMA<br>Mode4<br>(ns) |  |

|--------------------|----------------------------------------------------------------------------------------------------|------|------------------------|------|------------------------|------|------------------------|------|------------------------|-----|-----------------------|--|

|                    |                                                                                                    | Min  | Max                    | Min  | Max                    | Min  | Max                    | Min  | Max                    | Min | Max                   |  |

| t <sub>DSIC</sub>  | Recipient IC data setup time (from data valid until STROBE edge) (see note 2)                      | 14.7 |                        | 9.7  |                        | 6.8  |                        | 6.8  |                        | 4.8 |                       |  |

| t <sub>DHIC</sub>  | Recipient IC data hold time (from STROBE edge until data may become invalid) (see note 2)          | 4.8  |                        | 4.8  |                        | 4.8  |                        | 4.8  |                        | 4.8 |                       |  |

| t <sub>DVSIC</sub> | Sender IC data valid setup time<br>(from data valid until STROBE<br>edge) (see note 3)             | 72.9 |                        | 50.9 |                        | 33.9 |                        | 22.6 |                        | 9.5 |                       |  |

| t <sub>DVHIC</sub> | Sender IC data valid hold time<br>(from STROBE edge until data<br>may become invalid) (see note 3) | 9.0  |                        | 9.0  |                        | 9.0  |                        | 9.0  |                        | 9.0 |                       |  |

#### Notes:

- 1. All timing measurement switching points(low to high and high to low) shall be taken at 1.5 V.

- 2. The correct data value shall be captured by the recipient given input data with a slew rate of 0.4 V/ns rising and falling and the input STROBE with a slew rate of 0.4 V/ns rising and falling at t<sub>DSIC</sub> and t<sub>DHIC</sub> timing (as measured through 1.5 V).

- 3. The parameters t<sub>DVSIC</sub> and t<sub>DVHIC</sub> shall be met for lumped capacitive loads of 15 and 40 pF at the IC where all signals have the same capacitive load value. Noise that may couple onto the output signals from external sources has not been included in these values.

Table 25: Ultra DMA AC Signal Requirements

| Name              | Comment                               | Min<br>[V/ns] | Max<br>[V/ns] | Notes |

|-------------------|---------------------------------------|---------------|---------------|-------|

| S <sub>RISE</sub> | Rising Edge Slew Rate for any signal  |               | 1.25          | 1     |

| S <sub>FALL</sub> | Falling Edge Slew Rate for any signal |               | 1.25          | 1     |

#### Note:

1. The sender shall be tested while driving an 18 inch long, 80 conductor cable with PVC insulation material. The signal under test shall be cut at a test point so that it has not trace, cable or recipient loading after the test point. All other signals should remain connected through to the recipient. The test point may be located at any point between the sender's series termination resistor and one half inch or less of conductor exiting the connector. If the test point is on a cable conductor rather than the PCB, an adjacent ground conductor shall also be cut within one half inch of the connector.

The test load and test points should then be soldered directly to the exposed source side connectors. The test loads consist of a 15 pF or a 40 pF, 5%, 0.08 inch by 0.05 inch surface mount or smaller size capacitor from the test point to ground. Slew rates shall be met for both capacitor values.

Measurements shall be taken at the test point using a <1 pF, >100 k0hm, 1 GHz or faster probe and a 500 MHz or faster oscilloscope. The average rate shall be measured from 20% to 80% of the settled VOH level with data transitions at least 120 ns apart. The settled VOH level shall be measured as the average output high level under the defined testing conditions from 100 nsec after 80% of a rising edge until 20% of the subsequent falling edge.

# 6.3.2.4.1 Initiating an Ultra DMA Data-In Burst