## SCG102A Synchronous Clock Generators

PLL

2111 Comprehensive Drive

Aurora, Illinois 60505

Phone: 630-851-4722

Fax: 630-851-5040

www.conwin.com

### **Applications**

- SONET / SDH / ATM

- DWDM / FDM

- DSL-PON Interconnects

- FEC (Forward Error Correction)

#### **Features**

- 3.3V High Precision PLL

- Accepts 1 of 4 Selectable, Pre-determined Input Frequencies

- 77.76 MHz to 170 MHz Output Frequencies Available.

- Jitter Generation OC-192 Compliant

- 1.0" x 0.80" x 0.285", Surface Mount

| Bulletin  | SG076     |

|-----------|-----------|

| Page      | 1 of 8    |

| Revision  | 00        |

| Date      | 11 APR 07 |

| Issued By | ENG       |

#### **General Description**

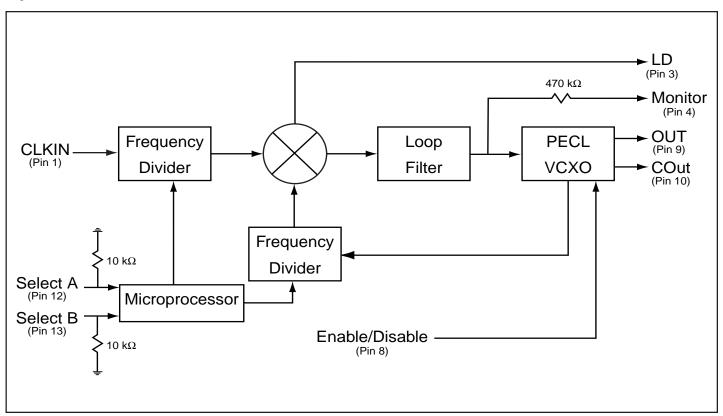

The SCG102A provides high precision phase lock loop frequency translation for the telecommunication applications. The SCG102A product generates LVPECL outputs from an intrinsically low jitter, voltage controlled crystal oscillator.

SCG102A is well suited for use in line cards, service termination cards and similar functions to provide reliable reference, phase locked, synchronization for TDM, PDH, SONET and SDH network equipment. The SCG102A provides a jitter filtered, wander following output signal sychronized to a superior Stratum or peer input reference signal.

The SCG102A includes a lock detect alarm output. The PLL control voltage is brought out through a 470 k $\Omega$  restistor and can be used to determine when the pull range limits are reached.The

LVPECL outputs may be put into the tri-state high impedance condition for external testing purposes by asserting a high signal to the Enable/Disable pin.

The SCG102A is a 3.3 Volt component that will typically draw 75mA. The SCG102A is designed to be used in applications that require temperature rating of -40°C - 85° C. The SCG102A package typical dimensions are 1.0" x 0.80" x 0.285" (See fig. 2 for maximum dimensions). Parts are assembled using high temperature solder to withstand surface mount reflow process.

The SCG102A locks to any one of four pred-determined input frequencies selected using the SELECT (A&B) lines (See Table 4). The output may be any single frequency from 77.76 MHz to 170 MHZ.

#### **Functional Block Diagram**

Figure 1

### **Absolute Maximum Rating**

Table 1

| Symbol         | Parameter            | Minimum | Nominal | Maximum | Units | Notes |  |

|----------------|----------------------|---------|---------|---------|-------|-------|--|

| Vcc            | Power Supply Voltage | -0.3    |         | 5.5     | Volts |       |  |

| ٧ <sub>I</sub> | Input Voltage        | -0.3    |         | Vcc     | Volts |       |  |

| Ts             | Storage Temperature  | -55     |         | 125     | °C    |       |  |

Data Sheet #: **SG076** Page **2** of **8** Rev: **00** Date: **4/11/07**

# **Specifications**

Table 2

| Symbol            | Parameter                                  | Minimum    | Nominal      | Maximum        | Units    | Notes |

|-------------------|--------------------------------------------|------------|--------------|----------------|----------|-------|

| f <sub>IN</sub>   | Available Input Frequencies CMOS PECL      | 8 k<br>1 M |              | 100 M<br>100 M | Hz<br>Hz |       |

| f <sub>out</sub>  | Output Frequencies(LVPECL)                 | 77.76 M    |              | 170 M          | Hz       |       |

| Vcc               | Supply Voltage                             | 3.135      | 3.3          | 3.465          | Volts    |       |

| I <sub>cc</sub>   | Supply Current                             |            | 75           | 100            | mA       |       |

| CLKIN             | Input Logic A = CMOS D = PECL              |            | CMOS<br>PECL |                |          | 1     |

| CLKOUT            | Output Logic <b>F</b> = Comp. PECL         |            | PECL         |                |          |       |

| V <sub>OH</sub>   |                                            | 2.275      |              |                | V        |       |

| $V_{OL}$          |                                            |            |              | 1.68           | V        |       |

| $T_R/T_F$         | Rise/Fall Time                             |            | 0.5          | 1              | ns       |       |

| SYM               | Output Symmetry                            | 45         |              | 55             | %        |       |

| BW                | Bandwidth                                  |            | 20           |                | Hz       |       |

| $J_{GEN}$         | Jitter Generation RMS<br>(12 kHz - 20 MHz) |            | 0.5          | 1              | ps       |       |

| J <sub>TRAN</sub> | Jitter Transfer                            |            |              | 0.1            | dB       | 2     |

| APR               | Input Frequency Tracking                   | ±50        |              |                | ppm      |       |

| T <sub>OP</sub>   | Operating Temperature F = C =              | -40<br>0   |              | 85<br>70       | °C<br>°C |       |

NOTES: 1.0: Only HCMOS and LVHCMOS is supported for input frequencies < 1MHz

2.0: GR-253-CORE, Sec. 5.6.2.1.2

## **Pin Description**

#### Table 3

| Pin# | Connection      | Description                                                                                                                                    |  |

|------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | CLKIN           | Input Frequency - The SCG102A AC couples the input, this means that the unit is capable of handling HCMOS, LVCMOS, PECL, LVPECL input signals. |  |

| 2    | GND             | Ground                                                                                                                                         |  |

| 3    | Lock Detector   | Logic "1" indicates that the unit is locked to the input reference Logic "0" indicates that the reference is lost or out of lock range         |  |

| 4    | VCXO Monitor    | Control voltage level for the PECL oscillator (Between 0.3V and 3.0V when locked)                                                              |  |

| 5    |                 | Missing                                                                                                                                        |  |

| 6    | NC              | No connection                                                                                                                                  |  |

| 7    | GND             | Ground                                                                                                                                         |  |

| 8    | Enable/Disable  | Logic "0" (or no connect) = Output Enabled Logic "1" = Output Disabled (Tri-Stated)                                                            |  |

| 9    | Out             | Output                                                                                                                                         |  |

| 10   | COut            | Complementary Output                                                                                                                           |  |

| 11   | NC              | No connection                                                                                                                                  |  |

| 12   | Select A        | Input Frequency Select Control Pin. See Table 4.                                                                                               |  |

| 13   | Select B        | Input Frequency Select Control Pin. See Table 4.                                                                                               |  |

| 14   | NC              | No connection                                                                                                                                  |  |

| 15   | GND             | Ground                                                                                                                                         |  |

| 16   | V <sub>cc</sub> | Power supply voltage (3.3 Vdc ± 5%)                                                                                                            |  |

Data Sheet #: **SG076** Page **3** of **8** Rev: **00** Date: **4/11/07**

Table 4

| Input Freq     | SEL A | SEL B |

|----------------|-------|-------|

| f <sub>1</sub> | 0     | 0     |

| $f_2$          | 0     | 1     |

| f <sub>3</sub> | 1     | 0     |

| f <sub>4</sub> | 1     | 1     |

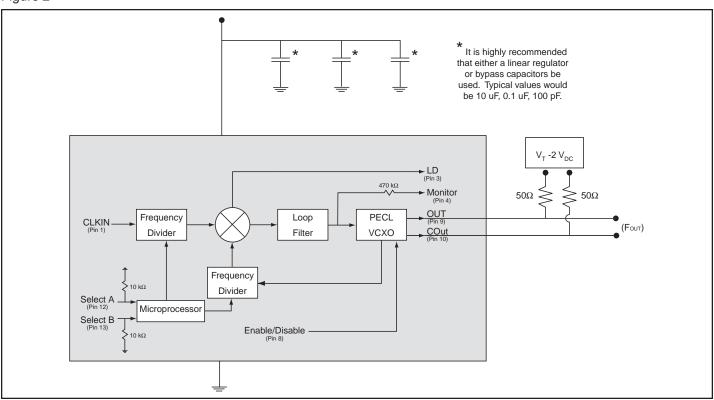

## **Output Load and Power Supply Filtering Recommendations**

Figure 2

Data Sheet #: **SG076** Page **4** of **8** Rev: **00** Date: **4/11/07**

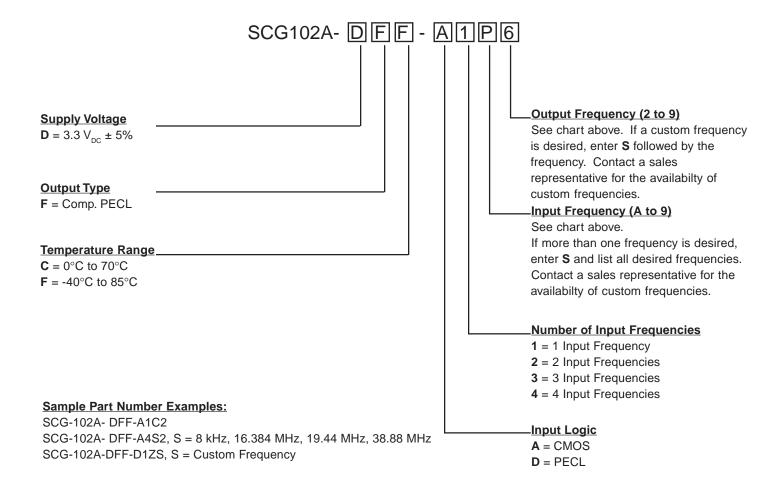

#### **Ordering Information**

Table 5

| 10 MHz    | А | 8.192 MHz    | L | 51.84 MHz    | 0 |

|-----------|---|--------------|---|--------------|---|

| 10 kHz    | В | 13.00 MHz    | M | 61.44 MHz    | 1 |

| 8 kHz     | С | 16.384 MHz   | N | 77.76 MHz    | 2 |

| 16 kHz    | D | 19.44 MHz    | Р | 82.944 MHz   | 3 |

| 64 kHz    | E | 20.48 MHz    | R | 112.00 MHz   | 4 |

| 1.024 MHz | F | 26.00 MHz    | T | 139.264 MHz  | 5 |

| 1.048 MHz | G | 27.00 MHz    | W | 155.52 MHz   | 6 |

| 1.544 MHz | H | 38.88 MHz    | X | 166.6286 MHz | 7 |

| 2.048 MHz | J | 44.736 MHz   | Y | 114.0 MHz    | 8 |

| 4.096 MHz | K | 53.10468 MHz | Z | 125.0 MHz    | 9 |

For any model, the reference inputs and output frequency must have a common frequency of 2.667Hz (8kHz/3) Ex 1: A Model with reference inputs of 8kHz, 16kHz, 32kHz and 64kHz with a Output frequency of 155.52MHz is valid due to the common frequency of 2.667kHz. Contact CW regarding models that do not have a input/output common frequency of 2.667kHz.

Data Sheet #: **SG076** Page **5** of **8** Rev: **00** Date: **4/11/07**

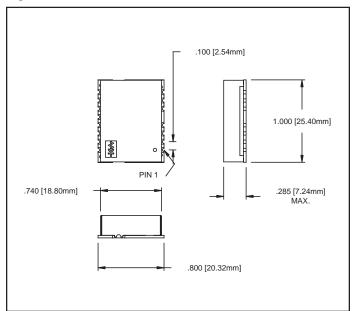

## **Package Dimensions**

Figure 3

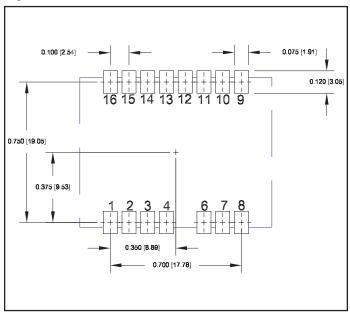

## **Recommended Footprint Dimensions**

Figure 4

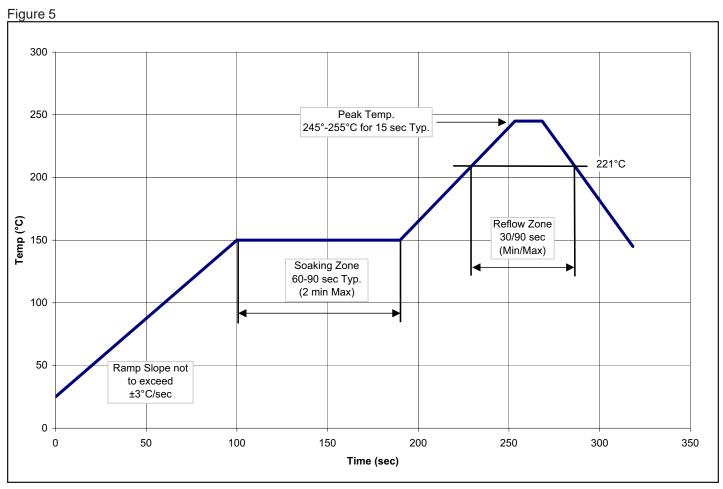

#### **Solder Profile**

Data Sheet #: **SG076** Page **6** of **8** Rev: **00** Date: **4/11/07**

Data Sheet #: **SG076** Page **7** of **8** Rev: **00** Date: **4/11/07**

2111 Comprehensive Drive Aurora, Illinois 60505 Phone: 630-851-4722

Fax: 630-851-5040 **www.conwin.com**

| Revision | Revision Date | Note          |

|----------|---------------|---------------|

| 00       | 4/11/07       | Final Release |