## 0.6-4.5VIN, 1.8-5.25VOUT, 3.5µA, Low Input Voltage, High-Efficiency Boost + LDO

## **FEATURES**

- Combines Low-power Boost + Low Dropout Linear Regulator (LDO)

- ♦ Boost Regulator

- Input Voltage: 0.6V- 4.5VOutput Voltage: 1.8V- 5.25V

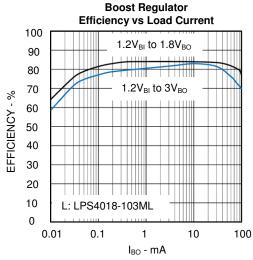

- Efficiency: Up to 84%

- No-Load Supply Current: 3.5μA

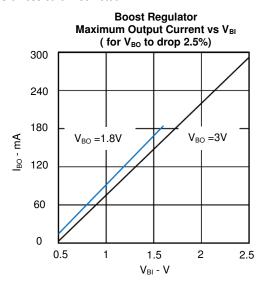

- Delivers >100mA at 1.8V<sub>BO</sub> from 1.2V<sub>BI</sub>

- Shutdown Control

- Anti-Crush Capability

- Prevents Input Voltage Collapse when powered with Weak/High Impedance power Sources

- Single-Inductor, Discontinuous Conduction Mode Scheme with Automatic Peak Current Adjustment

- ♦ LDO

- Adjustable LDO Output Voltage: 1.8V- 5V

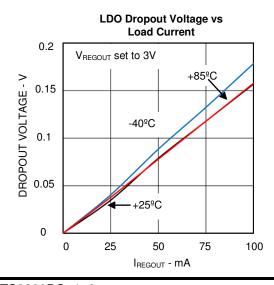

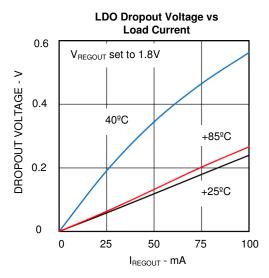

- Dropout Voltage: 255mV @ 100mA

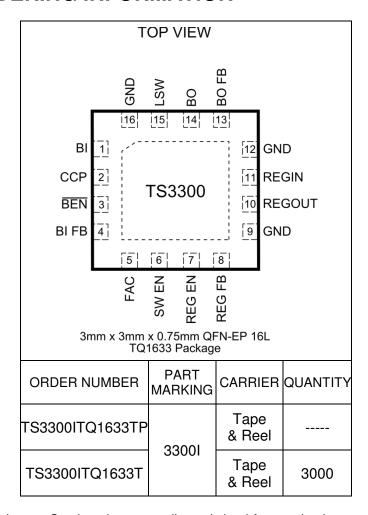

- ♦ 16-Pin, Low-Profile, Thermally-Enhanced 3mm x 3mm TQFN Package

## **APPLICATIONS**

Coin Cell-Powered Portable Equipment

Single Cell Li-ion or Alkaline Powered Equipment

Solar or Mechanical Energy Harvesting

Wireless Microphones

Wireless Remote Sensors

RFID Tags

Blood Glucose Meters

Personal Health-Monitoring Devices

### DESCRIPTION

The TS3300 is a 1st-generation Touchstone Semi power management product that combines a high-efficiency boost regulator and a low dropout linear regulator (LDO) in one package. The boost regulator operates from a supply voltage as low as 0.6V and can deliver at least 75mA at 1.2V<sub>BI</sub> to 3V<sub>BO</sub>, an industry first. The TS3300 LDO's input is connected to the output of the boost regulator, serving as a post-regulator for the boost, enabling a number of useful functions such as a buck-boost function. In power harvesting or peak load buffering applications, the LDO may post-regulate voltage buffered in a large capacitor or supercapacitor at boost's output. Finally, the LDO may be operated simply as an on/off load switch. The LDO can deliver up to 100mA output current at a dropout voltage of 255mV and reduce the ripple voltage out of the boost regulator by a factor of 3.

The TS3300's boost section includes an *anti-crush*<sup>TM</sup> feature to prevent the collapse of the input voltage to the boost regulator when the input is a weak (high impedance) source. If the input voltage drops below a determined voltage threshold (settable by a resistor divider), the boost regulator switching cycles are paused, effectively limiting the minimum input voltage. *Anti-crush*<sup>TM</sup> is useful in applications where a buffer capacitor at the boost's output can service burst loads, and the input source exhibits substantial source impedance (such as with an old battery, or at cold temperatures).

The TS3300 is fully specified over the -40 ℃ to +85 ℃ temperature range and is available in a low-profile, thermally-enhanced 16-pin 3x3mm TQFN package with an exposed back-side paddle.

Page 1

## **ABSOLUTE MAXIMUM RATINGS**

| BI to GND                   | 0.3V to V <sub>BO</sub> +0.1V |

|-----------------------------|-------------------------------|

| CCP                         | 0.3V to +2.5V                 |

| BEN to GND                  | 0.3V to +5.75V                |

| BI FB, REG FB, BO FB to GND | 0.3V to +5.75V                |

| SW EN, REG EN to GND        | 0.3V to +5.75V                |

| BO, REG OUT, REG IN to GND  | 0.3V to +5.75V                |

| LSW to GND                  | 0.3V to +5.75V                |

| Continuous Power Dissipation (T <sub>A</sub> = +70 °C) |                 |

|--------------------------------------------------------|-----------------|

| 16-Pin TQFN (Derate at 17.5mW/℃ above +70              | °C) 1398mW      |

| Operating Temperature Range                            | 40 ℃ to +85 ℃   |

| Storage Temperature Range                              | -65°C to +150°C |

| Lead Temperature (Soldering, 10s)                      | +300℃           |

Electrical and thermal stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to any absolute maximum rating conditions for extended periods may affect device reliability and lifetime.

## PACKAGE/ORDERING INFORMATION

Lead-free Program: Touchstone Semiconductor supplies only lead-free packaging.

Consult Touchstone Semiconductor for products specified with wider operating temperature ranges.

Page 2 TS3300DS r1p0

# **ELECTRICAL CHARACTERISTICS**

$V_{BI}$  = 1.2V,  $V_{BO}$  = 3V,  $V_{\overline{BEN}}$  = LOW,  $I_{BO}$  = 20mA, L = 10 $\mu$ H,  $C_{BO}$  = 22 $\mu$ F unless otherwise noted. Values are at  $T_A$  = 25 °C unless otherwise noted. See Note 1.

| PARAMETER                                 | SYMBOL                  | CONDITIONS                                                                 | MIN   | TYP   | MAX                   | UNITS |

|-------------------------------------------|-------------------------|----------------------------------------------------------------------------|-------|-------|-----------------------|-------|

|                                           |                         | BOOST REGULATOR                                                            |       |       |                       |       |

| Minimum Input Boost<br>Voltage            | $V_{BI\_MIN}$           | I <sub>BO</sub> = 0mA. T <sub>A</sub> =25°C                                |       | 0.6   | 0.75                  | V     |

| Maximum Input Boost<br>Voltage            | $V_{BI\_MAX}$           | Guaranteed by design                                                       | 4.5   |       |                       | V     |

| Output Boost Voltage<br>Range             | $V_{BO}$                |                                                                            | 1.8   |       | 5.25                  | V     |

| Current Measured at BO                    |                         | $I_{BO} = 0mA$ ,                                                           |       | 3.5   |                       | μΑ    |

| Current Measured at BI                    | $I_{B\_Q}$              | V <sub>BO FB</sub> = 0.6V<br>T <sub>A</sub> =25 ℃                          |       | 0.07  |                       | μΑ    |

| Current Measured at BO                    |                         | $I_{BO} = 0 \text{mA}, -40 \text{ °C} < T_A < +85 \text{ °C}$              |       |       | 6                     | μΑ    |

| Current Measured at BI                    |                         | $V_{BO FB} = 0.6V$                                                         |       |       | 0.9                   | μΑ    |

| Efficiency                                | Eff                     | $V_{BI}$ = 1.2V, $V_{BO}$ =1.8, $I_{BO}$ =30mA                             |       | 84    |                       | %     |

| Boost Shutdown Supply<br>Current          | I <sub>SHUTDOWN</sub>   | Measured at BI. $V_{BEN} = V_{BI}$ $V_{\overline{BEN}} = 0V$ $T_A = 25 °C$ |       |       | 100                   | nA    |

| Boost Feedback Voltage during operation   | $V_{BOFB}$              | Output voltage accuracy: ± 4%                                              | 0.489 | 0.505 | 0.521                 | V     |

| Boost Feedback Pin<br>Current             | I <sub>BO FB</sub>      |                                                                            |       | ±0.1  | ±1                    | nA    |

| Anti-Crush Feedback<br>Voltage            | V <sub>BI FB</sub>      | V <sub>BI</sub> ≥ 0.6V                                                     | 0.363 | 0.392 | 0.425                 | V     |

| Anti-Crush Feedback<br>Voltage Hysteresis | V <sub>BI FB_HYST</sub> |                                                                            |       | 50    |                       | mV    |

| Boost Enable Threshold                    | $V_{\overline{BEN}}$    | V <sub>IL</sub>                                                            | 0.2   |       | V <sub>BI</sub> -0.05 | V     |

| Boost Enable Hysteresis                   | V <sub>BEN_HYST</sub>   |                                                                            |       | 200   |                       | mV    |

| Inductor Peak Current                     | I <sub>PK</sub>         | No Load                                                                    | 365   |       |                       | mA    |

| Inductor Valley Current                   | l <sub>V</sub>          |                                                                            |       | 10    |                       | mA    |

| N-channel ON Resistance                   | Rds <sub>N-CH</sub>     |                                                                            |       | 0.27  |                       | Ω     |

| P-channel ON Resistance                   | $Rds_{P-CH}$            |                                                                            |       | 0.48  |                       | Ω     |

TS3300DS r1p0 Page 3 RTFDS

## **ELECTRICAL CHARACTERISTICS**

$V_{REGIN} = V_{BO} = 3V$ ,  $V_{REGOUT} = 1.8V$ ,  $V_{REG~EN} = HIGH$ ,  $I_{REGOUT} = 20mA$ ,  $C_{REGOUT} = 10\mu F$  unless otherwise noted. Values are at  $T_A = 25\,^{\circ}C$  unless otherwise noted. See Note 1.

| PARAMETER                             | SYMBOL                                 | CONDITIONS                                                                                                |                               | MIN                     | TYP  | MAX                      | UNITS    |

|---------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------|------|--------------------------|----------|

|                                       |                                        | LINEAR                                                                                                    | REGULATOR                     |                         |      |                          |          |

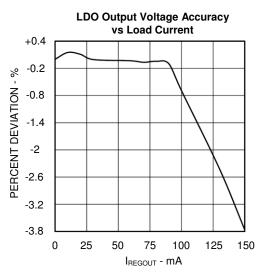

| DC Output Accuracy                    | V <sub>BEGOLIT</sub>                   | $2.3V \le V_{REGIN} \le 5V$ $0mA \le I_{REGOUT} \le 20mA$ $V_{REG FB} = 505mV$                            |                               |                         | 2.5  |                          | %        |

| ,                                     | 112001                                 |                                                                                                           | -40ºC ≤ T <sub>A</sub> ≤ 85°C | -3.5                    |      | 3.5                      | %        |

| Input Voltage Range                   | $V_{REGIN}$                            | Guaranteed by design                                                                                      |                               | 1.8                     |      | 5.25                     | V        |

| Output Voltage Range                  | $V_{REGOUT}$                           |                                                                                                           |                               | 1.8                     |      | 5                        | V        |

| Input Supply Current                  | I <sub>REGIN</sub>                     | I <sub>REGOUT</sub> = 0mA, V <sub>REG EN</sub> = V <sub>REGIN</sub>                                       |                               |                         | 0.4  | 1                        | μΑ       |

| Line Regulation                       | $\Delta V_{REGOUT} / \Delta V_{REGIN}$ | V <sub>REGOUT</sub> +0.5V ≤ V <sub>REGIN</sub> ≤ 5V                                                       |                               | -1                      |      | 1                        | %        |

| Load Regulation                       | $\Delta V_{REGOUT}$                    | $10\text{mA} \le I_{\text{REGOUT}} \le 20\text{mA}$<br>$0\text{mA} \le I_{\text{REGOUT}} \le 20\text{mA}$ |                               | -1                      |      | 1                        | %        |

| Load negulation                       | $\Delta I_{REGOUT}$                    |                                                                                                           |                               | -1.5                    |      | 1.5                      | %        |

| Drop Out Voltage                      | VDO                                    |                                                                                                           |                               |                         | 40   |                          | mV       |

| Output Current Limit                  | ICL                                    |                                                                                                           |                               |                         | 150  |                          | mA       |

| D 0 1 D : ::                          |                                        | C 22uE                                                                                                    | f = 10Hz                      |                         | -70  |                          | dB       |

| Power Supply Rejection Ratio          | PSRR                                   |                                                                                                           | f = 100Hz                     |                         | -50  |                          | dB       |

| Tidalo .                              |                                        | TREGOUT - TOOTHING                                                                                        | f = 1kHz                      |                         | -36  |                          | dB       |

| Startup Time                          | t <sub>STR</sub>                       |                                                                                                           |                               |                         |      | 1                        | ms       |

| Linear Regulator Enable               | V                                      | V <sub>IL</sub> (CMOS logic)                                                                              |                               |                         |      | 0.2 x V <sub>REGIN</sub> | <b>V</b> |

| Voltage                               | V <sub>REG EN</sub>                    | V <sub>IH</sub> (CMOS logic)                                                                              |                               | 0.8 xV <sub>REGIN</sub> |      |                          | >        |

| Linear Regulator Enable<br>Hysteresis | V <sub>REG EN_HYST</sub>               |                                                                                                           |                               |                         | 100  |                          | mV       |

| Enable Pin Current                    | I <sub>REG EN</sub>                    |                                                                                                           |                               |                         |      | 10                       | nA       |

| SWITCH Rdson                          | R <sub>sw</sub>                        | V <sub>SW EN</sub> = HIGH. Measured from REGIN to REGOUT                                                  |                               |                         | 0.9  | 1.2                      | Ω        |

| CMITOU Frable Valtage                 | V <sub>SW EN</sub>                     | V <sub>IL</sub> (CMOS logic)                                                                              |                               |                         |      | 0.2 x V <sub>REGIN</sub> | V        |

| SWITCH Enable Voltage                 |                                        | V <sub>IH</sub> (CMOS logic)                                                                              |                               | 0.8 xV <sub>REGIN</sub> |      |                          | V        |

| Regulator Feedback Pin<br>Current     | I <sub>REG FB</sub>                    |                                                                                                           |                               |                         | ±0.1 | ±1                       | nA       |

**Note 1:** All devices are 100% production tested at  $T_A = +25$  °C and are guaranteed by characterization for  $T_A = T_{MIN}$  to  $T_{MAX}$ , as specified.

Page 4 TS3300DS r1p0

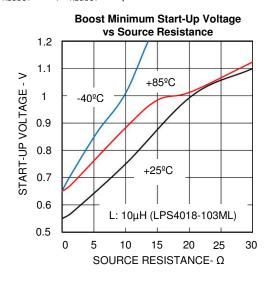

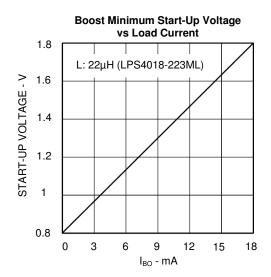

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{BI}=1.2V,\ V_{BO}=3V,\ V_{\overline{BEN}}=LOW,\ I_{BO}=0A,\ L=10\mu H\ (LPS4018-103ML),\ C_{BO}=22\mu F,\ C_{BI}=22\mu F,\ V_{REGIN}=V_{BO}=3V,\ V_{REGOUT}=1.8V,\ I_{REGOUT}=0A,\ C_{REGOUT}=10\mu F\ unless\ otherwise\ noted.$

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{BI}=1.2V,\ V_{BO}=3V,\ V_{\overline{BEN}}=LOW,\ I_{BO}=0A,\ L=10\mu H\ (LPS4018-103ML),\ C_{BO}=22\mu F,\ V_{REGIN}=V_{BO}=3V,\ V_{REGOUT}=1.8V,\ I_{REGOUT}=0A,\ C_{REGOUT}=10\mu F\ unless otherwise noted.$

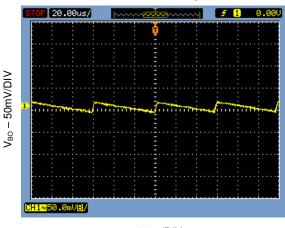

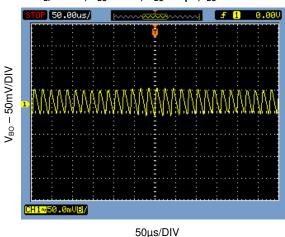

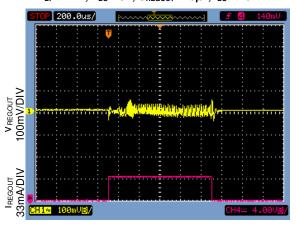

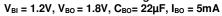

Boost Regulator Output Voltage Ripple  $V_{BI} = 1.2V$ ,  $V_{BO} = 1.8V$ ,  $C_{BO} = 22\mu F$ ,  $I_{BO} = 5mA$

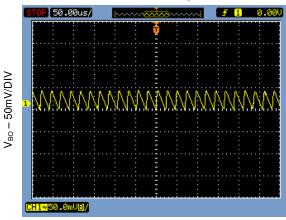

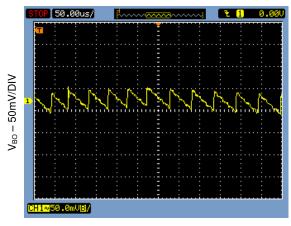

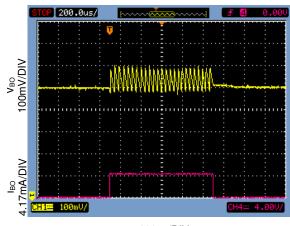

Boost Regulator Output Voltage Ripple  $V_{BI}$  = 1.2V,  $V_{BO}$  = 1.8V,  $C_{BO}$  = 22 $\mu$ F,  $I_{BO}$  = 40mA

20μs/DIV

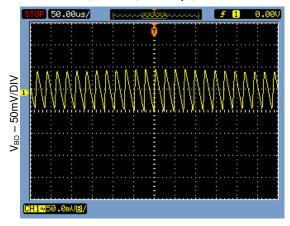

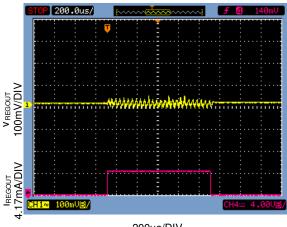

Boost Regulator Output Voltage Ripple  $V_{BI} = 1.2V$ ,  $V_{BO} = 3V$ ,  $C_{BO} = 22\mu F$ ,  $I_{BO} = 5mA$

50μs/DIV

50μs/DIV

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{BI}=1.2V,\ V_{BO}=3V,\ V_{\overline{BEN}}=LOW,\ I_{BO}=0A,\ L=10\mu H\ (LPS4018-103ML),\ C_{BO}=22\mu F,\ V_{REGIN}=V_{BO}=3V,\ V_{REGOUT}=1.8V,\ I_{REGOUT}=0A,\ C_{REGOUT}=10\mu F\ unless otherwise noted.$

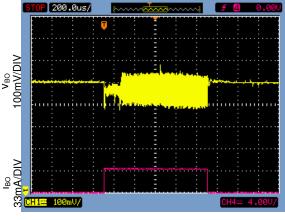

### **Boost Regulator Output Voltage Ripple** $V_{BI} = 1.2V$ , $V_{BO} = 3V$ , $C_{BO} = 22 \mu F$ , $I_{BO} = 80 mA$

50µs/DIV

### **Boost Regulator Load Step Response** $V_{BI} = 1.2V$ , $V_{BO} = 3V$ , $C_{BO} = 10\mu F$ , $I_{BO} = 40mA$

200μs/DIV

### **LDO Load Step Response** $V_{BI} = 1.2V$ , $V_{BO} = 3V$ , $C_{REGOUT} = 10 \mu F$ , $I_{BO} = 40 mA$

200µs/DIV

### **Boost Regulator Load Step Response** $V_{BI} = 1.2V$ , $V_{BO} = 3V$ , $C_{BO} = 10\mu F$ , $I_{BO} = 5mA$

200µs/DIV

### **LDO Load Step Response** $V_{BI} = 1.2V$ , $V_{BO} = 3V$ , $C_{REGOUT} = 10 \mu F$ , $I_{BO} = 5 mA$

200µs/DIV

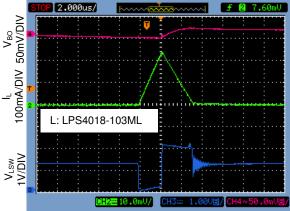

### **Boost Regulator Output Voltage Ripple, Inductor Current,** and LSW Voltage

2μs/DIV

TYPICAL PERFORMANCE CHARACTERISTICS  $V_{BI} = 1.2V, V_{BO} = 3V, V_{BEN} = LOW, I_{BO} = 0A, L = 10 \mu H (LPS4018-103ML), C_{BO} = 22 \mu F, C_{BI} = 22 \mu F, V_{REGIN} = V_{BO} = 3V, V_{REGOUT} = 1.8V, I_{REGOUT} = 0A, C_{REGOUT} = 10 \mu F unless otherwise noted. Values are at <math>T_A = 25 \, ^{\circ}\!\!\!\! \text{C}$  unless otherwise noted.

### **Boost Regulator Output Voltage Ripple, Inductor Current,** and LSW Voltage

$V_{BI} = 1.2V$ ,  $V_{BO} = 3V$ ,  $C_{BO} = 22\mu F$ ,  $I_{BO} = 40mA$ I<sub>L</sub> V<sub>BO</sub> 500mA/DIV 50mV/DIV L: LPS4018-103ML V<sub>LSW</sub>

2µs/DIV

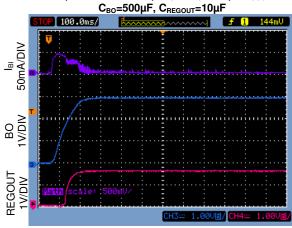

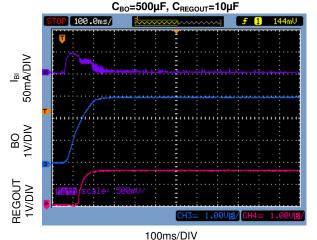

Large Output Capacitor Start-up with Anti-Crush at 0.9V  $V_{BI}$ =1.2V, ESR of  $V_{BI}$ =10 $\Omega$ ,  $V_{BO}$ = $V_{REGIN}$ =3V,  $V_{REGOUT}$ =1.8V,

100ms/DIV

Page 8 TS3300DS r1p0

# **PIN FUNCTIONS**

| PIN | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                  |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | BIN    | Boost Input. Bypass this pin with a 22µF ceramic capacitor in close proximity to the TS3300.                                                                                                                                                                                                                                                                              |

| 2   | CCP    | Charge Pump Capacitor. Place a 3.3nF capacitor between this pin and GND                                                                                                                                                                                                                                                                                                   |

| 3   | BEN    | Boost Enable (active low). To enable the TS3300, connect this to GND. To disable the TS3300, set the voltage to greater than $V_{\text{BI}}$ – 50mV.                                                                                                                                                                                                                      |

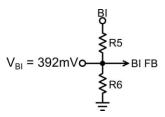

| 4   | BI FB  | Boost Input Feedback for Anti-Crush Voltage Setting. The BI FB pin voltage is 392mV. To set the anti-crush voltage, refer to the <i>Applications Information</i> section and to Figure 7.                                                                                                                                                                                 |

| 5   | FAC    | Factory use only. Do not connect to GND or VDD. Leave open.                                                                                                                                                                                                                                                                                                               |

| 6   | SW EN  | Switch Enable. When SW EN is high and REG EN is low, the internal FET/SWITCH connects the LDO output to the LDO input. The internal FET has an Rds <sub>ON</sub> = $1.2\Omega$ . Refer to Table 1.                                                                                                                                                                        |

| 7   | REG EN | LDO Regulator Enable. When REG EN is high and SW EN is low, the LDO is under normal operation. Refer to Table 1.                                                                                                                                                                                                                                                          |

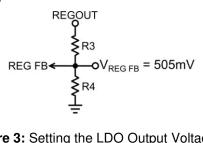

| 8   | REG FB | LDO Regulator Output Feedback. The REG FB pin voltage is 505mV. REG FB coupled with a voltage divider circuit sets the LDO output voltage. Refer to Figure 3.                                                                                                                                                                                                             |

| 9   | GND    | Ground. Connect this pin to the analog ground plane                                                                                                                                                                                                                                                                                                                       |

| 10  | REGOUT | LDO Regulator Output Voltage. A minimum output capacitance of $10\mu F$ is recommended to be placed from this pin to GND. To set the LDO output voltage, use a voltage divider circuit along with the REG FB pin as shown in Figure 3.                                                                                                                                    |

| 11  | REGIN  | LDO Regulator Input/Boost Output. REGIN should always be connected to the boost regulator output voltage pin BO. BO is always the input to the LDO. Do not apply an external supply voltage to this pin.                                                                                                                                                                  |

| 12  | GND    | Ground. Connect this pin to the analog ground plane.                                                                                                                                                                                                                                                                                                                      |

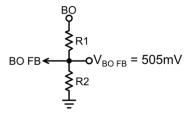

| 13  | BO FB  | Boost Output Feedback. The BO FB pin voltage is 505mV. BO FB coupled with a voltage divider circuit sets the boost regulator output voltage. Refer to Figure 2.                                                                                                                                                                                                           |

| 14  | ВО     | Boost Regulator Output Voltage. A minimum output capacitance of 10μF is recommended to be placed from this pin to GND. To set the boost regulator output voltage, use a voltage divider circuit along with the BO FB pin. Refer to Figure 2.                                                                                                                              |

| 15  | LSW    | Coil is a low-ESR, high-saturation current, shielded inductor. A 10µH inductor is recommended for most applications and is to be placed from this pin to the input of the boost regulator BI. Furthermore, there should exist at least an 8% margin between the saturation current of the inductor and the peak inductor current for a given set of operating conditions. |

| 16  | GND    | Ground. Connect this pin to the analog ground plane.                                                                                                                                                                                                                                                                                                                      |

| EP  | _      | For best electrical and thermal performance, connect exposed paddle to GND.                                                                                                                                                                                                                                                                                               |

TS3300DS r1p0 Page 9 RTFDS

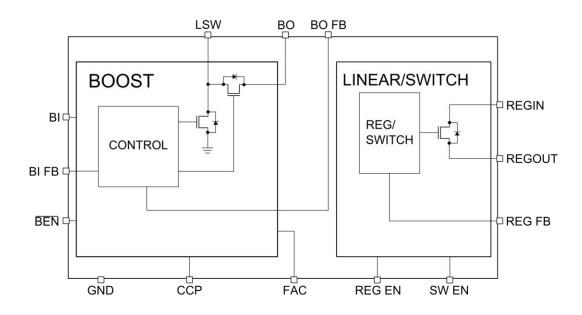

### **BLOCK DIAGRAM**

## THEORY OF OPERATION

The TS3300 is a power management product that combines a high-efficiency boost regulator and a linear regulator into one package. It is the industry's 1<sup>st</sup> boost regulator + linear regulator where the boost regulator can operate from supply voltages as low as 0.6V and can deliver at least 75mA at  $1.2V_{BI}$  and 3V<sub>BO</sub>. Under no-load conditions, the boost regulator idles at 3.5µA. The internal, low-dropout linear regulator is driven by the output of the boost regulator. It can deliver up to 100mA output current at a dropout voltage of 255mV and reduce the ripple voltage out of the boost regulator by a factor of 3.

### **BOOST REGULATOR**

At start-up, an internal low voltage oscillator in the start-up control circuitry drives the gate of the internal FET to charge the load capacitor. Once the output voltage reaches approximately 1.1V, the main control circuitry starts to operate.

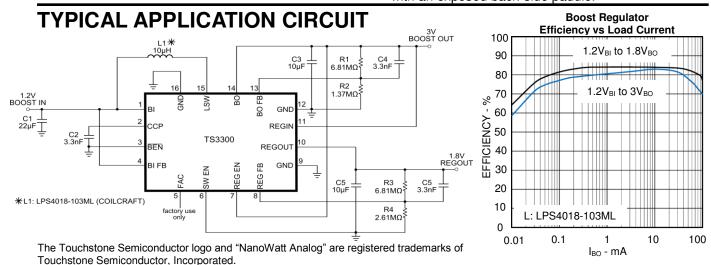

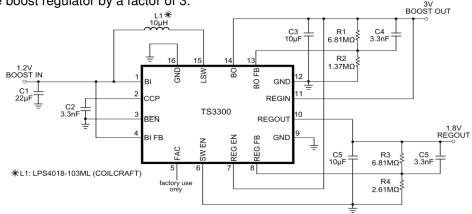

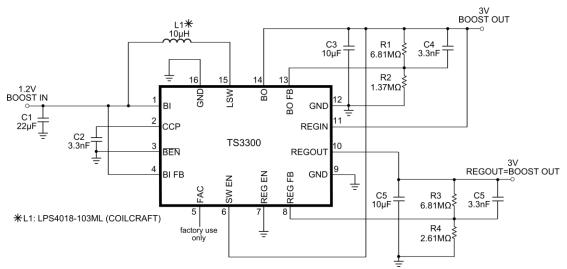

With an adjustable peak inductor current, the TS3300 can provide up to 84% efficiency with a 1.2V<sub>BI</sub> and 3V<sub>BO</sub>. Refer to Figure 1. The input and output supply voltage range for the boost regulator is from 0.6V to 4.5V and 1.8V to 5.25V, respectively.

Figure 1: 1.2V Input to 3V Boost Regulator Output Voltage and to 1.8V LDO Output Voltage Circuit

Page 10 TS3300DS r1p0

The output voltage can be set via a voltage divider circuit as shown in Figure 2. The output feedback (BO FB) pin is 505mV. It is recommended to use

Figure 2: Setting the Boost Output Voltage with a Voltage Divider

large resistor values to minimize additional current draw at the output. Resistors values less than  $8M\Omega$ are recommended. Using the following equation to solve for R1 for a given R2 value, the output voltage can be set:

$$R1 = \frac{(V_{BO} - 0.505)R2}{0.505}$$

To set a 3V output voltage with R2 =  $1.37M\Omega$ , R1 is calculated to be  $6.77M\Omega$ . A 1% standard resistor value of  $6.81M\Omega$  can be selected. This results in an output voltage of 3.02V.

A shutdown (BEN) pin is also available to shutdown the boost regulator. The boost regulator is in shutdown mode when BEN is LOW and supply current reduces to 0.1µA.

### **LDO Post-Regulator**

The input and output supply voltage range for the LDO is from 2.3V to 5.25V and 1.8V to 5V, respectively, where the LDO input is driven by the output of the boost regulator. The output voltage can be set via a voltage divider circuit as shown in Figure 3.

Figure 3: Setting the LDO Output Voltage with a Voltage Divider

The output feedback (REG FB) pin is 505mV. It is recommended to use the largest resistor values to minimize additional current draw at the output. Using the following equation to solve for R3 for a given R4 value, the output voltage can be set:

$$R3 = \frac{(V_{REGOUT} - 0.505)R4}{0.505}$$

To set a 1.8V output voltage with R4 =  $2.61M\Omega$ , R3 is calculated to be 6.69MΩ. A 1% standard resistor value of  $6.81M\Omega$  can be selected. This results in an output voltage of 1.82V.

Figure 4: TS3300 LDO FET/Switch Enabled Circuit

TS3300DS r1p0 Page 11

The LDO was designed to operate in conjunction with the boost regulator where the output of the boost regulator is connected to the input to the linear regulator. The LDO can provide an output voltage based on the resistor divider circuit as shown in Figure 3 or the output voltage can be set to the input voltage where the internal switch/FET is fully enhanced. Table 1 summarizes the settings for pins REG EN and SW EN. Figure 4 shows the configuration where the internal switch/FET is fully enhanced (SW EN =high, REG EN = low) so the boost output is equal to the LDO output. The LDO can be shutdown by connecting the REF FB pin to BO when SW EN = low and REG EN = high.

| SW EN | REG EN  | CONDITION                          | FUNCTION                |                 |

|-------|---------|------------------------------------|-------------------------|-----------------|

| low   | high    | Connect<br>REG EN pin<br>to BO pin | LDO Normal<br>Operation |                 |

| IOW   | Connect | REG FB                             | REG FB pin              | LDO<br>Shutdown |

| high  | low     | Connect<br>SW EN pin<br>to BO pin  | Internal FET<br>Hard-on |                 |

Table 1. LDO REG EN and SW EN Settings

## APPLICATIONS INFORMATION

### **Inductor Selection**

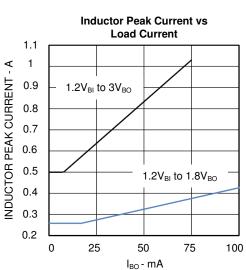

A low ESR, shielded 10µH inductor is recommended for most applications and provides the best compromise between efficiency and size. A low loss ferrite and low dc resistance (DCR) inductor is best for optimal efficiency. Furthermore, there should exist at least an 8% margin between the saturation current of the inductor and the peak inductor current for a given set of operating conditions. Table 2 provides a list of inductor manufactures. Refer to the Inductor Peak Current vs Load Current plot in the "Typical Performance Characteristics" section. This plot

| Inductors      |                       |  |  |

|----------------|-----------------------|--|--|

| Supplier       | Website               |  |  |

| Coilcraft      | www.coilcraft.com     |  |  |

| Murata         | www.murata.com        |  |  |

| Sumida         | www.sumida.com        |  |  |

| Capacitors     |                       |  |  |

| Taiyo<br>Yuden | www.t-yuden.com       |  |  |

| Murata         | www.murata.com        |  |  |

| AVX            | www.avxcorp.com       |  |  |

| TDK            | www.component.tdk.com |  |  |

Table 2. Inductor and Capacitor Manufactures

shows how the inductor peak current varies with load current with a LPS4018-103ML inductor from Coilcraft.

### Input and Output Capacitor Selection

For the boost regulator, a low ESR ceramic input and output capacitor of at least 10µF is recommended to be placed as close as possible to the BI and BO pin. Output voltage ripple can be reduced by increasing the value of the output capacitor while providing improved transient response. Ceramic capacitors with X5R dielectric are recommended.

For the LDO, a low ESR ceramic input and output capacitor of at least 10µF is recommended to be placed as close as possible to the REG OUT pin. Refer to Table 2 for a list of inductor and capacitor manufacturers.

### **Buck-Boost Function**

The TS3300 can act as a buck-boost device. For instance, if two 1.5V alkaline cells are used to power the TS3300, the boost output voltage (V<sub>BO</sub>) can be set to 5V and the LDO output voltage (V<sub>REGOUT</sub>) can be set to 2.5V. The output voltage for the boost regulator and the LDO can be set according to Figure 2 and 3, respectively.

### **Boost Input Anti-Crush<sup>™</sup> Feature**

The TS3300 includes an anti-crush<sup>TM</sup> feature to prevent the collapse of the input voltage to the boost regulator when the input is a weak (high impedance) source. If the input voltage drops below a determined voltage threshold (settable by a resistor divider), the boost regulator switching cycles are paused, effectively limiting the minimum input voltage. Anti-crush  $^{TM}$  is useful in applications where a buffer capacitor at the boost's output can service burst loads, and the input source exhibits substantial source impedance (such as with an old battery, or at cold temperatures).

To set the anti-crush woltage, a feedback pin (BI FB) in conjunction with a voltage divider circuit can be implemented as shown in Figure 7. The feedback pin voltage is 392mV. It is recommended to use large resistor values to minimize additional current draw at the input.

Page 12 TS3300DS r1p0

**Figure 7:** Setting the Anti-Crush<sup>TM</sup> Voltage with a Voltage Divider

Using the following equation to solve for R5 for a given R6 value, the output voltage can be set:

$$R5 = \frac{(V_{ANTI-CRUSH}^{TM} - 0.392)R6}{0.392}$$

To set a 0.8V output voltage with R6 = 1.37M $\Omega$ , R5 is calculated to be 1.42M $\Omega$ . A 1% standard resistor value of 1.37M $\Omega$  can be selected. This results in an anti-crush voltage of 784mV. The anti-crush voltage is to be set above the minimum input voltage specification of the TS3300.

Figure 5 shows a scope capture of the anti-crush<sup>TM</sup> feature in action at start-up under a heavy capacitive

Large Output Capacitor Start-up with Anti-Crush<sup>TM</sup> at 0.9V  $V_{BI}$ =1.2V, ESR of  $V_{BI}$ =10 $\Omega$ ,  $V_{BO}$ = $V_{REGIN}$ =3V,  $V_{REGOUT}$ =1.8V,

Figure 5: Using the Anti-Crush<sup>™</sup> Feature under a Heavy Capacitive Load (500μF) and a 10Ω Boost Input Source Impedance at Start-up

load of  $500\mu F$  and an input source impedance of  $10\Omega$ . A high source impedance is typical of a weak battery source. The measurement was performed with the anti-crush voltage set to 0.9V. The purple, blue, and pink trace represent the input current, boost output voltage, and LDO output voltage, respectively. At start-up, the current rises up to 50mA and drops to approximately 30mA for approximately 40ms in order to charge the output capacitor. At this point, the voltage to the input of the TS3300 is 0.9V until the boost output achieves regulation and in turn, the LDO output voltage achieves regulation as well.

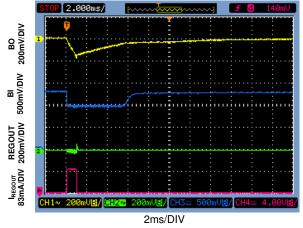

Figure 6 shows a scope capture of the load step response. The measurement was performed with the anti-crush  $^{\text{TM}}$  voltage set to 0.9V. As the output of the LDO is pulsed with a 100mA load every 100ms for 1ms as shown by the pink curve, the input voltage after a battery impedance of  $10\Omega$  drops from 1.2V to 0.9V as shown by the blue curve and the boost output voltage drops by only 160mV as shown by the yellow curve. The TS3300 quickly replenishes the  $500\mu F$  capacitor and the output of the boost regulator returns to 3V. Note that the LDO remains regulated and is unaffected by the load step.

Load Step Response with Anti-Crush<sup>TM</sup> at 0.9V  $V_{Bi}$ =1.2V, ESR of  $V_{Bi}$ =10 $\Omega$ ,  $V_{BO}$ = $V_{REGIN}$ =3V,  $V_{REGOUT}$ =1.8V,  $C_{BO}$ =500 $\mu$ F,  $C_{REGOUT}$ =10 $\mu$ F,  $I_{REGOUT}$ =100mA pulse

**Figure 6:** Using the Anti-Crush<sup>TM</sup> Feature to Maintain Regulation of the Boost Regulator and LDO Output Voltage

TS3300DS r1p0 Page 13

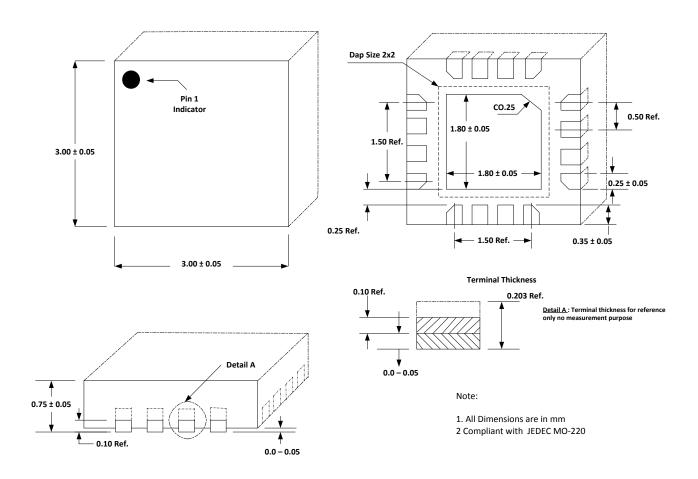

## PACKAGE OUTLINE DRAWING

## 16-Pin TQFN33 Package Outline Drawing

(N.B., Drawings are not to scale)

Information furnished by Touchstone Semiconductor is believed to be accurate and reliable. However, Touchstone Semiconductor does not assume any responsibility for its use nor for any infringements of patents or other rights of third parties that may result from its use, and all information provided by Touchstone Semiconductor and its suppliers is provided on an AS IS basis, WITHOUT WARRANTY OF ANY KIND. Touchstone Semiconductor reserves the right to change product specifications and product descriptions at any time without any advance notice. No license is granted by implication or otherwise under any patent or patent rights of Touchstone Semiconductor. Touchstone Semiconductor assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using Touchstone Semiconductor components. To minimize the risk associated with customer products and applications, customers should provide adequate design and operating safeguards. Trademarks and registered trademarks are the property of their respective owners.