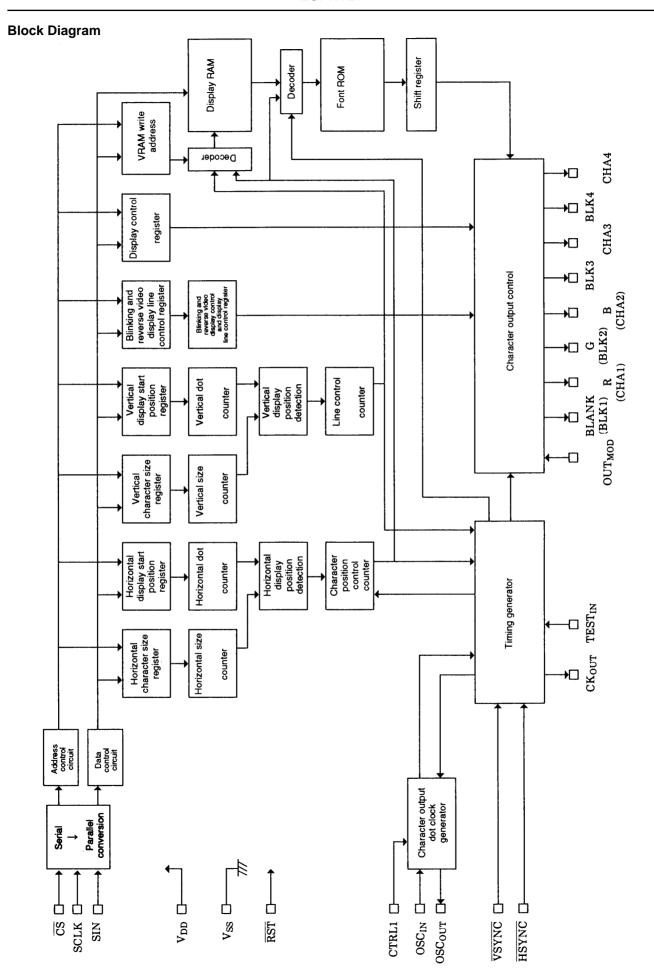

# Camcorder On-Screen Display LSI

#### Overview

The LC74772V is a CMOS LSI that implements on-screen display for camcorders. It displays characters and patterns in a camcorder viewfinder under microprocessor control. The LC74772V displays a  $12 \times 18$  dot font with 256 characters.

#### **Features**

- Screen format: 12 lines × 24 characters (up to 288 characters)

- Number of characters displayed: Up to 288 characters

- Character format: 12 (horizontal) × 18 (vertical) dots

- Number of characters in font: 256 characters

- Character sizes: Normal and double, specified in line units

- · Display start position

- Horizontal: 64 positionsVertical: 64 positions

- Character reverse video function: Individual characters can be displayed in reverse video.

- Types of blinking: Two types with periods of 1.0 and 0.5 seconds, specifiable on a per character basis. (Blinking has a 60% display on duty.)

(Four divisors: 1/25, 1/30, 1/50, 1/60)

- Outputs: R, G, B plus 2 output systems

Or: 4 output systems (character data and blanking data: 4 outputs each)

- External control input: 8-bit serial data input format.

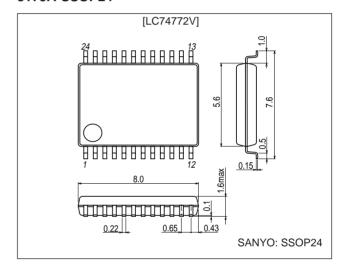

#### **Package Dimensions**

unit: mm

#### 3175A-SSOP24

### **Specifications**

#### **Absolute Maximum Ratings**

| Parameter                   | Symbol           | Conditions                                                 | Ratings                          | Unit |

|-----------------------------|------------------|------------------------------------------------------------|----------------------------------|------|

| Supply voltage              | V <sub>DD</sub>  | V <sub>DD</sub>                                            | $V_{SS} - 0.3$ to $V_{SS} + 7.0$ | V    |

| Input voltage               | V <sub>IN</sub>  | All input pins                                             | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ | V    |

| Output voltage              | V <sub>OUT</sub> | CK <sub>OUT</sub> , CHA4, BLK4, CHA3, BLK3, B, G, R, BLANK | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ | V    |

| Allowable power dissipation | Pd max           | Ta = 25°C                                                  | 300                              | mW   |

| Operating temperature       | Topr             |                                                            | -30 to +70                       | °C   |

| Storage temperature         | Tstg             |                                                            | -40 to +125                      | °C   |

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

# Allowable Operating Ranges at $Ta = -30 \text{ to } +70^{\circ}\text{C}$

| Parameter                | Symbol Conditions |                                                                                                                       |                       | Unit |                       |       |

|--------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| Farameter                |                   |                                                                                                                       | min                   | typ  | max                   | Utill |

| Supply voltage           | $V_{DD}$          | $V_{DD}$                                                                                                              | 2.7                   | 5.0  | 5.5                   | V     |

| Input high-level voltage | V <sub>IH</sub>   |                                                                                                                       | 0.8 V <sub>DD</sub>   |      | V <sub>DD</sub> + 0.3 | V     |

| Input low-level voltage  | V <sub>IL</sub>   | $\frac{\text{CTRL1, TEST_{IN}, \overline{CS}, SCLK, SIN, OUT_{MOD}, \overline{HSYNC},}{\text{VSYNC, }\overline{RST}}$ | V <sub>SS</sub> - 0.3 |      | 0.2 V <sub>DD</sub>   | V     |

| Oscillator frequency     | Fosc              | OSC <sub>IN</sub> , OSC <sub>OUT</sub> (LC oscillator)                                                                | 6                     | (8)  | 10                    | MHz   |

# Electrical Characteristics at Ta = -30 to $+70^{\circ}$ C, unless otherwise specified $V_{DD}$ = $5~\mathrm{V}$

| Parameter                 | Cymbol          | Symbol Conditions -                                                                                                                                          |                     | Ratings |                     |      |  |  |

|---------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|---------------------|------|--|--|

| Farameter                 | Symbol          |                                                                                                                                                              |                     | typ     | max                 | Unit |  |  |

| Output high-level voltage | V <sub>OH</sub> | $\rm CK_{OUT}$ , CHA4, BLK4, CHA3, BLK3, B, G, R, BLANK: $\rm V_{DD} = 5.5$ to $4.5$ V ( $\rm V_{DD} = 4.4$ to $2.7$ V), $\rm I_{OH} = -1.0$ mA ( $-0.5$ mA) | 0.9 V <sub>DD</sub> |         |                     | ٧    |  |  |

| Output low-level voltage  | V <sub>OL</sub> | $V_{DD} = 5.5$ to $4.5$ V ( $V_{DD} = 4.4$ to $2.7$ V), $I_{OL} = 1.0$ mA ( $0.5$ mA)                                                                        |                     |         | 0.1 V <sub>DD</sub> | ٧    |  |  |

| Input current             | I <sub>IH</sub> |                                                                                                                                                              |                     |         | 1                   | μA   |  |  |

|                           | I <sub>IL</sub> | CTRL1, TEST <sub>IN</sub> , HSYNC, VSYNC: V <sub>IN</sub> = V <sub>SS</sub>                                                                                  | -1                  |         |                     | μΑ   |  |  |

| Operating current drain   | I <sub>DD</sub> | V <sub>DD</sub> pin; all outputs open, LC oscillator: 8 MHz                                                                                                  |                     |         | 10                  | mA   |  |  |

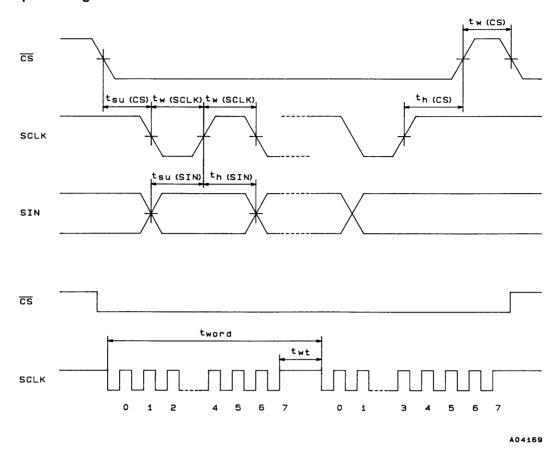

# Timing Characteristics at Ta = –30 to +70°C, $V_{DD}$ = 5 $\pm$ 0.5 V

| Parameter                  | Symbol                | Symbol Conditions                |     | Ratings |     |      |  |  |

|----------------------------|-----------------------|----------------------------------|-----|---------|-----|------|--|--|

| Farameter                  | Symbol                |                                  | min | typ     | max | Unit |  |  |

| Minimum input pulse width  | t <sub>W (SCLK)</sub> | SCLK                             | 200 |         |     | ns   |  |  |

| willimum input puise width | t <sub>W (CS)</sub>   | CS (the period that CS is high)  | 1   |         |     | μs   |  |  |

| Data setup time            | t <sub>SU (CS)</sub>  | CS                               | 200 |         |     | ns   |  |  |

| Data setup time            | t <sub>SU (SIN)</sub> | SIN                              | 200 |         |     | ns   |  |  |

| Data hold time             | t <sub>h (CS)</sub>   | CS                               | 2   |         |     | μs   |  |  |

| Data Hold time             | t <sub>h (SIN)</sub>  | SIN                              | 200 |         |     | ns   |  |  |

| One-word write time        | t <sub>word</sub>     | The time to write 8 bits of data | 4.2 |         |     | μs   |  |  |

| One-word write time        | t <sub>wt</sub>       | The RAM data write time          | 1   |         |     | μs   |  |  |

### **Serial Data Input Timing**

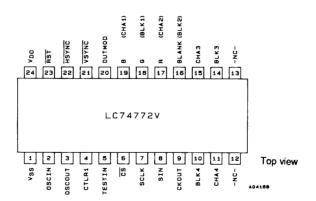

### **Pin Assignment**

The signal names in parentheses indicate the output pin functions when 4-system output mode is used.

### **Pin Functions**

| 1 2 | V <sub>SS</sub>    | Ground                                |                                                                                                                                 |

|-----|--------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 2   |                    | O O O O O O O O O O O O O O O O O O O | Ground connection                                                                                                               |

|     | OSCIN              | I C assillator                        | Connections for the coil and capacitor that form the oscillator that generates the character                                    |

| 3   | OSC <sub>OUT</sub> | LC oscillator                         | output horizontal dot clock.                                                                                                    |

| 4   | CTRL1              | Clock input control                   | Control input that switches between LC oscillator mode and clock input mode Low: LC oscillator mode, high: clock input mode     |

| 5   | TEST <sub>IN</sub> | Test control input                    | Test mode control input (The IC operates in test mode when this input is high.)                                                 |

| 6   | CS                 | Enable input                          | Serial data input enable input<br>Low: active (This input has hysteresis characteristics.)                                      |

| 7   | SCLK               | Clock input                           | Serial data input clock input (This input has hysteresis characteristics.)                                                      |

| 8   | SIN                | Data input                            | Serial data input (This input has hysteresis characteristics.)                                                                  |

| 9   | CK <sub>OUT</sub>  | Clock output                          | LC oscillator clock monitor output This signal is output when RST is low.                                                       |

| 10  | BLK4               | Blanking signal output                | Blanking signal output (system 2) Functions as the system 4 blanking data signal output in 4-system mode.                       |

| 11  | CHA4               | Character data output                 | Character data signal output (system 2) Functions as the system 4 character data signal output in 4-system mode.                |

| 12  | NC                 | Unused                                | Must be left open or tied to ground in normal operation.                                                                        |

| 13  | NC                 | Unused                                | Must be left open or tied to ground in normal operation.                                                                        |

| 14  | BLK3               | Blanking signal output                | Blanking signal output (system 1) Functions as the system 3 blanking data signal output in 4-system mode.                       |

| 15  | CHA3               | Character data output                 | Character data signal output (system 1) Functions as the system 3 character data signal output in 4-system mode.                |

| 16  | BLANK              | Blanking signal output                | Blanking signal output (blanking signal for RGB output) Functions as the system 2 blanking data signal output in 4-system mode. |

| 17  | R                  | Character data output                 | Character data (R) signal output Functions as the system 2 character data signal output in 4-system mode.                       |

| 18  | G                  | Character data output                 | Character data (G) signal output Functions as the system 1 blanking data signal output in 4-system mode.                        |

| 19  | В                  | Character data output                 | Character data (B) signal output Functions as the system 1 character data signal output in 4-system mode.                       |

| 20  | OUT <sub>MOD</sub> | Output control input                  | Control input that switches between RGB output and 4-system output Low: RGB output, high 4-system output                        |

| 21  | VSYNC              | Vertical synchronizing signal input   | Vertical synchronizing signal input (This input has hysteresis characteristics.)                                                |

| 22  | HSYNC              | Horizontal synchronizing              | Horizontal synchronizing signal input (This input has hysteresis characteristics.) signal input                                 |

| 23  | RST                | Reset input                           | System reset signal input (This input has hysteresis characteristics.)                                                          |

| 24  | $V_{DD}$           | Power supply                          | Power supply connection (+5 V)                                                                                                  |

Note: 1. Built-in pull-up resistors can be specified for inclusion in the  $\overline{CS}$  (pin 6), SCLK (pin 7), SIN (pin 8), and  $\overline{RST}$  (pin 23) pins as mask options.

2. In clock input mode (when CTRL1 is high), the function that holds the OSC<sub>IN</sub> (pin 2) pin high during an oscillator reset is stopped.

#### **Display Control Commands**

The display control commands have an 8-bit serial input format. Data is input LSB first.

### **Display Control Command Table**

|                                                                  |    |       |         | First | byte         |              |             |            |            |            |            | Secon       | d byte     |            |             |            |

|------------------------------------------------------------------|----|-------|---------|-------|--------------|--------------|-------------|------------|------------|------------|------------|-------------|------------|------------|-------------|------------|

| Command                                                          |    | Comma | nd code | )     | Data         |              |             | Data       |            |            |            |             |            |            |             |            |

|                                                                  | D7 | D6    | D5      | D4    | D3           | D2           | D1          | D0         | D7         | D6         | D5         | D4          | D3         | D2         | D1          | D0         |

| COMMAND 0<br>System setup 1                                      | 0  | 0     | 0       | 0     | RST<br>SYS   | RAM<br>CLR   | OSC         | TST<br>MOD | _          | _          | <u> </u>   | <u> </u>    | -          | <u> </u>   | <u> </u>    | <u> </u>   |

| COMMAND 1<br>System setup 2                                      | 0  | 0     | 0       | 1     | CSYN<br>MOD  | 1 -          | CLK<br>MOD1 | _          | _          | <u> </u>   | _          | <u> </u>    | _          | _          | <u> </u>    | _          |

| COMMAND 2<br>Input control setup                                 | 0  | 0     | 1       | 0     |              | HSYN<br>POLT | DATA        | ART<br>FMT | _          | <u> </u>   | _          | <u> </u>    | _          | _          | <u> </u>    | _          |

| COMMAND 3<br>General-purpose port control                        | 0  | 0     | 1       | 1     | PORT<br>SET  | OUT<br>P11   | OUT<br>P10  | OUT<br>P9  | _          | <u> </u>   | _          | <u> </u>    | _          | _          | <u> </u>    | _          |

| COMMAND 4 Display operation control: reverse video and blinking  | 0  | 1 1   | 0       | 0     | RVS<br>ON    | BLK<br>ON    | BLK         | BLK<br>0   | _          | -<br>-     | -<br>-     | -<br>-<br>- | _          | -          | -<br>-<br>- | -          |

| COMMAND 5<br>Display control: on/off settings<br>for each output | 0  | 1 1   | 0       | 1     | DSP<br>4     | DSP 3        | DSP         | DSP<br>1   | _          | -          | -          | -           | _          | -          | -           | -          |

| COMMAND 6<br>Output control: systems 3 and 4                     | 0  | 1 1   | 1 1     | 0     | DSPF<br>SL34 |              | DSP<br>GSG  | DSP<br>BSG | _          | <u> </u>   | <u> </u>   | <u> </u>    | -          | <u> </u>   | <u> </u>    | <u> </u>   |

| COMMAND 8<br>Display control: border                             | 1  | 0     | 0       | 0     | 0            | BKC<br>R     | BKC<br>G    | BKC<br>B   | BKO4<br>F1 | BKO4<br>F0 | BKO3<br>F1 | BKO3<br>F0  | BKO2<br>F1 | BKO2<br>F0 | BKO1<br>F1  | BKO1<br>F0 |

| COMMAND 9<br>Display start position                              | 1  | 0     | 0       | 1     | VP5          | VP4          | VP3         | VP2        | VP1        | VP0        | HP5        | HP4         | HP3        | HP2        | HP1         | HP0        |

| COMMAND 10<br>Display line control                               | 1  | 0     | 1       | 0     | LNF<br>SZ    | LNF<br>OT4   | LNF<br>OT3  | LN<br>SEL  | 0          | 0          | LIN<br>126 | LIN<br>115  | LIN<br>104 | LIN<br>93  | LIN<br>82   | LIN<br>71  |

| COMMAND 11<br>RAM write address                                  | 1  | 0     | 1       | 1     | VADR<br>3    | VADR<br>2    | VADR<br>1   | VADR<br>0  | 0          | 0          | 0          | HADR<br>4   | HADR<br>3  | HADR<br>2  | HADR<br>1   | HADR<br>0  |

| COMMAND 14<br>Display RAM setup data                             | 1  | 1 1   | 1 1     | BLK   | RV           | ¦ R          | G           | В          | C7         | C6         | C5         | C4          | СЗ         | C2         | C1          | C0         |

|                                                                  | 1  |       |         |       |              |              |             |            |            |            | 2          |             |            |            |             |            |

- ① Command code: (These 4 bits in the first byte identify the command.)

Command 14 is recognized by the upper 3 bits.

- ② Command data: (These bits specify the data for each command.)

- For commands 0 through 7, 8 bits of data are read in.

- For commands 8 through 14, 16 bits of data are read in.

- If the command 2 data-1 bit (DATAFMT) was set to 1, after the first byte of a command 14 is read in, the system goes to continuous transfer mode for reading in a series of following bytes.

Note: 1. If the  $\overline{\text{CS}}$  pin is set high, the command state is set to the command 0 (system control setup) state.

2. If a system reset is executed from the  $\overline{\text{RST}}$  pin or by a command reset, the command register is set tot 0.

#### ① COMMAND 0 (System control setup 1)

#### First byte

| B40. B45   | 5             |       | Register content                                                  |                                                                                  |  |  |

|------------|---------------|-------|-------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|

| DA0 to DA7 | Register name | State | Function                                                          | Note                                                                             |  |  |

| 7          | _             | 0     |                                                                   |                                                                                  |  |  |

| 6          | _             | 0     | Command 0 identification code                                     |                                                                                  |  |  |

| 5          | _             | 0     | Command o identification code                                     |                                                                                  |  |  |

| 4          | _             | 0     |                                                                   |                                                                                  |  |  |

| 3          | RST           |       | Normal operation                                                  | If $\overline{\text{CS}}$ is low, the reset is executed, but if                  |  |  |

| 3          | SYS           | 1     | System reset                                                      | CS is high this command will be exclude                                          |  |  |

| 2          | RAM           | 0     | Normal operation                                                  | The VRAM clear operation is not executed when the oscillator                     |  |  |

| 2          | CLR           | 1     | Normal operation VRAM clear (All data is set to FE (hexadecimal)) | is stopped.                                                                      |  |  |

| 1          | osc           | 0     | The LC oscillator operating state is maintained.                  | Valid when the display is off. VRAM write is not possible when the oscillator is |  |  |

|            | STP           | 1     | The LC oscillator is stopped.                                     | stopped.                                                                         |  |  |

| 0          | TST           | 0     | Normal operation                                                  | Illegal setting. This bit must always be set to 0.                               |  |  |

|            | MOD           | 1     | Test mode                                                         |                                                                                  |  |  |

Note: This register is set to 0 on a reset (either by the  $\overline{\text{RST}}$  pin or by a command reset).

#### Notes on command settings

- RSTSYS: A command reset is executed immediately after the data is read.

The reset is cleared by returning the CS pin to high to reset this register. The reset is also cleared if this command is executed consecutively or if this register is set to 0.

- RAMCLR: The RAM can only be erased when display is off. This operation is not executed during display. This operation cannot be executed if the LC oscillator is stopped. Only use this command when the LC oscillator is operating.

- This command bit is automatically cleared when the RAM erase operation completes.

- Once the RAM erase command has been read in, the following time is required to complete the operation.

- Tclear = 5 [ $\mu$ s] + 4/f<sub>OSC</sub> (LC-oscillator) × 288

- 3. OSCSTP: The LC oscillator stop command stops the LC oscillator connected to pins 2 and 3 (OSC $_{IN}$ ) and OSC $_{OUT}$ ). The oscillator stop command is only executed when display is off. It is not executed if display is in progress.

- In external clock input mode, this command stops the acquisition of that clock signal.

- 4. TSTMOD: The test mode command is executed if the TEST<sub>IN</sub> pin (pin 5) is high. This command should not be used by applications in normal operation.

# ② COMMAND 1 (System control setup 2)

### First byte

| DA04- DA7  | Danistanuasas |       |                          | Re           | egister content                       | Note                                                                            |

|------------|---------------|-------|--------------------------|--------------|---------------------------------------|---------------------------------------------------------------------------------|

| DA0 to DA7 | Register name | State |                          |              | Function                              | Note                                                                            |

| 7          | _             | 0     |                          |              |                                       |                                                                                 |

| 6          | _             | 0     | Command                  | 1 identified | ation code                            |                                                                                 |

| 5          | _             | 0     | Command                  | i identinica | ation code                            |                                                                                 |

| 4          | _             | 1     |                          |              |                                       |                                                                                 |

| 3          | CSYN          | 0     | HSYNC (pi<br>signal inpu | ,            | tions as the horizontal synchronizing | The VSYNC pin (pin 21) must be tied to ground or V <sub>DD</sub> in composite   |

| 3          | 3 MOD         |       | HSYNC (pi<br>signal inpu | ,            | tions as the composite synchronizing  | synchronizing signal input mode.                                                |

| 2          | CLK           | 0     | The systen               | n clock has  | a positive polarity.                  | This sets the clock polarity for system operation when pin 2 is used as a clock |

| 2          | POLT          | 1     | The systen               | n clock has  | a negative polarity.                  | input.                                                                          |

|            |               | 0     |                          |              | 1                                     |                                                                                 |

| 1          | CLK           |       | MOD1                     | MOD0         | Operation                             | ) / alial cuts are the OTDI 4 min (airs 4) in high                              |

|            | MOD1          | 1     | 0                        | 0            | LC oscillator mode                    | Valid when the CTRL1 pin (pin 4) is high.                                       |

|            | CLK           |       | 0                        | 1            | Clock input (1 dot)                   | The input clock frequency in clock input mode is either 4fsc or the dot clock   |

|            |               | 0     | 1                        | 0            | Clock input (NTSC)                    | frequency.                                                                      |

| 0          | MOD0          | 1     | 1                        | 1            | Clock input (PAL)                     |                                                                                 |

### 3 COMMAND 2 (Input control)

# First byte

| DAG: DA7   | 5                        |   | Register content                                                                 | N .                                  |

|------------|--------------------------|---|----------------------------------------------------------------------------------|--------------------------------------|

| DA0 to DA7 | DA0 to DA7 Register name |   | Function                                                                         | Note                                 |

| 7          | _                        | 0 |                                                                                  |                                      |

| 6          | _                        | 0 | Command 2 identification code                                                    |                                      |

| 5          | _                        | 1 | Command 2 Identification code                                                    |                                      |

| 4          | _                        | 0 |                                                                                  |                                      |

| 3          | VSYN                     | 0 | The vertical synchronizing signal input polarity is low active.                  | Sets the pin 21 (VSYNC) signal input |

| 3          | POLT                     | 1 | The vertical synchronizing signal input polarity is high active.                 | polarity.                            |

| 2          | HSYN                     | 0 | The horizontal synchronizing signal input polarity is low active.                | Sets the pin 22 (HSYNC) signal input |

| 2          | POLT                     | 1 | The horizontal synchronizing signal input polarity is high active.               | polarity.                            |

| 1          | DATA                     | 0 | Data is transferred in 16-bit units.                                             | Sets the COMMAND 14 data transfer    |

| '          | FMT                      | 1 | Continuous transfers with the upper 8 bits input first and then the lower 8 bits | format.                              |

| 0          | ATR                      | 0 | RV specifies the reverse video display function.                                 | COMMAND-14 Data 11: Valid in RV      |

| U          | FMT                      | 1 | RV specifies system 3 output control.                                            | RGB output mode.                     |

# ② COMMAND 3 (General-purpose port control)

### First byte

| D. 1. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. | 5                        |      | Register content                                             |                                                                                |  |                                  |

|----------------------------------------------|--------------------------|------|--------------------------------------------------------------|--------------------------------------------------------------------------------|--|----------------------------------|

| DA0 to DA7                                   | DA0 to DA7 Register name |      | Function                                                     | Note                                                                           |  |                                  |

| 7                                            | _                        | 0    |                                                              |                                                                                |  |                                  |

| 6                                            | _                        | 0    | Command 3 identification code                                |                                                                                |  |                                  |

| 5                                            | _                        | 1    | Command 3 Identification code                                |                                                                                |  |                                  |

| 4                                            | _                        | 1    |                                                              |                                                                                |  |                                  |

| 3                                            | PORT                     |      | System 4 functions as a normal character and border outputs. | Controls the pin 10 (BLK4) and pin 11                                          |  |                                  |

| 3                                            | SET                      | 1    | System 4 functions as general-purpose ports.                 | (CHA4) outputs.                                                                |  |                                  |

| 2                                            | OUT                      | 0    | The pin 11 output is set to low.                             | Sets the output when PORTSET is                                                |  |                                  |

| 2                                            | P11                      | 1    | The pin 11 output is set to high.                            | set to 1.                                                                      |  |                                  |

| 4                                            | OUT                      | 0    | The pin 10 output is set to low.                             | Sets the output when PORTSET is                                                |  |                                  |

| '                                            | P10                      | 1    | The pin 10 output is set to high.                            | set to 1.                                                                      |  |                                  |

| 0                                            | OUT                      | 0    | The pin 9 output is set to low.                              | Sets the output for pin 9 during normal operation (other than during a reset). |  |                                  |

| U                                            | P9                       | P9 1 |                                                              |                                                                                |  | The pin 9 output is set to high. |

### (5) COMMAND 4 (Display control: reverse video and blinking)

# First byte

| DA0 4- DA7 | Da sista a sassa |       |                           | R            | egister content                          | Nete                                                       |

|------------|------------------|-------|---------------------------|--------------|------------------------------------------|------------------------------------------------------------|

| DA0 to DA7 | Register name    | State |                           |              | Function                                 | Note                                                       |

| 7          | _                | 0     |                           |              |                                          |                                                            |

| 6          | _                | 1     | Command                   | 4 : -! +: 4: | aliana ana da                            |                                                            |

| 5          | _                | 0     | Command                   | 4 Identifica | ation code                               |                                                            |

| 4          | _                | 0     |                           |              |                                          |                                                            |

| 3          | RVS              | 0     | _                         |              |                                          |                                                            |

| 3          | ON               | 1     | Characters<br>in reverse  |              | the attribute is specified are displayed |                                                            |

| 2          | BLK              | 0     | _                         |              |                                          |                                                            |

| 2          | ON               | 1     | Characters<br>displayed b |              | the attribute is specified are           |                                                            |

| 4          | 1 BLK1           | 0     | BLK1                      | BLK0         | Operation                                | ]                                                          |

| 1          |                  | 1     | 0                         | 0            | V × 25 (PAL: 0.5 s)                      | The blinking period setting The duty is 60% for all types. |

|            |                  |       | 0                         | 1            | V × 30 (NTSC: 0.5 s)                     | Character display on: 60%                                  |

|            |                  | 0     | 1                         | 0            | V × 50 (PAL: 1.0 s)                      | Character display off: 40%                                 |

| 0          | BLK0             | 1     | 1                         | 1            | V × 60 (NTSC: 1.0 s)                     | V: Vertical period                                         |

|            |                  |       |                           | •            |                                          |                                                            |

# **⑥** COMMAND 5 (Display control: on/off settings for each output system)

### First byte

| DAG 1 DA 7 | 5             |       | Register content                |                                                         |  |

|------------|---------------|-------|---------------------------------|---------------------------------------------------------|--|

| DA0 to DA7 | Register name | State | Function                        | Note                                                    |  |

| 7          | _             | 0     |                                 |                                                         |  |

| 6          | _             | 1     | Command 5 identification code   |                                                         |  |

| 5          | _             | 0     | Confinant 3 identification code |                                                         |  |

| 4          | _             | 1     |                                 |                                                         |  |

| 3          | 3 DSP4        |       | System 4 output off             | Pin 10 (BLK4) and pin 11 (CHA4) output                  |  |

| 3          | D3F4          | 1     | System 4 output on              | control                                                 |  |

| 2          | DSP3          | 0     | System 3 output off             | Pin 14 (BLK3) and pin 15 (CHA3) output                  |  |

| 2          | DSF3          | 1     | System 3 output on              | control                                                 |  |

| 1          | 1 DSP2        |       | System 2 output off             | Pin 16 (BLK2) and pin 17 (CHA2) output control          |  |

| ,          | DOI 2         | 1     | System 2 output on              | Invalid in RGB output mode.                             |  |

| 0          | DSP1          | 0     | System 1 (RGB) output off       | Pin 18 (BLK1) and pin 19 (CHA1) output control          |  |

| 0          |               | 1     | System 1 (RGB) output on        | Functions as the RGB output control in RGB output mode. |  |

### ⑦ COMMAND 6 (Output control: systems 3 and 4 output control settings)

# First byte

| DA04- DA7  | Danistanasa   |       |                            | Re                        | gister conte | ent                                                      | Nete                                                                    |  |  |  |  |

|------------|---------------|-------|----------------------------|---------------------------|--------------|----------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|

| DA0 to DA7 | Register name | State |                            |                           | Func         | tion                                                     | Note                                                                    |  |  |  |  |

| 7          | _             | 0     |                            |                           |              |                                                          |                                                                         |  |  |  |  |

| 6          | _             | 1     | Cammand                    | 6 identifica              | tion anda    |                                                          |                                                                         |  |  |  |  |

| 5          | _             | 1     | Command                    | 6 identifica              | tion code    |                                                          |                                                                         |  |  |  |  |

| 4          | _             | 0     |                            |                           |              |                                                          |                                                                         |  |  |  |  |

| 3          | DSPF          | 0     | Sets the sy<br>described I |                           | put conditio | ns according to the command                              | Only system 4 is valid in 4-system output mode. System 4 cannot be set  |  |  |  |  |

| 3          | SL34          | 1     | Sets the sy<br>described I |                           | put conditio | when the general-purpose output port usage is specified. |                                                                         |  |  |  |  |

|            | DSP           | 0     | DSPRSG                     | DSPGSG                    | DSPBSG       | Output selection                                         |                                                                         |  |  |  |  |

| 2          | RSG           | 1     | 0                          | 0                         | 0            | Signals other than R, G, B are output.                   | Note: The following registers are set to                                |  |  |  |  |

|            |               |       | 0                          | 0                         | 1            | B is output.                                             | 1 during a reset. DSPRSG                                                |  |  |  |  |

|            | DSP           | 0     | 0                          | 1                         | 0            | G is output.                                             | DSPGSG                                                                  |  |  |  |  |

| 1          | GSG           | 1     | 0                          | 1                         | 1            | G and B are output.                                      | DSPBSG                                                                  |  |  |  |  |

|            |               | '     | 1                          | 0                         | 0            | R is output.                                             | As a result, the "All of R, G, B are output" state is selected during a |  |  |  |  |

|            |               | 0     | 1                          | 1 0 1 R and B are output. |              | R and B are output.                                      | reset.                                                                  |  |  |  |  |

| 0          | DSP<br>BSG    |       | 1                          | 1                         | 0            | R and G are output.                                      |                                                                         |  |  |  |  |

|            | 250           | 1     | 1                          | 1                         | 1            | All of R, G, B are output.                               |                                                                         |  |  |  |  |

# **(8)** COMMAND 8 (Output control: background color setting: RGB output mode)

### First byte

| DA04- DA7  | Danistas sassa |          |            | Re           | gister cont | ent              |                                                  | Nists                                                                |  |  |  |

|------------|----------------|----------|------------|--------------|-------------|------------------|--------------------------------------------------|----------------------------------------------------------------------|--|--|--|

| DA0 to DA7 | Register name  | State    |            |              | Fund        | etion            |                                                  | Note                                                                 |  |  |  |

| 7          | _              | 1        |            |              |             |                  |                                                  |                                                                      |  |  |  |

| 6          | _              | 0        | Command    | Q idontifica | tion anda   |                  |                                                  |                                                                      |  |  |  |

| 5          | _              | 0        | Command    | o identinica | lion code   |                  |                                                  |                                                                      |  |  |  |

| 4          | _              | 0        |            |              |             |                  |                                                  |                                                                      |  |  |  |

| 3          |                | 0        | _          |              |             |                  |                                                  |                                                                      |  |  |  |

|            | 2 BKCR         | 0        | BKCR       | BKCG         | вксв        | Background color | 1                                                |                                                                      |  |  |  |

| 2          |                | 1        | 0          | 0            | 0           | Black            | 1                                                |                                                                      |  |  |  |

|            |                | <u> </u> | 0          | 0            | 1           | Blue             |                                                  | Background color setting in RGB output                               |  |  |  |

|            |                | 0        | 0          | 1            | 0           | Green            |                                                  | mode                                                                 |  |  |  |

| 1          | BKCG           |          | 0 1 1 Cyan |              |             |                  | This command is invalid in 4-system output mode. |                                                                      |  |  |  |

|            |                | 1        | 1          | 0            | 0           | Red              |                                                  | <ul> <li>Invalid when pin 20 (OUT<sub>MOD</sub>) is high.</li> </ul> |  |  |  |

|            |                |          | 1          | 0            | 1           | Magenta          |                                                  | <ul> <li>Valid when pin 20 (OUT<sub>MOD</sub>) is low.</li> </ul>    |  |  |  |

| 0          | ВКСВ           | 0        | 1          | 1            | 0           | Yellow           |                                                  |                                                                      |  |  |  |

|            | DICO           | 1        | 1          | 1            | 1           | White            | ┚┃                                               |                                                                      |  |  |  |

# Second byte

| DA0 to DA7 | Pagistar nama |       |            | Re     | egister content                        | Note                                                                                                                        |  |  |  |

|------------|---------------|-------|------------|--------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DAU IO DA7 | Register name | State |            |        | Function                               | Note                                                                                                                        |  |  |  |

| 7          | BKO4          | 0     | BKO4F1     | BKO4F0 | Operation function                     |                                                                                                                             |  |  |  |

| /          | F1            | 1     | 0          | 0      | No background or border                | -                                                                                                                           |  |  |  |

|            |               |       | 0          | 1      | Font size (black characters)           | The system 4 output border setting                                                                                          |  |  |  |

|            | BKO4          | 0     | 1          | 0      | Border                                 |                                                                                                                             |  |  |  |

| 6          | F0            | 1     | 1          | 1      | Areas other than the font (all filled) |                                                                                                                             |  |  |  |

|            |               |       |            |        |                                        |                                                                                                                             |  |  |  |

| 5          | BKO3          | 0     | BKO3F1     | BKO3F0 | Operation function                     |                                                                                                                             |  |  |  |

|            | F1            | 1     | 0          | 0      | No background or border                |                                                                                                                             |  |  |  |

|            |               |       | 0          | 1      | Font size (black characters)           | The system 3 output border setting                                                                                          |  |  |  |

|            | BKO3          | 0     | 1 0 Border |        | Border                                 |                                                                                                                             |  |  |  |

| 4          | F0            | 1     | 1          | 1      | Areas other than the font (all filled) |                                                                                                                             |  |  |  |

|            |               |       |            |        |                                        |                                                                                                                             |  |  |  |

| 3          | BKO2<br>F1    | 0     | BKO2F1     | BKO2F0 | Operation function                     | The system 2 output border setting                                                                                          |  |  |  |

|            | F1            | 1     | 0          | 0      | No background or border                | This command is invalid in RGB output                                                                                       |  |  |  |

|            |               |       | 0          | 1      | Font size (black characters)           | mode.                                                                                                                       |  |  |  |

|            | BKO2          | 0     | 1          | 0      | Border                                 | <ul> <li>Invalid when pin 20 (OUT<sub>MOD</sub>) is low.</li> <li>Valid when pin 20 (OUT<sub>MOD</sub>) is high.</li> </ul> |  |  |  |

| 2          | F0            | 1     | 1          | 1      | Areas other than the font (all filled) | Valid Whoti pin 20 (00 mob) to mgri.                                                                                        |  |  |  |

|            |               |       |            |        |                                        |                                                                                                                             |  |  |  |

| 1          | BKO1          | 0     | BKO1F1     | BKO1F0 | Operation function                     |                                                                                                                             |  |  |  |

|            | F1            | 1     | 0          | 0      | No background or border                | The system 1 or RGB output border                                                                                           |  |  |  |

|            |               |       | 0          | 1      | Font size                              | setting                                                                                                                     |  |  |  |

|            | BKO1          | 0     | 1          | 0      | Border                                 |                                                                                                                             |  |  |  |

| 0          | F0            | 1     | 1          | 1      | Areas other than the font (all filled) |                                                                                                                             |  |  |  |

|            |               | 1     |            |        |                                        |                                                                                                                             |  |  |  |

#

### First byte

| DAG 4- DAZ | Danistan      |       | Register content                                                                                 | Nete |

|------------|---------------|-------|--------------------------------------------------------------------------------------------------|------|

| DA0 to DA7 | Register name | State | Function                                                                                         | Note |

| 7          | _             | 1     |                                                                                                  |      |

| 6          | _             | 0     | Command 9 identification code                                                                    |      |

| 5          | _             | 0     | Command 9 Identification code                                                                    |      |

| 4          | _             | 1     |                                                                                                  |      |

| 3          | VP5           | 0     | If VS is the vertical display start position then: $VS = H \times (\Sigma 2^n VP_n) + 16H$ $= 0$ |      |

| 3          | VI 3          | 1     | n`= 0 ""  Where H is horizontal period pulse period.                                             |      |

| 2          | VP4           | 0     | HSYNC                                                                                            |      |

|            |               | 1     |                                                                                                  |      |

| 1          | VP3           | 0     | vs                                                                                               |      |

| ı ı        | VF3           | 1     | VSYNC Character                                                                                  |      |

| 0          | VP2           | 0     | HS display area                                                                                  |      |

| Ŭ .        | VF2           | 1     |                                                                                                  |      |

# Second byte

| DAG 4- DAZ | Danistas assess |       | Register content                                                                                                            | NI-4- |

|------------|-----------------|-------|-----------------------------------------------------------------------------------------------------------------------------|-------|

| DA0 to DA7 | Register name   | State | Function                                                                                                                    | Note  |

| 7          | VP1             | 0     |                                                                                                                             |       |

| ,          | VPI             | 1     |                                                                                                                             |       |

| 6          | VP0             | 0     |                                                                                                                             |       |

| 8          | VPU             | 1     |                                                                                                                             |       |

| 5          | HP5             | 0     |                                                                                                                             |       |

| 5          | пгэ             | 1     |                                                                                                                             |       |

| 4          | HP4             | 0     | If VS is the horizontal display start position then:                                                                        |       |

| 4          | 11174           | 1     | $HS = Tc \times (\sum_{n=0}^{\infty} 2^{n}HP_{n}) + 12Tc$                                                                   |       |

| 3          | HP3             | 0     | n = 0                                                                                                                       |       |

| 3          | 111-3           | 1     | Where Tc is a single period of the LC oscillator connected to pins 2 and 3 (OSC <sub>IN</sub> and OSC <sub>OUT</sub> ), or: |       |

| 2          | HP2             | 0     | Tc is the period of the input clock (4fsc input) if CTRL1 (pin 4) is                                                        |       |

|            | 111 2           | 1     | high.                                                                                                                       |       |

| 1          | HP1             | 0     | NTSC mode: 7.159 MHz = 4fsc × 1/2                                                                                           |       |

|            | 111-1           | 1     | PAL mode: 7.094 MHz = 4fsc × 2/5                                                                                            |       |

| 0          | HP0             | 0     |                                                                                                                             |       |

|            | 111-0           | 1     |                                                                                                                             |       |

# (n) COMMAND 10 (Display line control)

### First byte

| DAG: DA7   | <b>D</b>      |       | Register content                                               |                                          |  |  |

|------------|---------------|-------|----------------------------------------------------------------|------------------------------------------|--|--|

| DA0 to DA7 | Register name | State | Function                                                       | Note                                     |  |  |

| 7          | _             | 1     |                                                                |                                          |  |  |

| 6          | _             | 0     | Command 10 identification code                                 |                                          |  |  |

| 5          | _             | 1     | Command to identification code                                 |                                          |  |  |

| 4          | _             | 0     |                                                                |                                          |  |  |

| 3          | LNF           |       | _                                                              |                                          |  |  |

| 3          | SZ            | 1     | Sets the character size.                                       |                                          |  |  |

| 2          | LNF           | 0     | _                                                              | Invalid in general-purpose port mode.    |  |  |

| 2          | OT4           | 1     | Sets the system 4 display line.                                | mivalid in general-purpose port mode.    |  |  |

| 4          | LNF           | 0     | _                                                              | Invalid in system 4 output setup mode.   |  |  |

| '          | OT3           | 1     | Sets the system 3 display line.                                | mivalid in system 4 output setup mode.   |  |  |

| 0          | LNF           | 0     | The line specified by the next 6 bits is one of lines 1 to 6.  | Controls the line switching specified by |  |  |

| U          | SEL           | 1     | The line specified by the next 6 bits is one of lines 7 to 12. | the six bits in the second byte.         |  |  |

# Second byte

| B40. B45   | 5             |       | Register content                |                                                                            |  |  |  |  |

|------------|---------------|-------|---------------------------------|----------------------------------------------------------------------------|--|--|--|--|

| DA0 to DA7 | Register name | State | Function                        | Note                                                                       |  |  |  |  |

| 7          | _             | 0     | _                               |                                                                            |  |  |  |  |

| 6          | _             | 0     | _                               |                                                                            |  |  |  |  |

| 5          | LIN           | 0     | Clears the line 6 (12) setting. |                                                                            |  |  |  |  |

| 5          | 126           | 1     | Sets line 6 (12).               |                                                                            |  |  |  |  |

| 4          | LIN<br>115    | 0     | Clears the line 5 (11) setting. |                                                                            |  |  |  |  |

| 4          |               | 1     | Sets line 5 (11).               | The character size or display line                                         |  |  |  |  |

| 3          | LIN           | 0     | Clears the line 4 (10) setting. | setting                                                                    |  |  |  |  |

| 3          | 104           | 1     | Sets line 4 (10).               | 0: Character size specification = norma                                    |  |  |  |  |

| 2          | LIN           | 0     | Clears the line 3 (9) setting.  | Display line specification = off  1: Character size specification = double |  |  |  |  |

| 2          | 93            | 1     | Sets line 3 (9).                | size                                                                       |  |  |  |  |

| 4          | LIN           | 0     | Clears the line 2 (8) setting.  | Display line specification = on                                            |  |  |  |  |

| '          | 82            | 1     | Sets line 2 (8).                |                                                                            |  |  |  |  |

| 0          | LIN           | 0     | Clears the line 1 (7) setting.  |                                                                            |  |  |  |  |

| 0          | 71            | 1     | Sets line 1 (7).                |                                                                            |  |  |  |  |

# ① COMMAND 11 (Display RAM write address setting)

# First byte

| DAG 1 DA 7 | <b>D</b>      |       | Register content                                                                                              |      |

|------------|---------------|-------|---------------------------------------------------------------------------------------------------------------|------|

| DA0 to DA7 | Register name | State | Function                                                                                                      | Note |

| 7          | _             | 1     |                                                                                                               |      |

| 6          | _             | 0     | Command 11 identification code                                                                                |      |

| 5          | _             | 1     | Command 11 Identification code                                                                                |      |

| 4          | _             | 1     |                                                                                                               |      |

| 3          | VADR          | 0     |                                                                                                               |      |

| 3          | 3             | 1     |                                                                                                               |      |

| 2          | VADR          | 0     |                                                                                                               |      |

| 2          | 2             | 1     | The range of the display RAM vertical address (line address) setting is from 0 to B (hexadecimal) (12 lines). |      |

| 1          | VADR          | 0     | Values of C (hexadecimal) or larger are not allowed.                                                          |      |

| '          | 1             | 1     | ,                                                                                                             |      |

| 0          | VADR          | 0     |                                                                                                               |      |

|            | 0             | 1     |                                                                                                               |      |

# Second byte

| DAG . DA 7 | <b>D</b>      |       | Register content                                                                                                        | N. c |

|------------|---------------|-------|-------------------------------------------------------------------------------------------------------------------------|------|

| DA0 to DA7 | Register name | State | Function                                                                                                                | Note |

| 7          | _             | 0     | _                                                                                                                       |      |

| 6          | _             | 0     | _                                                                                                                       |      |

| 5          | _             | 0     | _                                                                                                                       |      |

| 4          | HADR          | 0     |                                                                                                                         |      |

| 4          | 4             | 1     |                                                                                                                         |      |

| 3          | HADR          | 0     |                                                                                                                         |      |

| 3          | 3             | 1     |                                                                                                                         |      |

| 2          | HADR          | 0     | The range of the display RAM horizontal address (character                                                              |      |

| 2          | 2             | 1     | address) setting is from 00 to 17 (hexadecimal) (24 characters).  Values of 18 (hexadecimal) or larger are not allowed. |      |

| 1          | HADR          | 0     | 3                                                                                                                       |      |

| ſ          | 1             | 1     |                                                                                                                         |      |

| 0          | HADR          | 0     |                                                                                                                         |      |

| U          | 0             | 1     |                                                                                                                         |      |

# (2) COMMAND 14 (Display RAM setup data)

# First byte

| 540. 545   | 5             |       | Register content                                                 |      |

|------------|---------------|-------|------------------------------------------------------------------|------|

| DA0 to DA7 | Register name | State | Function                                                         | Note |

| 7          | _             | 1     |                                                                  |      |

| 6          | _             | 1     | Command 14 identification code                                   |      |

| 5          | _             | 1     |                                                                  |      |

| 4          | BLK           | 0     | _                                                                |      |

| 4          | 4 BLK         |       | Blinking character specification                                 |      |

| 3          | D) (          | 0     | _                                                                |      |

| 3          | RV            | 1     | Reverse video character specification                            |      |

| 2          | R             | 0     | _                                                                |      |

| 2          | K             | 1     | R output specification (system 3 output in 4-system output mode) |      |

| 1          | G             | 0     | _                                                                |      |

|            |               | 1     | G output specification (system 2 output in 4-system output mode) |      |

| 0          | В             | 0     | _                                                                |      |

| U          | Б             | 1     | B output specification (system 1 output in 4-system output mode) |      |

### Second byte

| D404 D45   | 5             |       | Register content                                                                          |      |

|------------|---------------|-------|-------------------------------------------------------------------------------------------|------|

| DA0 to DA7 | Register name | State | Function                                                                                  | Note |

| 7          | C7            | 0     |                                                                                           |      |

| /          | C7            | 1     |                                                                                           |      |

| 6          | C6            | 0     |                                                                                           |      |

| 0          | Co            | 1     |                                                                                           |      |

| 5          | C5            | 0     | Character code setting                                                                    |      |

|            | 03            | 1     | There are 256 characters (00 to FF hexadecimal).                                          |      |

| 4          | C4            | 0     | FE hexadecimal is handled as blank data.                                                  |      |

|            | 04            | 1     | Nothing is displayed, whatever the other conditions are set to.                           |      |

| 3          | C3            | 0     | FF hexadecimal functions as the transfer termination code for                             |      |

|            | 00            | 1     | character-code-only continuous transfers.                                                 |      |

| 2          | C2            | 0     | Continuous transfer mode is set up by setting the data 0 bit (DATAFMT) in COMMAND 2 to 1. |      |

|            | 02            | 1     | (DATAL WIT) III COMMINIAND 2 to 1.                                                        |      |

| 1          | C1            | 0     |                                                                                           |      |

|            | J 1           | 1     |                                                                                           |      |

| 0          | CO            | 0     |                                                                                           |      |

|            | 30            | 1     |                                                                                           |      |

### **Display Screen Organization**

The display screen consists of 12 lines of 24 characters each.

Thus the maximum number of characters that can be displayed is 288 characters.

The display memory address consists of a line address (VADR0, VADR1, VADR2, and VADR3 representing values from 0 to B (hexadecimal)), and a column (character position) address (HADR0, HADR1, HADR2, HADR3, and HADR4 representing values from 0 to 17 (hexadecimal)).

#### **Display Screen Organization (Display memory address)**

|      | -     |           |            |            |            |              |            |            |            |            |            | <b>-</b> 24 | chara      | cters :    |            |            |            |            |            |            |            |            |            |            |            |

|------|-------|-----------|------------|------------|------------|--------------|------------|------------|------------|------------|------------|-------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

|      |       | 1         | 2          | 3          | 4          | 5            | 6          | 7          | 8          | 9          | 10         | 11          | 12         | 13         | 14         | 15         | 16         | 17         | 18         | 19         | 20         | 21         | 22         | 23         | 24         |

|      | H     | Oh<br>Oh  | 01h<br>00h | 02h<br>00h | 03h<br>00h | 04h<br>00h   | 05h<br>00h | 06h<br>00h | 07h<br>00h | 08h<br>00h | 09h<br>00h | 0Ah<br>00h  | 0Bh<br>00h | 0Ch<br>00h | 0Dh<br>00h | 0Eh<br>00h | 0Fh<br>00h | 10h<br>00h | 11h<br>00h | 12h<br>00h | 13h<br>00h | 14h<br>00h | 15h<br>00h | 16h<br>00h | 17h<br>00h |

| ;    | 2   ` | Oh<br>1h  | 01h<br>01h | 02h<br>01h | 03h<br>01h | 04h<br>01h   | 05h<br>01h | 06h<br>01h | 07h<br>01h | 08h<br>01h | 09h<br>01h | 0Ah<br>01h  | 0Bh<br>01h | 0Ch        | 0Dh<br>01h | 0Eh        | 0Fh<br>01h | 10h<br>01h | 11h<br>01h | 12h<br>01h | 13h<br>01h | 14h<br>01h | 15h<br>01h | 16h<br>01h | 17h<br>01h |