# LV8850GA

Bi-CMOS IC

## Three-Phase sensorless FAN Motor Pre-Driver

ON Semiconductor®

<http://onsemi.com>

### Overview

LV8850GA is a pre-driver IC which is three-phase, sensorless and drives with PWM.

LV8850GA drives without a hole sensor, which is suitable for driving high-current motor which requires high reliability and long life.

### Function

- VCC+7V charge pump booster circuit for output drive

- Integrated Synchronous Rectifier circuit (Selected by SYNSEL pin)

- PWM or DC input signal is selectable (Selected by CTLSW pin)

- Adjustable PWM frequency (By the external capacitor at DC input mode)

- Integrated Current Limit circuit (highly accurate detection by using sensing (RFGND) pin for monitoring)

- Integrated Forward / Reverse rotation switch circuit (Selected by F/R pin)

- Integrated Lock Protection circuit with auto-recovery

- Output Lock Protection signal (RD pin) / Output 1-hole FG signal (FG pin)

### Specifications

#### Absolute Maximum Ratings at Ta = 25°C

| Parameter                    | Symbol                | Conditions                      | Ratings     | Unit |

|------------------------------|-----------------------|---------------------------------|-------------|------|

| Maximum Supply voltage       | V <sub>CC</sub> max   | V <sub>CC</sub> pin             | 18          | V    |

| Maximum VG voltage           | V <sub>G</sub> max    | V <sub>G</sub> pin              | 23          | V    |

| Maximum RD/FG pin voltage    | V <sub>FG</sub> max   | RD, FG pin                      | 18          | V    |

| Maximum RD/FG pin current    | I <sub>FG</sub> max   | RD, FG pin                      | 5           | mA   |

| Maximum Output pin voltage1  | V <sub>O</sub> max1   | UH, VH, WH pin                  | 23          | V    |

| Maximum Output pin voltage2  | V <sub>O</sub> max2   | UL, VL, WL pin                  | 6           | V    |

| Maximum Output pin current   | I <sub>O</sub> max    | UH, VH, WH, UL, VL, WL pin      | 30          | mA   |

| Maximum Input pin voltage    | V <sub>L</sub> max    | SOSC, LIM, VCTL, PWMOSC, CSDOSC | 6           | V    |

| Maximum VREG pin current     | I <sub>VREG</sub> max | VREG pin                        | 5           | mA   |

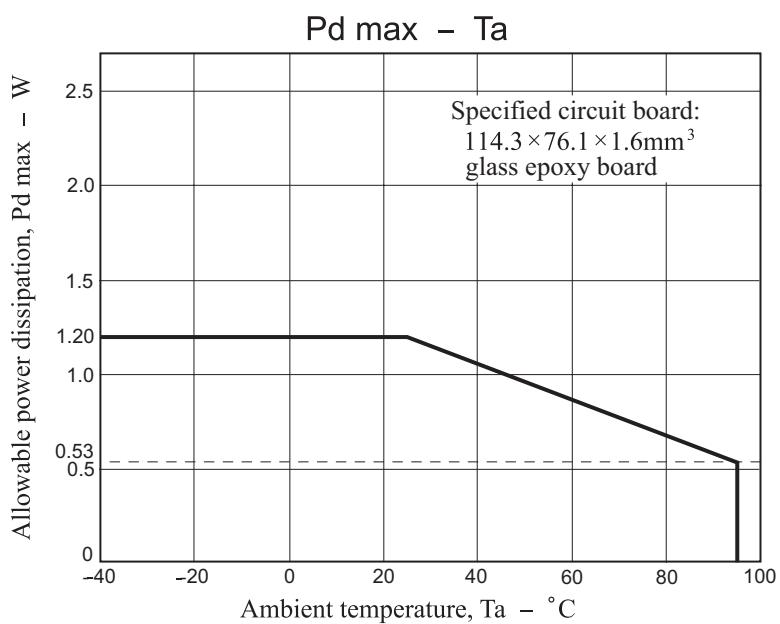

| Allowable power dissipation2 | P <sub>d</sub> max    | Mounted on a board. *1          | 1.2         | W    |

| Operating temperature        | T <sub>opr</sub>      |                                 | – 40 to 95  | deg. |

| Storage temperature          | T <sub>stg</sub>      |                                 | – 55 to 150 | deg. |

| Junction temperature         | T <sub>j</sub> max    |                                 | 150         | deg. |

\*1: Specified board: 76.1mm x 114.3mm x 1.6mm, glass epoxy board

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

### ORDERING INFORMATION

See detailed ordering and shipping information on page 13 of this data sheet.

# LV8850GA

## Recommended Operating Conditions at $T_a = 25^\circ\text{C}$

| Parameter                              | Symbol     | Conditions                                                        | Ratings |     |      | Unit |

|----------------------------------------|------------|-------------------------------------------------------------------|---------|-----|------|------|

|                                        |            |                                                                   | min     | typ | max  |      |

| Operating voltage                      | $V_{CC}$   | $V_{CC}$ pin                                                      |         | 12  |      | V    |

| Operating supply voltage               | $V_{CCOP}$ | $V_{CC}$ pin <sup>2</sup>                                         | 4       |     | 16   | V    |

| VG pin voltage range                   | $V_G$      | VG pin ( $V_{CC}+7V$ ) <sup>3</sup>                               |         |     | 21   | V    |

| Pin voltage range                      | $V_L$      | SOSC, LIM, VCTL, PWMOSC, CSDOSC<br>SOFTST, CTLSW, SYNSEL, F/R pin | 0       |     | VREG | V    |

| Output current range                   | $I_O$      | UL, VL, WL, UH, VH, WH pin                                        | 0       |     | 25   | mA   |

| Input PWM frequency range <sup>4</sup> | $f(PWM)$   |                                                                   | 20      |     | 60   | kHz  |

<sup>2</sup>: When the voltage of  $V_{CC}$  is reduced, the speed might not be controllable properly depending on settings.

<sup>3</sup>: For VG pin, be applied either  $V_{CC}+7V$  or 21V, whichever is lower.

<sup>4</sup>: Make sure to adjust it according to External-FETs and types of Motor and maximum rotation speed.

## Electrical Characteristics at $T_a = 25^\circ\text{C}$ , $V_{CC} = 12\text{V}$

| Parameter                                                                    | Symbol           | Conditions                                                      | Ratings       |          |            | Unit     |

|------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------|---------------|----------|------------|----------|

|                                                                              |                  |                                                                 | Min           | typ      | max        |          |

| Supply current                                                               | $I_{CC}$         | DC input mode, PWM=100%                                         | 7             | 10       | 13         | mA       |

| <b>Internal oscillation circuit</b>                                          |                  |                                                                 |               |          |            |          |

| Oscillation frequency                                                        | $f(MOSC)$        |                                                                 | 8             | 10       | 12         | MHz      |

| <b>Constant voltage output (VREG pin) <sup>5</sup></b>                       |                  |                                                                 |               |          |            |          |

| Output voltage1                                                              | $V_{VREG}$       |                                                                 | 3.6           | 4.0      | 4.2        | V        |

| Load fluctuation                                                             | $\Delta V_{REG}$ | $I_O = -5 \text{ to } 0 \text{ mA}$                             |               |          | 100        | mV       |

| <b>Charge pump output (VG pin) <sup>6</sup></b>                              |                  |                                                                 |               |          |            |          |

| Output voltage                                                               | $V_{VG}$         |                                                                 |               |          | $V_{CC}+7$ |          |

| <b>Output block</b>                                                          |                  |                                                                 |               |          |            |          |

| On-resister of Upper-Tr in H-side                                            | $RON_{HH}$       | $I_O = -10 \text{ mA}$                                          |               | 25       | 40         | $\Omega$ |

| On-resister of Lower-Tr in H-side                                            | $RON_{HL}$       | $I_O = 10 \text{ mA}$                                           |               | 40       | 60         | $\Omega$ |

| On-resister of Upper-Tr in L-side                                            | $RON_{LH}$       | $I_O = -10 \text{ mA}$                                          |               | 40       | 60         | $\Omega$ |

| On-resister of Lower-Tr in L-side                                            | $RON_{LL}$       | $I_O = 10 \text{ mA}$                                           |               | 25       | 40         | $\Omega$ |

| <b>VCTL amplifier (VCTL pin) at DC input mode (CTLSTW pin=High)</b>          |                  |                                                                 |               |          |            |          |

| Input bias current                                                           | $IB(CTL)$        |                                                                 | -1            |          | 1          | uA       |

| Gain                                                                         | $G(CTL)$         |                                                                 |               | 0.57     |            | V/V      |

| 0% duty input voltage                                                        | $V_{IN1}(CTL)$   |                                                                 | 3.0           | 3.2      | 3.4        | V        |

| Max duty input voltage                                                       | $V_{IN2}(CTL)$   |                                                                 | 1.35          | 1.55     | 1.75       | V        |

| <b>During direct PWM input (VCTL pin) at PWM input mode (CTLSTW pin=Low)</b> |                  |                                                                 |               |          |            |          |

| High level input voltage                                                     | $V_{IH}(PWM)$    | Out transistor ON                                               | $V_{REG} - 1$ |          | $V_{REG}$  | V        |

| Low level input voltage                                                      | $V_{IL}(PWM)$    | Output transistor OFF                                           | 0             |          | 1          | V        |

| <b>Input mode select pin (CTLSTW pin)</b>                                    |                  |                                                                 |               |          |            |          |

| High level input voltage                                                     | $V_{IH}(CTLSTW)$ | DC input mode                                                   | $V_{REG} - 1$ |          | $V_{REG}$  | V        |

| Low level input voltage                                                      | $V_{IL}(CTLSTW)$ | PWM input mode                                                  | 0             |          | 1          | V        |

| <b>Internal PWM oscillator (PWMOSC pin)</b>                                  |                  |                                                                 |               |          |            |          |

| High level output voltage                                                    | $V_{OH}(PWM)$    |                                                                 | 2.7           | 3.0      | 3.3        | V        |

| Low level output voltage                                                     | $V_{OL}(PWM)$    |                                                                 | 1.75          | 2.0      | 2.25       | V        |

| Charge/ discharge current                                                    | $I(PWM)$         | 2.5V                                                            | $\pm 30$      | $\pm 45$ | $\pm 60$   | uA       |

| <b>Forward / Reverse switch (F/R pin) <sup>7</sup></b>                       |                  |                                                                 |               |          |            |          |

| High level input voltage                                                     | $V_{IH}(FR)$     | Energization: $U_{OUT} \rightarrow V_{OUT} \rightarrow W_{OUT}$ | $V_{REG} - 1$ |          | $V_{REG}$  | V        |

| Low level input voltage                                                      | $V_{IL}(FR)$     | Energization: $U_{OUT} \rightarrow W_{OUT} \rightarrow V_{OUT}$ | 0             |          | 1          | V        |

Continue to the next page

# LV8850GA

Continue from the former page

| Parameter                                                           | Symbol     | Conditions                                    | Ratings  |       |       | Unit  |

|---------------------------------------------------------------------|------------|-----------------------------------------------|----------|-------|-------|-------|

|                                                                     |            |                                               | Min      | typ   | max   |       |

| <b>Synchronous rectification switch (SYNSEL pin) <sup>*11</sup></b> |            |                                               |          |       |       |       |

| High level input voltage                                            | VIH (SYN)  | Synchronous rectification control is disabled | VREG – 1 |       | VREG  | V     |

| Low level input voltage                                             | VIL (SYN)  | Synchronous rectification control is enabled  | 0        |       | 1     | V     |

| <b>FG, RD output (FG pin, RD pin) <sup>*8</sup></b>                 |            |                                               |          |       |       |       |

| Low level output voltage                                            | VFG        | FG, RD pin. Io = 2mA                          |          |       | 0.3   | V     |

| Maximum FG frequency <sup>*9</sup>                                  | f (FG)     | <sup>*10</sup>                                |          |       | 600   | Hz    |

| <b>Current limiter circuit (RF pin)</b>                             |            |                                               |          |       |       |       |

| Limiter voltage                                                     | VRF        | RF = 0.2 ohm, limit current: 1.05A            | 0.18     | 0.21  | 0.23  | V     |

| <b>Lock protection (CSDOSC pin)</b>                                 |            |                                               |          |       |       |       |

| High level output input                                             | VOH (CSD)  |                                               | 1.7      | 1.9   | 2.1   | V     |

| Low level output input                                              | VOL (CSD)  |                                               | 0.25     | 0.40  | 0.55  | V     |

| Charge current                                                      | IC (CSD)   |                                               | – 4.5    | – 3.5 | – 2.5 | uA    |

| Discharge current                                                   | ID (CSD)   |                                               | 0.25     | 0.35  | 0.45  | uA    |

| Ratio of charge and discharge                                       | RI (CSD)   |                                               | 8        | 10    | 12    | uA/uA |

| <b>Internal Start-Up oscillator (SOSC pin)</b>                      |            |                                               |          |       |       |       |

| High level output input                                             | VOH (SOSC) |                                               | 0.9      | 1.1   | 1.3   | V     |

| Low level output input                                              | VOL (SOSC) |                                               | 0.45     | 0.60  | 0.75  | V     |

| Charge/ discharge current                                           | I (SOSC)   |                                               | ±3.5     | ±5    | ±6.5  | uA    |

| <b>SOFT start (SOFTS pin)</b>                                       |            |                                               |          |       |       |       |

| SOFT start cancel voltage                                           | VIH(STS)   |                                               | 0.9      | 1.2   | 1.45  | V     |

| SOFTS charge current                                                | I(STS)     |                                               | 0.35     | 0.50  | 0.65  | uA    |

| <b>Overheat protection circuit (thermal shutdown)</b>               |            |                                               |          |       |       |       |

| Operating temperature                                               | TSDON      | Design guarantee <sup>*10</sup>               |          | 160   |       | deg.  |

| Hysteresis temperature                                              | ΔTSD       | Design guarantee <sup>*10</sup>               |          | 20    |       | deg.  |

<sup>\*5</sup>: For VREG pin, it can be used for only internal and setting of this IC, not for power supply.

<sup>\*6</sup>: For VG pin, be applied either VCC+7V or 21V, whichever is lower. And it can not be for power supply.

<sup>\*7</sup>: Do not switch R/F pin during motor rotation. This may damage the IC and the motor.

<sup>\*8</sup>: For FG, RD output pins, it is recommended to connect pull-up resistor between the pins and power supply of the controller.

<sup>\*9</sup>: Be limited by External-FETs and types of Motor.

<sup>\*10</sup>: Design guarantee: Signifies target value in design. These parameters are not tested in an independent IC.

<sup>\*11</sup>: For heat reduction and higher efficiency, this IC uses synchronous rectification by setting the "SYNSEL"-pin. However, it may increase supply voltage under usage conditions:

\* When output duty is reduced rapidly.

\* PWM input frequency is low. And other.

The above behavior depends on inserting a diode for protection against reverse connection, a bypass capacitor value between power supply and GND and FAN motor. Please confirm it enough. If the supply voltage shall increase, make sure that it does not exceed the maximum ratings with the following measures:

\*Select an optimal capacitor between power supply and GND.

\*Insert a zener diode between power supply and GND.

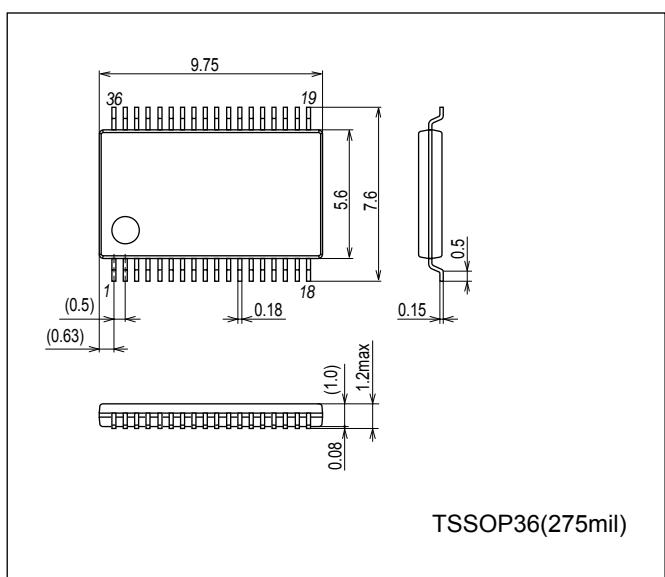

## Package Dimensions

unit : mm (typ)

3253B

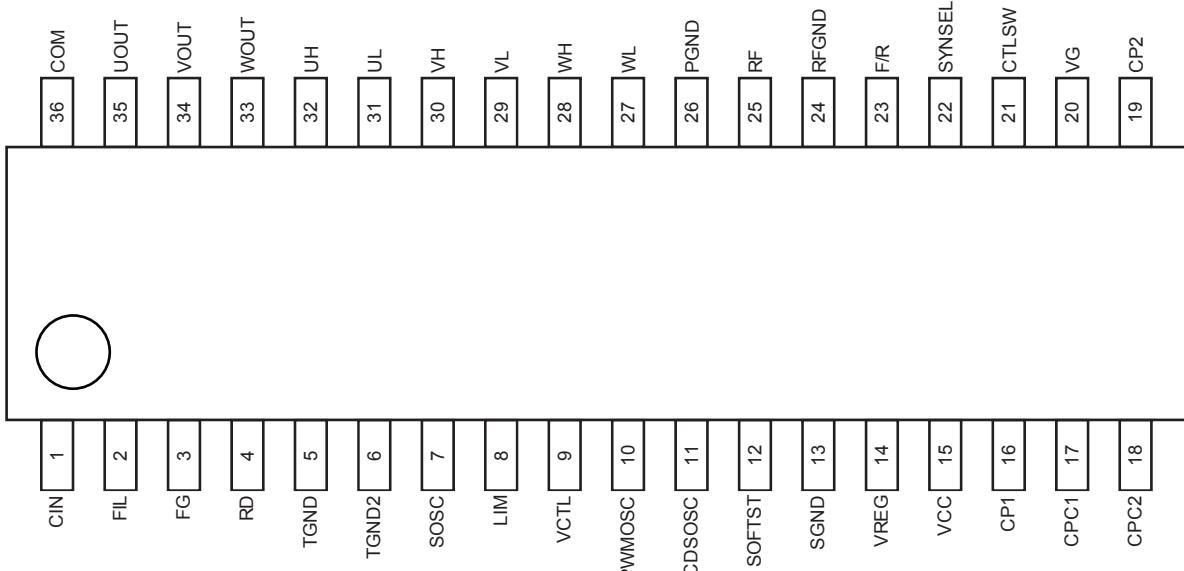

## Pin Assignment

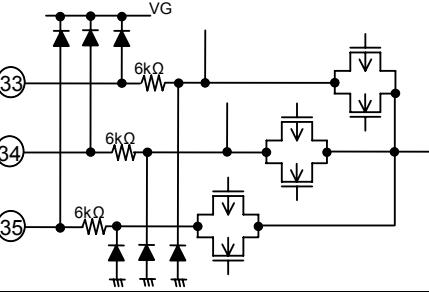

## Equivalent Circuit

| Pin No.      | Pin name          | Equivalent Circuit |

|--------------|-------------------|--------------------|

| 36<br>1<br>2 | COM<br>CIN<br>FIL |                    |

| 3            | FG                |                    |

| 4            | RD                |                    |

| 5<br>6       | TGND<br>TGND2     |                    |

| 7            | SOSC              |                    |

Continue to the next page

Continue from the former page

| Pin No. | Pin name    | Equivalent Circuit |

|---------|-------------|--------------------|

| 8<br>9  | LIM<br>VCTL |                    |

| 10      | PWMOSC      |                    |

| 11      | CSDOSC      |                    |

| 12      | SOFTST      |                    |

| 13      | SGND        |                    |

| 14      | VREG        |                    |

| 15      | VCC         |                    |

Continue to the next page

# LV8850GA

Continue from the former page

| Pin No.                    | Pin name                         | Equivalent Circuit                                                                   |

|----------------------------|----------------------------------|--------------------------------------------------------------------------------------|

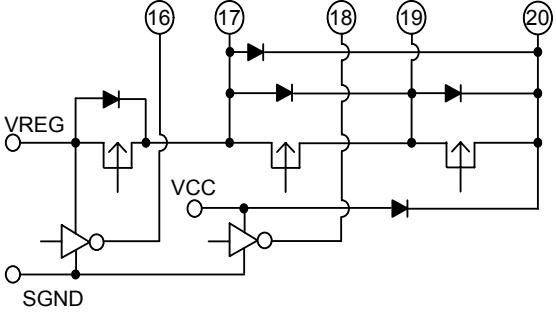

| 16<br>17<br>18<br>19<br>20 | CP1<br>CPC1<br>CPC2<br>CP2<br>VG |    |

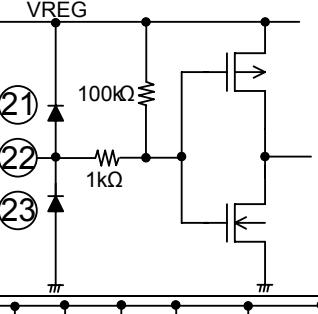

| 21<br>22<br>23             | CTL SW<br>SYNSEL<br>F/R          |    |

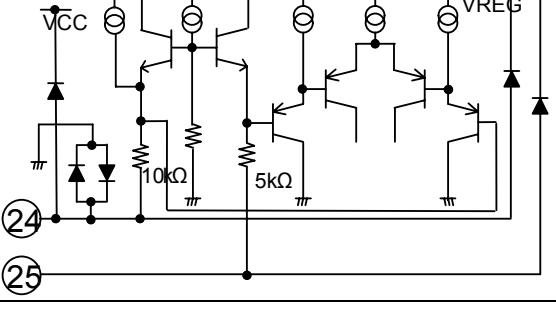

| 24<br>25                   | RFGND<br>RF                      |   |

| 26                         | PGND                             |                                                                                      |

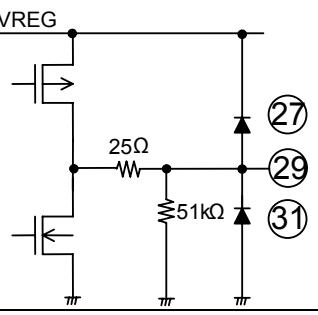

| 27<br>29<br>31             | WL<br>VL<br>UL                   |  |

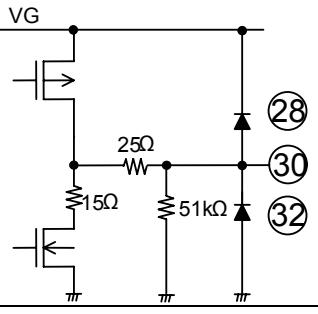

| 28<br>30<br>32             | WH<br>VH<br>UH                   |  |

| 33<br>34<br>35             | WOUT<br>VOUT<br>UOUT             |  |

## Pin Functions

| Pin No. | Pin name | Function                                                                                                                                                                                                                                                  |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CIN      | Filter pin for motor position detection comparator.<br>Make sure to connect a capacitor between FIL (PIN2) and CIN.                                                                                                                                       |

| 2       | FIL      | Filter pin for motor position detection comparator.<br>Make sure to connect a capacitor between CIN (PIN1) and FIL.                                                                                                                                       |

| 3       | FG       | FG pulse output. Outputs pulse equivalent to 1 hole. Synchronizes with U-phase.                                                                                                                                                                           |

| 4       | RD       | Motor lock detection output.<br>Outputs high level voltage when the motor is locked. Auto-recovery lock protection circuit.                                                                                                                               |

| 5       | TGND     | Test pin.                                                                                                                                                                                                                                                 |

| 6       | TGND2    | Connect to SGND.                                                                                                                                                                                                                                          |

| 7       | SOSC     | Setting pin for motor startup frequency. Make sure to connect a capacitor between SOSC and GND. Adjusts startup frequency according to charge/discharge current and the capacitor.                                                                        |

| 8       | LIM      | Voltage input for setting the lowest speed during DC control signal input mode.<br>By dividing the regulator voltage with resistance and inputting the voltage ( $1 < LIM < 3V$ ), you can set the lowest speed for the motor.                            |

| 9       | VCTL     | Motor control voltage input.<br>VCTL functions as DC control signal input pin and PWM control input signal input pin. CTLSW (PIN21) switches between DC input and PWM input.                                                                              |

| 10      | PWMOSC   | Reference frequency setting for PWM switching.<br>Make sure to connect a capacitor between PWMOSC and GND. You can set a carrier frequency for PWM switching during DC control signal input mode by adjusting the capacitor.                              |

| 11      | CSDOSC   | Setting pin for motor lock detection time. Make sure to connect a capacitor between CSDOSC and GND. You can set time to start lock protection operation by adjusting the capacitor.                                                                       |

| 12      | SOFTST   | Setting pin for soft start time. By connecting a capacitor between SOFTS and GND, you can start up the motor smoothly.                                                                                                                                    |

| 13      | SGND     | GND for the IC.                                                                                                                                                                                                                                           |

| 14      | VREG     | Regulator voltage output (4V).<br>Make sure to connect a capacitor between VREG and GND.<br>You cannot supply power outside the IC.                                                                                                                       |

| 15      | VCC      | Supply for the IC. Make sure to connect a capacitor between VCC and GND.                                                                                                                                                                                  |

| 16      | CP1      | Charge pump: pulse output for the 1st stage booster. Make sure to connect a capacitor between CP1 and CPC1 (17PIN).                                                                                                                                       |

| 17      | CPC1     | Charge pump: a pin for the 1st stage booster. Make sure to connect a capacitor between CPC1 and CP1 (PIN16).                                                                                                                                              |

| 18      | CPC2     | Charge pump: a pin for the 2nd stage booster. Make sure to connect a capacitor between CPC2 and CP2 (PIN19).                                                                                                                                              |

| 19      | CP2      | Charge pump: pulse output for the 2nd stage booster. Make sure to connect a capacitor between CP2 and CPC2 (PIN18).                                                                                                                                       |

| 20      | VG       | Charge pump: output for booster voltage.<br>Make sure to connect a capacitor between VG and GND.                                                                                                                                                          |

| 21      | CTLSW    | Switching pin for control input signal. CTLSW= "High": DC control signal input mode<br>CTLSW="Low", PWM control signal input mode<br>Configuration should be performed according to control method.                                                       |

| 22      | SYNSEL   | Switching pin for synchronous rectification operation.<br>SYNSEL="High": Stop<br>SYNSEL="Low": Enable                                                                                                                                                     |

| 23      | F/R      | Switching pin for motor rotation direction. The order of energization to the motor is as follows:<br>"High" input: U→V→W<br>"Low" input: U→W→V By changing the order, rotation direction is switched. Do not switch operation while the motor is driving. |

Continue to the next page

## LV8850GA

Continue from the former page

| Pin No. | Pin name | Function                                                                                                                          |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------|

| 24      | RFGND    | GND for RF sensing for drive current detection. By connecting RFGND to RF (PIN25), drive current is detected with high precision. |

| 25      | RF       | RF sensing for drive current detection. By connecting RF to RFGND, drive current is detected.                                     |

| 26      | PGND     | GND for the IC.                                                                                                                   |

| 27      | WL       | Low-side pre-driver outputs.                                                                                                      |

| 29      | VL       | Make sure to connect Nch-Tr gate for motor drive to each pin. They outputs drive signal for the sink.                             |

| 31      | UL       |                                                                                                                                   |

| 28      | WH       | High-side pre-driver outputs.                                                                                                     |

| 30      | VH       | Make sure to connect Nch-Tr gate for motor drive to each pin. They outputs drive signal for the source.                           |

| 32      | UH       |                                                                                                                                   |

| 33      | WOUT     | Detection pin for motor back EMF voltage. Make sure to connect them to each phase of U,V,W of the motor.                          |

| 34      | VOUT     |                                                                                                                                   |

| 35      | UOUT     |                                                                                                                                   |

| 36      | COM      | Connection pin for motor midpoint.                                                                                                |

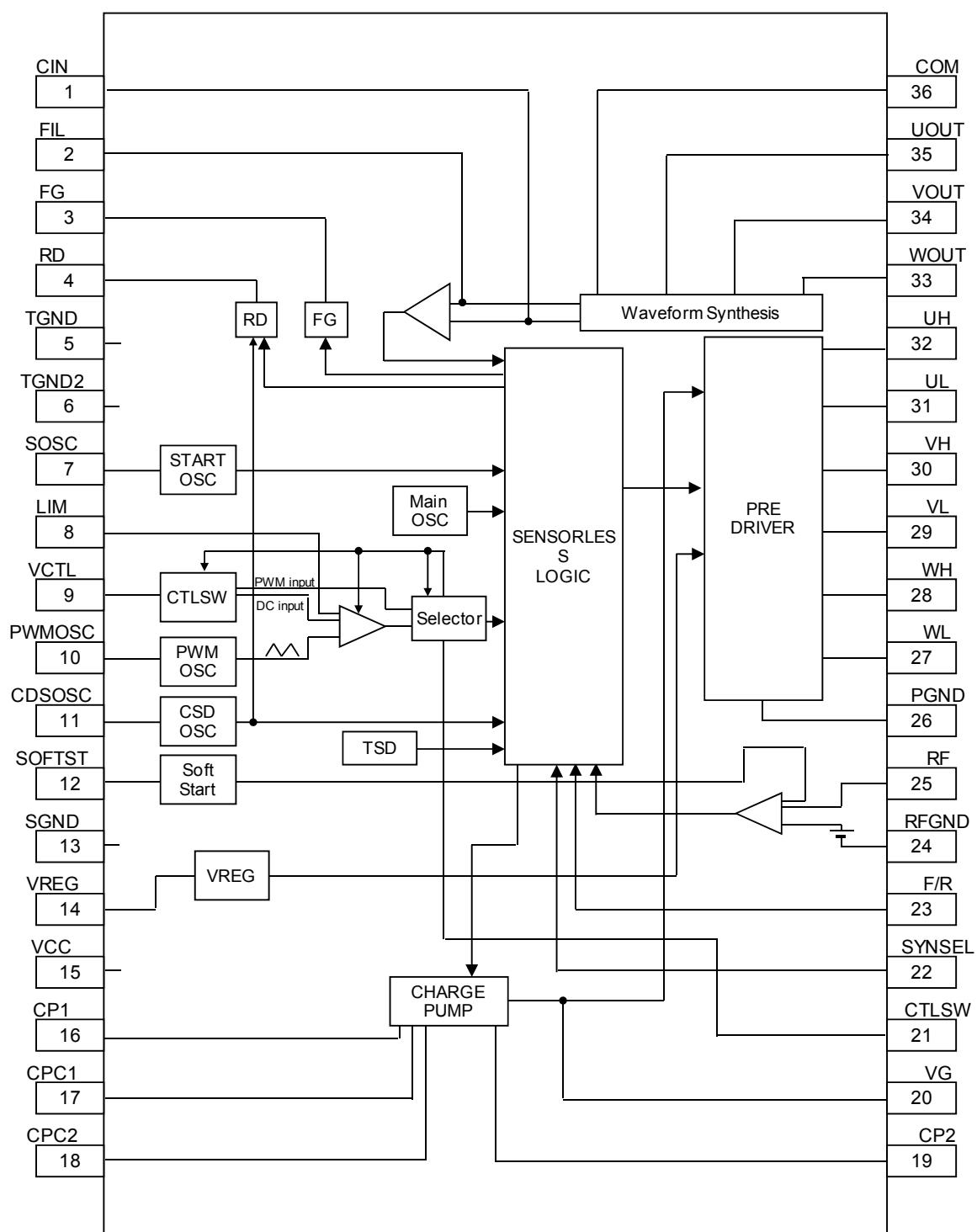

## Block Diagram

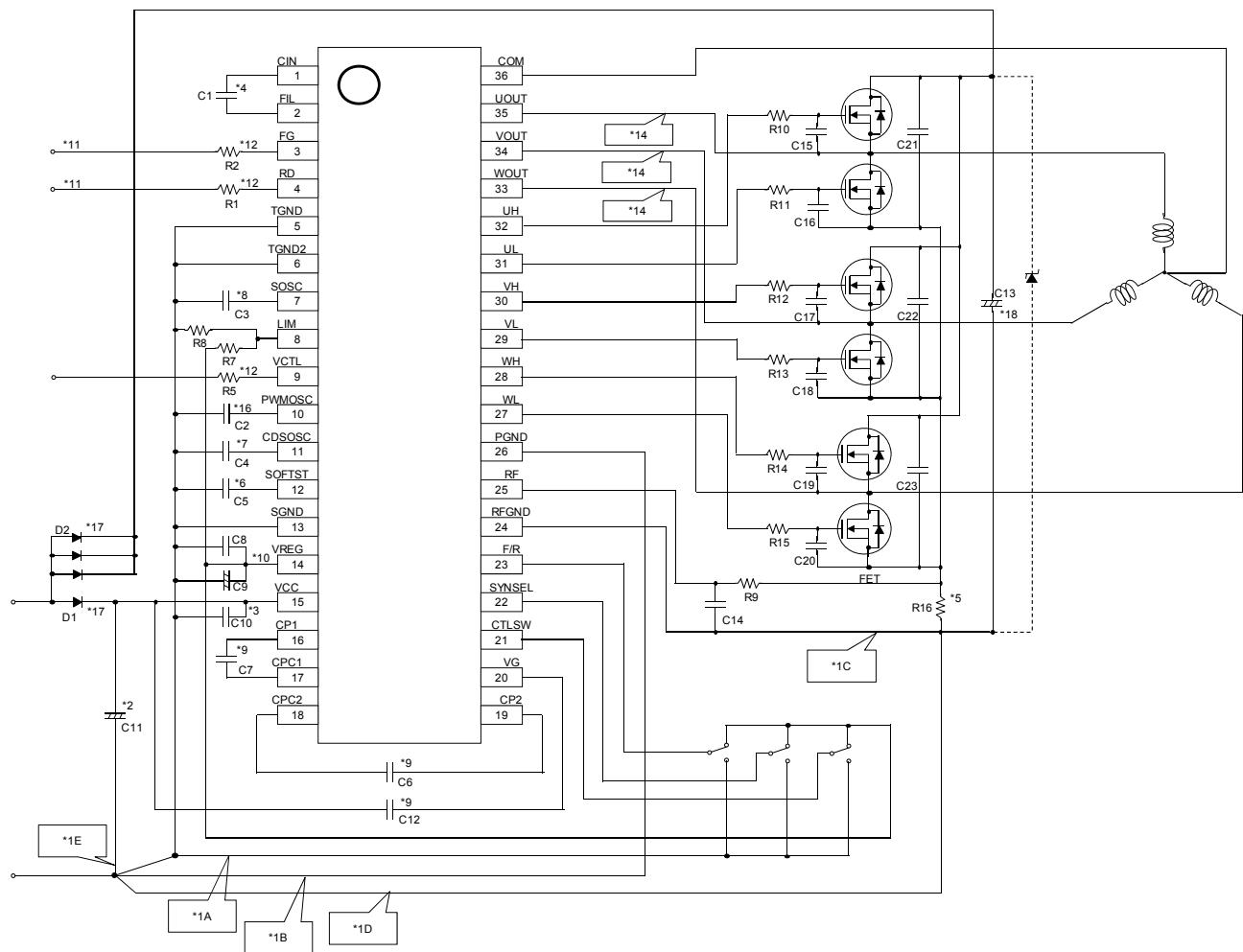

## Application Circuit Example

\* Each fixed number in the following FIG. is the referential value. Make sure to adjust it according to External-FETs and types of Motor.

|     |        |                        |     |          |                    |

|-----|--------|------------------------|-----|----------|--------------------|

| C1  | 1000pF | B-EMF detection filter | C14 | 470pF    | RF filter          |

| C2  | 470pF  | PWM oscillator         | C15 | 220pF    | FET                |

| C3  | 1000pF | Start-Up oscillator    | C16 | 220pF    | FET                |

| C4  | 2.2uF  | Lock-detection time    | C17 | 220pF    | FET                |

| C5  | 2.2uF  | Soft Start time        | C18 | 220pF    | FET                |

| C6  | 0.15uF | Charge pump            | C19 | 220pF    | FET                |

| C7  | 0.15uF | Charge pump            | C20 | 220pF    | FET                |

| C12 | 0.47uF | Charge pump            | C21 | 0.1uF    | FET                |

| C8  | 0.47uF | VREG                   | C22 | 0.1uF    | FET                |

| C9  | 10uF   | VREG                   | C23 | 0.1uF    | FET                |

| C10 | 0.1uF  | VCC                    | C13 | 33uF     | VM                 |

| C11 | 47uF   | VCC                    |     |          |                    |

| R1  | 100 Ω  | RD                     | R9  | 510 Ω    | RF filter          |

| R2  | 100 Ω  | FG                     | R10 | 330 Ω    | FET, gate resistor |

| R3  | 100k Ω | RD                     | R11 | 510 Ω    | FET, gate resistor |

| R4  | 100k Ω | FG                     | R12 | 330 Ω    | FET, gate resistor |

| R5  | 100 Ω  | Input signal           | R13 | 510 Ω    | FET, gate resistor |

| R7  | 100k Ω | LIM                    | R14 | 330 Ω    | FET, gate resistor |

| R8  | 100k Ω | LIM                    | R15 | 510 Ω    | FET, gate resistor |

|     |        |                        | R16 | 0.2 Ω    | RF resistor        |

| D1  | DSE010 |                        | FET | NTMD5836 | Nch / Nch          |

| D2  | DSP10  |                        |     |          |                    |

A value of these circuit fixed number is one example. Make sure to adjust it according to External-FETs and types of Motor.

\*1A, \*1B, \*1C, \*1D, \*1E .<GND line>

GND is classified as follows: SGND, PGND RFGND and MGND.

SGND (\*1A) : Small-signal (VREG4, TGND, TGND2, PWMOSC, SYNSEL, CTLSW, SGND, VCTL, LIM, SOFTS, F/R, CSDOSC, SOSC)

MGND (\*1B) : Middle-signal (PGND)

PGND (\*1D) : Power-signal (GND-side of RF-resistor, GND-side of bypass-capacitor for a Motor)

RFGND (\*1C) : Sensing-signal (RFGND)

When design a PCB layout, SGND(\*1A), MGND(\*1B) and PGND(\*1D) should be connected at a single GND with a capacitor (power supply stabilizer capacitor(\*1E)) between VCC and GND.

Power supply and GND should be connected as wide and short as possible. RFGND should be connected near the resistance which should be lined separately from the other GND line.

\*2.<Power supply stabilizer capacitor for power stabilization>

Power supply stabilization capacitor(C11) should be 10uF or higher.

\*3.<Noise rejection capacitor>

Noise rejection capacitor(C10) should be connected as short as possible.

\*4.<CIN, FIL pin>

Connection pin for filter capacitor. LV8850 detects rotor position using back-EMF (electromotive force) which is generated during rotation of the motor. Based on the information, energization timing for output pins are defined.

Problems in startup due to noise can be improved by connecting a filter capacitor (C1) between CIN and FIL.

If the capacitance is too high, energization timing of the output during high-speed rotation is delayed and efficiency is degraded. Make sure to connect capacitor between COMIN and FIL as short as possible to reject noise.

\*5.<RF pin>

Setting pin for current limiter. When pin voltage is higher than 0.21V, current is limited and recirculation mode is set. In the example of application circuit, current limiter is set at 1A. RF resistance (R16) is calculated as follows:

RF resistance = 0.21V/ desired current limit value.

If detection precision of current limit is low due to noise, make sure to insert a filter (R9, C14) between RF and RFGND.

\*6.<SOFTST pin>

Setting pin for soft start. Motor rotation count increases gradually by connecting a capacitor (C5) between SOFTST pin and SGND. The period of Soft-Start is calculated approximately as follows:

Period of Soft-Start  $\approx$  Capacitor value /  $380 \times 10^{-9}$

ex) In the case of Capacitor value = 2.2uF,

Then Period of Soft-Start  $\approx$  5.8s

\*7.<CSDOSC pin>

Capacitor connection pin for lock detection. It integrates constant current charger, constant current discharger circuit.

Lock protection time can be modified by connecting capacitor (C4) between CSDOSC and SGND. When it isn't used, then make sure to connect to SGND. The Period of Start-Up and Lock is calculated approximately as follows:

Period of Start-Up  $\approx$  Capacitor value \*  $0.43 \times 10^6$

Period of Lock  $\approx$  Capacitor value \*  $4.29 \times 10^6$

ex) In the case of Capacitor value = 2.2uF,

Then Period of Start-Up  $\approx$  0.9s

Period of Lock  $\approx$  9.4s

\*8.<SOSC pin>

Capacitor connection pin for setting startup frequency. Make sure to connect a capacitor (C3) between SOSC and SGND. The capacitor is required for SOSC pin to define frequency to start up motor.

Also make sure to confirm constant when you change motors or circuit specification because optimum value changes according to startup condition. The Frequency of SOSC is calculated approximately as follows:

Frequency of SOSC  $\approx$   $5 \times 10^{-6}$  / Capacitor value

ex) In the case of Capacitor value = 1000pF,

Then Frequency of SOSC  $\approx$  5kHz

\*9.<VG,CP1,CPC1,CP2,CPC2 pin>

Capacitor connection pin for pre-drive voltage generation and pre-drive power supply stabilizer. Make sure to connect capacitor to the pins because they generate voltage to drive upper output DMOS transistor. The layout should be as wide and short as possible.

\*10.<VREG pin>

Power supply pin for the internal control block. Regulator output pin to generate power supply for the control circuit. Make sure to connect capacitor (C8, C9) between VREG and SGND to stabilize operation of the control block. Make sure to connect the capacitor with greater capacitance than the one connected to the charge pump because it is used for power supply to the control block and to generate charge pump voltage.

\*11.<FG/RD pin>

Since FG, RD output are open-drain, it is recommended to connect pull-up resistance between FG and RD and the power supply for the controller.

\*12.<Noise rejection resistor>

Make sure to implement resistance (R1, R2, R5) for protection because the line is easily influenced by noise.

\*14.<UOUT,VOUT,WOUT,COM pin>

Back EMF detection pins. Make sure to line the pins as short as possible without crossing with the other lines.

\*15.<VCTL pin>

Make sure not to open.

\*16.<PWMSOC pin>

Capacitor connection pin for setting PWM frequency. When it is the “DC control signal input mode”, make sure to connect a capacitor (C2) between PWMSOC and SGND as short as possible. When it is the “PWM control signal input mode”, make sure to be open.

Also make sure to confirm constant when you change motors or circuit specification because optimum value changes according to motor rotation speed. The Frequency of PWM is calculated approximately as follows:

Frequency of PWM  $\approx 23 \times 10^{-6} / \text{Capacitor value}$

ex) In the case of Capacitor value = 470pF,

Then Frequency of PWM  $\approx 49\text{kHz}$

\*17.<Separation of power supply>

Make sure to insert a diode to prevent the inverted-current from a motor.

\*18.<Protection of VM (power supply for a motor)>

When the motor power supply voltage (VM) abnormally rises by environment to use, please insert a Zener diode between a motor power supply and motor GND.

## ORDERING INFORMATION

| Device      | Package                                      | Shipping (Qty / Packing) |

|-------------|----------------------------------------------|--------------------------|

| LV8850GA-AH | TSSOP36 (275mil)<br>(Pb-Free / Halogen Free) | 1000 / Tape & Reel       |

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at [www.onsemi.com/site/pdf/Patent-Marking.pdf](http://www.onsemi.com/site/pdf/Patent-Marking.pdf). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.