# Bi-CMOS IC For Brushless Motor Drive PWM Driver IC

http://onsemi.com

# **Overview**

The LV8824QA is a PWM pre-driver IC suitable for use in 3-phase brushless motors. This IC was designed based on the assumption that Nch FETs are used as the upper and lower output transistors. The rotational speed is controllable by inputting PWM pulse or DC voltage externally and changing duty. LV8824QA incorporates latch-type constraint protection circuit.

# **Features**

- $I_{O}$  max = 50mA

- Speed control and synchronous rectification by PWM direct input (3.3V input-ready) and DC voltage.

- 3-Hall FG output

- Latch type constraint protection circuit (latch is released by S/B and F/R.)

- Forward/reverse switch circuit, Hall bias pin

- Power saving circuit

- Current limiter circuit, Low-voltage protection circuit, Thermal shut-down circuit

- Charge pump circuit (external Nch/Nch), 5V regulator output.

- Start/Brake circuit

# **Specifications**

# **Absolute Maximum Ratings** at $Ta = 25^{\circ}C$

| Parameter                   | Symbol              | Conditions                    | Ratings     | Unit |

|-----------------------------|---------------------|-------------------------------|-------------|------|

| Supply voltage              | V <sub>CC</sub> max | V <sub>CC</sub> pin           | 34          | V    |

|                             | V <sub>G</sub> max  | V <sub>G</sub> pin            | 42          | ٧    |

| Output current              | I <sub>O</sub> max  |                               | 50          | mA   |

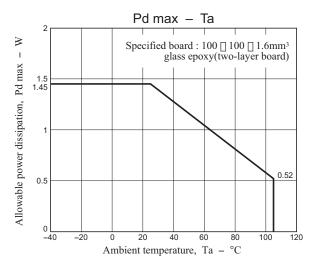

| Allowable power dissipation | Pd max              | Mounted on a circuit board.*1 | 1.45        | W    |

| Junction temperature        | Tj max              |                               | 150         | °C   |

| Operating temperature       | Topr                |                               | -40 to +105 | °C   |

| Storage temperature         | Tstg                |                               | -55 to +150 | °C   |

<sup>\*1 :</sup> Specified circuit board : 100mm × 100mm × 1.6mm, glass epoxy (double-layer board)

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Caution 1) Absolute maximum ratings represent the value which cannot be exceeded for any length of time.

Caution 2) Even when the device is used within the range of absolute maximum ratings, as a result of continuous usage under high temperature, high current, high voltage, or drastic temperature change, the reliability of the IC may be degraded. Please contact us for the further details.

# Allowable Operating range at Ta = 25°C

| Parameter                          | Symbol           | Conditions | Ratings   | Unit |

|------------------------------------|------------------|------------|-----------|------|

| Supply voltage range               | V <sub>CC</sub>  |            | 7.0 to 33 | V    |

| 5V constant voltage output current | I <sub>REG</sub> |            | 0 to -10  | mA   |

| HB pin output current              | I <sub>HB</sub>  |            | 0 to -200 | μΑ   |

| 3FG pin applied voltage            | V <sub>3FG</sub> |            | 0 to 6    | V    |

| 3FG pin output current             | l <sub>3FG</sub> |            | 0 to 10   | mA   |

# **Electrical Characteristics** at Ta = 25 °C, $V_{CC} = 24$ V

| Parameter                            | Cumbal                | Conditions                                          | Ratings              |                      |          | Unit  |  |

|--------------------------------------|-----------------------|-----------------------------------------------------|----------------------|----------------------|----------|-------|--|

| Parameter                            | Symbol                | Symbol                                              |                      | min typ max          |          | Unit  |  |

| Supply current 1                     | I <sub>CC</sub> 1     |                                                     |                      | 5.0                  | 6.0      | mA    |  |

| Supply current 2                     | I <sub>CC</sub> 2     | Power saving                                        |                      | 0.8                  | 0.98     | mA    |  |

| Output block (UH, VH, WH, UL, VL, V  | /L)                   |                                                     |                      |                      |          |       |  |

| Low-side output ON resistance 1      | R <sub>ON</sub> (L1)  | Low level I <sub>O</sub> = 10mA                     |                      | 20                   | 30       | Ω     |  |

| Low-side output ON resistance 2      | R <sub>ON</sub> (L2)  | High level I <sub>O</sub> = -10mA                   |                      | 20                   | 30       | Ω     |  |

| High-side output ON resistance 1     | R <sub>ON</sub> (H1)  | Low level I <sub>O</sub> = 10mA                     |                      | 25                   | 40       | Ω     |  |

| High-side output ON resistance 2     | R <sub>ON</sub> (H2)  | High level I <sub>O</sub> = -10mA                   |                      | 65                   | 90       | Ω     |  |

| 5V Constant-voltage Output           |                       |                                                     |                      |                      |          | •     |  |

| Output voltage                       | VREG                  | I <sub>O</sub> = -5mA                               | 4.8                  | 5.1                  | 5.4      | V     |  |

| Line regulation                      | ΔV (REG1)             | V <sub>CC</sub> = 7.0 to 33V, I <sub>O</sub> = -5mA |                      |                      | 50       | mV    |  |

| Load regulation                      | ΔV (REG2)             | I <sub>O</sub> = -5m to -10mA                       |                      |                      | 100      | mV    |  |

| Hall Amplifier                       |                       |                                                     |                      |                      | •        | •     |  |

| Input bias current                   | IB (HA)               |                                                     | -2                   |                      |          | μΑ    |  |

| Common-mode input voltage range 1    | VICM1                 | When using Hall elements                            | 0.3                  |                      | VREG-1.7 | V     |  |

| Common-mode input voltage range 2    | VICM2                 | At one-side input bias (Hall IC application)        | 0                    |                      | VREG     | V     |  |

| Hall input sensitivity               | VHIN                  | SIN wave                                            | 80                   |                      |          | mVp-p |  |

| Hysteresis width                     | ΔV <sub>IN</sub> (HA) |                                                     | 9                    | 20                   | 35       | mV    |  |

| Input voltage Low → High             | VSLH                  |                                                     | 3                    | 7.5                  | 15       | mV    |  |

| Input voltage High → Low             | VSHL                  |                                                     | -19                  | -11                  | -5       | mV    |  |

| CSD oscillator circuit               |                       |                                                     |                      |                      |          |       |  |

| High level output voltage            | V <sub>OH</sub> (CSD) |                                                     | 2.7                  | 3.0                  | 3.3      | V     |  |

| Low level output voltage             | V <sub>OL</sub> (CSD) |                                                     | 0.9                  | 1.1                  | 1.3      | V     |  |

| Amplitude                            | V (CSD)               |                                                     | 1.6                  | 1.9                  | 2.2      | Vp-p  |  |

| External capacitor charge current    | ICHG1 (CSD)           | VCHG1 = 2.0V                                        | -14                  | -11.5                | -9       | μΑ    |  |

| External capacitor discharge current | ICHG2 (CSD)           | VCHG2 = 2.0V                                        | 9.5                  | 12                   | 14.5     | μΑ    |  |

| Oscillation frequency                | f (CSD)               | C = 0.022μF (Design target*)                        |                      | 130                  |          | Hz    |  |

| Charge pump output (VG pin)          |                       |                                                     |                      |                      |          |       |  |

| Output voltage                       | VGOUT                 |                                                     | V <sub>CC</sub> +6.5 | V <sub>CC</sub> +7.0 |          | V     |  |

| CP1 pin                              |                       |                                                     |                      |                      |          |       |  |

| Output ON resistance (High level)    | V <sub>OH</sub> (CP1) | ICP1 = -2mA                                         |                      | 350                  | 500      | Ω     |  |

| Output ON resistance (Low level)     | V <sub>OL</sub> (CP1) | ICP1 = 2mA                                          |                      | 200                  | 280      | Ω     |  |

| Charge pump frequency                | f (CP)                |                                                     | 82                   | 103                  | 124      | kHz   |  |

| Internal PWM frequency               |                       |                                                     |                      |                      |          |       |  |

| Oscillation frequency                | f (PWM)               |                                                     | 41                   | 51.5                 | 62       | kHz   |  |

| Current limiter operation            |                       |                                                     |                      |                      |          |       |  |

| Limiter voltage                      | VRF                   |                                                     | 0.18                 | 0.20                 | 0.22     | V     |  |

|                                      |                       |                                                     |                      |                      |          |       |  |

<sup>\*:</sup> Design target value and no measurement is made.

Continued on next page.

| Continued from preceding page.     |                               |                                       |          | Ratings  |                 |          |

|------------------------------------|-------------------------------|---------------------------------------|----------|----------|-----------------|----------|

| Parameter                          | Symbol                        | Conditions                            | min      | typ      | max             | Unit     |

| PWM oscillator                     |                               |                                       | 1        | 31       |                 | I        |

| Output High level voltage          | V <sub>O</sub> H(PWM)         |                                       | 2.8      | 3.05     | 3.3             | V        |

| Output Low level voltage           | V <sub>O</sub> L(PWM)         |                                       | 0.85     | 1.0      | 1.15            | V        |

| Amplitude                          | V(PWM)                        |                                       | 1.7      | 2.0      | 2.3             | Vp-p     |

| External C charge current          | I <sub>CHG</sub> 1(PWM)       | V <sub>CHG</sub> 1 = 2.0V             | -135     | -110     | -85             | μА       |

| External C discharge current       | I <sub>CHG</sub> 2(PWM)       | V <sub>CHG</sub> 2 = 2.0V             | 1.4      | 1.8      | 2.2             | mA       |

| Oscillation frequency              | f(PWM)                        | C = 2200pF (Design target*)           |          | 25       |                 | kHz      |

| CTL input voltage                  |                               |                                       | ı        |          |                 | Į        |

| Input voltage 1                    | V <sub>CTL</sub> 1            | Output Duty 100%                      | 2.79     | 3.1      | 3.4             | V        |

| Input voltage 2                    | V <sub>CTL</sub> <sup>2</sup> | Output Duty 0%                        | 0.84     | 1.05     | 1.3             | V        |

| Thermal shutdown operation         | 1 0.2                         | -                                     | ı        |          |                 | Į        |

| Operation temperature              | TSD                           | Design target* (Junction temperature) | 150      | 170      |                 | °C       |

| Hysteresis width                   | ΔTSD                          | Design target* (Junction temperature) |          | 30       |                 | °C       |

| HB pin                             |                               |                                       |          |          |                 |          |

| Output voltage                     | VHB                           | IHB = -100μA                          | 3.6      | 3.8      | 4.0             | V        |

| Low-voltage protection (5V constar | nt voltage output dete        | ection)                               | 1        |          |                 | I        |

| Operation voltage                  | VSD                           |                                       | 3.95     | 4.15     | 4.35            | V        |

| Hysteresis width                   | ΔVSD                          |                                       | 0.2      | 0.3      | 0.4             | V        |

| 3FG pin                            | 1                             | 1                                     | 1        | <u> </u> | <u> </u>        | 1        |

| Output ON resistance               | V <sub>O</sub> L (3FG)        | I3FG = 5mA                            |          | 30       | 45              | Ω        |

| Output leakage current             | IL (3FG)                      | V <sub>O</sub> = 6V                   |          |          | 10              | μΑ       |

| STIME pin                          | , ,                           | Ü                                     |          |          |                 |          |

| Input threshold voltage 1          | V <sub>I</sub> 1(TIME)        |                                       | 0        |          | 1.0             | V        |

| Input threshold voltage 2          | V <sub>I</sub> 2(TIME)        |                                       | 1.5      |          | 2.25            | V        |

| Input threshold voltage 3          | V <sub>I</sub> 3(TIME)        |                                       | 2.8      |          | 3.5             | V        |

| Input threshold voltage 4          | V <sub>I</sub> 4(TIME)        |                                       | 4.2      |          | VREG            | V        |

| MODE pin                           | 1 ( )                         |                                       | 1        |          |                 |          |

| Input threshold voltage 1          | V <sub>I</sub> 1(MODE)        |                                       | 0        |          | 1.0             | V        |

| Input threshold voltage 2          | V <sub>I</sub> 2(MODE)        |                                       | 1.5      |          | 2.25            | V        |

| Input threshold voltage 3          | V <sub>I</sub> 3(MODE)        |                                       | 2.8      |          | 3.5             | V        |

| Input threshold voltage 4          | V <sub>I</sub> 4(MODE)        |                                       | 4.2      |          | VREG            | V        |

| S/B pin                            | 1 \ /                         |                                       |          |          |                 |          |

| High level input voltage           | V <sub>IH</sub> (SB)          |                                       | 2.0      |          | VREG            | V        |

| Low level input voltage            | V <sub>IL</sub> (SB)          |                                       | 0        |          | 1.0             | V        |

| Input open voltage                 | V <sub>IO</sub> (SB)          |                                       | VREG-2.2 | VREG-2.0 | VREG-1.8        | V        |

| Hysteresis width                   | V <sub>IS</sub> (SB)          |                                       | 0.25     | 0.33     | 0.4             | V        |

| High level input current           | I <sub>IH</sub> (SB)          | V <sub>SB</sub> = VREG                | 45       | 65       | 85              | μΑ       |

| Low level input current            | I <sub>IL</sub> (SB)          | V <sub>SB</sub> = 0V                  | -125     | -95      | -65             | μA       |

| PWMIN pin                          | IL V                          | 65                                    |          |          |                 |          |

| Recommended input frequency        | f (PWIN)                      |                                       | 0.5      |          | 60              | kHz      |

| High level input voltage           | V <sub>IH</sub> (PWIN)        |                                       | 2.0      |          | VREG            | V        |

| Low level input voltage            | V <sub>IL</sub> (PWIN)        |                                       | 0        |          | 1.0             | V        |

| Input open voltage                 | V <sub>IO</sub> (PWIN)        |                                       | VREG-2.2 | VREG-2.0 | VREG-1.8        | V        |

| Hysteresis width                   | V <sub>IS</sub> (PWIN)        |                                       | 0.25     | 0.33     | 0.4             | V        |

| High level input current           | I <sub>IH</sub> (PWIN)        | VPWIN = VREG                          | 45       | 65       | 85              | μA       |

| Low level input current            | I <sub>IL</sub> (PWIN)        | VPWIN = 0V                            | -125     | -95      | -65             | μА       |

| F/R pin                            | 1 15 ( )                      | <u> </u>                              | 1        | 1        |                 | <u> </u> |

| High level input voltage           | V <sub>IH</sub> (FR)          | *Design target value                  | 2.0      |          | VREG            | V        |

| Low level input voltage            | V <sub>IL</sub> (FR)          | *Design target value                  | 0        |          | 1.0             | V        |

| Input open voltage                 | V <sub>IO</sub> (FR)          | _ 55.5 351 14140                      | VREG-2.2 | VREG-2.0 | VREG-1.8        | V        |

| Hysteresis width                   | V <sub>IS</sub> (FR)          | *Design target value                  | 0.25     | 0.33     | 0.4             | V        |

| 11701010010 WIGHT                  |                               | Doolgii targot value                  |          |          | U. <del>4</del> |          |

| High level input current           | I <sub>IH</sub> (FR)          | VF/R = VREG                           | 45       | 65       | 85              | μΑ       |

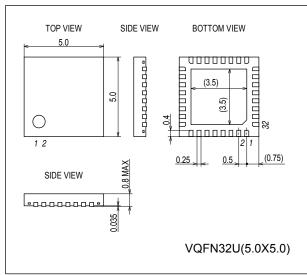

# **Package Dimensions**

unit: mm (typ)

3436

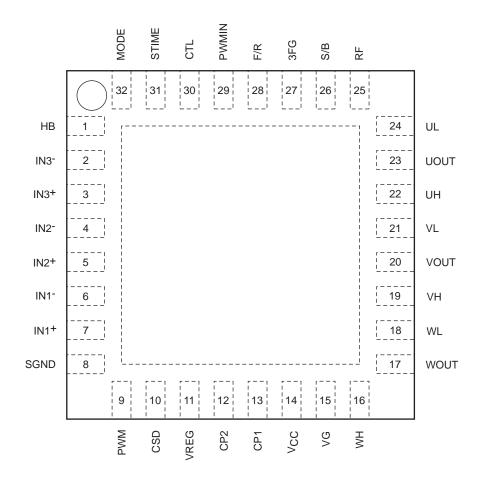

# **Pin Assignment**

# Three-phase HALL logic truth table (IN = "High" means the following state: IN+ > IN-.)

("Upper gate = VH" and "lower gate = UL" mean the following state: the upper FET connected to VH pin is on and the lower FET connected to UL pin operates by PWM signal.)

|     | F/R = High |     |     | F/R = Low |     | Driving    | goutput          |

|-----|------------|-----|-----|-----------|-----|------------|------------------|

| IN1 | IN2        | IN3 | IN1 | IN2       | IN3 | Upper gate | Lower gate (PWM) |

| Н   | L          | Н   | L   | Н         | L   | VH         | UL               |

| Н   | L          | L   | L   | Н         | Н   | WH         | UL               |

| Н   | Н          | L   | L   | L         | Н   | WH         | VL               |

| L   | Н          | L   | Н   | L         | Н   | UH         | VL               |

| L   | Н          | Н   | Н   | L         | L   | UH         | WL               |

| L   | L          | Н   | Н   | Н         | L   | VH         | WL               |

|     | 3FG output |     |     |  |  |

|-----|------------|-----|-----|--|--|

| IN1 | IN2        | IN3 | 3FG |  |  |

| Н   | L          | Н   | L   |  |  |

| Н   | L          | L   | Н   |  |  |

| Н   | Н          | L   | L   |  |  |

| L   | Н          | L   | Н   |  |  |

| L   | Н          | Н   | L   |  |  |

| L   | L          | Н   | Н   |  |  |

# S/B pin, PWMIN pin

| Input state  | S/B pin            | PWMIN pin  |

|--------------|--------------------|------------|

| High or Open | Stop (short brake) | Output OFF |

| Low          | Start              | Output ON  |

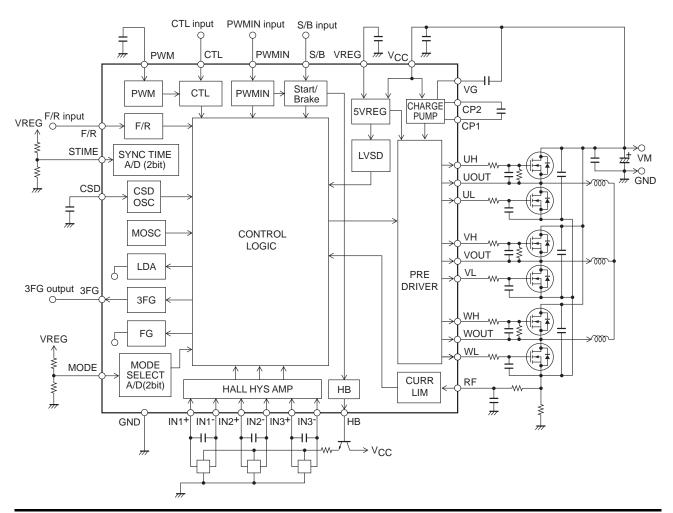

# Internal Equivalent Circuit and Sample External Component Circuit

# **Pin Functions**

| Pin No.                    | Pin Name                                                                                              | Pin function                                                                                                                                                                                                                                                                                                                                           | Equivalent Circuit                                                                 |

|----------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 1                          | НВ                                                                                                    | Hall bias pin (3.8Vtyp output). Connect NPN transistor. (See P.11"9.Hall input signal".) During power saving mode, output is turned off (0V). HB pin enable to reduce power consumption of Hall element to 0V during power saving mode.                                                                                                                | VREG $30\Omega$                                                                    |

| 2<br>3<br>4<br>5<br>6<br>7 | IN3 <sup>-</sup> IN3 <sup>+</sup> IN2 <sup>-</sup> IN2 <sup>+</sup> IN1 <sup>-</sup> IN1 <sup>+</sup> | Hall input pin.  Where IN <sup>+</sup> > IN <sup>-</sup> , voltage level becomes High. Where IN <sup>+</sup> < IN <sup>-</sup> , voltage level becomes Low.  Desirably, the amplitude of Hall signal is 100mVp-p (differential) or higher.  If the noise of Hall signal is an issue, connect a capacitor between IN <sup>+</sup> and IN <sup>-</sup> . | VREG<br>3<br>500Ω<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7 |

| 8                          | SGND                                                                                                  | Ground pin for control circuitry.                                                                                                                                                                                                                                                                                                                      |                                                                                    |

| 9                          | PWM                                                                                                   | Triangular wave oscillation pin for PWM signal generation.  Connect a capacitor between this pin and GND.  (See P.9 "4. PWM oscillation frequency.")                                                                                                                                                                                                   | VREG  200Ω  9                                                                      |

| 10                         | CSD                                                                                                   | Timing setting pin for constraint protection detection as well as setting pin for initial reset pulse.  Connect a capacitor between this pin and GND.  When protection circuitry is not used, connect a resistor of 220kΩ and capacitor of 4700pF in parallel against GND.  (See P.10 "5. Constraint protection circuit")                              | VREG 500Ω 10                                                                       |

| 11                         | VREG                                                                                                  | 5V regulator output pin (power supply for control circuitry).  Desirably, connect a capacitor of 0.1μF between this pin and GND for stabilization.  (See P.10 "8. VREG stabilization" and P.12 "15. Low voltage protection circuit")                                                                                                                   | VCC 30Ω 111                                                                        |

Continued on next page.

Continued from preceding page. Pin No. Pin Name Pin function **Equivalent Circuit** CP2 Capacitor connect pin for charge pump. 12 13 CP1 Connect a capacitor between CP1 and VCCCP2 14  $V_{CC}$ Supply pin for control.  $150\Omega$ Connect a capacitor between this pin and GND to reject noise. ‡ CG (See P.12 "14. Supply stabilization") VG 15 Charge pump output pin. (Power supply for upper FET gate.) Connect a capacitor between this pin and  $V_{CC}$ . (See P.10 "7. Charge pump circuit") WH 16 High side output pin. ۷G 19 (Output pin for gate driver of upper side 22 UH Nch power FET.) (See P.9 "1. Output driving circuit.") 17 WOUT Voltage detection pin. 20 VOUT (Source voltage detection pin of upper UOUT 23 side Nch power FET.") (See P.9 "1. Output driving circuit.") WL 18 Low side output pin. **VREG** 21 VΙ (Output pin for gate driver of lower side 24 UL Nch power FET.) 25 RF Output current detection pin. Connect a detection resistor (R<sub>F</sub>) between this pin and GND. Current limit value is obtained as follow:  $I = VRF / R_F (VREF = 0.2Vtyp).$ (See P.9 "2. Current limiter circuit") 5kΩ 26 S/B Start/Brake selector pin. "High or OPEN": Short brake. "Low": Start **VREG** (See P.12 "13. Power saving circuit") 28 F/R Selects forward/reverse rotation. 50kΩ ≸ Voltage level becomes High when this pin is open. 29 **PWMIN** PWM direct input pin. 75kΩ ≸ Output is controllable by the duty of the input pulse. When using PWMIN pin, make sure that CTL pin is set to High level voltage. (See P.9 "3. Speed control method") 3FG 3 Hall FG signal output pin. 27 Open drain output.

Continued on next page.

| Pin No. | Pin Name | Pin function                                                                                                                                                                                                           | Equivalent Circuit        |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 30      | CTL      | Control input pin. Output On-duty is controllable using the comparison result of CTL pin voltage and PWM oscillation waveform. To use CTL pin, set PWMIN pin to Low level voltage. (See P.9 "3. Speed control method") | VREG 500Ω 30              |

| 31      | STIME    | Dead-time setting pin for synchronous rectification.  Depends on input voltage to STIME pin, 4 types of mode are selectable.  (See P.10 "6. How to set STIME")                                                         | VREG  500Ω  500Ω  31)(32) |

| 32      | MODE     | Operation MODE setting pin. Depends on input voltage to MODE pin, 4 types of mode are selectable. (See P.11 "10. MODE pin")                                                                                            |                           |

# Overview of LV8824QA

# 1. Output driving circuit

LV8824QA is designed to use Nch FETs for upper and lower output. It adopts direct PWM driving method to reduce the power loss during output. You can adjust motor torque by changing the duty cycle of the output of lower FET. Make sure to connect capacitor at the proximity of each 3-phase output FET to prevent high frequency oscillation caused by leading pattern layout around the board (approx. 0.1µF between Supply and RF).

If the ON speed of FET is too fast, penetration current may flow. In this case, insert serial resistors to a gate to control speed. On the other hand, if excessively high resistor is inserted to the gate, the waveform of the gate can be distorted and when the duty cycle of PWM is low, gate voltage becomes insufficient and lower side FET may be damaged or destroyed by heat generation.

Or even without resistance, the same phenomenon as what happens with high gate capacitor for FET could occur. In this case, make sure to take ASO of the switching element into consideration and limit the usage lowest duty. Depends on types of FET, penetration current may flow when the duty cycle of PWM is low. As a countermeasure, you can insert capacitor between the gate and the source of the upper FET. However, caution is required since excessively high capacitor value slows down the speed of switching which may cause heat generation in the upper FET.

# 2. Current Limiter Circuit

The peak current of current limiter circuit is limited by the current determined as follows. I = VRF/RF ( $V_{RF}$  = 0.2V (typical),  $R_F$ : current detection resistance). Current is limited as the duty cycle of output of UL, VL and WL lowers. The operation of current limiter circuit is delayed approximately for 1.5 $\mu$ s to avoid operation error of current limiter when it mistakenly detects reverse current of diode driven by PWM. However, if the coil resistance or inductance of motor is too small, such delay may operate current limiter at higher current than the setting value because the current charge when starting up motor rotation is too fast (without back EMF of the motor). Hence, make sure to set current limiter value taking such increase of current caused by delay into consideration.

If noise leads to error operation, make sure to insert a filter.

\*PWM frequency of current limiter circuit.

The PWM frequency of current limiter circuit is determined by the internal reference oscillator which is approx 50kHz.

# 3. Speed control method

The speed control input of LV8824 supports digital and analog input.

# (1) Digital input

You can control output by the duty obtained as a result of inputting pulse to PWMIN pin.

PWMIN pin:

Low level input voltage → PWM side (lower side) output ON

High level input voltage → PWM side (lower side) output OFF

If you need to perform input with logic inversion, add external Tr (NPN).

If the input of PWMIN pin is at High level for a certain period (approx. 2.5ms), it is judged to be Duty = 0%. When power saving mode is selected, HB pin output is set to Low level.

\*To use PWMIN pin, make sure to set CTL input to High level voltage.

### (2) Analog input

Based on the comparison between CTL pin voltage and PWM oscillation waveform, you can control the duty cycle of output. By adjusting the CTL pin voltage approximately between 1V and 3V, on time of duty cycle is controllable from 0% to 100%.

When CTL pin voltage < 1.05V (typ) is observed for approximately 2.5ms, the duty is judged to be 0%. If power saving mode is selected, HB pin output turns Low level.

\*To use CTL pin, make sure to set PWMIN input to Low level voltage.

# 4. PWM oscillation frequency

PWM oscillation frequency is configurable by the capacitance (CPWM) connected to PWM pin.

PWM oscillation frequency (kHz)  $\approx 48 - 10.2 * CpWM (nF)$

When the capacitor of 2.2nF is connected, PWD oscillation frequency is approximately 25kHz.

### 5. Constraint protection circuit

LV8824 includes a constraint protection circuit to protect the IC and the motor that are under motor constraint mode. This circuit operates when the motor is under operation and the Hall signal does not switch over a certain period of time. Note that while this constraint protection circuit is under operation, lower side output transistor is off. Also during power saving mode, HB pin output is off.

(See P.15 "10. MODE pin" and P.16 "12. HB pin" for further details.)

Time is set by the value of capacitor connected the CSD pin.

Set time (s)

$$\approx 90 \times C (\mu F)$$

When the capacitor of 0.022µF is connected, the protection time becomes approximately 2.0 seconds. The set time should allow margin taking motor startup time into consideration.

| Conditions for releasing constraint protection state                | Conditions for restarting motor rotation            |

|---------------------------------------------------------------------|-----------------------------------------------------|

| S/B pin: H input (during power saving mode*1)                       | S/B pin: L input *2                                 |

| S/B pin: H input (during FG output mode *1)                         | S/B pin: L input                                    |

| F/R pin: input H/L switch                                           | (immediately after releasing constraint protection) |

| After Duty = 0% is detected from PWM input and Duty Up is detected. | (immediately after releasing constraint protection) |

| Low voltage protection circuit is in operation.                     | After the recovery from low voltage state *2        |

# \*1 See P.15"10. MODE pin"

If thermal shutdown is running under the constraint protection, even after the temperature decreases, the constraint protection state continues.

CSD pin also functions as initial reset generation pin. If it is connected to GND, the logic circuit will go into a reset state and speed control cannot be performed. Therefore, when you do not use constraint protection, connect a resistor of approximately  $220k\Omega$  and a capacitor of approximately 4700pF in parallel to GND.

# 6. How to set STIME

STIME pin sets Dead-time for synchronous rectification.

This IC has the time for preventing "shoot-through current" when it makes synchronous rectification.

4 types of dead-time are configurable according to the input voltage to STIME pin.

| S | TIME pin input voltage | Dead-time                         |

|---|------------------------|-----------------------------------|

| • | 0V to 1.0V             | $\rightarrow$ approx. 2.0 $\mu$ s |

| • | 1.5V to 2.25V          | → approx. 1.5µs                   |

| • | 2.8V to 3.5V           | $\rightarrow$ approx. 1.0 $\mu$ s |

| • | 4.2V to (VREG)V        | → approx. 0.5µs                   |

# 7. Charge pump Circuit

Charge pump circuit boosts the voltage to generate gate voltage in the upper-side output FET. The capacitor CP connected between CP1 pin and CP2 boosts the voltage which is stored in the capacitor CG between VG pin and V<sub>CC</sub> pin. The relation of CP and CG capacitance should be as follows:

$$CG \ge 4 \times CP$$

The charge and discharge to CP capacitor is performed in the cycle of 100kHz. The greater the CP capacitor is, the higher the current capability of VG supply become. However, if the capacitance is too large, the charge and discharge operation becomes insufficient. Likewise, the larger the CG capacitor is, the more stable VG voltage becomes. However, if the capacitance is too large, generation time of VG voltage becomes longer at power supply. Hence,

caution is required for setting capacitance.

The desirable capacitances of CP and CG are follows.

$$CP = 0.1\mu F$$

$$CG = 0.47\mu F$$

### 8. VREG Stabilization

Make sure to connect capacitor of 0.1µF higher to stabilize VREG voltage which is used as supply voltage to control circuit. In the layout, GND of the capacitor should be as close as possible to the GND pin of the IC.

<sup>\*2</sup> Since this is an initial reset state, after satisfying the conditions for restarting motor operation where CSD pin voltage reaches to the defined voltage level, the motor starts up once again. The time for restart is approximately 1.0ms if the capacitor of  $0.022\mu F$  is connected to CSD pin.

# 9. Hall Input Signal

The amplitude of Hall input should be higher than the hysteresis width (35mV max).

The amplitude should be 100mVp-p or higher to take the influence of noise and phase gap into consideration. If output wave form is distorted by noise when switching from one phase to another, make sure to insert capacitor between hall inputs. In constraint protection circuit, Hall input is used as judgment signal. Although the circuit ignores noise to a certain level, caution is still required. If all 3 phases of Hall input signal turn to the same input state (HHH or LLL), all of the outputs are turned off. If you use Hall IC, by fixing one input side (either + or -) to the voltage within the range of common-mode input (0.3V to VREG-1.7V), the other input side accepts input from 0V to VREG.

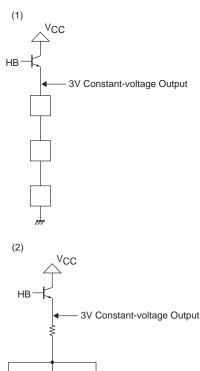

### Connection of Hall elements

Connection (1) (where three Hall elements in serial connection) Merit

- Compared to parallel connection, current consumption is less because serial connection enables sharing current among 3 Hall elements.

- Current limiter resistance is reducible.

- Amplitude variation caused by temperature is less.

### Demerit

- Amplitude may not be sufficient because each Hall element is powered with 1V only.

- Current may fluctuate depends on temperature.

- HALL amplitude tends to be affected by the fluctuation of Hall elements (especially for input resistor).

Connection (2) (three Hall elements in parallel connection) Merit

- The current for Hall elements is adjustable with current limiter resistance.

- Amplitude is sufficient because supply voltage to Hall elements is adjustable.

### Demerit

- Current consumption is large because each Hall element requires current independently.

- Requires resistor for current limiter.

- Amplitude may fluctuate depends on temperature.

# 10. MODE pin

MODE pin allows selecting functions of the IC.

MODE pin sets 4 functions based on input voltage.

| MODE pin input voltage |                 | mode                                     |  |

|------------------------|-----------------|------------------------------------------|--|

| •                      | 0V to 1.0V      | $\rightarrow$ mode B & power saving mode |  |

| •                      | 1.5V to 2.25V   | $\rightarrow$ mode B & FG output mode    |  |

| •                      | 2.8V to 3.5V    | $\rightarrow$ mode A & FG output mode    |  |

| •                      | 4.2V to (VREG)V | $\rightarrow$ mode A & power saving mode |  |

|                                                                                               | mode A (suitable for fan)                            | mode B (suitable for office equipments) |  |

|-----------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------|--|

| When Duty cycle = 0% is detected                                                              | Synchronous rectifier OFF (free operation)           | Short brake                             |  |

| When frequency of PWM input is low (approx. 7.5kHz or lower)                                  | Synchronous rectifier OFF                            | Synchronous rectifier ON                |  |

| When the Duty cycle of PWM input is low<br>(ex. Frequency: 20kHz,<br>Duty cycle: 3% or lower) | Synchronous rectifier OFF                            | Synchronous rectifier ON                |  |

| Reverse current detection function                                                            | Yes (during detection, synchronous rectifier is OFF) | No                                      |  |

Power saving mode: When S/B pin = Brake, power saving mode is set. When Duty = 0% is detected as well as when constraint protection circuit is in operation, HB pin output is turned OFF.

(See "12. HB pin" and "13. Power saving circuit" for further details.)

DG output is always feasible since FG output mode: Power saving mode and HB pin output OFF are not set.

# 11. How to see STIME pin and MODE pin

The input voltage of STIME pin and MODE pin are configurable by the following methods.

● 0V to 1.0V → short-circuit the pins to GND

ullet 4.2V to (VREG)V ullet Leave the pins open or short-circuit VREG.

### 12. HB pin \*When power saving mode is selected.

HB pin is used to reduce current to Hall elements during standby mode (for power saving).

After the motor operation is stopped, HB pin output is turned off in the following states:

- When S/B is in brake mode.

- When duties of the input of PWMIN and CTL pin voltage are 0%.

- When constraint protection circuit is under operation.

# 13. Power Saving Circuit (Start/Brake circuit) \*When power saving mode is selected.

In brake state, after the motor is stopped, majority of the circuits are stopped to reduce current consumption. By using HB pin, current consumption during power saving is less than 1mA. Also, the output is fixed to short-brake state (lower-side is shorted). Even in the power saving state, 5V regulator voltage is output.

# 14. Supply Stabilization

The supply line of LV8824 is unstable because it adopts switching driving method. Hence, you need to connect sufficient capacitor between  $V_{CC}$  and GND to stabilize power supply (electrolysis capacitor). If such capacitor (electrolytic capacitor) cannot be connected at the proximity of the pin, make sure to insert a ceramic capacitor of approx.  $0.1\mu F$  by the pin.

If you insert diode to supply line to prevent reverse connection, make sure to select a larger capacitor.

# 15. Low voltage protection circuit

This IC incorporates comparator which uses band gap voltage as reference. Where S/B pin is at Low voltage level, VREG pin voltage (5V) is monitored and when this voltage decreases to 4.15V or lower (typ), protection circuit operates.

In this case, output transistor of each phase is fixed to the following states according to the input voltage of MODE pin and S/B pin.

| MODE pin input voltage | S/B pin input voltage | Source side | Sink side |

|------------------------|-----------------------|-------------|-----------|

| 0V to 2.25V            | L/H                   | All OFF     | All ON    |

| 0.0V/+- (V/DEO)V/      | Н                     | All OFF     | All ON    |

| 2.8V to (VREG)V        | L                     | All OFF     | All OFF   |

# 16. Thermal shutdown Circuit

When the junction temperature of the IC exceeds 170°C (design target), thermal shutdown circuit operates and all the output transistors are turned off.

When the temperature decreases by 30°C (design target), each output transistor returns to operation state. However, the thermal shutdown operates when a junction temperature exceeds the ratings and this does not protect an application against breakdown.

# 17. Exposed die pad

The exposed die pad should be GND or open.

# 18. Cautions for usage

This IC operates at synchronous rectification for high efficiency.

The synchronous rectification is effective for reducing heat generation and improving efficiency because it reduces the loss of output transistor.

However, synchronous rectification may increase supply voltage depends on usage conditions.

- If output duty decreases drastically.

- If PWM input frequency is low, etc.

To prevent the voltage to exceed the maximum ratings as a result of increased supply voltage, following measures are highly recommended.

- Select an optimum capacitor between power supply and GND.

- Insert a Zener diode between power supply and GND.

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa