## SONY

Diagonal 8mm (Type 1/2) Progressive Scan CCD Image Sensor with Square Pixel for B/W Cameras

# ICX267AL

#### **Description**

The ICX267AL is a diagonal 8mm (Type 1/2) interline CCD solid-state image sensor with a square pixel array and 1.45M effective pixels. Progressive scan allows all pixels' signals to be output independently. Also, the adoption of high frame rate readout mode supports 30 frames per second. This chip features an electronic shutter with variable charge-storage time which makes it possible to realize full-frame still image without a mechanical shutter. High resolution and high low dark current are achieved through the adoption of HAD (Hole-Accumulation Diode) sensors.

(Applications: Electronic still cameras, PC input cameras, etc.)

#### **Features**

- ◆ Progressive scan allows individual readout of the image signals from all pixels.

- ◆ High horizontal and vertical resolution (both approx. 1024TV-lines) still image without a mechanical shutter.

- ◆ Supports high frame rate readout mode (effective 512 lines output, 30 frames/s)

- ◆ Square pixel

- ◆ Horizontal drive frequency: 28.636MHz

- ♦ No voltage adjustments (Reset gate and substrate bias need no adjustment.)

- ◆ High resolution, high color reproductivity, high sensitivity, low dark current

- ◆ Low smear, excellent antiblooming characteristics

- ◆ Continuous variable-speed shutter

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

- 1 -

E01Y03C88-CR

SONY ICX267AL

#### **Device Structure**

◆ Interline CCD image sensor

♦ Image size : Diagonal 8mm (Type 1/2)

◆ Total number of pixels

★ Number of effective pixels

∴ 1434 (H) × 1050 (V) approx. 1.50M pixels

∴ 1392 (H) × 1040 (V) approx. 1.45M pixels

♦ Number of active pixels : 1360 (H) × 1024 (V) approx. 1.40M pixels (7.959mm diagonal)

♦ Chip size : 7.60mm (H) × 6.20mm (V) ♦ Unit cell size : 4.65μm (H) × 4.65μm (V)

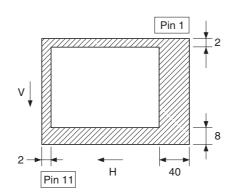

◆ Optical black : Horizontal (H) direction : Front 2 pixels, rear 40 pixels

Vertical (V) direction : Front 8 pixels, rear 2 pixels

◆ Number of dummy bits : Horizontal 20

Vertical 3

◆ Substrate material : Silicon

## **Optical Black Position**

(Top View)

#### **USE RESTRICTION NOTICE**

This USE RESTRICTION NOTICE ("Notice") is for customers who are considering or currently using the CCD image sensor products ("Products") set forth in this specifications book. Sony Corporation ("Sony") may, at any time, modify this Notice which will be available to you in the latest specifications book for the Products. You should abide by the latest version of this Notice. If a Sony subsidiary or distributor has its own use restriction notice on the Products, such a use restriction notice will additionally apply between you and the subsidiary or distributor. You should consult a sales representative of the subsidiary or distributor of Sony on such a use restriction notice when you consider using the Products.

#### **Use Restrictions**

- ◆ The Products are intended for incorporation into such general electronic equipment as office products, communication products, measurement products, and home electronics products in accordance with the terms and conditions set forth in this specifications book and otherwise notified by Sony from time to time.

- ◆ You should not use the Products for critical applications which may pose a life- or injury- threatening risk or are highly likely to cause significant property damage in the event of failure of the Products. You should consult your Sony sales representative beforehand when you consider using the Products for such critical applications. In addition, you should not use the Products in weapon or military equipment.

- ◆ Sony disclaims and does not assume any liability and damages arising out of misuse, improper use, modification, use of the Products for the above-mentioned critical applications, weapon and military equipment, or any deviation from the requirements set forth in this specifications book.

#### **Design for Safety**

◆ Sony is making continuous efforts to further improve the quality and reliability of the Products; however, failure of a certain percentage of the Products is inevitable. Therefore, you should take sufficient care to ensure the safe design of your products such as component redundancy, anti-conflagration features, and features to prevent mis-operation in order to avoid accidents resulting in injury or death, fire or other social damage as a result of such failure.

#### **Export Control**

♦ If the Products are controlled items under the export control laws or regulations of various countries, approval may be required for the export of the Products under the said laws or regulations. You should be responsible for compliance with the said laws or regulations.

#### No License Implied

◆ The technical information shown in this specifications book is for your reference purposes only. The availability of this specifications book shall not be construed as giving any indication that Sony and its licensors will license any intellectual property rights in such information by any implication or otherwise. Sony will not assume responsibility for any problems in connection with your use of such information or for any infringement of third-party rights due to the same. It is therefore your sole legal and financial responsibility to resolve any such problems and infringement.

#### **Governing Law**

◆ This Notice shall be governed by and construed in accordance with the laws of Japan, without reference to principles of conflict of laws or choice of laws. All controversies and disputes arising out of or relating to this Notice shall be submitted to the exclusive jurisdiction of the Tokyo District Court in Japan as the court of first instance.

#### **Other Applicable Terms and Conditions**

◆ The terms and conditions in the Sony additional specifications, which will be made available to you when you order the Products, shall also be applicable to your use of the Products as well as to this specifications book. You should review those terms and conditions when you consider purchasing and/or using the Products.

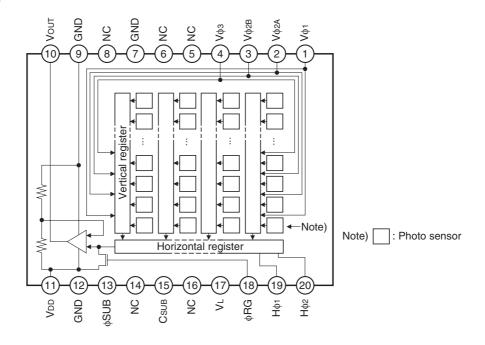

## **Block Diagram and Pin Configuration**

(Top View)

## **Pin Description**

| Pin No. | Symbol       | Description                      | Pin No. | Symbol | Description                        |

|---------|--------------|----------------------------------|---------|--------|------------------------------------|

| 1       | Vф1          | Vertical register transfer clock | 11      | VDD    | Supply voltage                     |

| 2       | Vф2A         | Vertical register transfer clock | 12      | GND    | GND                                |

| 3       | <b>V</b> ф2В | Vertical register transfer clock | 13      | φSUB   | Substrate clock                    |

| 4       | Vфз          | Vertical register transfer clock | 14      | NC     |                                    |

| 5       | NC           |                                  | 15      | CsuB   | Substrate bias*1                   |

| 6       | NC           |                                  | 16      | NC     |                                    |

| 7       | GND          | GND                              | 17      | VL     | Protective transistor bias         |

| 8       | NC           |                                  | 18      | φRG    | Reset gate clock                   |

| 9       | GND          | GND                              | 19      | Нф1    | Horizontal register transfer clock |

| 10      | Vоит         | Signal output                    | 20      | Нф2    | Horizontal register transfer clock |

$<sup>^{*1}~</sup>$  DC bias is generated within the CCD, so that this pin should be grounded externally through a capacitance of 0.1  $\mu\text{F}.$

### **Absolute Maximum Ratings**

|                          | Item                                                 | Ratings     | Unit | Remarks |

|--------------------------|------------------------------------------------------|-------------|------|---------|

|                          | Vdd, Vout, фRG – фSUB                                | -40 to +10  | V    |         |

|                          | V¢2A, V¢2B – ¢SUB                                    | -50 to +15  | V    |         |

| Against ∳SUB             | Vφ1, Vφ3, VL – φSUB                                  | -50 to +0.3 | V    |         |

|                          | Hφ1, Hφ2, GND – φSUB                                 | -40 to +0.3 | V    |         |

|                          | Csub – \$SUB                                         | –25 to      | V    |         |

|                          | VDD, VOUT, фRG, CSUB – GND                           | -0.3 to +18 | V    |         |

| Against GND              | Vφ1, Vφ2A, Vφ2B, Vφ3 – GND                           | –10 to +18  | V    |         |

|                          | Hφ1, Hφ2 – GND                                       | –10 to +15  | V    |         |

| Against VL               | Vφ2A, Vφ2B – VL                                      | -0.3 to +28 | V    |         |

|                          | Vφ1, Vφ3, Hφ1, Hφ2, GND – VL                         | -0.3 to +15 | V    |         |

|                          | Voltage difference between vertical clock input pins | to +15      | V    | *1      |

| Between input clock pins | Ηφ1 – Ηφ2                                            | -16 to +16  | V    |         |

|                          | Hφ1, Hφ2 – Vφ3                                       | -16 to +16  | V    |         |

| Storage temperatu        | -30 to +80                                           | °C          |      |         |

| Operating tempera        | -10 to +60                                           | °C          |      |         |

<sup>\*1 +24</sup>V (Max.) when clock width <  $10\mu$ s, clock duty factor < 0.1%.

#### **Bias Conditions**

| Item                       | Symbol | Min.  | Тур. | Max.  | Unit | Remarks |

|----------------------------|--------|-------|------|-------|------|---------|

| Power Supply voltage       | VDD    | 14.55 | 15.0 | 15.45 | V    |         |

| Protective transistor bias | VL     | *1    |      |       |      |         |

| Substrate clock            | φSUB   | *2    |      |       |      |         |

| Reset gate clock           | φRG    | *2    |      |       |      |         |

<sup>\*1</sup> VL setting is the VvL voltage of the vertical transfer clock waveform, or the same power supply as the VL power supply for the V driver should be used.

#### **DC Characteristics**

| Item                 | Symbol | Min. | Тур. | Max. | Unit | Remarks |

|----------------------|--------|------|------|------|------|---------|

| Power supply current | IDD    |      | 7.7  |      | mA   |         |

<sup>+16</sup>V (Max.) is guaranteed for turning on or off power supply.

<sup>\*2</sup> Do not apply a DC bias to the substrate clock and reset gate clock pins, because a DC bias is generated within the CCD.

## **Clock Voltage Conditions**

| Item                            | Symbol                      | Min.  | Тур. | Max.  | Unit | Waveform diagram | Remarks               |

|---------------------------------|-----------------------------|-------|------|-------|------|------------------|-----------------------|

| Readout clock voltage           | Vvт                         | 14.55 | 15.0 | 15.45 | V    | 1                |                       |

|                                 | VvH02A                      | -0.05 | 0    | 0.05  | V    | 2                | Vvh = Vvho2A          |

|                                 | Vvh1, Vvh2A,<br>Vvh2B, Vvh3 | -0.2  | 0    | 0.05  | V    | 2                |                       |

|                                 | VVL1, VVL2A,<br>VVL2B, VVL3 | -8.4  | -8.0 | -7.6  | V    | 2                | VvL = (VvL1 + VvL3)/2 |

| Vertical transfer clock voltage | Vφ1, Vφ2A,<br>Vφ2B, Vφ3     | 7.6   | 8.0  | 8.4   | V    | 2                |                       |

|                                 | VVL1 – VVL3                 |       |      | 0.1   | V    | 2                |                       |

|                                 | Vvнн                        |       |      | 0.9   | V    | 2                | High-level coupling   |

|                                 | VVHL                        |       |      | 1.3   | V    | 2                | High-level coupling   |

|                                 | VVLH                        |       |      | 1.0   | V    | 2                | Low-level coupling    |

|                                 | VVLL                        |       |      | 0.9   | V    | 2                | Low-level coupling    |

| Horizontal transfer clock       | Vфн                         | 4.75  | 5.0  | 5.25  | V    | 3                |                       |

| voltage                         | VHL                         | -0.05 | 0    | 0.05  | V    | 3                |                       |

|                                 | VφRG                        | 3.0   | 3.3  | 5.5   | V    | 4                |                       |

| Reset gate clock voltage        | VRGLH – VRGLL               |       |      | 0.4   | V    | 4                | Low-level coupling    |

|                                 | VRGL - VRGLm                |       |      | 0.5   | V    | 4                | Low-level coupling    |

| Substrate clock voltage         | Vфsuв                       | 22.15 | 23.0 | 23.85 | V    | 5                |                       |

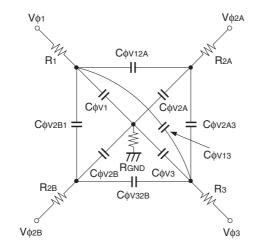

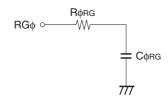

## **Clock Equivalent Circuit Constant**

| Item                                                  | Symbol           | Min. | Тур. | Max. | Unit | Remarks |

|-------------------------------------------------------|------------------|------|------|------|------|---------|

|                                                       | СфV1             |      | 2200 |      | pF   |         |

| Capacitance between vertical transfer clock           | СфV2А            |      | 3300 |      | pF   |         |

| and GND                                               | Сф∨2В            |      | 3300 |      | pF   |         |

|                                                       | Сф∨з             |      | 3300 |      | pF   |         |

|                                                       | СфV12A, СфV2В1   |      | 1200 |      | pF   |         |

| Capacitance between vertical transfer clocks          | Сфу2А3, Сфу32В   |      | 1200 |      | pF   |         |

|                                                       | СфV13            |      | 2200 |      | pF   |         |

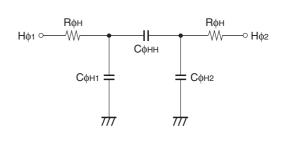

| Capacitance between horizontal transfer clock and GND | Сфн1, Сфн2       |      | 47   |      | pF   |         |

| Capacitance between horizontal transfer clocks        | Сфнн             |      | 100  |      | pF   |         |

| Capacitance between reset gate clock and GND          | СфRG             |      | 8    |      | pF   |         |

| Capacitance between substrate clock and GND           | Сфѕив            |      | 680  |      | pF   |         |

|                                                       | R <sub>1</sub>   |      | 36   |      | Ω    |         |

| Vertical transfer clock series resistor               | R2A, R3          |      | 56   |      | Ω    |         |

|                                                       | R <sub>2</sub> B |      | 56   |      | Ω    |         |

| Vertical transfer clock ground resistor               | RGND             |      | 30   |      | Ω    |         |

| Horizontal transfer clock series resistor             | Rфн              |      | 15   |      | Ω    |         |

| Reset gate clock series resistor                      | Rørg             |      | 20   |      | Ω    |         |

Vertical transfer clock equivalent circuit

Horizontal transfer clock equivalent circuit

Reset gate clock equivalent circuit