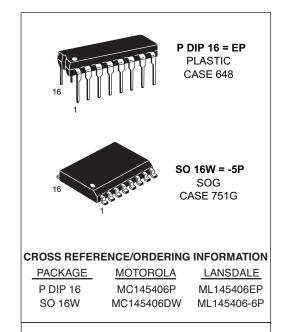

# ML145406 Driver/Receiver EIA 232-E and CCITT V.28 (Formerly RS-232-D)

Legacy Device: Motorola MC145406

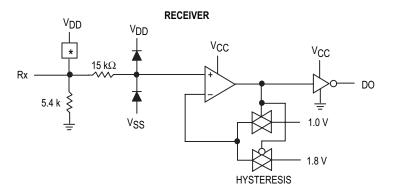

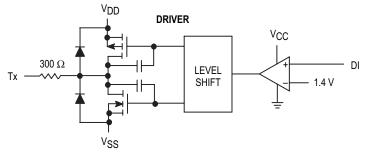

The ML145406 is a silicon–gate CMOS IC that combines three drivers and three receivers to fulfill the electrical specifications of standards EIA 232–E and CCITT V.28. The drivers feature true TTL input compatibility, slew–rate–limited output, 300– $\Omega$  power–off source impedance, and output typically switching to within 25% of the supply rails. The receivers can handle up to ±25 V while presenting 3 to 7 k $\Omega$  impedance. Hysteresis in the receivers aids reception of noisy signals. By combining both drivers and receivers in a single CMOS chip, the ML145406 provides efficient, low–power solutions for EIA 232–E and V.28 applications.

# This device offers the following performance features:

• Operating Temperature Range =  $T_A - 40^\circ$  to  $+85^\circ$ C

# **Drivers**

- $\pm$  5 V to  $\pm$ 12 V Supply Range

- 300–Ω Power–Off Source Impedance

- Output Current Limiting

- TTL Compatible

- Maximum Slew Rate = 30 V/μs

# **Receivers**

- $\pm$  25 V Input Voltage Range When V<sub>DD</sub> = 12 V, V<sub>SS</sub> = 12 V

- 3 to 7  $k\Omega$  Input Impedance

- · Hysteresis on Input Switchpoint

# **BLOCK DIAGRAM**

\*Protection circuit

**Note**: Lansdale lead free (**Pb**) product, as it becomes available, will be identified by a part number prefix change from **ML** to **MLE**.

## MAXIMUM RATINGS (Voltage polarities referenced to GND)

| Rating                                              | Symbol                                                | Value                                                                                | Unit |

|-----------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------|------|

| DC Supply Voltages ( $V_{DD} \ge V_{CC}$ )          | V <sub>DD</sub><br>V <sub>SS</sub><br>V <sub>CC</sub> | - 0.5 to + 13.5<br>+ 0.5 to - 13.5<br>- 0.5 to + 6.0                                 | V    |

| Input Voltage Range<br>Rx1–3 Inputs<br>DI1–3 Inputs | VIR                                                   | (V <sub>SS</sub> – 15) to (V <sub>DD</sub> + 15)<br>– 0.5 to (V <sub>CC</sub> + 0.5) | V    |

| DC Current Per Pin                                  |                                                       | ± 100                                                                                | mA   |

| Power Dissipation                                   | PD                                                    | 1.0                                                                                  | W    |

| Operating Temperature Range                         | TA                                                    | – 40 to + 85                                                                         | °C   |

| Storage Temperature Rate                            | T <sub>stg</sub>                                      | – 85 to + 150                                                                        | °C   |

This device contains protection circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation, it is recommended that the voltages at the DI and DO pins be constrained to the range  $\text{GND} \! \leq \! \text{V}_{DI} \! \leq \! \text{V}_{CC}$  and  $\text{GND} \! \leq \! \text{V}_{DC} \! \leq \! \text{V}_{CC}$ . Also, the voltage at the Rx pin should be constrained to  $(\text{VSS} - 15 \text{ V}) \leq \text{V}_{Rx1-3} \leq (\text{V}_{DD} + 15 \text{ V})$ , and Tx should be constrained to  $\text{V}_{SS} \leq \text{V}_{Tx1-3} \leq \text{V}_{DD}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., GND or  $V_{CC}$  for DI and Ground for Rx.)

# DC ELECTRICAL CHARACTERISTICS (All polarities referenced to GND = 0 V, T<sub>A</sub> = -40 to +85°C)

| Parameter                                               | Symbol          | Min  | Тур         | Max           | Unit |

|---------------------------------------------------------|-----------------|------|-------------|---------------|------|

| DC Supply Voltage                                       |                 |      |             |               | V    |

| V <sub>DD</sub>                                         | $V_{DD}$        | 4.5  | 5 to 12     | 13.2          |      |

| V <sub>SS</sub>                                         | V <sub>SS</sub> | -4.5 | – 5 to – 12 | <b>–</b> 13.2 |      |

| $VCC (VDD \ge VCC)$                                     | Vcc             | 4.5  | 5.0         | 5.5           |      |

| Quiescent Supply Current (Outputs unloaded, inputs low) |                 |      |             |               | μΑ   |

| V <sub>DD</sub> = + 12 V                                | I <sub>DD</sub> | _    | 140         | 400           |      |

| $V_{SS} = -12 V$                                        | ISS             | l –  | 340         | 600           |      |

| V <sub>CC</sub> = + 5 V                                 | Icc             | _    | 300         | 450           |      |

# RECEIVER ELECTRICAL SPECIFICATIONS

(Voltage polarities referenced to GND = 0 V,  $V_{DD}$  = + 5 to + 12 V,  $V_{SS}$  = - 5 to - 12 V,  $V_{DD} \ge V_{CC}$ ,  $T_A$  = -40 to +85°C)

| Characteristic                                                                                                                                                                                           | Symbol                            | Min        | Тур                 | Max               | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------|---------------------|-------------------|------|

| Input Turn–on Threshold Rx1–Rx3 $V_{DO1-DO3} = V_{OL}$ , $V_{CC} = 5.0 \text{ V} \pm 5\%$                                                                                                                | V <sub>on</sub>                   | 1.35       | 1.80                | 2.35              | V    |

| Input Turn–off Threshold Rx1–Rx3 $V_{DO1-DO3} = V_{OH}, V_{CC} = 5.0 \text{ V} \pm 5\%$                                                                                                                  | V <sub>off</sub>                  | 0.75       | 1.00                | 1.25              | V    |

| Input Threshold Hysteresis $Rx1-Rx3$ $V_{CC} = 5.0 \text{ V} \pm 5\%$                                                                                                                                    | V <sub>on</sub> –V <sub>off</sub> | 0.6        | 0.8                 | _                 | V    |

| Input Resistance Rx1–Rx3 $(V_{SS} - 15 \text{ V}) \le V_{Rx1-Rx3} \le (V_{DD} + 15 \text{ V})$                                                                                                           | R <sub>in</sub>                   | 3.0        | 5.4                 | 7.0               | kΩ   |

| High–Level Output Voltage ( $V_{Rx1-Rx3}$ = $-3$ V to ( $V_{SS}$ $-15$ V))* DO1–DO3 $I_{OH}$ = $-20$ $\mu$ A, $V_{CC}$ = $+5.0$ V $I_{OH}$ = $-1$ mA, $V_{CC}$ = $+5.0$ V                                | VOH                               | 4.9<br>3.8 | 4.9<br>4.3          |                   | V    |

| Low–Level Output Voltage ( $V_{RX1-RX3}$ = + 3 V to ( $V_{DD}$ + 15 V))* DO1–DO3 $I_{OL}$ = + 20 $\mu$ A, $V_{CC}$ = + 5.0 V $I_{OL}$ = + 2 mA, $V_{CC}$ = + 5.0 V $I_{OL}$ = + 4 mA, $V_{CC}$ = + 5.0 V | VoL                               |            | 0.01<br>0.02<br>0.5 | 0.1<br>0.5<br>0.7 | V    |

<sup>\*</sup> This is the range of input voltages as specified by EIA 232-E to cause a receiver to be in the high or low logic state.

# **ELECTRICAL SPECIFICATIONS** (Voltage polarities referenced to GND = 0 V, $V_{CC}$ = + 5 V $\pm$ 5%, $T_A$ = -40 to +85°C)

| Characteristic                                                                                                                           | Symbol                 | Min                      | Тур                    | Max         | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------|------------------------|-------------|------|

| Digital Input Voltage Logic 0 Logic 1                                                                                                    | V <sub>IL</sub><br>VIH | _<br>2.0                 | _<br>_                 | 0.8         | V    |

| Input Current DI1–DI3 VDI1–DI3 = VCC                                                                                                     | l <sub>in</sub>        | _                        | _                      | ± 1.0       | μА   |

| Output High Voltage ( $V_{DI1-3}$ = Logic 0, $R_L$ = 3.0 k $\Omega$ )                                                                    | Voн                    | 3.5<br>4.3<br>9.2        | 3.9<br>4.7<br>9.5      | _<br>_<br>_ | V    |

| Output Low Voltage* ( $V_{DI1-3}$ = Logic 1, $R_L$ = 3.0 k $\Omega$ )                                                                    | VOL                    | - 4.0<br>- 4.5<br>- 10.0 | -4.3<br>-5.2<br>- 10.3 | _<br>_<br>_ | V    |

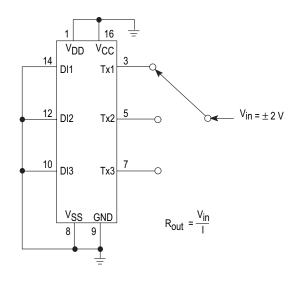

| Off Source Resistance (Figure 1) $V_{DD} = V_{SS} = GND = 0 \text{ V}, V_{Tx1-Tx3} = \pm 2.0 \text{ V}$                                  |                        | 300                      | _                      | _           | Ω    |

| Output Short–Circuit Current ( $V_{DD}$ = + 12.0 V, $V_{SS}$ = - 12.0 V) Tx1–Tx3 Tx1–Tx3 shorted to GND** Tx1–Tx3 shorted to ± 15.0 V*** | I <sub>SC</sub>        |                          | ±22<br>±60             | ±60<br>±100 | mA   |

<sup>\*</sup>The voltage specifications are in terms of absolute values.

# SWITCHING CHARACTERISTICS (V<sub>CC</sub> = + 5 V $\pm$ 5%, T<sub>A</sub> = -40 to + $85^{\circ}$ C

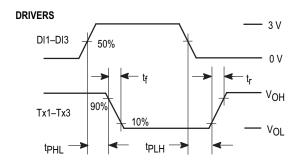

# **Drivers**

| Char                                              | Symbol                                                | Min              | Тур | Max | Unit |      |

|---------------------------------------------------|-------------------------------------------------------|------------------|-----|-----|------|------|

| Propagation Delay Time                            | Tx1–Tx3                                               |                  |     |     |      | ns   |

| Low-to-High                                       |                                                       |                  |     |     |      |      |

|                                                   | $R_L = 3 \text{ k}\Omega$ , $C_L = 50 \text{ pF}$     | <sup>t</sup> PLH | _   | 300 | 500  |      |

| High-to-Low                                       |                                                       | <sup>t</sup> PHL |     |     |      |      |

|                                                   | $R_L = 3 \text{ k}\Omega \text{ C}_L = 50 \text{ pF}$ |                  | _   | 300 | 500  |      |

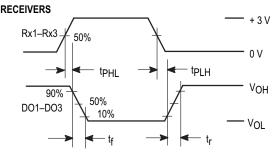

| Output Slew Rate                                  | Tx1–Tx3                                               | SR               |     |     |      | V/μs |

| Minimum Load                                      |                                                       |                  |     |     |      |      |

| $R_L = 7 \text{ k}\Omega, C_L = 0 \text{ pF, } V$ | $V_{DD}$ = +6 to + 12 V, $V_{SS}$ = -6 to -12 V       |                  | _   | ±9  | ±30  |      |

| Maximum Load                                      |                                                       |                  |     |     |      | 1    |

|                                                   | $R_L = 3 \text{ k}\Omega$ , $C_L = 2500 \text{ pF}$   |                  |     |     |      |      |

|                                                   | $V_{DD} = + 12 \text{ V}, V_{SS} = - 12 \text{ V}$    |                  | 4   | _   |      |      |

|                                                   | $V_{DD} = + 5 V, V_{SS} = - 5 V$                      |                  | _   | _   | _    |      |

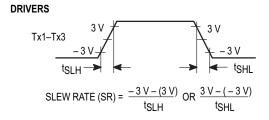

# Receivers ( $C_L = 50 pF$ )

| Characteristic   |         | Symbol           | Min | Тур | Max | Unit |

|------------------|---------|------------------|-----|-----|-----|------|

| , , ,            | DO1-DO3 |                  |     |     |     | ns   |

| Low-to-High      |         | <sup>t</sup> PLH | _   | 150 | 425 |      |

| High-to-Low      |         | <sup>t</sup> PHL | _   | 150 | 425 |      |

| Output Rise Time | DO1–DO3 | t <sub>r</sub>   | _   | 250 | 400 | ns   |

| Output Fall Time | DO1-DO3 | t <sub>f</sub>   | _   | 40  | 100 | ns   |

<sup>\*\*</sup> Specification is for one Tx output pin to be shorted at a time. Should all three driver outputs be shorted simultaneously, device power dissipation limits will be exceeded.

<sup>\*\*\*</sup> This condition could exceed package limitations.

Figure 1. Power-Off Source Resistance (Drivers)

Figure 2. Switching Characteristics

Figure 3. Slew-Rate Characterization

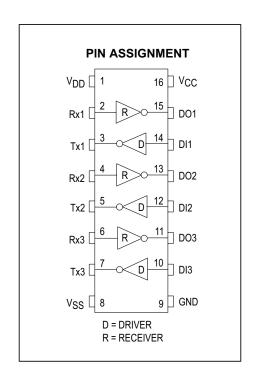

## PIN DESCRIPTIONS

# **VDD**

# Positive Power Supply (Pin 1)

The most positive power supply pin, which is typically  $\pm$  5 to  $\pm$ 12 V.

### **VSS**

# **Negative Power Supply (Pin 8)**

The most negative power supply pin, which is typically -5 to -12 V.

# V<sub>CC</sub> Digital Power Supply (Pin 16)

The digital supply pin, which is connected to the logic power supply (maximum  $\pm 5.5$  V). V<sub>CC</sub> **must** be less than or equal to V<sub>DD</sub>.

# GND

# Ground (Pin 9)

Ground return pin is typically connected to the signal ground pin of the EIA 232–E connector (Pin 7) as well as to the logic power supply ground.

# Rx1, Rx2, Rx3 Receive Data Input (Pins 2, 4, 6)

These are the EIA 232–E receive signal inputs whose voltages can range from (VDD + 15 V) to (VSS – 15 V). A voltage between +3 and (VDD + 15 V) is decoded as a space and causes the corresponding DO pin to swing to ground (0V); a voltage between – 3 and (VDD – 15 V) is decoded as a mark and causes the DO pin to swing up to VCC. The actual turn–on input switch point is typically biased at 1.8 V above ground, and includes 800 mV of hysteresis for noise rejection. The nominal input impedance is 5 k $\Omega$ . An open or grounded input pin is interpreted as a mark, forcing the DO pin to VCC.

# DO1, DO2, DO3 Data Output (Pins 11, 13, 15)

These are the receiver digital output pins, which swing from V<sub>CC</sub> to GND. A space on the Rx pin causes DO to produce a logic 0; a mark produces a logic 1. Each output pin is capable of driving one LSTTL input load.

# DI1, DI2, DI3 Data Input (Pins 10, 12,14)

These are the high–impedance digital input pins to the drivers. TTL compatibility is accomplished by biasing the input switchpoint at 1.4 V above GND. However, 5V CMOS compatibility is maintained as well. Input voltage levels on these pins must be between V<sub>CC</sub> and GND.

# Tx1, Tx2, Tx3 Transmit Data Output(Pins 3, 5, 7)

These are the EIA 232–E transmit signal output pins, which swing toward  $V_{DD}$  and  $V_{SS}$ . A logic 1 at a DI input causes the corresponding Tx output to swing toward  $V_{SS}$ . A logic 0 causes the output to swing toward  $V_{DD}$  (the output voltages will be slightly less than  $V_{DD}$  or  $V_{SS}$  depending upon the output load). Output slew rates are limited to a maximum of 30 V per  $\mu_{SS}$ . When the ML145406 is off ( $V_{DD} = V_{SS} = V_{CC} = G_{ND}$ ), the minimum output impedance is 300  $\Omega$ .

# Legacy Applications Information

The ML145406 has been designed to meet the electrical-specifications of standards EIA 232–E and CCITT V.28. EIA 232–E defines the electrical and physical interface between Data Communication Equipment (DCE) and DataTerminal Equipment (DTE). A DCE is connected to a DTE using a cable that typically carries up to 25 leads. These leads, referred to as interchange circuits, allow the transfer of timing, data, control, and test signals. Electrically this transfer requires level shifting between the TTL/CMOS logic levels of the computer or modem and the high voltage levels of EIA 232–E, which can range from  $\pm 3$  to  $\pm 25$  V. The ML145406 provides the necessary level shifting as well as meeting other aspects of the EIA 232–E specification.

## **DRIVERS**

As defined by the specification, an EIA 232–E driver presents a voltage of between  $\pm 5$  to  $\pm 15$  V into a load of between 3 to 7 k $\Omega$ . A logic 1 at the driver input results in a voltage of between  $\pm 5$  to  $\pm 15$  V. A logic 0 results in a voltage between  $\pm 5$  to  $\pm 15$  V. When operating VDD and VSS at  $\pm 7$  to  $\pm 12$  V, the ML145406 meets this requirement. When operating at  $\pm 5$  V, the ML145406 drivers produce less than  $\pm 5$  V at the output (when terminated), which does not meet EIA 232–E specification. However, the output voltages when using a  $\pm 5$  V power supply are high enough (around  $\pm 4$  V) to permit proper reception by an EIA 232–E receiver, and can be used in applications where strict compliance to EIA 232–E is not required.

Another requirement of the ML145406 drivers is that they withstand a short to another driver in the EIA 232–E cable. The worst–case condition that is permitted by EIA 232–E is a  $\pm 15 V$  source that is current limited to 500 mA. The ML145406 drivers can withstand this condition momentarily. In most short circuit conditions the source driver will have a series 300  $\Omega$  output impedance needed to satisfy the EIA 232–E driver requirements. This will reduce the short circuit current to under 40 mA which is an acceptable level for the ML145406 to withstand.

Unlike some other drivers, the ML145406 drivers feature an internally-limited output slew-rate that does not exceed 30 V per µs.

# **RECEIVERS**

The job of an EIA 232–E receiver is to level–shift voltages in the range of – 25 to + 25 V down to TTL/CMOS logic levels (0 to + 5 V). A voltage of between – 3 and – 25 V on Rx1 is defined as a mark and produces a logic 1 at DO1. A voltage between + 3 and + 25 V is a space and produces a logic zero. While receiving these signals, the Rx inputs must present a resistance between 3 and 7 k $\Omega$ . Nominally, the input resistance of the Rx1–Rx3 inputs is 5.4 k $\Omega$ .

The input threshold of the Rx1–Rx3 inputs is typically biased at 1.8 V above ground (GND) with typically 800 mV of hysteresis included to improve noise immunity. The 1.8 V bias

forces the appropriate DO pin to a logic 1 when its Rx input is open or grounded as called for in the EIA 232–E specification. Notice that TTL logic levels can be applied to the Rx inputs in lieu of normal EIA 232–E signal levels. This might be helpful in situations where access to the modem or computer through the EIA 232–E connector is necessary with TTL devices. However, it is important not to connect the EIA 232–E outputs (Tx1–Tx3) to TTL inputs since TTL operates off + 5 V only, and may be damaged by the high output voltage of the ML145406.

The DO outputs are to be connected to a TTL or CMOS input (such as an input to a modem chip). These outputs will swing from  $V_{CC}$  to ground, allowing the designer to operate the DO and DI pins from digital power supply. The Tx and Rx sections are independently powered by  $V_{DD}$  and  $V_{SS}$  so that one may run logic at  $\pm$  5 V and the EIA 232–E signals at  $\pm$ 12V.

## POWER SUPPLY CONSIDERATIONS

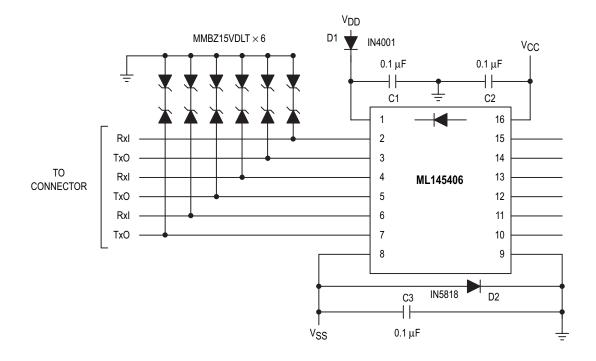

Figure 4 shows a technique to guard against excessive device current.

The diode D1 prevents excessive current from flowing through an internal diode from the  $V_{CC}$  pin to the  $V_{DD}$  pin when  $V_{DD} < V_{CC}$  by approximately 0.6 V. This high current condition can exist for a short period of time during powerup/down. Additionally, if the + 12 V supply is switched off while the + 5 V is on and the off supply is a low impedance to ground, the diode D1 will prevent current flow through the internal diode.

The diode D2 is used as a voltage clamp, to prevent VSS from drifting positive to VCC, in the event that power is removed from VSS (Pin 12). If VSS power is removed, and the impedance from the VSS pin to ground is greater than approximately 3 k $\Omega$ , this pin will be pulled to VCC by internal circuitry causing excessive current in the VCC pin.

If by design, neither of the above conditions are allowed to exist, then the diodes D1 and D2 are not required.

# **ESD PROTECTION**

ESD protection on IC devices that have their pins accessible to the outside world is essential. High static voltages applied to the pins when someone touches them either directly or indirectly can cause damage to gate oxides and transistor junctions by coupling a portion of the energy from the I/O pin to the power supply buses of the IC. This coupling will usually occur through the internal ESD protection diodes. The key to protecting the IC is to shunt as much of the energy to ground as possible before it enters the IC. Figure 4 shows a technique which will clamp the ESD voltage at approximately  $\pm 15$  V using the MMVZ15VDLT1. Any residual voltage which appears on the supply pins is shunted to ground through the capacitors C1–C3. This scheme has provided protection to the interface part up to  $\pm 10$ kV, using the human body model test.

# Legacy Applications Information

Figure 4. ESD and Power Supply Networks

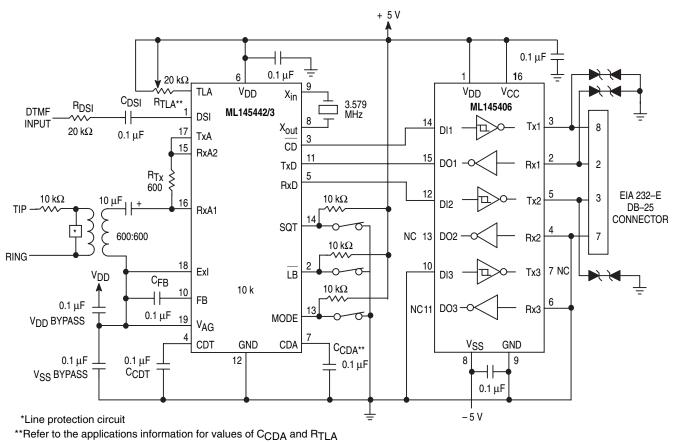

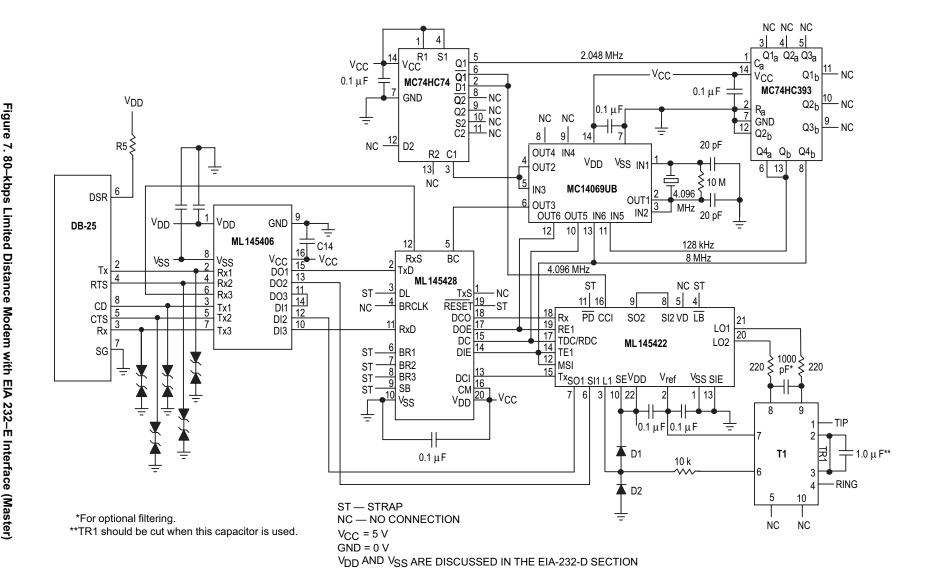

Figure 5. 5-V 300-Baud Modem with EIA 232-E Interface

# Legacy Applications Information

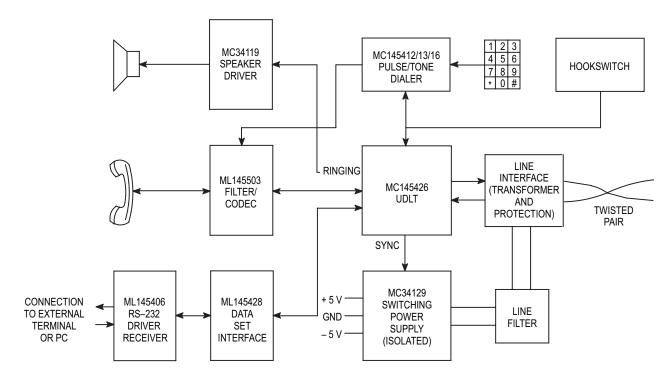

Figure 6. Line-Powered Voice/Data Telephone with Electrically Isolated EIA 232-E Interface

www.lansdale.com

ML145406

# **OUTLINE DIMENSIONS**

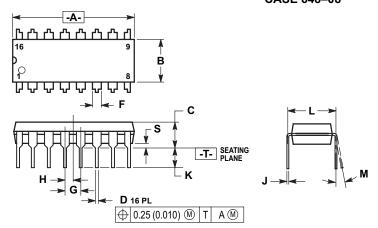

**P DIP 16 = EP** (ML145406EP) **CASE 648-08**

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- CONTROLLING DIMENSION: INCH.

DIMENSION L TO CENTER OF LEADS WHEN

FORMED PARALLEL.

- DIMENSION B DOES NOT INCLUDE MOLD FLASH.

- ROUNDED CORNERS OPTIONAL.

|     | INCHES |       | MILLIN   | IETERS |

|-----|--------|-------|----------|--------|

| DIM | MIN    | MAX   | MIN      | MAX    |

| Α   | 0.740  | 0.770 | 18.80    | 19.55  |

| В   | 0.250  | 0.270 | 6.35     | 6.85   |

| С   | 0.145  | 0.175 | 3.69     | 4.44   |

| D   | 0.015  | 0.021 | 0.39     | 0.53   |

| F   | 0.040  | 0.070 | 1.02     | 1.77   |

| G   | 0.100  | BSC   | 2.54     | BSC    |

| Н   | 0.050  | BSC   | 1.27 BSC |        |

| J   | 0.008  | 0.015 | 0.21     | 0.38   |

| K   | 0.110  | 0.130 | 2.80     | 3.30   |

| L   | 0.295  | 0.305 | 7.50     | 7.74   |

| М   | 0°     | 10°   | 0°       | 10°    |

| S   | 0.020  | 0.040 | 0.51     | 1.01   |

# NOTES:

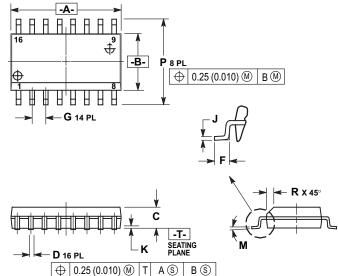

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- CONTROLLING DIMENSION: MILLIMETER.

- DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13 (0.005) TOTAL IN EXCESS OF D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       | INC   | HES   |

|-----|-------------|-------|-------|-------|

| DIM | MIN         | MAX   | MIN   | MAX   |

| Α   | 10.15       | 10.45 | 0.400 | 0.411 |

| В   | 7.40        | 7.60  | 0.292 | 0.299 |

| С   | 2.35        | 2.65  | 0.093 | 0.104 |

| D   | 0.35        | 0.49  | 0.014 | 0.019 |

| F   | 0.50        | 0.90  | 0.020 | 0.035 |

| G   | 1.27        | BSC   | 0.050 | BSC   |

| J   | 0.25        | 0.32  | 0.010 | 0.012 |

| K   | 0.10        | 0.25  | 0.004 | 0.009 |

| M   | 0°          | 7°    | 0°    | 7°    |

| Р   | 10.05       | 10.55 | 0.395 | 0.415 |

| R   | 0.25        | 0.75  | 0.010 | 0.029 |

Lansdale Semiconductor reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Lansdale does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. "Typical" parameters which may be provided in Lansdale data sheets and/or specifications can vary in different applications, and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts. Lansdale Semiconductor is a registered trademark of Lansdale Semiconductor, Inc.