# ML13158

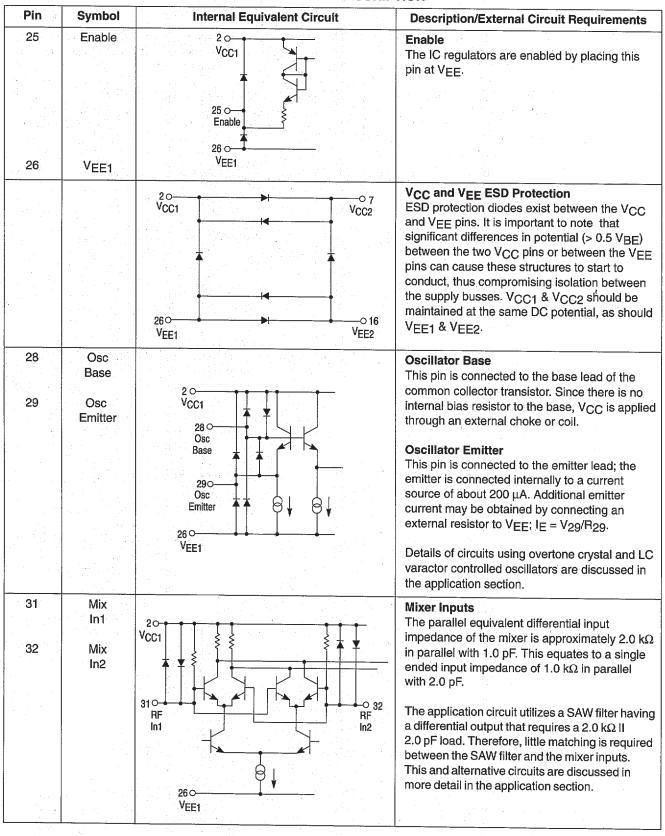

# Wideband FM IF Subsystem For Dect and Digital Applications

Legacy Device: Motorola MC13158

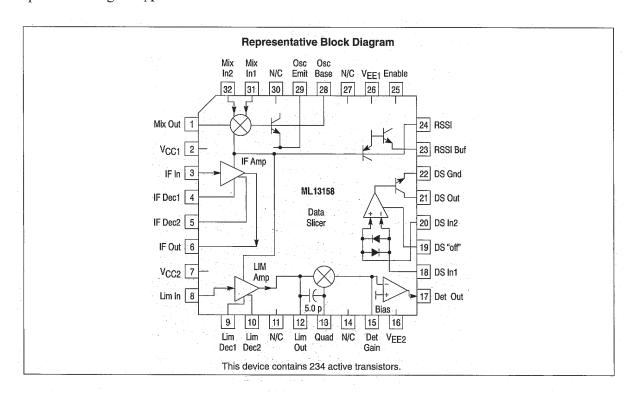

The ML13158 is a wideband IF subsystem that is designed for high performance data and analog applications. The ML13158 has an on–board grounded collector VCO transistor that may be used with a fundamental or overtone crystal in single channel operation or with a PLL in multi–channel operation. The mixer is useful to 500 MHz and may be used in a balanced differential or a single ended configuration. The IF amplifier is split to accommodate two low cost cascaded filters. RSSI output is derived by summing the output of both IF sections. A precision data shaper has an Off function to shut the output off to save current. An enable control is provided to power down the IC for power management in battery operated applications.

Applications include DECT, wideband wireless data links for personal and portable laptop computers and other battery operated radio systems which utilize GFSK, FSK or FM modulation.

- Designed for DECT Applications

- 1.8 to 6.0 Vdc Operating Voltage

- Low Power Consumption in Active and Standby Mode

- · Greater than 600 kHz Detector Bandwidth

- Data Slicer with Special Off Function

- Enable Function for Power Down of Battery Operated Systems

- RSSI Dynamic Range of 80 dB Minimum

- Low External Component Count

- Operating Temperature Range  $T_A = -40$  to +85°C

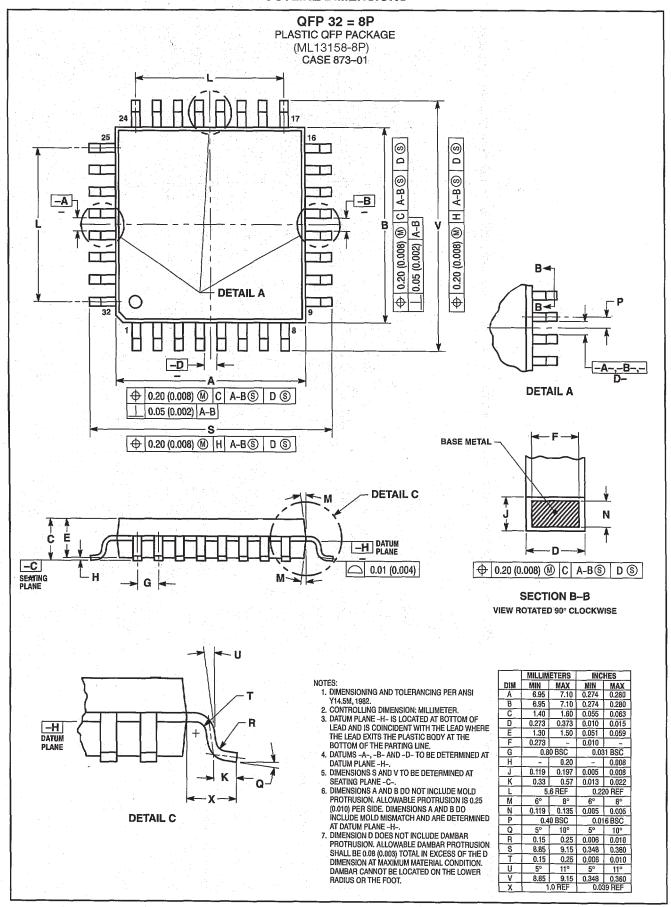

QFP 32 = 8P PLASTIC QFP PACKAGE CASE 873

#### **CROSS REFERENCE/ORDERING INFORMATION**

PACKAGE QFP 32 MOTOROLA MC13158FTB LANSDALE ML13158-8P

**Note**: Lansdale lead free (**Pb**) product, as it becomes available, will be identified by a part number prefix change from **ML** to **MLE**.

#### MAXIMUM RATINGS

| Rating                    | Pin    | Symbol              | Value       | Unit |

|---------------------------|--------|---------------------|-------------|------|

| Power Supply Voltage      | 16, 26 | V <sub>S(max)</sub> | 6.5         | Vdc  |

| Junction Temperature      |        | TJMAX               | +150        | °C   |

| Storage Temperature Range |        | T <sub>stg</sub>    | -65 to +150 | °C   |

NOTE: 1. Devices should not be operated at or outside these values. The "Recommended Operating Limits" provide for actual device operation.

# **RECOMMENDED OPERATING CONDITIONS** $(V_{CC} = V_2 = V_7; V_{EE} = V_{16} = V_{22} = V_{26}; V_S = V_{CC} - V_{EE})$

| Rating                         | Pin    | Symbol          | Value      | Unit  |

|--------------------------------|--------|-----------------|------------|-------|

| Power Supply Voltage TA = 25°C | 2,7    | ٧s              | 2.0 to 6.0 | Vdc   |

| -40°C ≤ T <sub>A</sub> ≤ 85°C  | 16, 26 |                 |            |       |

| Input Frequency                | 31, 32 | Fin             | 10 to 500  | MHz   |

| Ambient Temperature Range      |        | TA              | -40 to +85 | °C    |

| Input Signal Level             | 31, 32 | V <sub>in</sub> | 200        | mVrms |

# DC ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = 25°C; V<sub>S</sub> = 3.0 Vdc; No Input Signal; See Figure 1.)

| Characteristic      | Condition                                | Pin    | Symbol | Min | Тур | Max | Unit |

|---------------------|------------------------------------------|--------|--------|-----|-----|-----|------|

| Total Drain Current | V <sub>S</sub> = 2.0 Vdc                 | 16, 26 | ITOTAL | 2.5 | 5.5 | 8.5 | mA   |

|                     | V <sub>S</sub> = 3.0 Vdc                 |        |        | 3.5 | 5.7 | 8.5 |      |

|                     | V <sub>S</sub> = 6.0 Vdc<br>See Figure 2 |        |        | 3.5 | 6.0 | 9.5 |      |

#### DATA SLICER (Input Voltage Referenced to VEE; VS = 3.0 Vdc; No Input Signal)

| Output Current; V <sub>18</sub> LO;<br>Data Slicer Enabled (DS "on") | V <sub>19</sub> = VEE<br>V <sub>18</sub> < V <sub>20</sub><br>V <sub>20</sub> = V <sub>5</sub> /2<br>See Figure 3             | 21 | l <sub>21</sub> | 2.0 | 5.9 |     | mA |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----|-----------------|-----|-----|-----|----|

| Output Current; V <sub>18</sub> HI;<br>Data Slicer Enabled (DS "on") | V <sub>19</sub> = V <sub>EE</sub><br>V <sub>18</sub> > V <sub>20</sub><br>V <sub>20</sub> = V <sub>S</sub> /2<br>See Figure 4 | 21 | l <sub>21</sub> |     | 0.1 | 1.0 | μА |

| Output Current;<br>Data Slicer Disabled (DS "off")                   | V <sub>19</sub> = V <sub>CC</sub><br>V <sub>20</sub> = V <sub>S</sub> /2                                                      | 21 | l <sub>21</sub> |     | 0.1 | 1.0 | μА |

# AC ELECTRICAL CHARACTERISTICS ( $T_A = 25$ °C; $V_S = 3.0$ Vdc; $f_{RF} = 110.7$ MHz; $f_{LO} = 100$ MHz; See Figure 1 unless otherwise specified.)

| Characteristic         | Condition                                   | Pin       | Symbol                                       | Min | Тур        | Max | Unit    |

|------------------------|---------------------------------------------|-----------|----------------------------------------------|-----|------------|-----|---------|

| MIXER                  |                                             |           | <u>'                                    </u> |     |            | ,   |         |

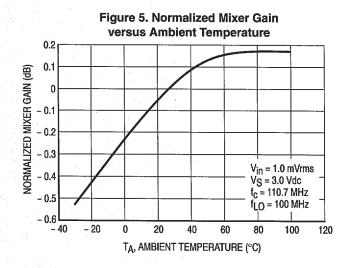

| Mixer Conversion Gain  | V <sub>in</sub> = 1.0 mVrms<br>See Figure 5 | 31, 32, 1 |                                              | -   | 22         | _   | dB      |

| Noise Figure           | Input Matched                               | 31, 32, 1 | NF                                           |     | 14         | _   | dB      |

| Mixer Input Impedance  | Single-Ended<br>See Figure 15               | 31, 32    | Rp<br>Cp                                     | -   | 865<br>1.6 |     | Ω<br>pF |

| Mixer Output Impedance |                                             | 1         |                                              |     | 330        |     | Ω       |

AC ELECTRICAL CHARACTERISTICS (continued) ( $T_A = 25$ °C;  $V_S = 3.0$  Vdc;  $f_{RF} = 110.7$  MHz;  $f_{LO} = 100$  MHz; See Figure 1 unless otherwise specified.)

| Characteristic                | Condition                    | Pin   | Symbol | Min  | Тур | Max | Unit  |

|-------------------------------|------------------------------|-------|--------|------|-----|-----|-------|

| MIXER<br>IF AMPLIFIER SECTION |                              |       |        |      |     |     |       |

| IF RSSI Slope                 | See Figure 8                 | 23    |        | 0.15 | 0.3 | 0.4 | μA/dB |

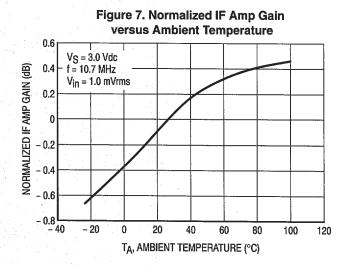

| IF Gain                       | f = 10.7 MHz<br>See Figure 7 | 3, 6  |        |      | 36  |     | dB    |

| Input Impedance               |                              | 3     |        | -    | 330 | _   | Ω     |

| Output Impedance              |                              | 6     |        | _    | 330 |     | Ω     |

| LIMITING AMPLIFIER SECTION    |                              |       | •      |      |     |     |       |

| Limiter RSSI Slope            | See Figure 9                 | 23    |        | 0.15 | 0.3 | 0.4 | μA/dB |

| Limiter Gain                  | f = 10.7 MHz                 | 8, 12 |        | -    | 70  |     | dB    |

| Input Impedance               |                              | 8     |        |      | 330 |     | Ω     |

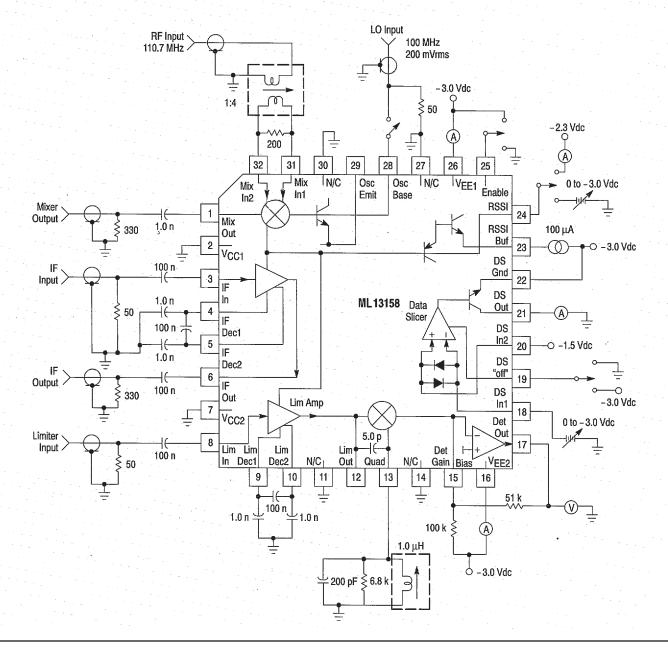

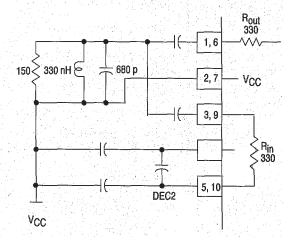

Figure 1. Test Circuit

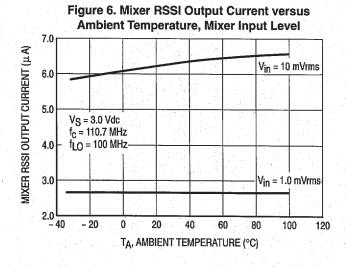

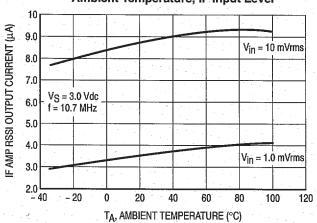

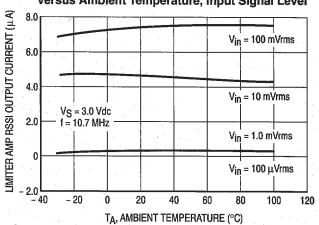

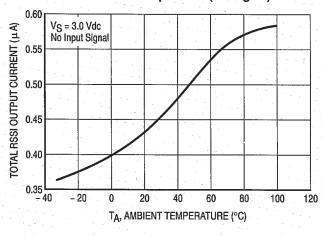

#### **Typical Performance Over Temperature**

(per Figure 1)

Figure 2. Total Supply Current versus **Ambient Temperature, Supply Voltage** 6.4 TOTAL SUPPLY CURRENT (mA)  $V_S = 6.0 \text{ V}$ 3.0 V 6.0 2.0 V 5.8 5.6 5.4 5.2 20 - 20 0 40 60 80 100 120 TA, AMBIENT TEMPERATURE (°C)

Figure 3. Data Slicer On Output Current versus Ambient Temperature 8.5 DATA SLICER OUTPUT CURRENT (mA) Data Slicer "On" V<sub>19</sub> = V<sub>EE</sub> 8.0  $V_{20} = V_{\overline{S}}/2$ V<sub>18</sub> < V<sub>20</sub> 7.5 7.0 6.5 6.0 5.0 20 40 0 20 60 80 100 120 TA, AMBIENT TEMPERATURE (°C)

Figure 4. Data Slicer On Output Current versus Ambient Temperature 0.12 DATA SLICER OUTPUT CURRENT (µA) V<sub>18</sub> > V<sub>20</sub> Data Slicer "On' V<sub>19</sub> = V<sub>CC</sub> V<sub>20</sub> = V<sub>S</sub>/2 0.10 0.08 0.06 0.02 40 - 20 20 40 60 120 TA, AMBIENT TEMPERATURE (°C)

#### **Typical Performance Over Temperature**

(per Figure 1)

Figure 8. IF Amp RSSI Output Current versus Ambient Temperature, IF Input Level

Figure 9. Limiter Amp RSSI Output Current versus Ambient Temperature, Input Signal Level

Figure 10. Total RSSI Output Current versus Ambient Temperature (No Signal)

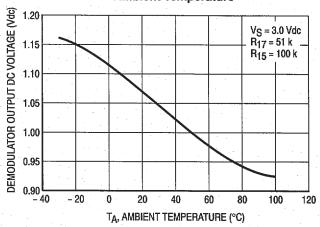

Figure 11. Demodulator DC Voltage versus

Ambient Temperature

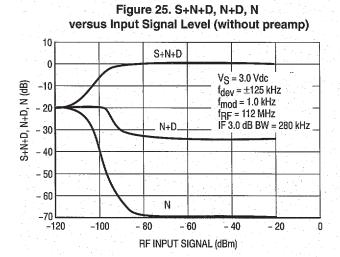

SYSTEM LEVEL AC ELECTRICAL CHARACTERISTICS ( $T_A = 25$ °C;  $V_S = 3.0$  Vdc;  $f_{RF} = 112$  MHz;  $f_{LO} = 122.7$  MHz)

| Characteristic              | Condition                       | Notes Symbol |              | Тур  | Unit |

|-----------------------------|---------------------------------|--------------|--------------|------|------|

| 12 dB SINAD Sensitivity:    | f <sub>RF</sub> = 112 MHz       | 1            |              |      | dBm  |

| Narrowband Application      | f <sub>mod</sub> = 1.0 kHz      |              |              |      |      |

|                             | $f_{dev} = \pm 125 \text{ kHz}$ | 1.44         |              |      |      |

|                             | SINAD Curve                     |              |              |      |      |

| Without Preamp              | Figure 25                       |              |              | -101 |      |

| With Preamp                 | Figure 26                       |              |              | -113 |      |

| Third Order Intercept Point | f <sub>RF1</sub> = 112 MHz      | 2            | IIP3         | -32  | dBm  |

|                             | f <sub>RF2</sub> = 112.1 MHz    |              |              |      |      |

| 1.0 dB Comp. Point          | V <sub>S</sub> = 3.5 Vdc        |              | 1.0 dB C.Pt. | -39  |      |

|                             | Figure 28                       |              |              |      |      |

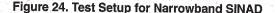

NOTES: 1. Test Circuit & Test Set per Figure 24.

2. Test Circuit & Test Set per Figure 27.

#### CIRCUIT DESCRIPTION

#### **GENERAL**

The ML13158 is a low power single conversion wideband FM receiver incorporating a split IF. This device can be used as the backend in digital FM systems such as Digital European Cordless Telephone (DECT) and wide band data links with data rates up to 2.0 Mbps. It contains a mixer, oscillator, Received Signal Strength Indicator (RSSI), IF amplifier, limiting IF, quadrature detector, power down or enable function, and a data slicer with output off function. Further details are covered in the Pin Function Description which shows the equivalent internal circuit and external circuit requirements.

#### **CURRENT REGULATION**

Temperature compensating voltage independent current regulators which are controlled by the enable pin (Pin 25) where "low" powers up and "high" powers down the entire circuit.

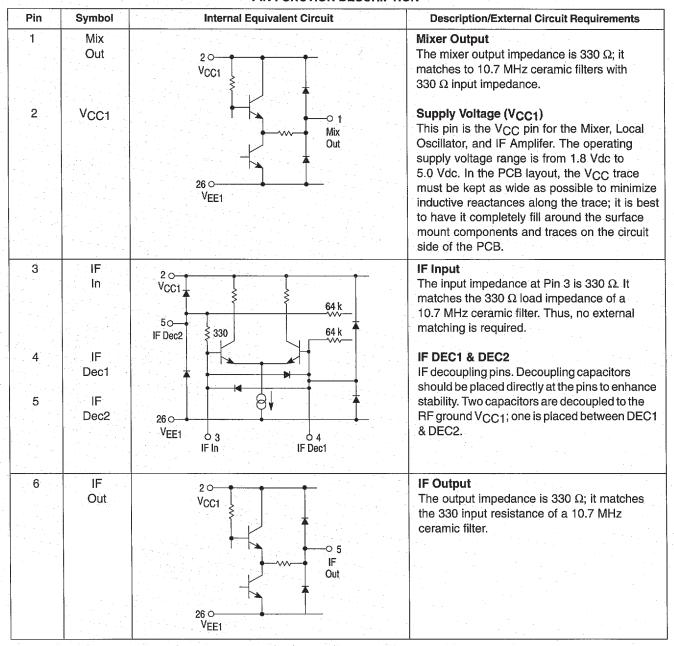

#### **MIXER**

The mixer is a double–balanced four quadrant multiplier and is designed to work up to 500 MHz. It can be used in differential or in single–ended mode by connecting the other input to the positive supply rail. The linear gain of the mixer is approximately 22 dB at 100 mVrms LO drive level. The mixer gain and noise figure have been emphasized at the expense of intermodulation performance. RSSI measurements are added in the mixer to extend the range to higher signal levels. The single–ended parallel equivalent input impedance of the mixer is Rp  $\sim 1.0~\text{k}\Omega$  and Cp  $\sim 2.0~\text{pF}$ . The buffered output of the mixer is internally loaded resulting in an output impedance of 330  $\Omega$ .

#### LOCAL OSCILLATOR

The on–chip transistor operates with crystal and LC resonant elements up to 220 MHz. Series resonant, overtone crystals are used to achieve excellent local oscillator stability. Third overtone crystals are used through about 65 to 70 MHz. Operation from 70 MHz up to 180 MHz is feasible using the on–chip transistor with a 5th or 7th overtone crystal. To enhance operation using an overtone crystal, the internal transistor bias is increased by adding an external resistor from Pin 29 to VEE, however, with an external resistor, the oscillator stays on during power down. Typically,  $-10~{\rm dBm}$  of local oscillator drive is needed to adequately drive the mixer. With an external oscillator source, the IC can be operated up to 500 MHz.

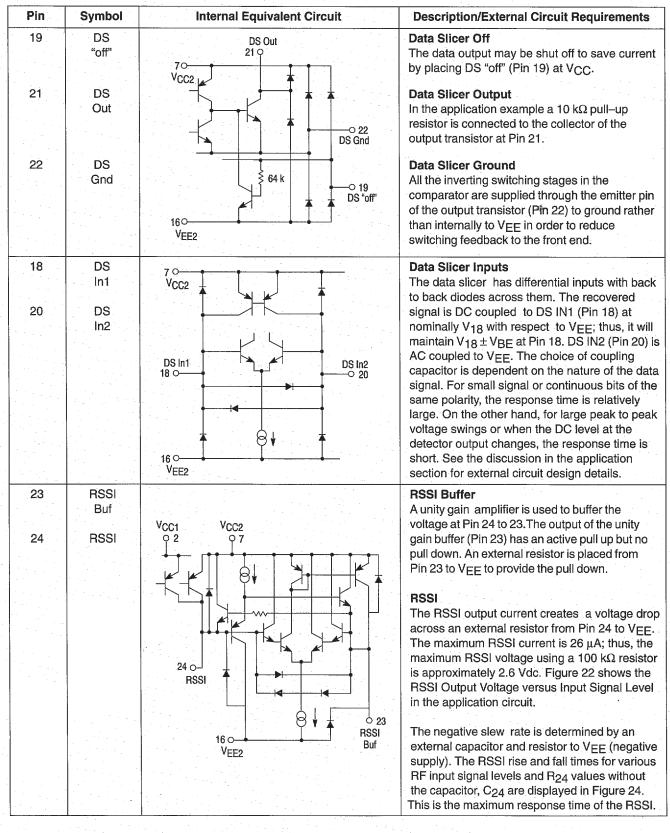

#### **RSSI**

The Received Signal Strength Indicator (RSSI) output is a current proportional to the log of the received signal amplitude. The RSSI current output is derived by summing the currents from the mixer, IF and limiting amplifier stages. An increase in RSSI dynamic range, particularly at higher input signal levels is achieved. The RSSI circuit is designed to provide typically 85 dB of dynamic range with temperature compensation.

Linearity of the RSSI is optimized by using external ceramic bandpass filters which have an insertion loss of 4.0 dB and 330  $\Omega$  source and load impedance. For higher data rates used in DECT and related applications, LC bandpass filtering is necessary to acquire the desired bandpass response; however, the RSSI linearity will require the same insertion loss.

#### **RSSI BUFFER**

The RSSI output current creates a voltage across an external resistor. A unity voltage—gain amplifier is used to buffer this voltage.

The output of this buffer has an active pull—up but no pull—down, so it can also be used as a peak detector. The negative slew rate is determined by external capacitance and resistance to the negative supply.

#### IF AMPLIFIER

The first IF amplifier section is composed of three differential stages with the second and third stages contributing to the RSSI. This section has internal DC feedback and external input decoupling for improved symmetry and stability. The total gain of the IF amplifier block is approximately 40 dB at 10.7 MHz.

The fixed internal input impedance is 330  $\Omega$ . When using ceramic filters requiring source and loss impedances of 330  $\Omega$ , no external matching is necessary. Overall RSSI linearity is dependent on having total midband attenuation of 10 dB (4.0 dB insertion loss plus 6.0 dB impedance matching loss) for the filter. The output of the IF amplifier is buffered and the impedance is 330  $\Omega$ .

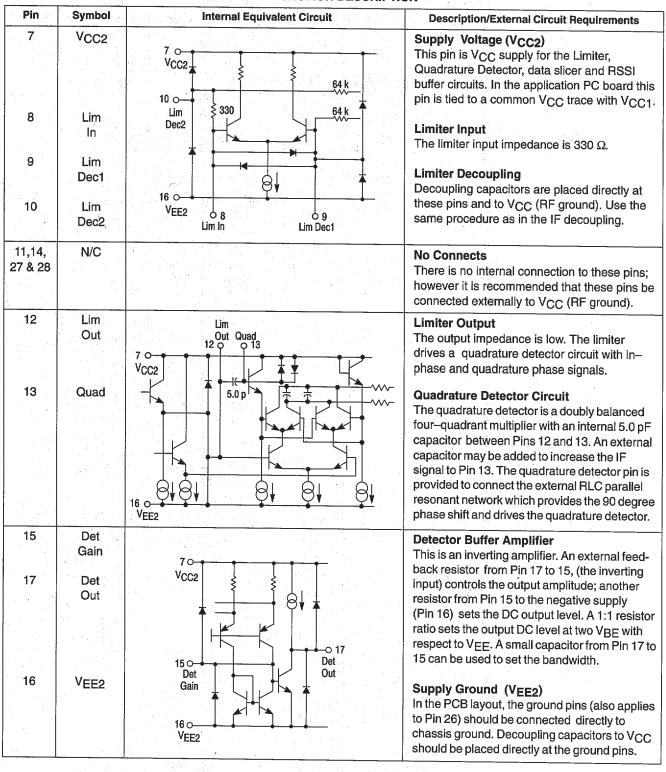

#### LIMITER

The limiter section is similar to the IF amplifier section except that five differential stages are used. The fixed internal input impedance is 330  $\Omega$ . The total gain of the limiting amplifier section is approximately 70 dB. This IF limiting amplifier section internally drives the quadrature detector section and it is also brought out on Pin 12.

#### QUADRATURE DETECTOR

The quadrature detector is a doubly balanced four quadrant multiplier with an internal 5.0 pF quadrature capacitor between Pins 12 and 13. An external capacitor may be added between these pins to increase the IF signal to the external parallel RLC resonant circuit that provides the 90 degree phase shift and drives the quadrature detector. A single pin (Pin 13) provides for the external LC parallel resonant network and the internal connection to the quadrature detector.

Internal low pass filter capacitors have been selected to control the bandwidth of the detector. The recovered signal is brought out by the inverting amplifier buffer. An external feedback resistor from the output (Pin 17) to the output amplitude; it is combined with another external resistor from the input to the negative supply (Pin 15) controls the output amplitude; it is combined with another external resistor from the input to the negative supply (Pin 16) to set the output DC level. For a resistor ratio of 1, the DC level at the detector output is 2.0 VBE (see Figure 12). A small capacitor C17 across the first resistor (from Pin 17 to 15) can be used to reduce the bandwidth.

#### **DATA SLICER**

The data slicer is a comparator that is designed to square up the data signal. Across the data slicer inputs (Pins 18 and 20) are back to back diodes.

The recovered data signal from the quadrature detector can be DC coupled to the data slicer DS IN1 (Pin 18). In the application circuit shown in Figure 1 it will be centered at  $2.0~\mathrm{V_{BE}}$  and allowed to swing  $\pm~\mathrm{V_{BE}}$ . A capacitor is placed from DS IN2 (Pin 20) to VEE. The size of this capacitor and the nature of the data slicer shapes up the recovered signal. The time constant is short for large peak to peak voltage swings or when there is a change in DC level at the detector output. For small signal or for continuous bits of the same polarity which drift close to the threshold voltage, the time

constant is longer.

A unique feature of the data slicer is that inverting switching stages in the comparator are supplied through the emitter pin of the output transistor (Pin 22 – DS Gnd) to  $V_{EE}$  rather than internally to  $V_{EE}$ . This is provided in order to reduce switching feedback to the front end. A control pin is provided to shut the data slicer output off (DS "off" – Pin 19). With DS "off" pin at  $V_{CC}$  the data slicer output is

shut off by shutting down the base drive to the output transistor. When a channel is being monitored to make an RSSI measurement, but not to collect data, the data output may be shut off to save current

#### APPLICATIONS INFORMATION

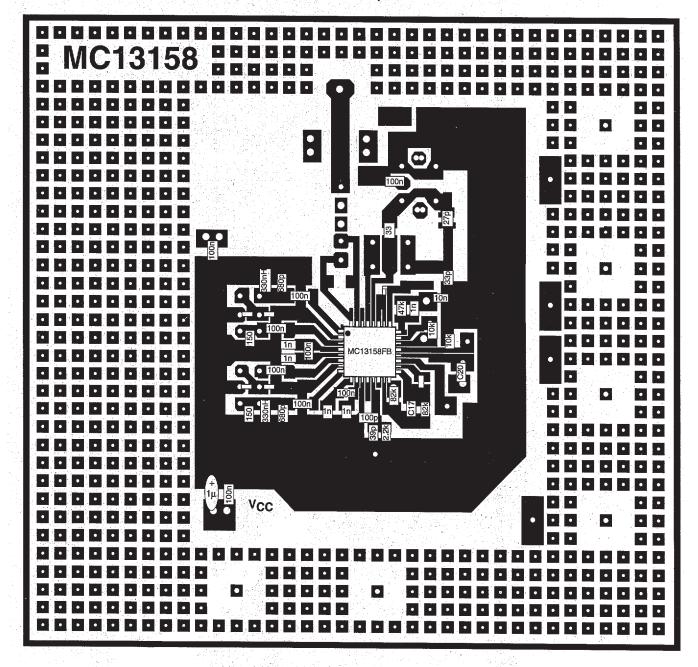

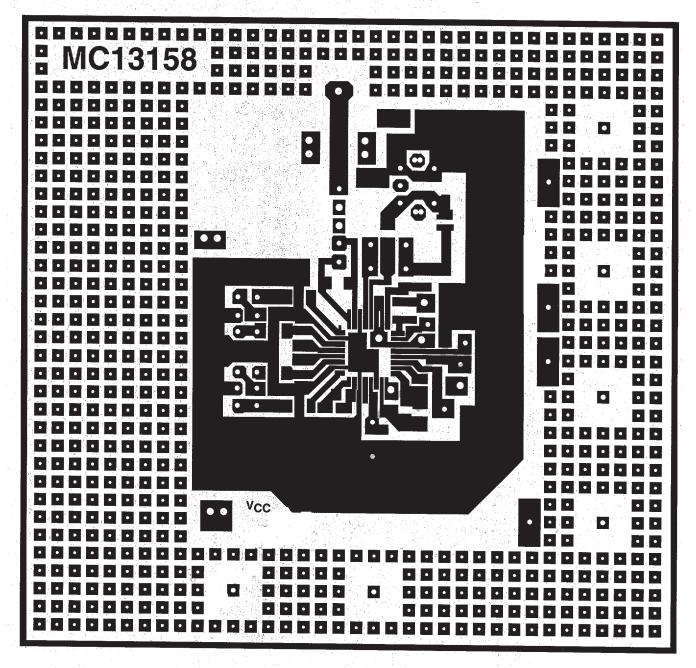

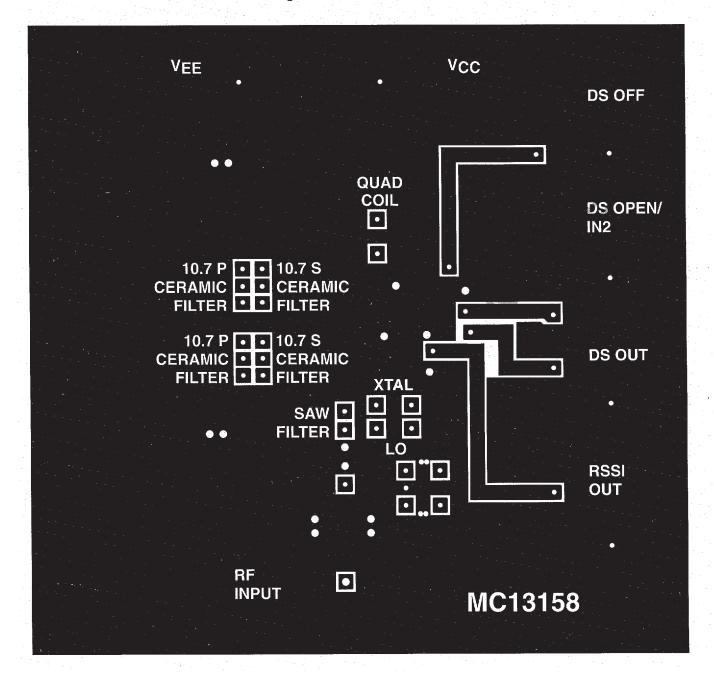

#### **EVALUATION PC BOARD**

The evaluation PCB is very versatile and is intended to be used across the entire useful frequency range of this device. The center section of the board provides an area for attaching all SMT components to the circuit side and radial leaded components to the component ground side (see Figures 29 and 30). Additionally, the peripheral area surrounding the RF core provides pads to add supporting and interface circuitry as a particular application requires. This evaluation board will be discussed and referenced in this section.

#### COMPONENT SELECTION

The evaluation PC board is designed to accommodate specific components, while also being versatile enough to use components from various manufacturers and coil types. Figures 13 and 14 show the placement for the components specified in the application circuit (Figure 12). The application circuit schematic specifies particular components that were used to achieve the results shown in the typical curves and tables but alternate components should give similar results.

Figure 12. Application Circuit (4) 122.7 MHz 33 p 5th OT Crystal 27 p (6) 0.68 µH (5) 95 nH RF Input 10 n Saw 112 MHz 4.7 k 335 Enable Filter 32 31 30 29 28 27 25 RSSI N/C N/C V<sub>EE1</sub> Enable Out Mixer (2) LCR Filter 100 n 24 680 p V<sub>CC1</sub> 23 2 100 k IF Amp 330 nH 100 n 22 3 10 n ML13158 21 4 10 k 100 n O DS Out 1.0 n 20 5 O DS In2 士 C<sub>20</sub> 330 nH 19 6 O DS "off Quad 100 n Detector 150 Lim Amp 7  $V_{CC2}$ 18 DS In1 (2)680 p 5.0 p 17 8 N/C 100 n Bias C<sub>17</sub> 11 9 10 12 14 15 13 16 R<sub>17</sub> 82 k R<sub>15</sub> 100 n 1.0 n 1.0 n 100 p 39 p 2.2 k

NOTES: 1. Saw Filter - Siemens part number Y6970M(5 pin SIP plastic package).

- An LCR filter reduces the broadband noise in the IF; ceramic filters may be used for data rates under 500 kHz. 4.0 dB insertion loss filters optimize the linearity of RSSI.

- 3. The quadrature tank components are chosen to optimize linearity of the recovered signal while maintaining adequate recovered signal level. 1.5 μH 7.0 mm variable shielded inductor: Toko part # 292SNS–T1373Z. The shunt resistor is approximately equal to Q(2πfL), where Q ~ 18 (3.0 dB BW = 600 kHz).

- 4. The local oscillator circuit utilizes a 122.7 MHz, 5th overtone, series resonant crystal specified with a frequency tolerance of 25 PPM, ESR of 120 Ω max. The oscillator configuration is an emitter coupled butter.

- 5. The 95 NH (Nominal) inductor is a 7.0 mm variable shielded inductor: Coilcraft part # 150-04J08S or equivalent.

- 6. 0.68 µH axial lead chokes (molded inductor ): Coilcraft part # 90–11.

- 7. To enable the IC, Pin 25 is taken to V<sub>EE</sub>. The external pull down resistor at Pin 29 could be linked to the enable function; otherwise if it is taken to V<sub>EE</sub> as shown, it will keep the oscillator biased at about 500 μA depending on the V<sub>CC</sub> level.

Figure 13. Circuit Side Component Placement

VEE VCC **DS OFF** QUAD COIL DS OPEN/ IN<sub>2</sub> 10.7 S CERAMIC • CERAMIC **FILTER** FILTER • 10.7 P • 1 10.7 S • **DS OUT** CERAMIC • | CERAMIC FILTER • FILTER **XTAL** SAW **FILTER** LO **RSSI** OUT RF **INPUT** MC13158 SMA

Figure 14. Ground Side Component Placement

#### INPUT MATCHING/COMPONENTS

It is desirable to use a SAW filter before the mixer to provide additional selectivity and adjacent channel rejection. In a wideband system the primary sensitivity of the receiver backend may be achieved before the last mixer. Bandpass filtering in the limiting IF is costly and difficult to achieve for bandwidths greater than 280 kHz.

The SAW filter should be selected to easily interface with the mixer differential input impedance of approximately 2.0 k $\Omega$  in parallel with 1.0 pF. The PC board is dedicated to the Siemens SAW filter (part number Y6970M); the part is designed for DECT at 112 MHz 1st IF frequency. It is designed for a load impedance of 2.0

$k\Omega$  in parallel with 2.0 pF; thus, no or little input matching is required between the SAW filter and the mixer.

The Siemens SAW filter has an insertion loss of typically 10 dB and a 3.0 dB bandwidth of 1.0 MHz. The relatively high insertion loss significantly contributes to the system noise and a filter having lower insertion loss would be desirable. In existing low loss SAW filters, the required load impedance is 50  $\Omega$ ; thus, interface matching between the filter and the mixer will be required. Figure 15 is a table of the single–ended mixer input impedance. A careful noise analysis is necessary to determine the secondary contribution to system noise.

Figure 15. Mixer Input Impedance

(Single-ended)

|      | f<br>(MHz) | Rs<br>(Ω) | Xs<br>(Ω) | Rp<br>(Ω) | Xp<br>(Ω) | Cp<br>(pF) |

|------|------------|-----------|-----------|-----------|-----------|------------|

|      | 50         | 930       | -350      | 1060      | -2820     | 1.1        |

|      | 100        | 480       | -430      | 865       | -966      | 1.6        |

|      | 150        | 270       | -400      | 860       | -580      | 1.8        |

|      | 200        | 170       | -320      | 770       | -410      | 1.9        |

|      | 250        | 130       | -270      | 690       | -330      | 1.85       |

|      | 300        | 110       | -250      | 680       | -300      | 1.8        |

|      | 400        | 71        | -190      | 580       | -220      | 1.8        |

|      | 500        | 63        | -140      | 370       | -170      | 1.9        |

| H.H. | 600        | 49        | -110      | 300       | -130      | 2.0        |

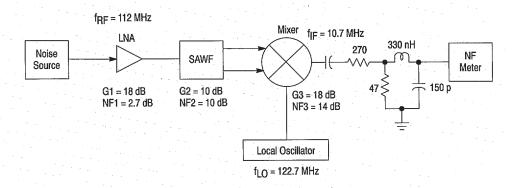

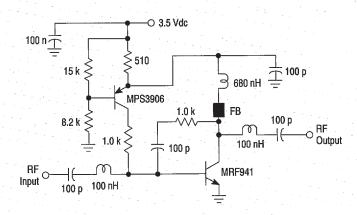

#### SYSTEM NOISE CONSIDERATIONS

The system block diagram in Figure 16 shows the cascaded noise stages contributing to the system noise; it represents the application circuit in Figure 12 and a low noise preamp using a MRF941 translator (see Figure 17). The preamp is designed for a conjugately matched input and output at 2.0 Vdc. VCE and 3.0 mAdc  $I_{\text{C}}.$  Sparameters at 2.0 V, 3.0 mA and 100 MHz are:

S11 = 0.86, -20

S21 = 9.0, 164

S12 = 0.02, 79

S22 = 0.96, -12

The bias network and VCE at 2.0 V and  $I_c$  at 3.0 mA for VCC = 3.0 to 3.5 Vdc. The preamp operates with 18 dB gain and 2.7 dB noise figure.

In the cascaded noise analysis the system noise equation is:

Fsystem = F1 + [(F2-1)/G1] + [(F3-1)]/[(G1)(G2)]

where:

F1 = the Noise Factor of the Preamp

G1= the Gain of the Preamp

F2 = the Noise factor of the SAW filter

G2 =the Gain of the SAW filter

F3 = the Noise factor of the Mixer

Note: the proceeding terms are defined as linear relationships and are related to the log form for gain and noise figure by the following:

$$F = log - 1$$

[(NF in dB)/10] and similarly

$$G = \log(1)[(NF \text{ in } dB)/10]$$

The noise figure and gain measured in dB are shown in the system block diagram. The mixer noise figure is typically 14 dB and the SAW filter adds typically 10 dB insertion loss. Addition of a low noise preamp having a 18 dB gain and 2.7 dB noise figure not only improves th system noise figure but it increases the reverse isolation from the local oscillator to the antenna input at the receiver. Calculating in terms of gain and noise factor yields the following:

$$F1 = 1.86$$

;  $G1 = 63.1$

$$F2 = 10$$

;  $G2 = 0.1$

$$F3 = 25.12$$

Thus, substituting in the equation for system noise factor:

Fsystem =

$$5.82$$

; NFsystem =  $7.7 \text{ dB}$

Figure 16. System Block Diagram for Noise Analysis

Figure 17. 112 MHz LNA

#### LOCAL OSCILLATORS

#### VHF APPLICATIONS

The on-chip grounded collector transistor may be used for HF and VHF local oscillator with higher order overtone crystals. The local oscillator in the application circuit (Figure 12) shows a 5th overtone oscillator at 122.7 MHz. This circuit uses a Butler overtone oscillator configuration. The amplifier is an emitter follower. The crystal is driven from the emitter and is coupled to the high impedance base through a capacitive tap network. Operation at the desired overtone frequency is ensured by the parallel resonant circuit formed by the variable inductor and the tap capacitor and parasitic capacitances of the on-chip transistor and PC board. The variable inductor specified in the schematic could be replaced with a high tolerance, high Q ceramic or air wound surface mount component if the other components have tight enough tolerances. A variable inductor provides an adjustment for gain and frequency of the resonant tank ensuring lock up and start—up of the crystal oscillator. The overtone crystal is chosen with ESR of typically  $80 \Omega$  and 120 $\Omega$  maximum; if the resistive loss in the crystal is too high the performance of oscillator may be impacted by lower gain margins.

A series LC network to ground (which is  $V_{CC}$ ) is comprised of the inductance of the base lead of the on–chip transistor and PC board

traces and tap capacitors. Parasitic oscillations often occur in the 200 to 800 MHz range. A small resistor is placed in series with the base (Pin 28) to cancel the negative resistance associated with this undesired mode of oscillation. Since the base input impedance is so large a small resistor in the range of 27 to 68  $\Omega$  has very little effect on the desired Butler mode of oscillation.

The crystal parallel capacitance,  $C_0$ , provides a feedback path that is low enough in reactance at frequencies of 5th overtones or higher to cause trouble.  $C_0$  has little effect near resonance because of the low impedance of the crystal motional arm  $(R_m-L_m-C_m)$ . As the tunable inductor which forms the resonant tank with the tap capacitors is tuned "off" the crystal resonant frequency it may be difficult to tell if the oscillation is under crystal control. Frequency jumps may occur as the inductor is tuned. In order to eliminate this behavior an inductor,  $L_0$ , is placed in parallel with the crystal.  $L_0$  is chosen to be resonant with he crystal parallel capacitance,  $C_0$ , at the desired operation frequency. The inductor provides a feedback path at frequencies well below resonance; however, the parallel tank network of the tap capacitors and tunable inductor prevent oscillation at these frequencies.

#### IF FILTERING/MATCHING

In wideband data systems the IF bandpass needed is greater than can be found in low cost ceramic filters operating at 10.7 MHz. It is necessary to bandpass limit with LC networks or series—parallel ceramic filter networks. Murata offers a series—parallel resonator pair (part number KMFC545) with a 3.0 dB band width of  $\pm 325$  kHz and a maximum insertion loss of 5.0 dB. The application PC board is laid out to accommodate this filter pair (a filter pair is used at both locations of the split IF). However, even using a series parallel ceramic filter network yields only a maximum bandpass of 650 kHz. In some applications a wider band IF bandpass is necessary.

A simple LC network yields a bandpass wider than the SAW filter but it does reduce an appreciable amount of wideband IF noise. In the application circuit an LC network is specified using surface mount components. The parallel LC components are placed from the outputs of the mixer and IF amplifier to the  $V_{CC}$  trace; internal 330 $\Omega$  loads are connected from the mixer and IF amplifier outputs DEC2 (Pin 5 and 10 respectively). This loads the outputs with the optimal load impedance but creates a low insertion loss filter. An external shunt resistor may be used to widen the bandpass and to acquire the 10 dB composite loss necessary to linearize the RSSI output. The equivalent circuit is shown in Figure 18.

Figure 18. IF LCR Filter Equivalent

The following equations satisfy the 12 dB loss (1:4 resistive ratio):

(Rext)(330)/(Rext + 330) = RequivalentRequivalent/Requivalent + 330) = 1/4

Solve for Requivalent:

4(Requivalent) = Requivalent + 330

3(Requivalent) = 330

Requivalent = 110

Substitue for Requivalent and solve for Rext

330(Rext) = 110 (Rext) + (330)(110)

Rext = (330)(110)/220

Rext -  $165 \Omega$

The IF is 10.7 Mhz although any IF between 10 to 20 MHz could be used. The value of the coil is lowered from that used in the quadrature circuit because the unloaded Q must be maintained in a surface mount component. A standard value component having an unloaded Q = 100 at 10.7 MHz is 330 nH; therefore the capacitor is 669 pF. Standard values have been chosen for these components;

Rext = 150 Q

C = 680 pF

L = 330 nH

Computation of the loaded Q of the is LCR network is

O = Requivalent/XI

where  $XL = 2\pi fl$  and Requivalent is 103  $\Omega$

Thus, Q = 4.65

The total system loss is

$20 \log (103/433) = -12.5 \text{ dB}$

#### QUADRATURE DETECTOR

The quadrature detector is coupled to the IF with an internal 5.0 pF capacitor between Pins 12 and 13. For wideband data applications, the drive to the detector can be increased with an additional external capacitor between these pins; thus, the recovered signal level output is increased for a given bandwidth.

The wideband performance of the detector is controlled by the loaded Q of the LC tank circuit. The following equation defines the components which set the detector circuit's bandwidth:

$$Q = R_T/X_L$$

[1]

where RT is the equivalent shunt resistance across the LC Tank XL is the reactance of the quadrature inductor at the IF frequency ( $X_L = 2\pi fl$ ).

The inductor and capacitator are chosen to form a resonant LC tank with the PCB and parasitic device capacitance at the desired IF center frequency as predicted by

$$fc = [2\pi (LC_p)^{1/2}]^{-1}$$

[2]

where L is the parallel tank inductor Cp is the equivalent parallel capacitance of the parallel resonant tank circuit.

The following is a design example for a wideband detector at 10.7 MHz and a loaded Q of 18. The loaded Q of the quadrature detector is chosen somewhat less than the Q of the IF bandpass. For an IF frequency of 10.7 MHz and an IF bandpass of 600 kHz, the IF bandpass Q is approximately 6.4.

#### **EXAMPLE:**

Let the external Cext = 139 pF. (The miminum value here should be much greater than the internal device and PCB parasitic capacitance, Cint = 3.0 pF.). Thus, Cp = Cint + Cext = 142 pF.

Rewrite equation (2) and solve for L

$L = (0.159)^2/(Cpfc^2)$

$L = 1.56 \mu H$ ; Thus, a standard value is chosen:

$L = 1.56 \mu H$  (tunable shielded inductor)

The value of the total damping resistor to obtain the required loaded Q of 18 can be calculated by rearranging equation (1):

$$R_T = Q(2\pi fl)$$

$$R_T = 18(2\pi)(10.7)(1.5) = 1815\Omega$$

The internal resistance, Rint at the quadrature tank Pin 13 is approximately 13 k $\Omega$  and is considered in determining the external resistance, Rext which is calculated from

$Rext = ((R_T)(Rint))/(Rint - R_T)$

Rext = 2110; Thus choose the standard value

$Rext = 2.2 k\Omega$

It is important to set the DC level of the detector output at Pin 17 to center the peak to peak swing of the recovered signal. In the equivalent internal circuit shown in the Pin Function Description, the reference voltage at the positive terminal of the inverting, op amp buffer amplifier is set at  $1.0 \, \mathrm{V_{BE}}$ . The detector DC level,  $V_{17}$  is determined by the following equation:

$$V_{17} = [((R_{15}/R_{17}) + 1)/(R_{15}/R_{17})] V_{BE}$$

Thus for a 1:1 ratio of  $R_{15}/R_{17}$ ,  $V_{17}$  = 2.0  $V_{BE}$  = 1.4 Vdc. Similarly for a 2:1,  $V_{17}$  = 1.5  $V_{BE}$  = 1.05 Vdc; and for 3:1,  $V_{17}$  = 1.33  $V_{BE}$  = 0.93 Vdc.

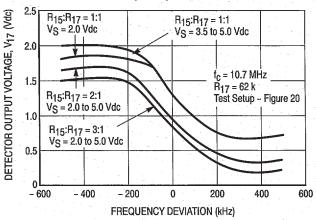

Figure 19 shows the detector "S–Curves", in which the resistor ratio is varied while maintaining a constant gain (R<sub>17</sub> is held at 62 k $\Omega$ ). R<sub>15</sub> is 62 k $\Omega$  for a 1:1 ratio; while R<sub>15</sub> = 120 k $\Omega$  and 180 k $\Omega$  to produce the 2:1 and 3:1 ratio. The IF signal into the detector is swept  $\pm$  500 KHz about the 10.7 MHz, IF center frequency. The resulting curve show how the resistor ratio and the supply voltage effects the symmetry of the "S–curve" (Figure 21 Test Setup). For the 3:1 and 2:1 ratio, symmetry is maintained with VS from 2.0 to 5.0 Vdc; however, for the 1:1 ratio, symmetry is lost at 2.0 Vdc.

Figure 19. Detector Output Voltage versus Frequency Deviation

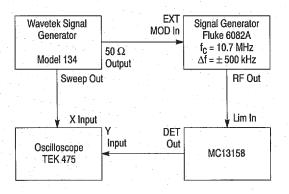

Figure 20. Demodulator "S-Curve" Test Setup

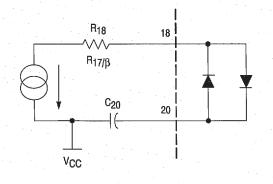

#### DATA SLICER CIRCUIT

C20 at the input of the data slicer is chosen to maintian a time constant long enought to hold the charge on the capacitor for the longest strings of bits at the same polarity. For a data rate of 576 kHz a bit stream of 15 bits at the same plarity would equate to an apparent data rate of approximately 77 kbps or 38 kHz. The time constant would be approximately 26 µs. The following expression equates the time constant t, to the external components;

$$t = 2\pi (R_{18})(C_{20})$$

Solve for C<sub>20</sub>:

$$C_{20} = t/2\pi (R_{18})$$

where the effective resistance  $R_{18}$  is a complex function of the demodulator feedback resistance and data slicer input circuit. In the data input network the back to back diodes form a charge and discharge path for the capacitor at Pin 20; however, the diodes create a non–linear response. This resistance is loaded by the  $\beta$ , beta of the detector output transistor; beta = 100 is a typical value (see Figure 21). Thus, the apparent value of the resitance at Pin 18 (DS IN1) is approximately equal to:

$$R_{18} \sim R_{17}/100$$

where R<sub>17</sub> is 82 k $\Omega$ , the feedback resistor from Pin 17 to 15. Therefore, substituting for R<sub>18</sub> and solving for C<sub>20</sub>:

$$C_{20} = 15.9 \text{ (t)/R}_{17} = 5.04 \text{ nF}$$

The closest standard value is 4.7 nF.

Figure 21. Data Slicer Equivalent Input Circuit

#### **RSSI**

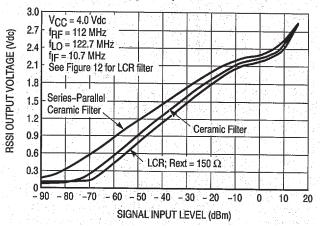

In Figure 22, the RSSI versus RF Input Level shows the linear response of RSSI over a 65 dB range but it has extended capability over 80 dB from –80 dBm to +10 dBm. The RSSI is measured in the application circuit (Figure 12) in which a SAW filter is used before the mixer; thus, the overall sensitivity is traded off for the sake of selectivity. The curves are shown for three filters having different bandwidths:

- 1) LCR Filter with 2.3 MHz 3.0 dBm BW (Circuit and Component Placement is shown in Figure 12)

- Series–Parallel Ceramic Filter with 650 kHz 3.0 dB BW (Murata Part # KMFC - 545)

- 3) Ceramic Filter with 280 kHz 3.0 dB BW.

Figure 22. RSSI Output Voltage versus Signal Input Level

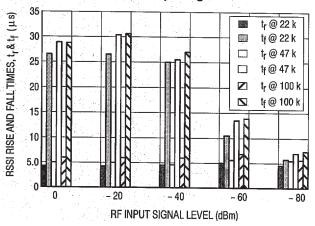

Figure 23. RSSI Output Rise and Fall Times versus RF Input Signal Level

#### SINAD PERFORMANCE

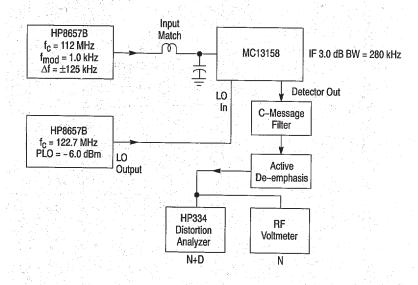

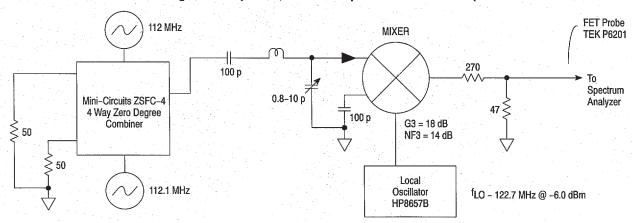

Figure 24 shows a test setup for a narrowband demodulator output response in which a C-message filter and an active de-emphasis filter is used following the demodulator. The input is matched using a 1:4 impedance transformer. The SINAD performance is shown in Figure 25 with no preamp and in Figure 26 with a preamp (Preamp-Figure 16). The 12 dB SINAD sensitivity is -101 dBm with no preamp and -113 dBm with the preamp.

Input Signal Level (with preamp) 10 S+N+D  $V_S = 3.0 \text{ Vdc}$  $f_{dev} = \pm 125 \text{ kHz}$ S+N+D, N+D, N (dB) f<sub>mod</sub> = 1.0 kHz - 20 fRF = 112 MHz IF 3.0 dB BW = 280 kHz N+D 30 - 40 - 50 - 60 N -70 L -120 -100RF INPUT SIGNAL (dBm)

Figure 26. S+N+D, N+D, N versus

Figure 27. Input IP3, 1.0 dB Compression Pt. Test Setup

Figure 28. 1.0 dB Compression Pt. and Input **Third Order Intercept** -10 1.0 dB Comp. Pt. = -39 dBm - 20 IP3 = -32 dBmS+N+D, N+D, N (dB) - 30 - 40 Vs = 3.5 Vdc - 50 fRF1 = 112 kHz fBF2 = 112.1 kHz - 60 f<sub>LO</sub> = 122.7 MHz PLO = -6.0 dBm -70 See Figure 27 - 80 - 60 - 20

RF INPUT SIGNAL LEVEL (dBm)

Figure 29. Circuit Side View

Figure 30. Ground Side View

#### **OUTLINE DIMENSIONS**

Lansdale Semiconductor reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Lansdale does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. "Typical" parameters which may be provided in Lansdale data sheets and/or specifications can vary in different applications, and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts. Lansdale Semiconductor is a registered trademark of Lansdale Semiconductor, Inc.