# ML12210 Serial Input PLL Frequency Synthesizer

Legacy Device: Motorola MC12210

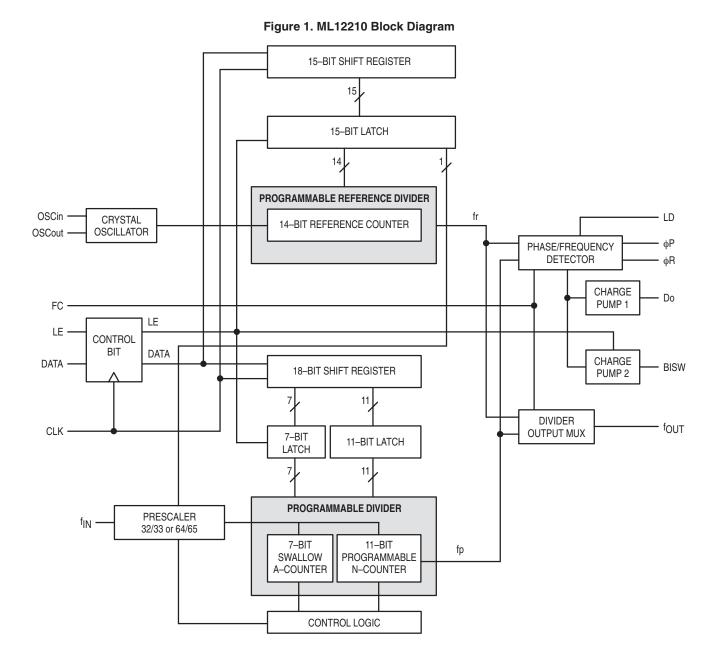

The ML12210 is a 2.5 GHz Bipolar monolithic serial input phase locked loop (PLL) synthesizer with pulse–swallow function. It is designed to provide the high frequency local oscillator signal of an RF transceiver in handheld communication applications.

The technology used allows for low power operation at a minimum supply voltage of 2.7 V. The device is designed for operation over 2.7 to 5.5 V supply range for input frequencies up to 2.5 GHz with a typical current drain of 9.5 mA. The low power consumption makes the ML12210 ideal for handheld battery operated applications such as cellular or cordless telephones, wireless LAN or personal communication services. A dual modulus prescaler is integrated to provide either a 32/33 or 64/65 divide ratio.

- Low Power Supply Current of 8.8 mA Typical for I<sub>CC</sub> and 0.7 mA Typical for Ip

- Supply Voltage of 2.7 to 5.5 V

- Dual Modulus Prescaler With Selectable Divide Ratios of 32/33 or 64/65

- On-Chip Reference Oscillator/Buffer

- Programmable Reference Divider Consisting of a Binary 14–Bit Programmable Reference Counter

- Programmable Divider Consisting of a Binary 7–Bit Swallow Counter and an 11–Bit Programmable Counter

- Phase/Frequency Detector With Phase Conversion Function

- Balanced Charge Pump Outputs

- Dual Internal Charge Pumps for Bypassing the First Stage of the Loop Filter to Decrease Lock Time

- Outputs for External Charge Pump

- Operating Temperature Range of  $T_A = -40$  to 85°C

NOTE: Also available is the ML12202, a 1.1 GHz version of this function.

## MAXIMUM RATINGS (Note 1)

| Parameter                   | Symbol         | Value                  | Unit |

|-----------------------------|----------------|------------------------|------|

| Power Supply Voltage, Pin 4 | VCC            | -0.5 to 6.0            | Vdc  |

| Power Supply Voltage, Pin 3 | V <sub>p</sub> | V <sub>CC</sub> to 6.0 | Vdc  |

| Storage Temperature Range   | Tstg           | -65 to 150             | °C   |

NOTES: 1. Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions.

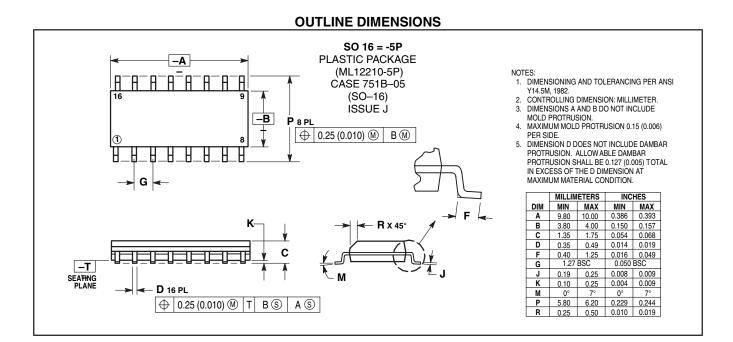

SO 16 = -5P PLASTIC PACKAGE CASE 751B (SO-16)

#### **CROSS REFERENCE/ORDERING INFORMATION**

PACKAGEMOTOROLALANSDALESO 16MC12210DML12210-5P

**Note**: Lansdale lead free (**Pb**) product, as it becomes available, will be identified by a part number prefix change from **ML** to **MLE**.

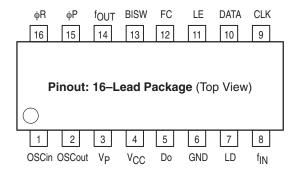

## **PIN NAMES**

| Pin             | I/O | Function                                                                                                                                                                                                                                                                                                    | 16–Lead Pkg<br>Pin No. | 20-Lead Pkg<br>Pin No. |

|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|

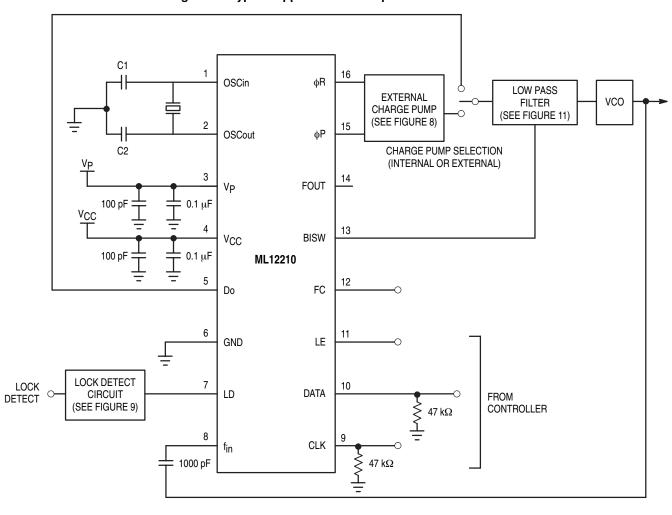

| OSCin           | I   | Oscillator input. A crystal may be connected between OSCin and OSCout. It is highly recommended that an external source be ac coupled into this pin (see text).                                                                                                                                             | 1                      |                        |

| OSCout          | 0   | Oscillator output. Pin should be left open if external source is used                                                                                                                                                                                                                                       | 2                      |                        |

| V <sub>P</sub>  | _   | Power supply for charge pumps (Vp should be greater than or equal to Vcc) Vp provides power to the Do, BISW and $\phi P$ outputs                                                                                                                                                                            | 3                      |                        |

| V <sub>CC</sub> | -   | Power supply voltage input. Bypass capacitors should be placed as close as possible to this pin and be connected directly to the ground plane.                                                                                                                                                              | 4                      |                        |

| Do              | 0   | Internal charge pump output. Do remains on at all times                                                                                                                                                                                                                                                     | 5                      |                        |

| GND             | -   | Ground                                                                                                                                                                                                                                                                                                      | 6                      |                        |

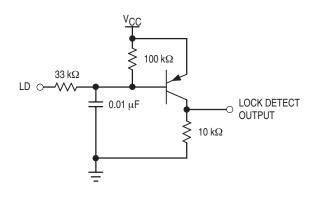

| LD              | 0   | Lock detect, phase comparator output                                                                                                                                                                                                                                                                        | 7                      |                        |

| fIN             | I   | Prescaler input. The VCO signal is AC–coupled into this pin                                                                                                                                                                                                                                                 | 8                      |                        |

| CLK             | I   | Clock input. Rising edge of the clock shifts data into the shift registers                                                                                                                                                                                                                                  | 9                      |                        |

| DATA            | I   | Binary serial data input                                                                                                                                                                                                                                                                                    | 10                     |                        |

| LE              | I   | Load enable input (with internal pull up resistor). When LE is HIGH or OPEN, data stored in the shift register is transferred into the appropriate latch (depending on the level of control bit). Also, when LE is HIGH or OPEN, the output of the second internal charge pump is connected to the BISW pin | 11                     |                        |

| FC              | I   | Phase control select (with internal pull up resistor). When FC is LOW, the characteristics of the phase comparator and charge pump are reversed. FC also selects fp or fr on the f <sub>OUT</sub> pin                                                                                                       | 12                     |                        |

| BISW            | 0   | Analog switch output. When LE is HIGH or OPEN ("analog switch is ON") the output of the second charge pump is connected to the BISW pin. When LE is LOW, BISW is high impedance                                                                                                                             | 13                     |                        |

| fOUT            | 0   | Phase comparator input signal. When FC is HIGH, f <sub>OUT</sub> =fr, programmable reference divider output; when FC is LOW, f <sub>OUT</sub> =fp, programmable divider output                                                                                                                              | 14                     |                        |

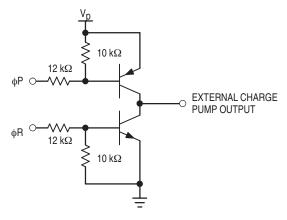

| φР              | 0   | Output for external charge pump. Standard CMOS output level                                                                                                                                                                                                                                                 | 15                     |                        |

| φR              | 0   | Output for external charge pump. Standard CMOS output level                                                                                                                                                                                                                                                 | 16                     |                        |

| NC              | _   | No connect                                                                                                                                                                                                                                                                                                  | _                      |                        |

## **DATA ENTRY FORMAT**

The three wire interface of DATA pin, CLK (clock) pin and LE (load enable) pin controls the serial data input of the 14-bit programmable reference divider plus the prescaler setting bit, and the 18-bit programmable divider. A rising edge of the clock shifts one bit of serial data into the internal shift registers. Depending upon the level of the control bit, stored data is transferred into the latch when load enable pin is HIGH or OPEN.

Control bit: "H" = data is transferred into 15-bit latch of programmable reference divider

"L" = data is transferred into 18-bit latch of programmable divider

WARNING: Switching CLK or DATA after the device is programmed may generate noise on the charge pump outputs which will affect the VCO.

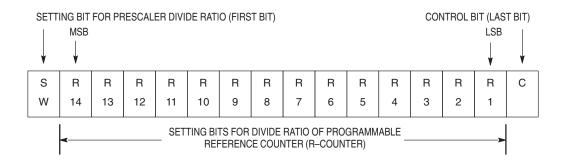

## PROGRAMMABLE REFERENCE DIVIDER

16—bit serial data format for the programmable reference counter, "R—counter", and prescaler select bit (SW) is shown below. If the control bit is HIGH, data is transferred from the 15—bit shift register into the 15—bit latch which specifies the R divide ratio (8 to 16383) and the prescaler divide ratio (SW=0 for  $\div$ 64/65, SW=1 for  $\div$ 32/33). An R divide ratio less than 8 is prohibited.

For Control bit (C) = HIGH:

## DIVIDE RATIO OF PROGRAMMABLE REFERENCE (R) COUNTER

| Divide<br>Ratio R | R<br>14 | R<br>13 | R<br>12 | R<br>11 | R<br>10 | R<br>9 | R<br>8 | R<br>7 | R<br>6 | R<br>5 | R<br>4 | R<br>3 | R<br>2 | R<br>1 |

|-------------------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| 8                 | 0       | 0       | 0       | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 0      | 0      |

| 9                 | 0       | 0       | 0       | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 0      | 1      |

| •                 | •       | •       | •       | •       | •       | •      | •      | •      | •      | •      | •      | •      | •      | •      |

| 16383             | 1       | 1       | 1       | 1       | 1       | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

# PRESCALER SELECT BIT

| Prescaler Divide Ratio P | SW |

|--------------------------|----|

| 64/65                    | 0  |

| 32/33                    | 1  |

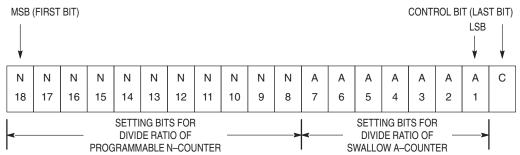

#### PROGRAMMABLE DIVIDER

19—bit serial data format for the programmable divider is shown below. If the control bit is LOW, data is transferred from the 18—bit shift register into the 18—bit latch which specifies the swallow A—counter divide ratio (0 to 127) and the programmable N—counter divide ratio (16 to 2047). An N—counter divide ratio less than 16 is prohibited.

For Control bit (C) = LOW:

## **DIVIDE RATIO OF PROGRAMMABLE N-COUNTER**

## **DIVIDE RATIO OF SWALLOW A-COUNTER**

| Divide<br>Ratio N | N<br>18 | N<br>17 | N<br>16 | N<br>15 | N<br>14 | N<br>13 | N<br>12 | N<br>11 | N<br>10 | N<br>9 | N<br>8 | Divide<br>Ratio A | A<br>7 | A<br>6 | A<br>5 | A<br>4 | A<br>3 | A<br>2 | A<br>1 |

|-------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|--------|--------|-------------------|--------|--------|--------|--------|--------|--------|--------|

| 16                | 0       | 0       | 0       | 0       | 0       | 0       | 1       | 0       | 0       | 0      | 0      | 0                 | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| 17                | 0       | 0       | 0       | 0       | 0       | 0       | 1       | 0       | 0       | 0      | 1      | 1                 | 0      | 0      | 0      | 0      | 0      | 0      | 1      |

| •                 | •       | •       | •       | •       | •       | •       | •       | •       | •       | •      | •      | •                 | •      | •      | •      | •      | •      | •      | •      |

| 2047              | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 1      | 1      | 127               | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

## **DIVIDE RATIO SETTING**

$fvco = [(P \cdot N) + A] \cdot fosc \div R \text{ with } A < N$

fvco: Output frequency of external voltage controlled oscillator (VCO)

N: Preset divide ratio of binary 11-bit programmable counter (16 to 2047)

A: Preset divide ratio of binary 7-bit swallow counter (0 to 127, A<N)

fosc: Output frequency of the external frequency oscillator

R: Preset divide ratio of binary 14-bit programmable reference counter (8 to 16383)

P: Preset mode of dual modulus prescaler (32 or 64)

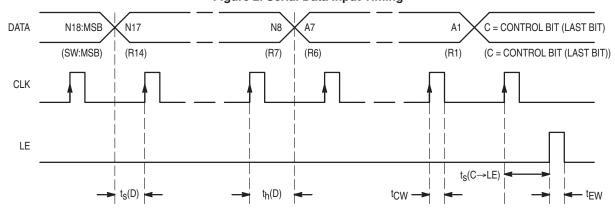

Figure 2. Serial Data Input Timing

NOTES: Programmable reference divider data shown in parenthesis. Data shifted into register on rising edge of CLK.

$\begin{array}{lll} t_S(D) = & \text{Setup Time DATA to CLK} & t_S(D) \geq 10 \text{ ns} \\ t_h(D) = & \text{Hold Time DATA to CLK} & t_h(D) \geq 20 \text{ ns} \\ t_{CW} = & \text{CLK Pulse Width} & t_{CW} \geq 30 \text{ ns} \\ t_{EW} = & \text{LE Pulse Width} & t_{EW} \geq 20 \text{ ns} \\ t_S(C \rightarrow LE) = & \text{Setup Time CLK to LE} & t_S(C \rightarrow LE) \geq 30 \text{ ns} \\ \end{array}$

## PHASE CHARACTERISTICS/VCO CHARACTERISTICS

The phase comparator in the ML12210 is a high speed digital phase frequency detector circuit. The circuit determines the "lead" or "lag" phase relationship and time difference between the leading edges of the VCO (fp) signal and the reference (fr) input. Since these edges occur only once per cycle, the detector has a range of  $\pm 2\pi$  radians. The phase comparator outputs are standard CMOS rail-to-rail levels (VP to GND for  $\phi$ P and V<sub>CC</sub> to GND for  $\phi$ R), designed for up to 20MHz operation into a 15pF load. These phase comparator outputs can be used along with an external charge pump to enhance the PLL characteristics.

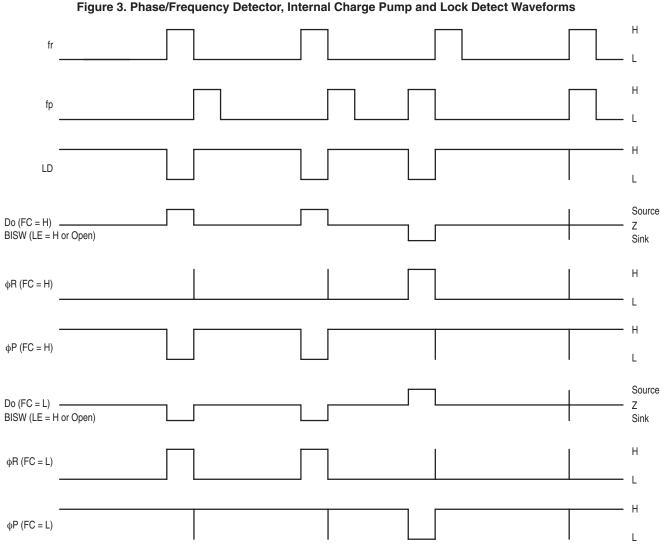

The operation of the phase comparator is shown in Figures 3 and 5. The phase characteristics of the phase comparator are controlled by the FC pin. The polarity of the phase comparator outputs,  $\phi R$  and  $\phi P$ , as well as the charge pump output Do can be reversed by switching the FC pin.

NOTES: Do and BISW are current outputs.

Phase difference detection range:  $-2\pi$  to  $+2\pi$

Spike difference depends on charge pump characteristics. Also, the spike is output in order to diminish dead band. When fr > fp or fr < fp, spike might not appear depending upon charge pump characteristics.

Internal Charge Pump Gain

$$\approx \frac{I_{Source} + I_{Sink}}{4\pi} = \frac{4mA}{4\pi}$$

#### For FC = HIGH:

# fr lags fp in phase OR fp>fr in frequency

When the phase of fr lags that of fp or the frequency of fp is greater than fr, the  $\phi P$  output will remain in a HIGH state while the  $\phi R$  output will pulse from LOW to HIGH. The output pulse will reach a minimum 50% duty cycle under a 180° out of phase condition. The signal on  $\phi R$  indicates to the VCO to decrease in frequency to bring the loop into lock.

# fr leads fp in phase OR fp<fr in frequency

When the phase of fr leads that of fp or the frequency of fp is less than fr, the  $\phi R$  output will remain in a LOW state while the  $\phi P$  output pulses from HIGH to LOW. The output pulse will reach a minimum 50% duty cycle under a 180° out of phase condition. The signal on  $\phi P$  indicates to the VCO to increase in frequency to bring the loop to lock.

# fr = fp in phase and frequency

When the phase and frequency of fr and fp are equal, the output  $\phi P$  will remain in a HIGH state and  $\phi R$  will remain in a LOW state except for voltage spikes when signals are in phase. This situation indicates that the loop is in lock and the phase comparator will maintain the loop in its locked state.

When FC = LOW, the operation of the phase comparator is reversed from the above explanation.

## For FC = LOW:

# fr lags fp in phase OR fp>fr in frequency

When the phase of fr lags that of fp or the frequency of fp is greater than fr, the  $\phi R$  output will remain in a LOW state while the  $\phi P$  output will pulse from HIGH to LOW. The output pulse will reach a minimum 50% duty cycle under a 180° out of phase condition. The signal on  $\phi P$  indicates to the VCO to increase in frequency to bring the loop into lock.

## fr leads fp in phase OR fp<fr in frequency

When the phase of fr leads that of fp or the frequency of fp is less than fr, the  $\phi P$  output will remain in a HIGH state while the  $\phi R$  output pulses from LOW to HIGH. The output pulse will reach a minimum 50% duty cycle under a 180° out of phase condition. The signal on  $\phi R$  indicates to the VCO to decrease in frequency to bring the loop to lock.

## fr = fp in phase and frequency

When the phase and frequency of fr and fp are equal, the output  $\phi P$  will remain in a HIGH state and  $\phi R$  will remain in a LOW state except for voltage spikes when signals are in phase. This situation indicates that the loop is in lock and the phase comparator will maintain the loop in its locked state.

The FC pin controls not only the phase characteristics, but also controls the f<sub>OUT</sub> test pin. The FC pin permits the user to monitor either of the phase comparator input signals, fr or fp, at the f<sub>OUT</sub> output providing a test mode where the programming of the dividers and the output of the counters can be checked. When FC is HIGH, f<sub>OUT</sub> = fr, the programmable reference divider output. When FC is LOW,  $f_{OUT} = fp$ , the programmable divider output.

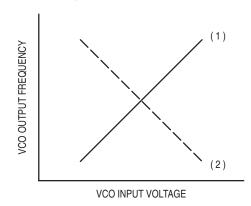

## Hence,

If VCO characteristics are like (1), FC should be set HIGH or OPEN.  $f_{OUT} = f_{T}$  If VCO characteristics are like (2), FC should be set LOW.  $f_{OUT} = f_{T}$

Figure 5. Phase Comparator, Internal Charge Pump, and four Characteristics

|         | FC | = HIGI | H or Ol | PEN  | FC = LOW |    |    |      |  |  |  |

|---------|----|--------|---------|------|----------|----|----|------|--|--|--|

|         | Do | φR     | φР      | fout | Do       | φR | φР | fout |  |  |  |

| fp < fr | Н  | L      | L       | fr   | L        | Н  | Н  | fp   |  |  |  |

| fp > fr | L  | Н      | Н       | fr   | Н        | L  | L  | fp   |  |  |  |

| fp = fr | Z  | L      | Н       | fr   | Z        | L  | Н  | fp   |  |  |  |

NOTES: Z = High impedance

When LE is HIGH or Open, BISW has the same characteristics as Do.

Legacy Applications Information

Figure 6. Detailed Phase Comparator Block Diagram

## LOCK DETECT

The Lock Detect (LD) output pin provides a LOW pulse when fr and fp are not equal in phase or frequency. The output is normally HIGH. LD is designed to be the logical NORing of the phase frequency detector's outputs UP and DOWN. See Figure 6. In typical applications the output signal drives external circuitry which provides a steady LOW signal when the loop is locked. See Figure 9.

## **OSCILLATOR INPUT**

For best operation, an external reference oscillator is recommended. The signal should be AC–coupled to the OSCin pin through a coupling capacitor. In this case, no connection to OSCout is required. The magnitude of the AC–coupled signal must be between 500 and 2200 mV peak–to–peak. To optimize the phase noise of the PLL when used in this mode, the input signal amplitude should be closer to the upper specification limit. This maximizes the slew rate of the signal as it switches against the internal voltage reference.

The device incorporates an on-chip reference oscillator/buffer so that an external parallel-resonant fundamental crystal can be connected between OSCin and OSCout. External capacitor C1 and C2 as shown in Figure 10 are required to set the proper crystal load capacitance and oscillator frequency. The values of the capacitors are dependent on the crystal chosen (up to a maximum of 30 pF each including parasitic and stray capacitance). However, using the on-chip reference oscillator greatly increases the synthesized phase noise.

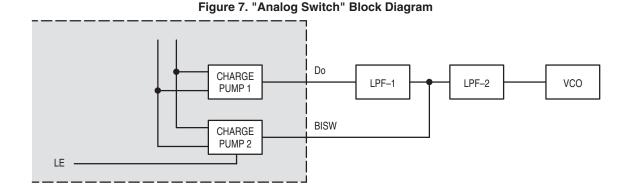

# **DUAL INTERNAL CHARGE PUMPS** ("ANALOG SWITCH")

Due to the pure Bipolar nature of the ML12210 design, the "analog switch" function is implemented with dual internal charge pumps. The loop filter time constant can be decreased by bypassing the first stage of the loop filter with the charge pump output BISW as shown in Figure 7 below. This enables the VCO to lock in a shorter amount of time.

When LE is HIGH or OPEN ("analog switch is ON"), the output of the second internal charge pump is connected to the BISW pin, and the Do output is ON. The charge pump 2 output on BISW is essentially equal to the charge pump 1 output on Do. When LE is LOW, BISW is in a high impedance state and Do output is active.

**ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 2.7 \text{ to } 5.5 \text{ V}; T_A = -40 \text{ to } +85^{\circ}\text{C}$ , unless otherwise noted.)

| Supply Current for V <sub>CC</sub> Supply Current for V <sub>P</sub> Operating Frequency f <sub>IN</sub> max f <sub>IN</sub> min  Operating Frequency (OSCin)  Input Sensitivity f <sub>IN</sub> OSCin  Input HIGH Voltage CLK, DATA, LE, FC | I <sub>CC</sub> I <sub>P</sub> F <sub>IN</sub> Fosc | -<br>-<br>-<br>-<br>2500<br>- | 8.8<br>10.2<br>0.7<br>0.8 | 13.0<br>16.0<br>1.1<br>1.3 | mA<br>mA | Note 1<br>Note 2<br>Note 3                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------|---------------------------|----------------------------|----------|------------------------------------------------------------|

| Operating Frequency f <sub>IN</sub> max f <sub>IN</sub> min  Operating Frequency (OSCin)  Input Sensitivity f <sub>IN</sub> OSCin  Input HIGH Voltage CLK, DATA, LE, FC                                                                      | F <sub>IN</sub>                                     | -<br>-<br>2500<br>-           | 0.7                       | 1.1                        | mA       |                                                            |

| Operating Frequency f <sub>IN</sub> max f <sub>IN</sub> min  Operating Frequency (OSCin)  Input Sensitivity f <sub>IN</sub> OSCin  Input HIGH Voltage CLK, DATA, LE, FC                                                                      | F <sub>IN</sub>                                     | 2500<br>–                     |                           |                            | mA       | Note 3                                                     |

| Input Sensitivity Input HIGH Voltage  flNmin  flN  oSCin  CLK, DATA, LE, FC                                                                                                                                                                  |                                                     | 2500<br>–                     | 0.8                       | 1.3                        |          |                                                            |

| Input Sensitivity Input HIGH Voltage  flNmin  flN  oSCin  CLK, DATA, LE, FC                                                                                                                                                                  |                                                     | _                             | _                         |                            |          | Note 4                                                     |

| Input Sensitivity f <sub>IN</sub> OSCin Input HIGH Voltage CLK, DATA, LE, FC                                                                                                                                                                 | Fosc                                                | _                             | _                         | _<br>500                   | MHz      | Note 5                                                     |

| OSCin Input HIGH Voltage CLK, DATA, LE, FC                                                                                                                                                                                                   |                                                     | I                             | 12                        | 20                         | MHz      | Crystal Mode                                               |

| OSCin Input HIGH Voltage CLK, DATA, LE, FC                                                                                                                                                                                                   |                                                     | _                             | _                         | 40                         | MHz      | External Reference Mode                                    |

| Input HIGH Voltage CLK, DATA, LE, FC                                                                                                                                                                                                         | VIN                                                 | 200                           | _                         | 1000                       | mVpp     |                                                            |

| •                                                                                                                                                                                                                                            | Vosc                                                | 500                           | -                         | 2200                       | mVpp     |                                                            |

|                                                                                                                                                                                                                                              | VIH                                                 | 0.7 V <sub>CC</sub>           | _                         | _                          | V        |                                                            |

| Input LOW Voltage CLK, DATA, LE, FC                                                                                                                                                                                                          | V <sub>IL</sub>                                     | -                             | _                         | 0.3 V <sub>CC</sub>        | V        | V <sub>CC</sub> = 5.5 V                                    |

| Input HIGH Current (DATA and CLK)                                                                                                                                                                                                            | lН                                                  | -                             | 1.0                       | 2.0                        | μΑ       | V <sub>CC</sub> = 5.5 V                                    |

| Input LOW Current (DATA and CLK)                                                                                                                                                                                                             | I <sub>IL</sub>                                     | -10                           | -5.0                      | -                          | μΑ       | V <sub>CC</sub> = 5.5 V                                    |

| Input Current (OSCin)                                                                                                                                                                                                                        | losc                                                | -                             | 130<br>–310               | -<br>-                     | μΑ       | OSCin = V <sub>CC</sub><br>OSCin = V <sub>CC</sub> - 2.2 V |

| Input HIGH Current (LE and FC)                                                                                                                                                                                                               | lіН                                                 | -                             | 1.0                       | 2.0                        | μΑ       |                                                            |

| Input LOW Current (LE and FC)                                                                                                                                                                                                                | I <sub>IL</sub>                                     | -75                           | -60                       | -                          | μΑ       |                                                            |

| Charge Pump Output Current                                                                                                                                                                                                                   | I <sub>Source</sub> 6                               | -2.6                          | -2.0                      | -1.4                       | mA       | $V_{Do} = V_p/2; V_p = 2.7 V$                              |

| Do and BISW                                                                                                                                                                                                                                  | I <sub>Sink</sub> 6                                 | +1.4                          | +2.0                      | +2.6                       |          | $V_{BISW} = V_p/2; V_p = 2.7 V$                            |

|                                                                                                                                                                                                                                              | I <sub>Hi</sub> –Z                                  | -15                           | -                         | +15                        | nA       | $0.5 < V_{DO} < V_p - 0.5$<br>$0.5 < V_{BISW} < V_p - 0.5$ |

| Output HIGH Voltage (LD, φR, φP, fOUT)                                                                                                                                                                                                       | VOH                                                 | 4.4                           | -                         | -                          | V        | V <sub>CC</sub> = 5.0 V                                    |

|                                                                                                                                                                                                                                              |                                                     | 2.4                           | _                         | _                          | V        | V <sub>CC</sub> = 3.0 V                                    |

| Output LOW Voltage (LD, φR, φP, fOUT)                                                                                                                                                                                                        | V <sub>OL</sub>                                     | -                             | _                         | 0.4                        | V        | V <sub>CC</sub> = 5.0 V                                    |

|                                                                                                                                                                                                                                              |                                                     | _                             | _                         | 0.4                        | V        | V <sub>CC</sub> = 3.0 V                                    |

| Output HIGH Current (LD, φR, φP, fOUT)                                                                                                                                                                                                       |                                                     |                               |                           |                            |          |                                                            |

| Output LOW Current (LD, φR, φP, fOUT)                                                                                                                                                                                                        | ІОН                                                 | -1.0                          | _                         | _                          | mA       |                                                            |

<sup>1.</sup>  $V_{CC} = 3.3 \text{ V}$ , all outputs open.

4.  $V_p = 6.0 \text{ V}$ , all outputs open.

Figure 8. Typical External Charge Pump Circuit

Figure 9. Typical Lock Detect Circuit

<sup>2.</sup> V<sub>CC</sub> = 5.5 V, all outputs open.

<sup>3.</sup>  $V_P = 3.3 V$ , all outputs open.

<sup>5.</sup> AC coupling, FIN measured with a 1000 pF capacitor.

<sup>6.</sup> Source current flows out of the pin and sink current flows into the pin.

Figure 10. Typical Applications Example

C1, C2: Dependent on Crystal Oscillator

BISW ODO OR EXTERNAL CHARGE PUMP R

Lansdale Semiconductor reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Lansdale does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. "Typical" parameters which may be provided in Lansdale data sheets and/or specifications can vary in different applications, and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts. Lansdale Semiconductor is a registered trademark of Lansdale Semiconductor, Inc.