# ML12040 Phase-Frequency Detector

Legacy Device: Motorola MC12040

The ML12040 is a phase–frequency detector intended for use in systems requiring zero phase and frequency difference at lock. In combination with a voltage controlled oscillator (such as the ML12149), it is useful in a broad range of phase–locked loop applications.

• Operating Frequency = 80 MHz Typical

• Operating Temperature Range  $T_A = 0^\circ$  to  $75^\circ$ C

#### **Pin Conversion Table**

| 14 Pin DIP  | 1 | 2 | 3 | 4 | 5 | 6 | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 |

|-------------|---|---|---|---|---|---|----|----|----|----|----|----|----|----|

| 20 Pin PLCC | 2 | 3 | 4 | 6 | 8 | 9 | 10 | 12 | 13 | 14 | 16 | 18 | 19 | 20 |

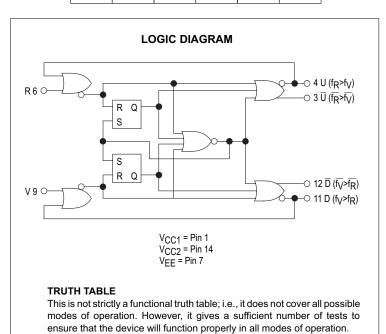

| Inp              | uts              | Outputs          |                  |                  |                  |  |  |  |  |  |

|------------------|------------------|------------------|------------------|------------------|------------------|--|--|--|--|--|

| R                | ٧                | U                | D                | Ū                | D                |  |  |  |  |  |

| 0<br>0           | 0<br>1           | X<br>X           | X<br>X           | X<br>X           | X<br>X           |  |  |  |  |  |

| 1                | 1<br>1           | X<br>X           | X<br>X           | X<br>X           | X<br>X           |  |  |  |  |  |

| 1<br>0<br>1<br>1 | 1<br>1<br>1<br>0 | 1<br>1<br>1<br>1 | 0<br>0<br>0<br>0 | 0<br>0<br>0<br>0 | 1<br>1<br>1      |  |  |  |  |  |

| 1<br>1<br>1      | 1<br>0<br>1<br>0 | 0<br>0<br>0<br>0 | 0<br>0<br>1<br>1 | 1<br>1<br>1<br>1 | 1<br>1<br>0<br>0 |  |  |  |  |  |

| 1<br>0<br>1      | 1<br>1<br>1      | 0<br>0<br>0      | 1<br>1<br>0      | 1<br>1<br>1      | 0<br>0<br>1      |  |  |  |  |  |

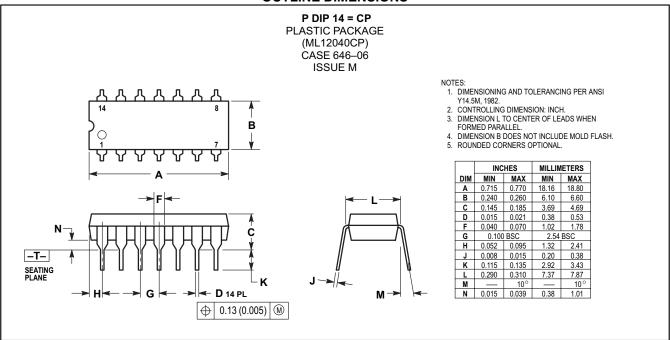

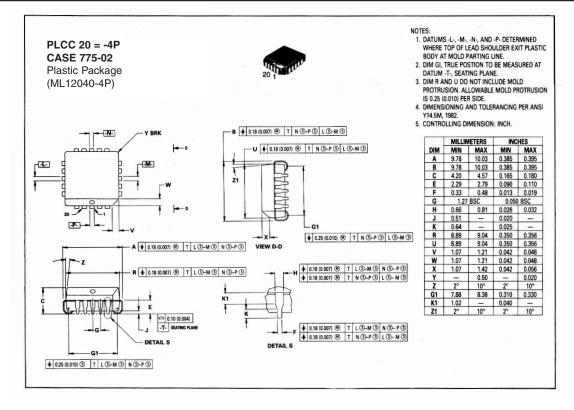

PLCC 20 = -4P PLASTIC PACKAGE CASE 775

#### **CROSS REFERENCE/ORDERING INFORMATION**

| PACKAGE             | MOTOROLA              | LANSDALE                |

|---------------------|-----------------------|-------------------------|

| P DIP 14<br>PLCC 20 | MC12040P<br>MC12040FN | ML12040CP<br>ML12040-4P |

| PLCC 20             | MC 12040FN            | WIL 12040-4P            |

**Note**: Lansdale lead free (**Pb**) product, as it becomes available, will be identified by a part number prefix change from **ML** to **MLE**.

# **ELECTRICAL CHARACTERISTICS**

The ML12040 has been designed to meet the DC specifications shown in the test table after thermal equilibrium has been established. Outputs are terminated through a 50  $\Omega$  resistor to 3.0 V for 5.0 V tests and through a 50  $\Omega$  resistor to -2.0 V for -5.2 V tests.

TEST VOLTAGE VALUES

(Volts)

$V_{IHAmin}$

$V_{ILAmax}$

٧EE

**NOTE**: For more information on using an ECL device in a 5.0 V system, refer to Application Note AN1406/D, "Designing with PECL (ECL at 5.0 V)"

|                    | TEST VOLTAGE VALUES |                    |                     |                     |                 |  |  |  |  |  |  |

|--------------------|---------------------|--------------------|---------------------|---------------------|-----------------|--|--|--|--|--|--|

|                    | (Volts)             |                    |                     |                     |                 |  |  |  |  |  |  |

| @ Test Temperature | V <sub>IHmax</sub>  | V <sub>ILmin</sub> | V <sub>IHAmin</sub> | V <sub>ILAmax</sub> | v <sub>EE</sub> |  |  |  |  |  |  |

| 0°C                | -0.840              | -1.870             | -1.145              | -1.490              | -5.2            |  |  |  |  |  |  |

| 25°C               | -0.810              | -1.850             | -1.105              | -1.475              | -5.2            |  |  |  |  |  |  |

| 75°C               | -0.720              | -1.830             | -1.045              | -1.450              | -5.2            |  |  |  |  |  |  |

Supply Voltage = -5.2V

| - upp.j                       | 90 0.21                     |                    |        |        |        |            |        |        |      | 020                |                                    |                     |                     | 0.2    |                           |

|-------------------------------|-----------------------------|--------------------|--------|--------|--------|------------|--------|--------|------|--------------------|------------------------------------|---------------------|---------------------|--------|---------------------------|

|                               |                             |                    |        |        |        | MC12040    |        |        |      | TEQT               | OW/                                |                     |                     |        |                           |

|                               |                             |                    | 0°C    |        | 25°C   |            | 75°C   |        |      | 1231               | TEST VOLTAGE APPLIED TO PINS BELOW |                     |                     |        |                           |

| Symbol                        | Characteristics             | Under<br>Test      | Min    | Max    | Min    | Max        | Min    | Max    | Unit | V <sub>IHmax</sub> | V <sub>ILmin</sub>                 | V <sub>IHAmin</sub> | V <sub>ILAmax</sub> | VEE    | (V <sub>CC</sub> )<br>Gnd |

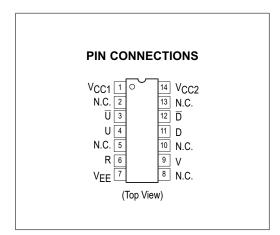

| ΙΕ                            | Power Supply Drain          | 7                  |        |        | -120   | -60        |        |        | mAdc |                    |                                    |                     |                     | 7      | 1,14                      |

| INH                           | Input Current               | 6<br>9             |        |        |        | 350<br>350 |        |        | μAdc | 6<br>9             |                                    |                     |                     | 7<br>7 | 1,14<br>1,14              |

| ∨ <sub>OH</sub> 1             | Logic "1"<br>Output Voltage | 3<br>4<br>11<br>12 | -1.000 | -0.840 | -0.960 | -0.810     | -0.900 | -0.720 | Vdc  |                    |                                    |                     |                     | 7      | 1,14                      |

| V <sub>OL</sub> 1             | Logic "0"<br>Output Voltage | 3<br>4<br>11<br>12 | -1.870 | -1.635 | -1.850 | -1.620     | -1.830 | -1.595 | Vdc  |                    |                                    |                     |                     | 7      | 1,14                      |

| V <sub>OHA</sub> <sup>2</sup> | Logic "1"<br>Input Voltage  | 3<br>4<br>11<br>12 | -1.020 |        | -0.980 |            | -0.920 |        | Vdc  |                    |                                    | 6.9                 |                     | 7      | 1,14                      |

| V <sub>OLA</sub> <sup>2</sup> | Logic "0"<br>Input Voltage  | 3<br>4<br>11<br>12 |        | -1.615 |        | -1.600     |        | -1.575 | Vdc  |                    |                                    | 9<br>6<br>9<br>6    | 6<br>9<br>6<br>9    | 7      | 1,14                      |

|                               |                             |                    |       |       |       |            |       |       | 0°C                                | +4.160             | +3.130             | +3.855              | +3.510              | +5.0            | ĺ                         |

|-------------------------------|-----------------------------|--------------------|-------|-------|-------|------------|-------|-------|------------------------------------|--------------------|--------------------|---------------------|---------------------|-----------------|---------------------------|

|                               |                             |                    |       |       |       |            |       |       | 25°C                               | +4.190             | +3.150             | +3.895              | +3.525              | +5.0            |                           |

| Supply Vo                     | Itage = +5.0V               |                    |       |       |       |            |       |       | 75°C                               | +4.280             | +3.170             | +3.955              | +3.550              | +5.0            |                           |

|                               |                             |                    |       |       |       | MC12040    |       |       |                                    | 7507               |                    |                     | o DINO DEL          | 0144            |                           |

|                               |                             | Pin<br>Under       | 0     | °C    | 25    | °C         | 75°C  |       | TEST VOLTAGE APPLIED TO PINS BELOW |                    |                    |                     |                     | (Vas)           |                           |

| Symbol                        | Characteristics             | Test               | Min   | Max   | Min   | Max        | Min   | Max   | Unit                               | V <sub>IHmax</sub> | V <sub>ILmin</sub> | V <sub>IHAmin</sub> | V <sub>ILAmax</sub> | ν <sub>EE</sub> | (V <sub>CC</sub> )<br>Gnd |

| ΙΕ                            | Power Supply Drain          | 7                  |       |       | -115  | -60        |       |       | mAdc                               |                    |                    |                     |                     | 1,14            | 7                         |

| INH                           | Input Current               | 6<br>9             |       |       |       | 350<br>350 |       |       | μAdc                               | 6<br>9             |                    |                     |                     | 1,14<br>1,14    | 7<br>7                    |

| ∨ <sub>OH</sub> 1             | Logic "1"<br>Output Voltage | 3<br>4<br>11<br>12 | 4.000 | 4.160 | 4.040 | 4.190      | 4.100 | 4.280 | Vdc                                |                    |                    |                     |                     | 1,14            | 7                         |

| V <sub>OL</sub> 1             | Logic "0"<br>Output Voltage | 3<br>4<br>11<br>12 | 3.190 | 3.430 | 3.210 | 3.440      | 3.230 | 3.470 | Vdc                                |                    |                    |                     |                     | 1,14            | 7                         |

| V <sub>OHA</sub> <sup>2</sup> | Logic "1"<br>Input Voltage  | 3<br>4<br>11<br>12 | 3.980 |       | 4.020 |            | 4.080 |       | Vdc                                |                    |                    | 6.9                 |                     | 1,14            | 7                         |

| V <sub>OLA</sub> <sup>2</sup> | Logic "0"<br>Input Voltage  | 3<br>4<br>11<br>12 |       | 3.450 |       | 3.460      |       | 3.490 | Vdc                                |                    |                    | 9<br>6<br>9<br>6    | 6<br>9<br>6<br>9    | 1,14            | 7                         |

@ Test Temperature

$v_{IHmax}$

$V_{ILmin}$

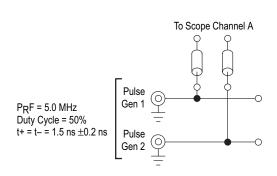

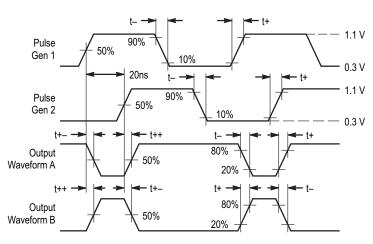

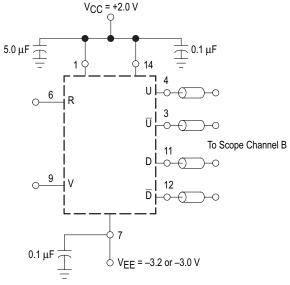

Figure 1. AC Tests

## NOTES:

- 1 All input and output cables to the scope are equal lengths of 50  $\Omega$  coaxial cable.

- 2 Unused input and outputs are connected to a 50  $\Omega$  resistor to ground.

- 3 The device under test must be preconditioned before performing the AC tests. Preconditioning may be accomplished by applying pulse generator 1 for a minimum of two pulses prior to pulse generator 2. The device must be preconditioned again when inputs to Pins 6 and 9 are interchanged. The same technique applies.

|                                                                          |                   |                                                          |                    |                                                      | ML12040                                              |                                                      |      | TEST V                     | OLTAGE:               | S/WAVEF                              | ORMS                      |

|--------------------------------------------------------------------------|-------------------|----------------------------------------------------------|--------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------|----------------------------|-----------------------|--------------------------------------|---------------------------|

|                                                                          |                   |                                                          |                    | 0°C                                                  | 25°C                                                 | 85°C                                                 |      | APPLIED TO PINS LISTED     |                       |                                      |                           |

| Symbol                                                                   | Characteristic    | Pin<br>Under<br>Test                                     | Output<br>Waveform | Max                                                  | Max                                                  | Max                                                  | Unit | Pulse<br>Gen 1             | Pulse<br>Gen 2        | V <sub>EE</sub><br>-3.0 or<br>-3.2 V | V <sub>C</sub> C<br>2.0 V |

| t6+4+<br>t6+12+<br>t6+3-<br>t6+11-<br>t9+11+<br>t9+3+<br>t9+12-<br>t9+4- | Propagation Delay | 6,4<br>6,12<br>6,3<br>6,11<br>9,11<br>9,3<br>9,12<br>9,4 | B A A B B A A B    | 4.6<br>6.0<br>4.5<br>6.4<br>4.6<br>6.0<br>4.5<br>6.4 | 4.6<br>6.0<br>4.5<br>6.4<br>4.6<br>6.0<br>4.5<br>6.4 | 5.0<br>6.6<br>4.9<br>7.0<br>5.0<br>6.6<br>4.9<br>7.0 | ns   | 6<br>9<br>6<br>9<br>6<br>9 | 9<br>6<br>9<br>6<br>9 | 7                                    | 1,14                      |

| t3+<br>t4+<br>t <sub>11+</sub><br>t <sub>14+</sub>                       | Output Rise Time  | 3<br>4<br>11<br>14                                       | A<br>B<br>B<br>A   | 3.4                                                  | 3.4                                                  | 3.8                                                  | ns   | 6<br>6<br>9<br>9           | 9<br>9<br>6<br>6      | 7                                    | 1,14                      |

| t3_<br>t4_<br>t <sub>11</sub> _<br>t <sub>14</sub> _                     | Output Fall Time  | 3<br>4<br>11<br>14                                       | A<br>B<br>B<br>A   | 3.4                                                  | 3.4                                                  | 3.8                                                  | ns   | 6<br>6<br>9<br>9           | 9<br>9<br>6<br>6      | 7                                    | 1,14                      |

# Legacy Applications Information

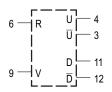

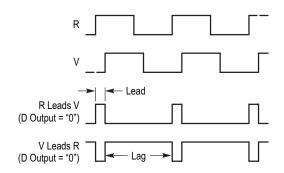

The ML12040 is a logic network designed for use as a phase comparator for MECL–compatible input signals. It determines the "lead" or "lag" phase relationship and the time difference between the leading edges of the waveforms. Since these edges occur only once per cycle, the detector has a range of  $\pm 2\pi$  radians.

Operation of the device may be illustrated by assuming two waveforms, R and V (Figure 2), of the same frequency but differing in phase. If the logic had established by past history that R was leading V, the U output of the detector (pin 4) would produce a positive pulse width equal to the phase difference and the D output (Pin 11) would simply remain low.

On the other hand, it is also possible that V was leading R (Figure 2), giving rise to a positive pulse on the D output and a constant low level on the U output pin. Both outputs for the sample condition are valid since the determination of lead or lag is dependent on past edge crossing and initial conditions at start—up. A stable phase—locked loop will result from either condition.

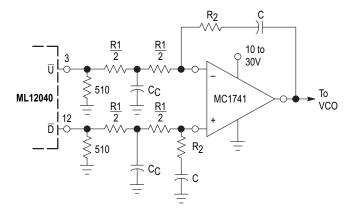

Phase error information is contained in the output duty cycle that is, the ratio of the output pulse width to total period. By integrating or low–pass filtering the outputs of the detector and shifting the level to accommodate ECL swings, usable analog information for the voltage controlled oscillator can be developed. A circuit useful for this function is shown in Figure 3.

Figure 2. Timing Diagram

Proper level shifting is accomplished by differentially driving the operational amplifier from the normally high outputs of the phase detector (U and D). Using this technique the quiescent differential voltage to the operational amplifier is zero (assuming matched "1" levels from the phase detector). The U and D outputs are then used to pass along phase information to the operational amplifier. Phase error summing is accomplished through resistors R1 connected to the inputs of the operational amplifier. Some R–C filtering imbedded within the input network (Figure 3) may be very beneficial since the very narrow correctional pulses of the ML12040 would not normally be integrated by the amplifier. Phase detector gain for this configuration is approximately 0.16 volts/radian.

System phase error stems from input offset voltage in the operational amplifier, mismatching of nominally equal resistors, and mismatching of phase detector "high" states between the outputs used for threshold setting and phase measuring. All these effects are reflected in the gain constant. For example, a 16 mV offset voltage in the amplifier would cause an error of 0.016/0.16 = 0.1 radian or 5.7 degrees of error. Phase error can be trimmed to zero initially by trimming either input offset or one of the threshold resistors (R1 in Figure 3). Phase error over temperature depends on how much the offending parameters drift.

Figure 3. Typical Filter and Summing Network

## **OUTLINE DIMENSIONS**

Lansdale Semiconductor reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Lansdale does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. "Typical" parameters which may be provided in Lansdale data sheets and/or specifications can vary in different applications, and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts. Lansdale Semiconductor is a registered trademark of Lansdale Semiconductor, Inc.