# SYNCHRONOUS SEPARATOR WITH AFC

#### **■ GENERAL DESCRIPTION**

The **NJM2257** excutes Horizontal and Vertical synchronous signal separation, and odd / even field signal detection, from composit video signals.

Built-in 1 / 2 fH Killer Function circuit can make stabilization of the Horizontal signal oscillation output during the vertical period.

### ■ PACKAGE OUTLINE

NJM2257D

NJM2257M

#### **■ FEATURES**

- Operating Voltage (+4.5 to +5.3V)

- Internal AFC circuit (Horizontal sync. signal.)

- Internal 1 / 2 fH Killer Function

- AFC output Pulse Delay time is Adjustable

- Vertical synchronous pulse width is Adjustable

- Internal Field Discrlainat Function

- Package Outline DIP16, DMP16

- Bipolar Technology

#### **■ APPLICATION**

• VTR, TV, AV components etc.

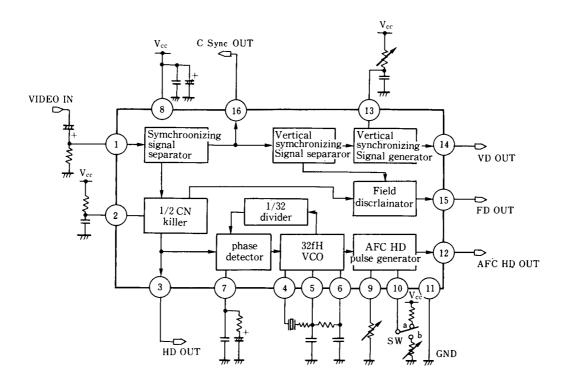

#### **■ BLOCK DIAGRAM**

# ■ ABSOLUTE MAXIMUM RATINGS

$(T_a = 25^{\circ}C)$

| PARAMETER                   | SYMBOL           | RATINGS                    | UNIT     |

|-----------------------------|------------------|----------------------------|----------|

| Supply Voltage              | V <sup>+</sup>   | +7                         | V        |

| Power Dissipation           | P <sub>D</sub>   | (DIP16) 500<br>(DMP16) 350 | mW<br>mW |

| Operating Temperature Range | T <sub>opr</sub> | -20 to +75                 | °C       |

| Storage Temperature Range   | T <sub>stg</sub> | - 40 to +125               | °C       |

# **■ ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 5V, T_a = 25^{\circ}C)$

| DADAMETED                     |             | SYMBOL            | TEST CONDITION | MIN.    |       | MAX.    | unit |  |

|-------------------------------|-------------|-------------------|----------------|---------|-------|---------|------|--|

| PARAMETER                     |             |                   | TEST CONDITION | IVIIIN. | TYP.  |         | _    |  |

| Quiessent Current             |             | lα                |                | -       | 23.0  | 30.0    | mA   |  |

| AFC Free Run Frequency        |             | f <sub>OH</sub>   |                | 15.54   | 15.74 | 15.94   | KHz  |  |

| AFC HD pulse width            | none adjust | T <sub>AHW1</sub> | SW=a           | 3.5     | 4.0   | 4.5     | μS   |  |

| Al OTID paise wattr           | adjust      | T <sub>AHW2</sub> | SW=b           | 2.5     | 4.0   | 5.5     |      |  |

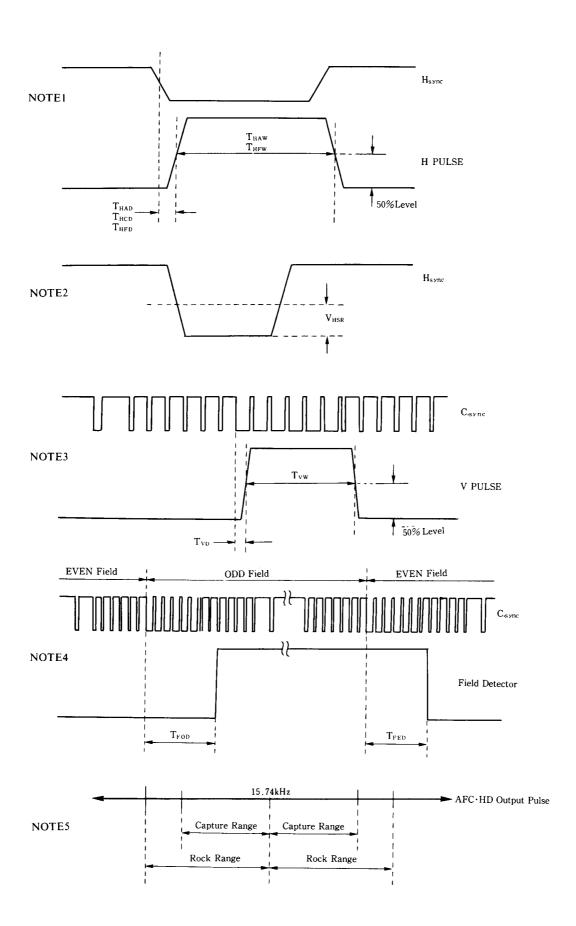

| AFC HD Delet Time             |             | T <sub>AHD</sub>  |                | -1.0    | 0.5   | 2.0     | μS   |  |

| AFC Lock Range                |             | $\Delta f_{HL}$   |                | 500     | 700   | -       | Hz   |  |

| AFC Cap Charange              |             | $\Delta f_{HP}$   |                | 400     | 600   | -       | Hz   |  |

| AFC Output Voltage            | Н           | V <sub>HAH</sub>  |                | 4.0     | 4.2   | -       | V    |  |

| AFC Output voltage            | L           | V <sub>HAL</sub>  |                | -       | 0     | 0.1     | ]    |  |

| Sync Sepa Sync. Separation L  | evel        | V <sub>HSR</sub>  |                | -       | 0.16  | 0.18    | V    |  |

| Sync Sepa Delay Time          |             | T <sub>HCD</sub>  |                | 0.05    | 0.20  | 0.35    | μS   |  |

| Sync Sepa Output Voltage      | Н           | V <sub>HCH</sub>  |                | 4.0     | 4.2   | -       | V    |  |

| Syric Sepa Output Voltage     | L           | V <sub>HCL</sub>  |                | -       | 0     | 0.1     |      |  |

| HD Output Palth Width         |             | T <sub>HPW</sub>  |                | 4.0     | 5.5   | 7.0     | μS   |  |

| HD Output Delay Time          |             | T <sub>HPD</sub>  |                | 0.35    | 0.6   | 0.8     | μS   |  |

| LID Outrout Voltage           | Н           | $V_{HfH}$         |                | 4.0     | 4.2   | -       | \/   |  |

| HD Output Voltage             | L           | V <sub>HfL</sub>  |                | -       | 0     | 0.1     | - V  |  |

| V Sync Palth Width            |             | V <sub>vw</sub>   |                | 170     | 190   | 210     | μS   |  |

| V Sync Delay Time             |             | T <sub>VD</sub>   |                | 7.0     | 10.0  | 13.0    | μS   |  |

| V Sync Output Voltage         | Н           | T <sub>VH</sub>   |                | 4.0     | 4.2   | -       | V    |  |

|                               | L           | $V_{VL}$          |                | -       | 0     | 0.1     |      |  |

| Field Distinction Delay Times | odd         | T <sub>FOD</sub>  |                | 246     | 256   | 266     |      |  |

| Field Distinction Delay Time  | even        | T <sub>FED</sub>  |                | 216     | 226   | 236     | μS   |  |

| Fideld Distinction Output     | odd         | V <sub>FOR</sub>  |                | 4.0     | 4.2   | -       |      |  |

| Voltage                       | even        | V <sub>FER</sub>  |                | -       | 0     | 0 0.1 V |      |  |

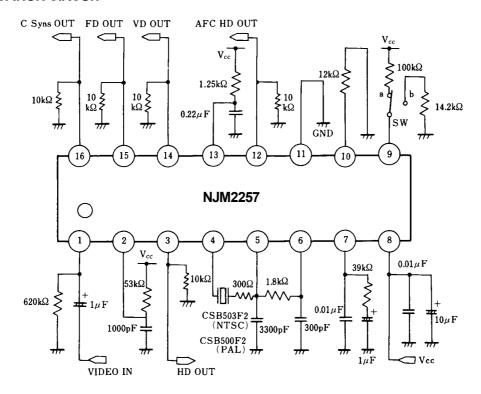

#### **■ APPLICATION CIRCUIT**

#### **■ APPLICATION NOTES**

It shows the characteristics by changing of the following resistor.

• The resistance between 9 Pin and GND

High resistance — AFC HD pulse is wide

Low resistance — AFC HD pulse is narrow

• The resistor between 9 Pin and V<sup>+</sup>

At the resistor is  $100\Omega$ . AFC HD Delay adjustment is off, and AFC HD output width is  $4\mu s$  (typ.)

- The resistor between 9 Pin and GND is fundamentally 14.2kΩ, because the purpose of this resistor is pulse width adjusts 4μs.

- The resistor between 10 Pin and GND

High resistance — AFC HD Delay time gains

Low resistance — AFC HD Delay time loses

• The resistor between 13 Pin and GND

High resistance — Vsync pulse is wide Low resistance — Vsync pulse is narrow

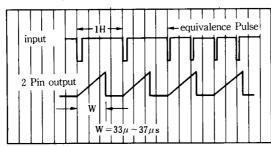

• The resistor joind 2 Pin

Please adjust the wide of following W is from 33  $\mu$ s to 37  $\mu$ s (W = - (C·R)In0.5)

Fig 1 I / O PULSE

# **■ TERMINAL EXPLANATION**

| PIN NO. | PIN NAME     | FUNCTION                                                                             | INSIDE EQUIVALENT CIRCUIT |

|---------|--------------|--------------------------------------------------------------------------------------|---------------------------|

| 1       | VIDEO-IN     | Composit Video Signal Input                                                          |                           |

| 2       | MM-HT        | HD & FD puse are Controlled by setling mono multi                                    | 2                         |

| 3       | HD-OUT       | 1 / 2 f <sub>H</sub> Killer D Output                                                 | 3<br>15k                  |

| 4       | VCO-OUT      | VCO Output is to be given to<br>Ceramic Oscillator                                   | 4                         |

| 5       | VCO-FILTER 1 | Decide the Volume to be transfered shall by decided of Ceramic Oscillator. (90°late) | 5                         |

# **■ TERMINAL EXPLANATION**

| PIN NO. | PIN NAME       | FUNCTION                                                                                                                                                                                   | INSIDE EQUIVALENT CIRCUIT |

|---------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 6       | VCO-FILTER 2   | Decide the Volume to be transfered shall by decided of Cramic Oscillator. (90°late)                                                                                                        | 3.3k                      |

| 7       | L.P.F          | L. P. F. of AFC                                                                                                                                                                            | 7                         |

| 8       | V <sup>+</sup> | Supply Voltage                                                                                                                                                                             |                           |

| 9       | VR-1           | AFC-HD Output Can be adjusted by putting resistor between 9 to GND (9 to V <sub>CC</sub> no adjustment). The pulse width cam be adjusted by making changeable of resister (Adjusting mode) | 9                         |

| 10      | VR-2           | AFC-HD Output delay adjustment by putting 10 pin resister changeable at 9 pin ajustment mode.                                                                                              | 12. 6k                    |

| 11      | GND            | Ground                                                                                                                                                                                     |                           |

# **■ TERMINAL EXPLANATION**

| PIN NO. | PIN NAME              | FUNCTION                                                                  | INSIDE EQUIVALENT CIRCUIT |

|---------|-----------------------|---------------------------------------------------------------------------|---------------------------|

| 12      | AFC, HD-OUT           | AFC·HD Output                                                             | 12)                       |

| 13      | MM-VT                 | Pulse Width of Vsync-OUT is adjusted by setting mono multi time constant. | 13                        |

| 14      | Vsync-OUT             | Vertical Synchronous Signal<br>Output.                                    | 20k                       |

| 15      | FD-OUT discrimination | Field Distiniction Signal Output.                                         | 15)<br>20k                |

| 16      | Csyne-OUT             | Synchronous Separation Output                                             | 15k                       |

# **NJM2257**

# **■ PIN FUNCTION**

| PIN NO. | FUNCTION BLOCK                                             | OPERATIONAL DESCRIPTION                                                                                                                                  | NOTE                                                                                   |  |  |

|---------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|

| 1)Pin   | Signal Input                                               | Video Signal input                                                                                                                                       | Sync tip clump                                                                         |  |  |

| 2Pin    | HD pulse control                                           | HD pulse and FD pulse control by time constant of CR                                                                                                     |                                                                                        |  |  |

| 3Pin    | HD pulse output                                            | 1 / 2 f <sub>H</sub> killer HD pulse output                                                                                                              | In a period of vertical synchronizing, a f <sub>H</sub> is converted to f <sub>H</sub> |  |  |

| 4)Pin   |                                                            | Oscillation of 503KHz by a ceramic                                                                                                                       |                                                                                        |  |  |

| ⑤Pin    | AFC Oscillation                                            | oscillator, and divided by 32 to get down                                                                                                                |                                                                                        |  |  |

| 6Pin    |                                                            | to 15.74KHz                                                                                                                                              |                                                                                        |  |  |

| 7)Pin   | AFC control                                                | Leg Lead filter for phase detection                                                                                                                      |                                                                                        |  |  |

| 8Pin    | V <sub>CC</sub>                                            | V <sub>CC</sub>                                                                                                                                          |                                                                                        |  |  |

| 9Pin    | AFC HD output Switch<br>(AFC HD pulse width<br>adjustment) | The case that R is connected between 9pin and V <sub>CC</sub> Fixed output The case that R is connected between 9pin and GNDAdjustable AFC HD Delay Mode | High Resistance → Wide pulse width Low Resistance → Narrow pulse width                 |  |  |

| 10 Pin  | AFC HD Delay adjustment                                    | The case that R is connected between 9pin and GND···Adjustable AFC HD Delay output                                                                       | High Resistance → AFC HD Delay time gains Low Resistance → AFC HD Delay time loses     |  |  |

| 11) Pin | GND                                                        | GND                                                                                                                                                      |                                                                                        |  |  |

| 12 Pin  | AFC HD output                                              | AFC HD pulse output                                                                                                                                      | Positive polarity                                                                      |  |  |

| 13) Pin | VD pulse width adujstment                                  | VD pulse width control by time constant of CR                                                                                                            |                                                                                        |  |  |

| 14) Pin | VD output                                                  | Vertical synchronizing signal output                                                                                                                     | Positive polarity                                                                      |  |  |

| 15) Pin | FD output                                                  | Field discriminating signal output                                                                                                                       | odd field → High Output<br>even field → Low Output                                     |  |  |

| 16 Pin  | C Sync. output                                             | Composite Sync Signal output                                                                                                                             | Positive polarity                                                                      |  |  |

[CAUTION]

The specifications on this databook are only given for information, without any guarantee as regards either mistakes or ornissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.