## Flash

# F25L16QA (2S)

## 16 Mbit Serial Flash Memory with Dual and Quad

## FEATURES

- Single supply voltage 2.7~3.6V

- Standard, Dual and Quad SPI

- Speed

- Read max frequency: 50MHz

- Fast Read max frequency: 50MHz / 86MHz / 100MHz

- Fast Read Dual/Quad max frequency: 50MHz / 86MHz / 100MHz

- (100MHz / 172MHz / 200MHz equivalent Dual SPI; 200MHz / 344MHz / 400MHz equivalent Quad SPI)

- Low power consumption

- Active current: 25 mA (max.)

- Standby current: 25 µ A (max.)

- Deep Power Down current: 10 µ A (max.)

- Reliability

- 100,000 typical program/erase cycles

- 20 years Data Retention

- Program

- Page programming time: 1.5 ms (typical)

- Erase

- Chip Erase time 10 sec (typical)

- 64K bytes Block Erase time 1 sec (typical)

- 32K bytes Block Erase time 500 ms (typical)

- 4K bytes Sector Erase time 120 ms (typical)

- Page Programming

256 byte per programmable page

- Lockable 512 bytes OTP security sector

- SPI Serial Interface

SPI Compatible: Mode 0 and Mode 3

- End of program or erase detection

- Write Protect ( WP )

- Hold Pin (HOLD)

- All Pb-free products are RoHS-Compliant

| Product ID         | Speed  | Packa             | ge      | Comments |

|--------------------|--------|-------------------|---------|----------|

| F25L16QA –50PG2S   | 50MHz  |                   |         |          |

| F25L16QA –86PG2S   | 86MHz  | 8-lead<br>SOIC    | 150 mil | Pb-free  |

| F25L16QA-100PG2S   | 100MHz |                   |         |          |

| F25L16QA50PAG2S    | 50MHz  |                   |         |          |

| F25L16QA86PAG2S    | 86MHz  | 8-lead<br>SOIC    | 200 mil | Pb-free  |

| F25L16QA -100PAG2S | 100MHz |                   |         |          |

| F25L16QA –50PHG2S  | 50MHz  |                   |         |          |

| F25L16QA86PHG2S    | 86MHz  | 16-lead<br>SOIC   | 300 mil | Pb-free  |

| F25L16QA-100PHG2S  | 100MHz |                   |         |          |

| F25L16QA50DG2S     | 50MHz  |                   |         |          |

| F25L16QA86DG2S     | 86MHz  | 8-pin<br>PDIP     | 300 mil | Pb-free  |

| F25L16QA-100DG2S   | 100MHz |                   |         |          |

| F25L16QA -50HG2S   | 50MHz  |                   |         |          |

| F25L16QA86HG2S     | 86MHz  | 8-contact<br>WSON | 6x5 mm  | Pb-free  |

| F25L16QA-100HG2S   | 100MHz |                   |         |          |

## ORDERING INFORMATION

## ■ GENERAL DESCRIPTION

The F25L16QA is a 16Megabit, 3V only CMOS Serial Flash memory device. The device supports the standard Serial Peripheral Interface (SPI), and a Dual/Quad SPI. ESMT's memory devices reliably store memory data even after 100,000 programming and erase cycles.

The memory array can be organized into 8,192 programmable pages of 256 byte each. 1 to 256 byte can be programmed at a time with the Page Program instruction.

The device features sector erase architecture. The memory array

is divided into 512 uniform sectors with 4K byte each; 64 uniform blocks with 32K byte each; 32 uniform blocks with 64K byte each. Sectors can be erased individually without affecting the data in other sectors. Blocks can be erased individually without affecting the data in other blocks. Whole chip erase capabilities provide the flexibility to revise the data in the device. The device has Sector, Block or Chip Erase but no page erase.

The sector protect/unprotect feature disables both program and erase operations in any combination of the sectors of the memory.

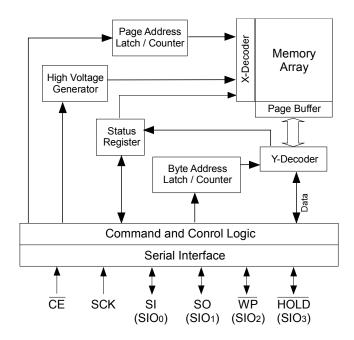

## FUNCTIONAL BLOCK DIAGRAM

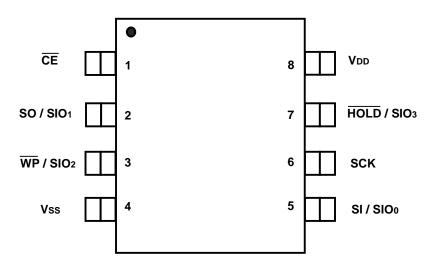

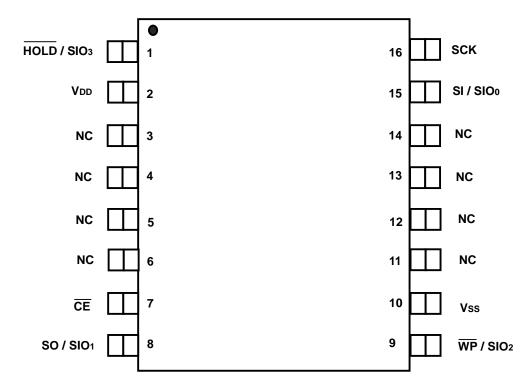

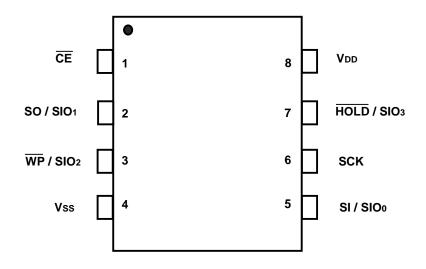

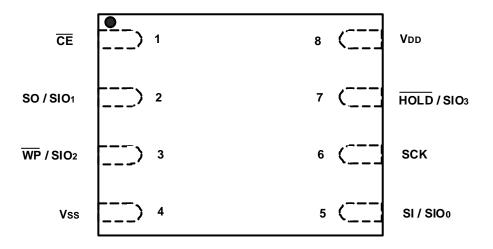

## PIN CONFIGURATIONS

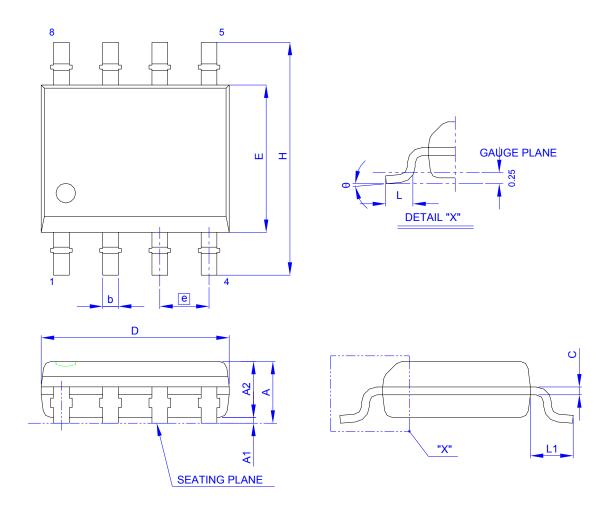

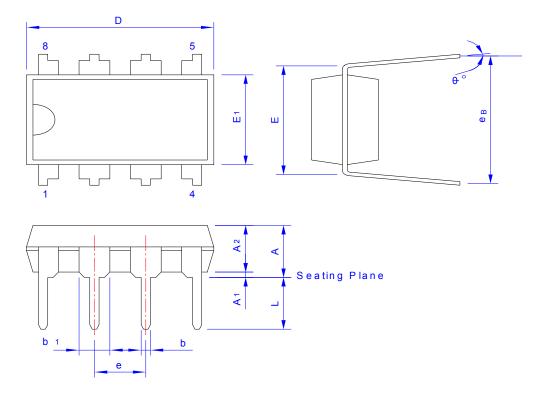

## 8-Lead SOIC

(SOIC 8L, 150mil Body, 1.27mm Pin Pitch) (SOIC 8L, 208mil Body, 1.27mm Pin Pitch)

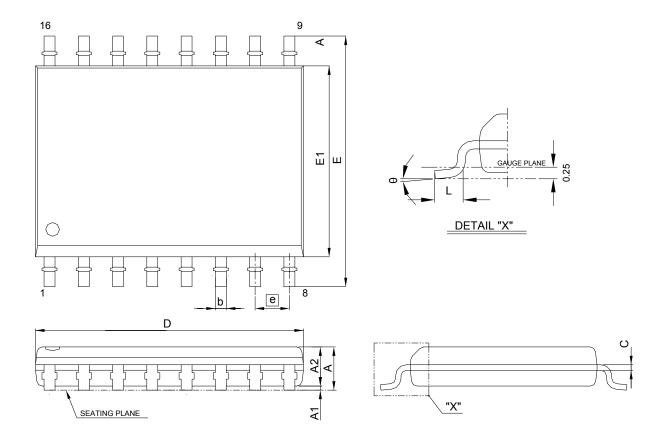

## 16-Lead SOIC

(SOIC 16L, 300mil Body, 1.27mm Pin Pitch)

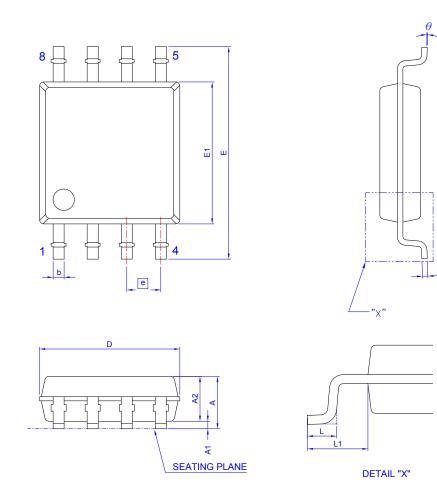

## 8-Pin PDIP

(PDIP 8P, 300mil Body, 2.54mm Pin Pitch)

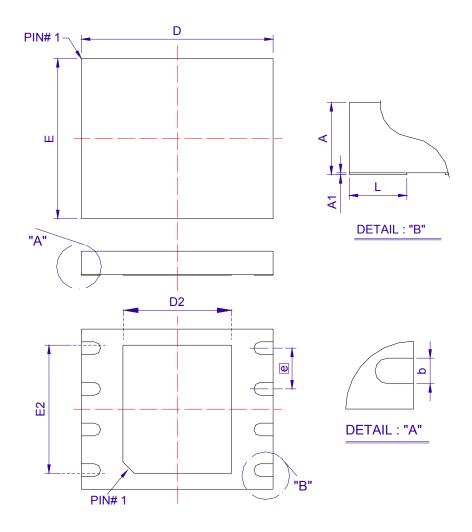

## 8- Contact WSON

(WSON 8C, 6mmX5mm Body, 1.27mm Contact Pitch)

## PIN DESCRIPTION

| Symbol      | Pin Name                                           | Functions                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK         | Serial Clock                                       | To provide the timing for serial input and output operations                                                                                                                                                                                                                                                                                    |

| SI / SIO0   | Serial Data Input /<br>Serial Data Input Output 0  | To transfer commands, addresses or data serially into the device. Data is latched on the rising edge of SCK (for Standard read mode). / Bidirectional IO pin to transfer commands, addresses or data serially into the device on the rising edge of SCK and read data or status from the device on the falling edge of SCK(for Dual/Quad mode). |

| SO / SIO1   | Serial Data Output /<br>Serial Data Input Output 1 | To transfer data serially out of the device. Data is shifted out on the falling edge<br>of SCK (for Standard read mode). / Bidirectional IO pin to transfer commands,<br>addresses or data serially into the device on the rising edge of SCK and read<br>data or status from the device on the falling edge of SCK (for Dual/Quad<br>mode).    |

| CE          | Chip Enable                                        | To activate the device when $\overline{CE}$ is low.                                                                                                                                                                                                                                                                                             |

| WP / SIO2   | Write Protect /<br>Serial Data Input Output 2      | The Write Protect ( $\overline{\text{WP}}$ ) pin is used to enable/disable BPL bit in the status register. / Bidirectional IO pin to transfer commands, addresses or data serially into the device on the rising edge of SCK and read data or status from the device on the falling edge of SCK (for Quad mode).                                |

| HOLD / SIO3 | Hold /<br>Serial Data Input Output 3               | To temporality stop serial communication with SPI flash memory without resetting the device. / Bidirectional IO pin to transfer commands, addresses or data serially into the device on the rising edge of SCK and read data or status from the device on the falling edge of SCK (for Quad mode).                                              |

| Vdd         | Power Supply                                       | To provide power.                                                                                                                                                                                                                                                                                                                               |

| Vss         | Ground                                             |                                                                                                                                                                                                                                                                                                                                                 |

## SECTOR STRUCTURE

ESMT

| 64KB  | 32KB  | •      | Sector Size |                   |     | Blo | ck Add   | ress |     |  |  |  |

|-------|-------|--------|-------------|-------------------|-----|-----|----------|------|-----|--|--|--|

| Block | Block | Sector | (Kbytes)    | Address range     | A20 | A19 | A18      | A17  | A16 |  |  |  |

|       |       | 511    | 4KB         | 1FF000H – 1FFFFFH |     |     |          |      |     |  |  |  |

|       | 63    | :      | :           | :                 |     |     |          |      |     |  |  |  |

|       |       | 504    | 4KB         | 1F8000H – 1F8FFFH |     |     |          |      |     |  |  |  |

| 31    |       | 503    | 4KB         | 1F7000H – 1F7FFFH | - 1 | 1   | 1        | 1    | 1   |  |  |  |

|       | 62    | :      | :           | :                 |     |     |          |      |     |  |  |  |

|       |       | 496    | 4KB         | 1F0000H – 1F0FFFH |     |     |          |      |     |  |  |  |

|       |       | 495    | 4KB         | 1EF000H – 1EFFFFH |     |     |          |      |     |  |  |  |

|       | 61    | :      | :           | :                 |     |     |          |      |     |  |  |  |

| 30    |       | 488    | 4KB         | 1E8000H – 1E8FFFH | 1   | 1   | 1        | 4    | 0   |  |  |  |

| 30    |       | 487    | 4KB         | 1E7000H – 1E7FFFH |     | •   | <b>'</b> | 1    | U   |  |  |  |

|       | 60    | :      | :           | :                 |     |     |          |      |     |  |  |  |

|       |       | 480    | 4KB         | 1E0000H – 1E0FFFH |     |     |          |      |     |  |  |  |

|       |       | 479    | 4KB         | 1DF000H – 1DFFFFH |     |     |          |      |     |  |  |  |

|       | 59    | :      | :           | :                 |     |     |          |      |     |  |  |  |

| 29    |       | 472    | 4KB         | 1D8000H – 1D8FFFH | 1   | 1   | 1        | 0    | 1   |  |  |  |

| 29    |       | 471    | 4KB         | 1D7000H – 1D7FFFH |     | •   | <b>'</b> | U    |     |  |  |  |

|       | 58    | :      | :           | :                 |     |     |          |      |     |  |  |  |

|       |       | 464    | 4KB         | 1D0000H – 1D0FFFH |     |     |          |      |     |  |  |  |

|       |       | 463    | 4KB         | 1CF000H – 1CFFFFH | -   |     |          |      |     |  |  |  |

|       | 57    | :      | :           | :                 |     |     |          |      |     |  |  |  |

| 28    |       | 456    | 4KB         | 1C8000H – 1C8FFFH | 1   | 1   | 1        | 0    | 0   |  |  |  |

| 20    |       | 455    | 4KB         | 1C7000H – 1C7FFFH | 1   |     |          |      | U   |  |  |  |

|       | 56    | :      | :           | :                 |     |     |          |      |     |  |  |  |

|       |       | 448    | 4KB         | 1C0000H – 1C0FFFH |     |     |          |      |     |  |  |  |

|       |       | 447    | 4KB         | 1BF000H – 1BFFFFH |     |     |          |      |     |  |  |  |

|       | 55    | :      | :           | :                 |     |     |          |      |     |  |  |  |

| 27    |       | 440    | 4KB         | 1B8000H – 1B8FFFH | 1   | 1   | 0        | 1    | 1   |  |  |  |

| 21    |       | 439    | 4KB         | 1B7000H – 1B7FFFH |     |     |          |      |     |  |  |  |

|       | 54    | :      | :           | :                 | 1   |     |          |      |     |  |  |  |

|       |       | 432    | 4KB         | 1B0000H – 1B0FFFH |     |     |          |      |     |  |  |  |

|       |       | 431    | 4KB         | 1AF000H – 1AFFFFH |     |     |          |      |     |  |  |  |

|       | 53    | :      | :           | :                 |     |     |          |      |     |  |  |  |

| 26    |       | 424    | 4KB         | 1A8000H – 1A8FFFH | 1   | 1   | 0        | 1    | 0   |  |  |  |

| 20    |       | 423    | 4KB         | 1A7000H – 1A7FFFH |     | 1   | 0        | 1    | U   |  |  |  |

|       | 52    | :      | : : :       | :                 |     |     |          |      |     |  |  |  |

|       |       | 416    | 4KB         | 1A0000H – 1A0FFFH |     |     |          |      |     |  |  |  |

#### Table 1: F25L16QA Sector Address Table

| 64KB  | 32KB  | Sector | Sector Size |                   |     | Blo | ck Add | ress |     |

|-------|-------|--------|-------------|-------------------|-----|-----|--------|------|-----|

| Block | Block | Sector | (Kbytes)    | Address range     | A20 | A19 | A18    | A17  | A16 |

|       |       | 415    | 4KB         | 19F000H – 19FFFFH |     |     |        |      |     |

|       | 51    | :      | :           | :                 |     |     |        | 0    |     |

| 25    |       | 408    | 4KB         | 198000H – 198FFFH | 1   | 1   | 0      |      | 1   |

| 25    |       | 407    | 4KB         | 197000H – 197FFFH |     | •   | Ū      | Ŭ    | •   |

|       | 50    | :      | :           | :                 |     |     |        |      |     |

|       |       | 400    | 4KB         | 190000H – 190FFFH |     |     |        |      |     |

|       |       | 399    | 4KB         | 18F000H – 18FFFFH |     |     |        |      |     |

|       | 49    | :      | :           | :                 |     |     |        |      |     |

| 24    |       | 392    | 4KB         | 188000H – 188FFFH | 1   | 1   | 0      | 0    | 0   |

| 24    |       | 391    | 4KB         | 187000H – 187FFFH |     | •   | U      | U    | U   |

|       | 48    | :      | :           | :                 |     |     |        |      |     |

|       |       | 384    | 4KB         | 180000H – 180FFFH |     |     |        |      |     |

|       |       | 383    | 4KB         | 17F000H – 17FFFFH |     |     |        |      |     |

|       | 47    | :      | :           | :                 | 1   |     |        |      |     |

| 22    |       | 376    | 4KB         | 178000H – 178FFFH |     | 0   |        |      |     |

| 23    |       | 375    | 4KB         | 177000H – 177FFFH | - 1 | 0   | 1      | 1    | 1   |

|       | 46    | :      | :           | :                 |     |     |        |      |     |

|       |       | 368    | 4KB         | 170000H – 170FFFH |     |     |        |      |     |

|       |       | 367    | 4KB         | 16F000H – 16FFFFH |     |     |        |      |     |

|       | 45    | :      | :           | :                 |     |     |        |      |     |

| 22    |       | 360    | 4KB         | 168000H – 168FFFH |     | •   |        | 1    | •   |

| 22    |       | 359    | 4KB         | 167000H – 167FFFH | - 1 | 0   | 1      |      | 0   |

|       | 44    | :      | :           | :                 |     |     |        |      |     |

|       |       | 352    | 4KB         | 160000H – 160FFFH |     |     |        |      |     |

|       |       | 351    | 4KB         | 15F000H – 15FFFFH |     |     |        |      |     |

|       | 43    | :      | :           | :                 |     |     |        |      |     |

| 24    |       | 344    | 4KB         | 158000H – 158FFFH |     | •   |        | •    |     |

| 21    |       | 343    | 4KB         | 157000H – 157FFFH | - 1 | 0   | 1      | 0    | 1   |

|       | 42    | :      | :           | :                 |     |     |        |      |     |

|       |       | 336    | 4KB         | 150000H – 150FFFH |     |     |        |      |     |

|       |       | 335    | 4KB         | 14F000H – 14FFFFH |     |     |        |      |     |

|       | 41    | :      | :           | :                 | 1   |     |        |      |     |

|       |       | 328    | 4KB         | 148000H – 148FFFH |     | •   |        | •    | _   |

| 20    |       | 327    | 4KB         | 147000H – 147FFFH | - 1 | 0   | 1      | 0    | 0   |

|       | 40    | :      | :           | :                 | 1   |     |        |      |     |

|       |       | 320    | 4KB         | 140000H – 140FFFH |     |     |        |      |     |

|       |       | 319    | 4KB         | 13F000H – 13FFFFH |     |     |        |      |     |

|       | 39    | :      | :           | :                 | 1   |     |        |      |     |

| 40    |       | 312    | 4KB         | 138000H – 138FFFH |     | _   | _      |      |     |

| 19    |       | 311    | 4KB         | 137000H – 137FFFH | - 1 | 0   | 0      | 1    | 1   |

|       | 38    | :      | :           | :                 | 1   |     |        |      |     |

|       |       | 304    | 4KB         | 130000H – 130FFFH | 1   |     |        |      |     |

| Table 1: F25L16Q/ | Sector Address | Table – Continued I |

|-------------------|----------------|---------------------|

|-------------------|----------------|---------------------|

| 64KB  | 32KB  | Sector | Sector Size | Address range     |     | Blo | ck Add | ress |     |

|-------|-------|--------|-------------|-------------------|-----|-----|--------|------|-----|

| Block | Block | Sector | (Kbytes)    | Address range     | A20 | A19 | A18    | A17  | A16 |

|       |       | 303    | 4KB         | 12F000H – 12FFFFH |     |     |        |      |     |

|       | 37    | :      | :           | :                 |     |     |        |      |     |

| 18    |       | 296    | 4KB         | 128000H – 128FFFH | 1   | 0   | 0      | 1    | 0   |

| 10    |       | 295    | 4KB         | 127000H – 127FFFH | ] ' | U   | U      | •    | U   |

|       | 36    |        | :           |                   |     |     |        |      |     |

|       |       | 288    | 4KB         | 120000H – 120FFFH |     |     |        |      |     |

|       |       | 287    | 4KB         | 11F000H – 11FFFFH |     |     |        |      |     |

|       | 35    | :      | :           | :                 |     |     |        |      |     |

| 17    |       | 280    | 4KB         | 118000H – 118FFFH | 1   | 0   | 0      | 0    | 1   |

| 17    |       | 279    | 4KB         | 117000H – 117FFFH | ] ' | U   |        | U    | •   |

|       | 34    | :      | :           | :                 |     |     |        |      |     |

|       |       | 272    | 4KB         | 110000H – 110FFFH |     |     |        |      |     |

|       |       | 271    | 4KB         | 10F000H – 10FFFFH |     |     |        |      |     |

|       | 33    | :      | :           | :                 | 1   |     |        |      |     |

| 46    |       | 264    | 4KB         | 108000H – 108FFFH |     | •   | •      | •    | •   |

| 16    |       | 263    | 4KB         | 107000H – 107FFFH | - 1 | 0   | 0      | 0    | 0   |

|       | 32    | :      | :           | :                 | -   |     |        |      |     |

|       |       | 256    | 4KB         | 100000H – 100FFFH |     |     |        |      |     |

|       |       | 255    | 4KB         | 0FF000H – 0FFFFFH |     |     |        |      |     |

|       | 31    | :      | :           | :                 |     |     |        |      |     |

| 45    |       | 248    | 4KB         | 0F8000H – 0F8FFFH |     |     |        | 1    |     |

| 15    |       | 247    | 4KB         | 0F7000H – 0F7FFFH | 0   | 1   | 1      |      | 1   |

|       | 30    | :      | :           | :                 |     |     |        |      |     |

|       |       | 240    | 4KB         | 0F0000H – 0F0FFFH |     |     |        |      |     |

|       |       | 239    | 4KB         | 0EF000H – 0EFFFFH |     |     |        |      |     |

|       | 29    | :      | :           | :                 |     |     |        |      |     |

|       |       | 232    | 4KB         | 0E8000H – 0E8FFFH |     |     |        |      | •   |

| 14    |       | 231    | 4KB         | 0E7000H – 0E7FFFH | 0   | 1   | 1      | 1    | 0   |

|       | 28    | :      | :           | :                 |     |     |        |      |     |

|       |       | 224    | 4KB         | 0E0000H – 0E0FFFH |     |     |        |      |     |

|       |       | 223    | 4KB         | 0DF000H – 0DFFFFH |     |     |        |      |     |

|       | 27    | :      | :           | :                 | 1   |     |        |      |     |

| 40    |       | 216    | 4KB         | 0D8000H – 0D8FFFH |     |     |        | •    |     |

| 13    |       | 215    | 4KB         | 0D7000H – 0D7FFFH | 0   | 1   | 1      | 0    | 1   |

|       | 26    | :      | :           | :                 | 1   |     |        |      |     |

|       |       | 208    | 4KB         | 0D0000H – 0D0FFFH | 1   |     |        |      |     |

|       |       | 207    | 4KB         | 0CF000H – 0CFFFFH |     |     |        |      |     |

|       | 25    | :      | :           | :                 | 1   |     |        |      |     |

| 40    |       | 200    | 4KB         | 0C8000H – 0C8FFFH |     |     |        | •    | •   |

| 12    |       | 199    | 4KB         | 0C7000H – 0C7FFFH | 0   | 1   | 1      | 0    | 0   |

|       | 24    | :      | :           | :                 | 1   |     |        |      |     |

|       |       | 192    | 4KB         | 0C0000H – 0C0FFFH | 1   |     |        |      |     |

| Table 1: F25L16QA S | Sector Address | Table – Continued II |

|---------------------|----------------|----------------------|

|---------------------|----------------|----------------------|

| 64KB  | 32KB  | Sector | Sector Size | Addross range     |     | Blo | ck Add | ress |     |   |   |

|-------|-------|--------|-------------|-------------------|-----|-----|--------|------|-----|---|---|

| Block | Block | Sector | (Kbytes)    | Address range     | A20 | A19 | A18    | A17  | A16 |   |   |

|       |       | 191    | 4KB         | 0BF000H – 0BFFFFH |     |     |        |      |     |   |   |

|       | 23    | :      | :           | :                 |     |     |        |      |     |   |   |

| 11    |       | 184    | 4KB         | 0B8000H – 0B8FFFH | 0   | 1   | 0      | 1    | 1   |   |   |

|       |       | 183    | 4KB         | 0B7000H – 0B7FFFH |     | •   | U      | •    | · · |   |   |

|       | 22    |        | :           |                   |     |     |        |      |     |   |   |

|       |       | 176    | 4KB         | 0B0000H – 0B0FFFH |     |     |        |      |     |   |   |

|       |       | 175    | 4KB         | 0AF000H – 0AFFFFH |     |     |        |      |     |   |   |

|       | 21    | :      | :           | :                 |     |     |        |      |     |   |   |

| 10    |       | 168    | 4KB         | 0A8000H – 0A8FFFH | 0   | 1   | 0      | 1    | 0   |   |   |

| 10    |       | 167    | 4KB         | 0A7000H – 0A7FFFH | , U | 1   | U      | •    | U   |   |   |

|       | 20    | :      | :           | :                 |     |     |        |      |     |   |   |

|       |       | 160    | 4KB         | 0A0000H – 0A0FFFH |     |     |        |      |     |   |   |

|       |       | 159    | 4KB         | 09F000H – 09FFFFH |     |     |        |      |     |   |   |

|       | 19    | :      | :           | :                 |     |     |        |      |     |   |   |

| •     |       | 152    | 4KB         | 098000H – 098FFFH |     |     | •      | •    |     |   |   |

| 9     |       | 151    | 4KB         | 097000H – 097FFFH | 0   | U   | U      | 1    | 0   | 0 | 1 |

|       | 18    | :      | :           | :                 |     |     |        |      |     |   |   |

|       |       | 144    | 4KB         | 090000H – 090FFFH |     |     |        |      |     |   |   |

|       |       | 143    | 4KB         | 08F000H – 08FFFFH |     |     |        |      |     |   |   |

|       | 17    | :      | :           |                   |     |     |        |      |     |   |   |

| •     |       | 136    | 4KB         | 088000H – 088FFFH |     |     |        | 0    |     |   |   |

| 8     |       | 135    | 4KB         | 087000H – 087FFFH | 0   | 1   | 0      |      | 0   |   |   |

|       | 16    | :      | :           | :                 |     |     |        |      |     |   |   |

|       |       | 128    | 4KB         | 080000H – 080FFFH |     |     |        |      |     |   |   |

|       |       | 127    | 4KB         | 07F000H – 07FFFFH |     |     |        |      |     |   |   |

|       | 15    | :      | :           | :                 | -   |     |        |      |     |   |   |

| _     |       | 120    | 4KB         | 078000H – 078FFFH |     |     |        |      |     |   |   |

| 7     |       | 119    | 4KB         | 077000H – 077FFFH | 0   | 0   | 1      | 1    | 1   |   |   |

|       | 14    | :      | :           | :                 |     |     |        |      |     |   |   |

|       |       | 112    | 4KB         | 070000H – 070FFFH |     |     |        |      |     |   |   |

|       |       | 111    | 4KB         | 06F000H – 06FFFFH |     |     |        |      |     |   |   |

|       | 13    | :      | :           | :                 | 1   |     |        |      |     |   |   |

|       |       | 104    | 4KB         | 068000H – 068FFFH | 1   |     |        |      |     |   |   |

| 6     |       | 103    | 4KB         | 067000H – 067FFFH | 0   | 0   | 1      | 1    | 0   |   |   |

|       | 12    | :      | :           | :                 |     |     |        |      |     |   |   |

|       |       | 96     | 4KB         | 060000H – 060FFFH | -   |     |        |      |     |   |   |

|       |       | 95     | 4KB         | 05F000H – 05FFFFH |     |     |        |      |     |   |   |

|       | 11    | :      | :           | :                 | 1   |     |        |      |     |   |   |

| _     |       | 88     | 4KB         | 058000H – 058FFFH |     | _   |        | _    |     |   |   |

| 5     |       | 87     | 4KB         | 057000H – 057FFFH | 0   | 0   | 1      | 0    | 1   |   |   |

|       | 10    | :      | :           | :                 |     |     |        |      |     |   |   |

|       |       | 80     | 4KB         | 050000H – 050FFFH | 1   |     |        |      |     |   |   |

| 64KB  | 32KB  | Sector | Sector Size | Address range     |     | Blo | ck Add | ress |     |

|-------|-------|--------|-------------|-------------------|-----|-----|--------|------|-----|

| Block | Block | Sector | (Kbytes)    | Address range     | A20 | A19 | A18    | A17  | A16 |

|       |       | 79     | 4KB         | 04F000H – 04FFFFH |     |     |        |      |     |

|       | 9     | :      | :           | :                 |     |     |        |      |     |

| 4     |       | 72     | 4KB         | 048000H – 048FFFH | 0   | 0   | 1      | 0    | 0   |

| 4     |       | 71     | 4KB         | 047000H – 047FFFH | Ū   | U   | •      | U    | U   |

|       | 8     | :      | :           | :                 |     |     |        |      |     |

|       |       | 64     | 4KB         | 040000H – 040FFFH |     |     |        |      |     |

|       |       | 63     | 4KB         | 03F000H – 03FFFFH |     |     |        |      |     |

|       | 7     | :      | :           | :                 |     |     |        |      |     |

| 3     |       | 56     | 4KB         | 038000H – 038FFFH | 0   | 0   | 0      | 1    | 1   |

| 3     |       | 55     | 4KB         | 037000H – 037FFFH | U   | U   | U      |      | 1   |

|       | 6     | :      | :           | :                 |     |     |        |      |     |

|       |       | 48     | 4KB         | 030000H – 030FFFH |     |     |        |      |     |

|       |       | 47     | 4KB         | 02F000H – 02FFFFH |     |     |        | 1    |     |

|       | 5     | :      | :           | :                 |     |     |        |      |     |

| 2     |       | 40     | 4KB         | 028000H – 028FFFH | 0   | 0   | 0      |      | 0   |

| Z     |       | 39     | 4KB         | 027000H – 027FFFH | U   | U   | U      | 1    | U   |

|       | 4     | :      | :           | :                 |     |     |        |      |     |

|       |       | 32     | 4KB         | 020000H – 020FFFH |     |     |        |      |     |

|       |       | 31     | 4KB         | 01F000H – 01FFFFH |     |     |        |      |     |

|       | 3     | :      | :           | :                 |     |     |        |      |     |

| 1     |       | 24     | 4KB         | 018000H – 018FFFH | 0   | 0   | 0      | 0    | 1   |

| I     |       | 23     | 4KB         | 017000H – 017FFFH | U   | U   | U      | U    | 1   |

|       | 2     | :      | :           | :                 |     |     |        |      |     |

|       |       | 16     | 4KB         | 010000H – 010FFFH |     |     |        |      |     |

|       |       | 15     | 4KB         | 00F000H – 00FFFFH |     |     |        |      |     |

|       | 1     | :      | :           | :                 | ]   |     |        |      |     |

| 0     |       | 8      | 4KB         | 008000H – 008FFFH | 0   | •   | 0      | 0    | 0   |

| U     |       | 7      | 4KB         | 007000H – 007FFFH |     | 0   | U      | U    | U   |

|       | 0     | :      | :           | :                 |     |     |        |      |     |

|       |       | 0      | 4KB         | 000000H – 000FFFH | ]   |     |        |      |     |

Table 1: F25L16QA Sector Address Table – Continued IV

## STATUS REGISTER

The software status register provides status on whether the flash memory array is available for any Read or Write operation, whether the device is Write enabled, and the state of the memory Write protection. During an internal Erase or Program operation, the status register may be read only to determine the completion of an operation in progress. Table 2 describes the function of each bit in the software status register.

| Bit      | Name     | Function                                                                                                             | Default at<br>Power-up | Read/Write |

|----------|----------|----------------------------------------------------------------------------------------------------------------------|------------------------|------------|

| Status F | Register |                                                                                                                      |                        |            |

| 0        | BUSY     | <ul><li>1 = Internal Write operation is in progress</li><li>0 = No internal Write operation is in progress</li></ul> | 0                      | R          |

| 1        | WEL      | <ul><li>1 = Device is memory Write enabled</li><li>0 = Device is not memory Write enabled</li></ul>                  | 0                      | R          |

| 2        | BP0      | Indicate current level of block write protection (See Table 3)                                                       | 0                      | R/W        |

| 3        | BP1      | Indicate current level of block write protection (See Table 3)                                                       | 0                      | R/W        |

| 4        | BP2      | Indicate current level of block write protection (See Table 3)                                                       | 0                      | R/W        |

| 5        | BP3      | Indicate current level of block write protection (See Table 3)                                                       | 0                      | R/W        |

| 6        | QE       | 1 = Quad enabled<br>0 = Quad disabled                                                                                | 0                      | R/W        |

| 7        | BPL      | 1 = BP3, BP2,BP1,BP0 are read-only bits<br>0 = BP3, BP2,BP1,BP0 are read/writable                                    | 0                      | R/W        |

#### **Table 2: Software Status Register**

Note:

1. BUSY and WEL are read only.

2. BP0~3, QE and BPL bits are non-volatile.

#### Write Enable Latch (WEL)

The Write-Enable-Latch bit indicates the status of the internal memory Write Enable Latch. If this bit is set to "1", it indicates the device is Write enabled. If the bit is set to "0" (reset), it indicates the device is not Write enabled and does not accept any memory Write (Program/ Erase) commands. This bit is automatically reset under the following conditions:

#### • Power-up

- Write Disable (WRDI) instruction completion

- · Page Program instruction completion

- Sector Erase instruction completion

- Block Erase instruction completion

- Chip Erase instruction completion

- · Write Status Register instructions

#### BUSY

The BUSY bit determines whether there is an internal Erase or Program operation in progress. A "1" for the BUSY bit indicates the device is busy with an operation in progress. A "0" indicates the device is ready for the next valid operation.

| Protection Level |     | Status Re | egister Bit |     | Protected   | l Memory Area     |

|------------------|-----|-----------|-------------|-----|-------------|-------------------|

| FIOLECTION Level | BP3 | BP2       | BP1         | BP0 | Block Range | Address Range     |

| 0                | 0   | 0         | 0           | 0   | None        | None              |

| Upper 1/32       | 0   | 0         | 0           | 1   | Block 31    | 1F0000H – 1FFFFFH |

| Upper 1/16       | 0   | 0         | 1           | 0   | Block 30~31 | 1E0000H – 1FFFFFH |

| Upper 1/8        | 0   | 0         | 1           | 1   | Block 28~31 | 1C0000H – 1FFFFFH |

| Upper 1/4        | 0   | 1         | 0           | 0   | Block 24~31 | 180000H – 1FFFFFH |

| Upper 1/2        | 0   | 1         | 0           | 1   | Block 16~31 | 100000H – 1FFFFFH |

| All Blocks       | 0   | 1         | 1           | 0   | Block 0~31  | 000000H – 1FFFFFH |

| All Blocks       | 0   | 1         | 1           | 1   | Block 0~31  | 000000H – 1FFFFFH |

| All Blocks       | 1   | 0         | 0           | 0   | Block 0~31  | 000000H – 1FFFFFH |

| All Blocks       | 1   | 0         | 0           | 1   | Block 0~31  | 000000H – 1FFFFFH |

| Bottom 1/2       | 1   | 0         | 1           | 0   | Block 0~15  | 000000H – 0FFFFFH |

| Bottom 3/4       | 1   | 0         | 1           | 1   | Block 0~23  | 000000H –17FFFFH  |

| Bottom 7/8       | 1   | 1         | 0           | 0   | Block 0~27  | 000000H –1BFFFFH  |

| Bottom 15/16     | 1   | 1         | 0           | 1   | Block 0~29  | 000000H – 1DFFFFH |

| Bottom 31/32     | 1   | 1         | 1           | 0   | Block 0~30  | 000000H – 1EFFFFH |

| All Blocks       | 1   | 1         | 1           | 1   | Block 0~31  | 000000H – 1FFFFFH |

## Table 3: F25L16QA Block Protection Table

## Block Protection (BP3, BP2, BP1, BP0)

The Block-Protection (BP3, BP2, BP1, BP0) bits define the memory area, as defined in Table 3, to be software protected against any memory Write (Program or Erase) operations. The Write Status Register (WRSR) instruction is used to program the

BP3, BP2, BP1 and BP0 bits as long as  $\overline{WP}$  is high or the Block- Protection-Look (BPL) bit is 0. Chip Erase can only be executed if BP3, BP2, BP1 and BP0 bits are all 0. The factory default setting for Block Protection Bit (BP3 ~ BP0) is 0.

## Quad Enable (QE)

When the Quad Enable bit is reset to "0" (factory default),  $\overline{WP}$  and  $\overline{HOLD}$  pins are enabled. When QE pin is set to "1", Quad SIO<sub>2</sub> and SIO<sub>3</sub> are enabled. (The QE should never be set to "1" during standard and Dual SPI operation if the  $\overline{WP}$  and  $\overline{HOLD}$  pins are tied directly to the V<sub>DD</sub> or V<sub>SS</sub>.)

#### **Block Protection Lock-Down (BPL)**

WP pin driven low (V<sub>IL</sub>), enables the Block-Protection-Lock-Down (BPL) bit. When BPL is set to 1, it prevents any further alteration of the BPL, BP3, BP2, BP1 and BP0 bits. When the  $\overline{WP}$  pin is driven high (V<sub>IH</sub>), the BPL bit has no effect and its value is "Don't Care".

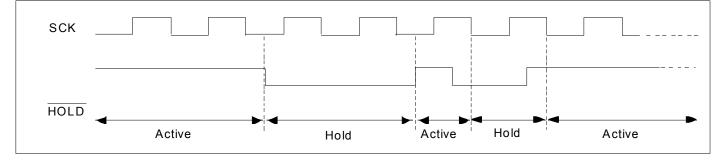

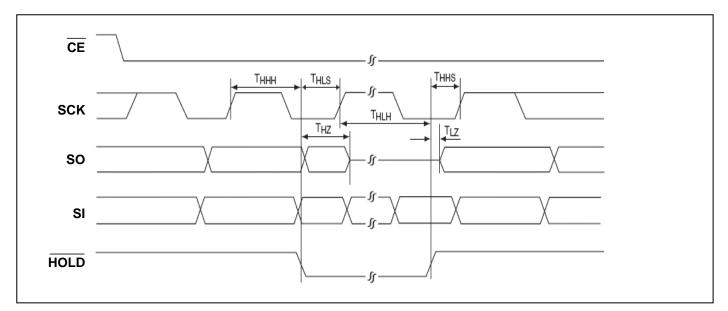

## HOLD OPERATION

HOLD pin is used to pause a serial sequence underway with the SPI flash memory without resetting the clocking sequence. To activate the  $\overline{\text{HOLD}}$  mode,  $\overline{\text{CE}}$  must be in active low state. The  $\overline{\text{HOLD}}$  mode begins when the SCK active low state coincides with the falling edge of the  $\overline{\text{HOLD}}$  signal. The HOLD mode ends when the  $\overline{\text{HOLD}}$  signal's rising edge coincides with the SCK active low state.

If the falling edge of the  $\overline{\text{HOLD}}$  signal does not coincide with the SCK active low state, then the device enters Hold mode when the SCK next reaches the active low state.

Similarly, if the rising edge of the HOLD signal does not coincide with the SCK active low state, then the device exits in Hold mode when the SCK next reaches the active low state. See Figure 1 for Hold Condition waveform.

Once the device enters Hold mode, SO will be in high impedance state while SI and SCK can be  $V_{IL}$  or  $V_{IH}$ .

If  $\overline{CE}$  is driven active high during a Hold condition, it resets the internal logic of the device. As long as  $\overline{HOLD}$  signal is low, the memory remains in the Hold condition. To resume communication with the device,  $\overline{HOLD}$  must be driven active high, and  $\overline{CE}$  must be driven active low. See Figure 35 for Hold timing.

The  $\overline{HOLD}$  function is only available for Standard SPI and Dual SPI operation, not during Quad SPI because this pin is used for SIO<sub>3</sub> when the QE bit of Status Register is set for Quad I/O.

Figure 1: HOLD Condition Waveform

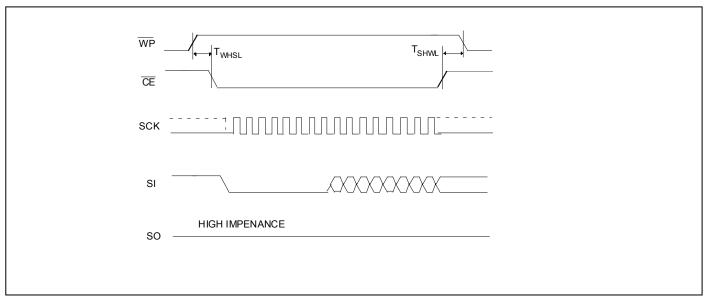

## WRITE PROTECTION

The device provides software Write Protection.

The Write-Protect pin ( $\overline{\text{WP}}$ ) enables or disables the lock-down function of the status register. The Block-Protection bits (BP3, BP2, BP1, BP0 and BPL) in the status register provide Write protection to the memory array and the status register. When the QE bit of Status Register is set for Quad I/O, the  $\overline{\text{WP}}$  pin function is not available since this pin is used for SIO<sub>2</sub>.

## Write Protect Pin (WP)

The Write-Protect ( $\overline{\text{WP}}$ ) pin enables the lock-down function of the BPL bit (bit 7) in the status register. When  $\overline{\text{WP}}$  is driven low, the execution of the Write Status Register (WRSR) instruction is determined by the value of the BPL bit (see Table 4). When  $\overline{\text{WP}}$  is high, the lock-down function of the BPL bit is disabled.

#### Table 4: Conditions to Execute Write-Status- Register (WRSR) Instruction

| WP | BPL | Execute WRSR Instruction |

|----|-----|--------------------------|

| L  | 1   | Not Allowed              |

| L  | 0   | Allowed                  |

| Н  | Х   | Allowed                  |

## INSTRUCTIONS

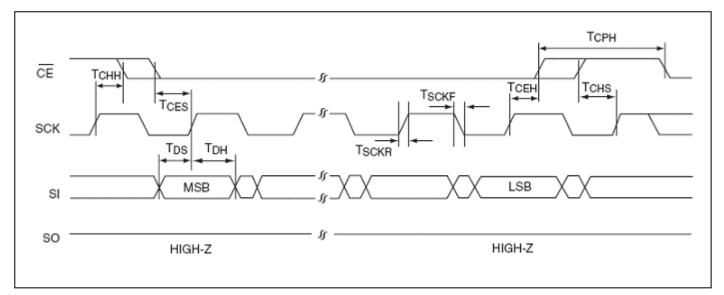

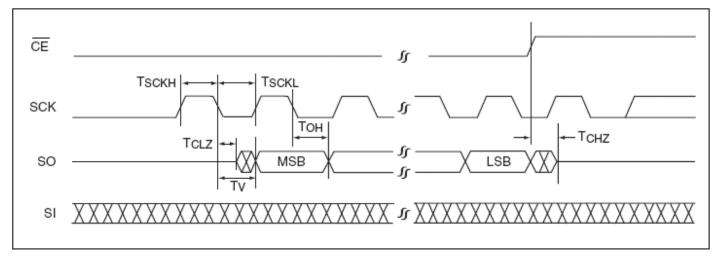

Instructions are used to Read, Write (Erase and Program), and configure the F25L16QA. The instruction bus cycles are 8 bits each for commands (Op Code), data, and addresses. Prior to executing any Page Program, Write Status Register, Sector Erase, Block Erase, or Chip Erase instructions, the Write Enable (WREN) instruction must be executed first. The complete list of the instructions is provided in Table 5. All instructions are synchronized off a high to low transition of  $\overrightarrow{CE}$ . Inputs will be accepted on the rising edge of SCK starting with the most significant bit.  $\overrightarrow{CE}$  must be driven low before an instruction is

entered and must be driven high after the last bit of the instruction has been shifted in (except for Read, Read ID, Read Status Register, Read Electronic Signature instructions). Any low to high transition on  $\overline{CE}$ , before receiving the last bit of an instruction bus cycle, will terminate the instruction in progress and return the device to the standby mode.

Instruction commands (Op Code), addresses, and data are all input from the most significant bit (MSB) first.

|                                                      | Max          |              |      | Bus Cycle <sup>1~3</sup>                             |                                                       |                                 |                                |                                |                 |                  |            |                  |                   |                       |       |

|------------------------------------------------------|--------------|--------------|------|------------------------------------------------------|-------------------------------------------------------|---------------------------------|--------------------------------|--------------------------------|-----------------|------------------|------------|------------------|-------------------|-----------------------|-------|

| Operation                                            | Max.<br>Freq | 1            |      | 2                                                    |                                                       | 3                               |                                | 4                              |                 | 5                |            | 6                |                   | N                     |       |

|                                                      |              | SIN          | SOUT | S <sub>IN</sub>                                      | SOUT                                                  | SIN                             | <b>S</b> <sub>OUT</sub>        | SIN                            | SOUT            | SIN              | SOUT       | SIN              | SOUT              | SIN                   | SOUT  |

| Read                                                 | 50 MHz       | 03H          | Hi-Z | A <sub>23</sub> -A <sub>16</sub>                     | Hi-Z                                                  | A <sub>15</sub> -A <sub>8</sub> | Hi-Z                           | A <sub>7</sub> -A <sub>0</sub> | Hi-Z            | Х                | $D_{OUT0}$ | Х                | D <sub>OUT1</sub> | Х                     | cont. |

| Fast Read                                            |              | 0BH          | Hi-Z | A <sub>23</sub> -A <sub>16</sub>                     | Hi-Z                                                  | A <sub>15</sub> -A <sub>8</sub> | Hi-Z                           | A <sub>7</sub> -A <sub>0</sub> | Hi-Z            | Х                | Х          | Х                | D <sub>OUT0</sub> | Х                     | cont. |

| Fast Read Dual Output <sup>12,13</sup>               |              | 3            | BH   | A <sub>23</sub> -                                    | -A <sub>16</sub>                                      | A <sub>15</sub> -               | A <sub>8</sub>                 | A7-                            | -A <sub>0</sub> | )                | X          | Dou              | JT0~1             | CO                    | nt.   |

| Fast Read Dual I/O <sup>12, 14</sup>                 |              | В            | BH   | A <sub>23</sub>                                      | -A <sub>8</sub>                                       | A7-A0, N                        | И <sub>7</sub> -М <sub>0</sub> | Dou                            | IT0~1           | со               | nt.        |                  | -                 | -                     | -     |

| Fast Read Quad<br>Output <sup>12, 15</sup>           |              | 6            | BH   | A <sub>23</sub> .                                    | -A <sub>16</sub>                                      | A <sub>15</sub> -               | A <sub>8</sub>                 | A <sub>7</sub> .               | -A <sub>0</sub> | )                | X          | Dou              | JT0~3             | со                    | nt.   |

| Fast Read Quad I/O <sup>12, 16</sup>                 |              | E            | BH   | A <sub>23</sub> -A <sub>0</sub>                      | M <sub>7</sub> -M <sub>0</sub>                        | X, Dou                          | JT0~1                          | Dou                            | IT2~6           | CO               | nt.        |                  | -                 | -                     | -     |

| Sector Erase <sup>4</sup> (4K Byte)                  |              | 20H          | Hi-Z | A <sub>23</sub> -A <sub>16</sub>                     | Hi-Z                                                  | A <sub>15</sub> -A <sub>8</sub> | Hi-Z                           | A <sub>7</sub> -A <sub>0</sub> | Hi-Z            | -                | -          | -                | -                 | -                     | -     |

| Block Erase <sup>5</sup> (32K Byte)                  |              | 52H          | Hi-Z | A <sub>23</sub> -A <sub>16</sub>                     | Hi-Z                                                  | A <sub>15</sub> -A <sub>8</sub> | Hi-Z                           | A <sub>7</sub> -A <sub>0</sub> | Hi-Z            | -                | -          | -                | -                 | -                     | -     |

| Block Erase <sup>5</sup> (64K Byte)                  |              | D8H          | Hi-Z | A <sub>23</sub> -A <sub>16</sub>                     | Hi-Z                                                  | A <sub>15</sub> -A <sub>8</sub> | Hi-Z                           | A <sub>7</sub> -A <sub>0</sub> | Hi-Z            | -                | -          | -                | -                 | -                     | -     |

| Chip Erase                                           |              | 60H /<br>C7H | Hi-Z | -                                                    | -                                                     | -                               | -                              | -                              | -               | -                | -          | -                | -                 | -                     | -     |

| Erase Suspend                                        |              | 75H          | Hi-Z | -                                                    | -                                                     | -                               | -                              | -                              | -               | -                | -          | -                | -                 | -                     | -     |

| Erase Resume                                         |              | 7AH          | Hi-Z | -                                                    | -                                                     | -                               | -                              | -                              | -               | -                | -          | -                | -                 | -                     | -     |

| Page Program ( <b>PP</b> ) <sup>6</sup>              | 50MHz        | 02H          | Hi-Z | A <sub>23</sub> -A <sub>16</sub>                     | Hi-Z                                                  | A <sub>15</sub> -A <sub>8</sub> | Hi-Z                           | A <sub>7</sub> -A <sub>0</sub> | Hi-Z            | D <sub>IN0</sub> | Hi-Z       | D <sub>IN1</sub> | Hi-Z              | Up to<br>256<br>bytes | Hi-Z  |

| Quad Page Program <sup>17</sup>                      | ~            | 3            | 2H   | A <sub>23</sub> .                                    | -A <sub>16</sub>                                      | A <sub>15</sub> -               | A <sub>8</sub>                 | A <sub>7</sub> .               | -A <sub>0</sub> | DIN              | N0~3       | Dır              | N4~7              | Up to<br>by           |       |

| Mode Bit Reset <sup>18</sup>                         |              | FFH          | Hi-Z | FFH                                                  | Hi-Z                                                  | -                               | -                              | -                              | -               | -                | -          | -                | -                 | -                     | -     |

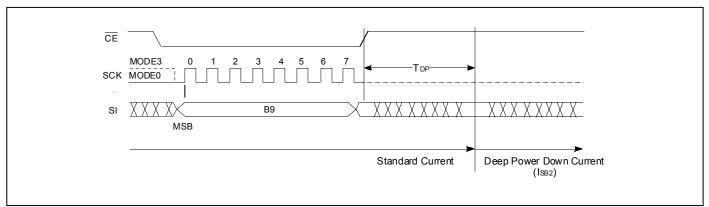

| Deep Power Down (DP)                                 |              | B9h          | Hi-Z | -                                                    | -                                                     | -                               | -                              | -                              | -               | -                | -          | -                | -                 | -                     | -     |

| Read Status Register ( <b>RDSR</b> ) <sup>7</sup>    | 100MHz       | 05H          | Hi-Z | Х                                                    | D <sub>OUT</sub><br>(S <sub>7</sub> -S <sub>0</sub> ) | -                               | -                              | -                              | -               | -                | -          | -                | -                 | -                     | -     |

| Write Status Register (WRSR) <sup>10</sup>           |              | 01H          | Hi-Z | D <sub>IN</sub><br>(S <sub>7</sub> -S <sub>0</sub> ) | Hi-Z                                                  | -                               | -                              |                                | -               | -                | -          | -                | -                 | -                     | -     |

| Write Enable (WREN) <sup>10</sup>                    |              | 06H          | Hi-Z | -                                                    | -                                                     | -                               | -                              | -                              | -               | -                | -          | -                | -                 | -                     | -     |

| Write Disable ( <b>WRDI</b> )/ Exit secured OTP mode |              | 04H          | Hi-Z | -                                                    | -                                                     | -                               | -                              | -                              | -               | -                | -          | -                | -                 | -                     | -     |

| Enter secured OTP mode (ENSO)                        |              | B1H          | Hi-Z | -                                                    | -                                                     | -                               | -                              |                                | -               | -                | -          | -                | -                 | -                     | -     |

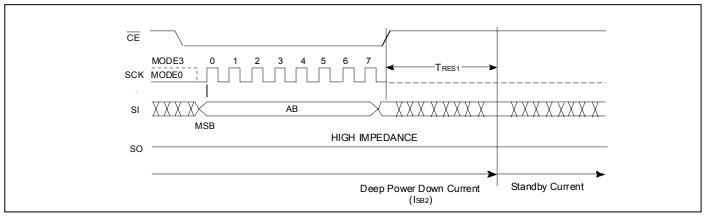

| Release from Deep Power<br>Down ( <b>RDP</b> )       |              | ABH          | Hi-Z | -                                                    | -                                                     | -                               | -                              | -                              | -               | -                | -          | -                | -                 | -                     | -     |

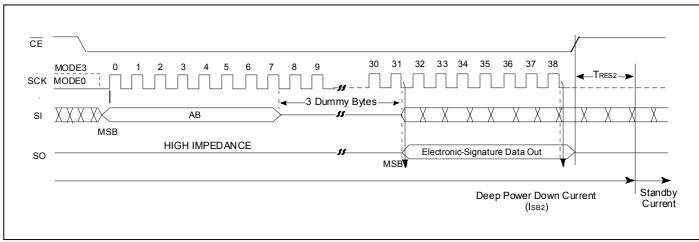

| Read Electronic Signature (RES) <sup>8</sup>         |              | ABH          | Hi-Z | Х                                                    | Х                                                     | х                               | х                              | х                              | Х               | Х                | 14H        | -                | -                 | -                     | -     |

| RES in secured OTP mode<br>& not lock down           |              | ABH          | Hi-Z | Х                                                    | Х                                                     | х                               | х                              | х                              | Х               | Х                | 34H        | -                | -                 | -                     | -     |

| <b>RES</b> in secured OTP mode & lock down           |              | ABH          | Hi-Z | х                                                    | Х                                                     | Х                               | х                              | х                              | Х               | Х                | 74H        | -                | -                 | -                     | -     |

## **Table 5: Device Operation Instruction**

|                                                   | Max.   |      |       |      |       |      | Bus   | s Cycle | <b>e</b> <sup>1~3</sup> |     |      |     |      |     |      |

|---------------------------------------------------|--------|------|-------|------|-------|------|-------|---------|-------------------------|-----|------|-----|------|-----|------|

| Operation                                         | Freq   |      | 1     | 1    | 2     | 3    |       | 4       | 4                       |     | 5    | (   | 6    | I   | N    |

|                                                   | печ    | SIN  | SOUT  | SIN  | SOUT  | SIN  | SOUT  | SIN     | SOUT                    | SIN | SOUT | SIN | SOUT | SIN | SOUT |

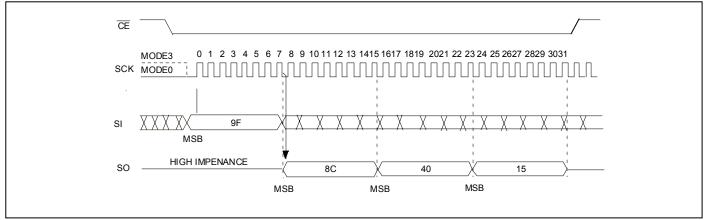

| Jedec Read ID<br>( <b>JEDEC-ID</b> ) <sup>9</sup> | 50MHz  | 9FH  | Hi-Z  | х    | 8CH   | х    | 40H   | Х       | 15H                     | -   | -    | -   | -    | -   | -    |

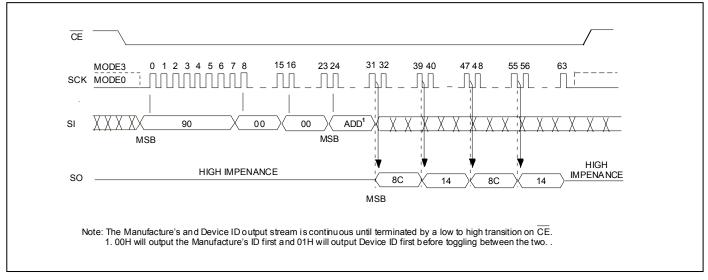

| Read ID ( <b>RDID</b> ) <sup>11</sup>             | 100MHz | ഹപ   | Hi-Z  | 00H  | Hi-Z  | 00H  | Hi-Z  | 00H     | Hi-Z                    | Х   | 8CH  | Х   | 14H  | -   | -    |

|                                                   |        | 9011 | 111-2 | 0011 | 111-2 | 0011 | 111-2 | 01H     | Hi-Z                    | Х   | 14H  | Х   | 8CH  | -   | -    |

#### Notes:

- 1. Operation:  $S_{IN}$  = Serial In,  $S_{OUT}$  = Serial Out, Bus Cycle 1 = Op Code

- 2. X = Dummy Input Cycles (V<sub>IL</sub> or V<sub>IH</sub>); = Non-Applicable Cycles (Cycles are not necessary); cont. = continuous

- 3. One bus cycle is eight clock periods.

- 4. 4K byte Sector Earse addresses: use A<sub>MS</sub> -A<sub>12</sub>, remaining addresses can be V<sub>IL</sub> or V<sub>IH</sub>.

- 5. 32K byte Block Earse addresses: use  $A_{MS}$  - $A_{15}$ , remaining addresses can be  $V_{IL}$  or  $V_{IH}$

- 64K byte Block Earse addresses: use A<sub>MS</sub> -A<sub>16</sub>, remaining addresses can be V<sub>IL</sub> or V<sub>IH</sub>

- 6. To continue programming to the next sequential address location, enter the 8-bit command, followed by the data to be programmed.

- 7. The Read-Status-Register is continuous with ongoing clock cycles until terminated by a low to high transition on  $\overline{\text{CE}}$ .

- 8. The Read-Electronic-Signature is continuous with on going clock cycles until terminated by a low to high transition on  $\overline{CE}$ .

- The JEDEC-Read-ID is output first byte 8CH as manufacture ID; second byte 40H as memory type; third byte 15H as memory capacity.

- The Write-Enable (WREN) instruction and the Write-Status-Register (WRSR) instruction must work in conjunction of each other. The WRSR instruction must be executed immediately (very next bus cycle) after the WREN instruction to make both instructions effective. A successful WRSR can reset WREN.

- 11. The Manufacture ID and Device ID output will repeat continuously until  $\overline{CE}$  terminates the instruction.

- 12. Dual and Quad commands use bidirectional IO pins. D<sub>OUT</sub> and cont. are serial data out; others are serial data in.

- 13. Dual output data: IO0 = (D6, D4, D2, D0), (D6, D4, D2, D0) IO1 = (D7, D5, D3, D1), (D7, D5, D3, D1) DOUT0 DOUT1

- 14. M<sub>7</sub>-M<sub>0</sub>: Mode bits. Dual input address:

- IO0 = (A22, A20, A18, A16, A14, A12, A10, A8) IO1 = (A23, A21, A19, A17, A15, A13, A11, A9)

Bus Cycle-2

Douts

Bus Cycle-3

(A6, A4, A2, A0, M6, M4, M2, M0)

(A7, A5, A3, A1, M7, M5, M3, M1)

15. Quad output data:  $IO_0 = (D_4, D_0), (D_4, D_0), (D_4, D_0), (D_4, D_0)$   $IO_1 = (D_5, D_1), (D_5, D_1), (D_5, D_1), (D_5, D_1)$   $IO_2 = (D_6, D_2), (D_6, D_2), (D_6, D_2), (D_6, D_2)$  $IO_3 = (D_7, D_3), (D_7, D_3), (D_7, D_3), (D_7, D_3)$

DOUT0 DOUT1 DOUT2

| Elite Semiconductor Memory Tec | hnology Inc. |

|--------------------------------|--------------|

|--------------------------------|--------------|

- 16. M<sub>7</sub>-M<sub>0</sub>: Mode bits. Quad input address:

- IO<sub>0</sub> = (A<sub>20</sub>, A<sub>16</sub>, A<sub>12</sub>, A<sub>8</sub>, A<sub>4</sub>, A<sub>0</sub>, M<sub>4</sub>, M<sub>0</sub>) IO<sub>1</sub> = (A<sub>21</sub>, A<sub>17</sub>, A<sub>13</sub>, A<sub>9</sub>, A<sub>5</sub>, A<sub>1</sub>, M<sub>5</sub>, M<sub>1</sub>) IO<sub>2</sub> = (A<sub>22</sub>, A<sub>18</sub>, A<sub>14</sub>, A<sub>10</sub>, A<sub>6</sub>, A<sub>2</sub>, M<sub>6</sub>, M<sub>2</sub>) IO<sub>3</sub> = (A<sub>23</sub>, A<sub>19</sub>, A<sub>15</sub>, A<sub>11</sub>, A<sub>7</sub>, A<sub>3</sub>, M<sub>7</sub>, M<sub>3</sub>)

Bus Cycle-2

| Fast Read Quad I/O data:<br>IO0 = (X, X), (X, X), (D4, D0), (D4, D0)                               | $(D_4 \ D_0)$ $(D_4 \ D_0)$ $(D_4 \ D_0)$ $(D_4 \ D_0)$ |

|----------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| $IO_1 = (X, X), (X, X), (D_2, D_3), (D_4, D_6)$<br>$IO_1 = (X, X), (X, X), (D_5, D_1), (D_5, D_1)$ |                                                         |

| $IO_2 = (X, X), (X, X), (D_6, D_2), (D_6, D_2)$                                                    |                                                         |

| IO3 = (X, X), (X, X), (D7, D3), (D7, D3)                                                           | (D7, D3), (D7, D3), (D7, D3), (D7, D3)                  |

|                                                                                                    |                                                         |

| DOUT0 DOUT1                                                                                        | Dout2 Dout3 Dout4 Dout5                                 |

|                                                                                                    |                                                         |

| Bus Cycle-3                                                                                        | Bus Cycle-4                                             |

17. The instruction is initiated by executing command code, followed by address bits into SI (SIO<sub>0</sub>) before D<sub>IN</sub>, and then input data to bidirectional IO pins (SIO<sub>0</sub> ~ SIO<sub>3</sub>).

| Quad input data      | i:        |           |          |

|----------------------|-----------|-----------|----------|

| $IO_0 = (D_4, D_0),$ | (D4, D0), | (D4, D0), | (D4, D0) |

| $IO_1 = (D_5, D_1),$ | (D5, D1), | (D5, D1), | (D5, D1) |

| $IO_2 = (D_6, D_2),$ | (D6, D2), | (D6, D2), | (D6, D2) |

| $IO_3 = (D_7, D_3),$ | (D7, D3), | (D7, D3), | (D7, D3) |

|                      |           |           |          |

| DINO                 | DIN1      | DIN2      | Ding     |

18. This instruction is recommended when using the Dual or Quad Mode bit feature.

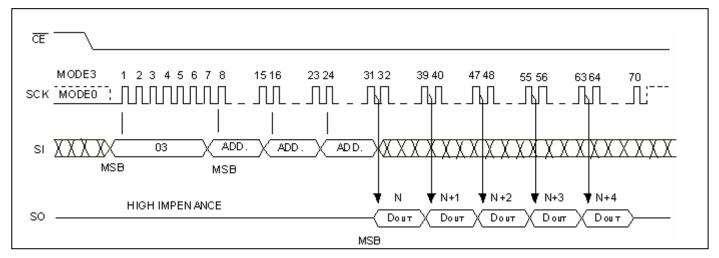

## Read (50MHz)

The Read instruction supports up to 50 MHz, it outputs the data starting from the specified address location. The data output stream is continuous through all addresses until terminated by a low to high transition on  $\overline{CE}$ . The internal address pointer will automatically increment until the highest memory address is reached. Once the highest memory address is reached, the address pointer will automatically increment to the beginning (wrap-around) of the address space, i.e. for 16Mbit density, once

the data from address location 1FFFFFH had been read, the next output will be from address location 000000H.

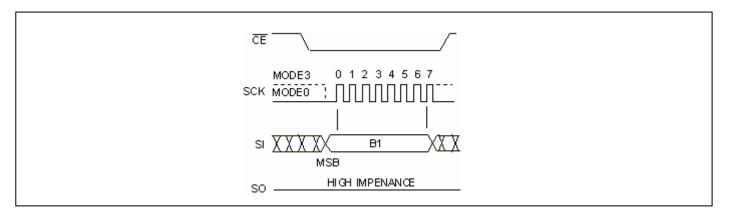

The Read instruction is initiated by executing an 8-bit command, 03H, followed by address bits  $[A_{23} - A_0]$ .  $\overline{CE}$  must remain active low for the duration of the Read cycle. See Figure 2 for the Read sequence.

Figure 2: Read Sequence

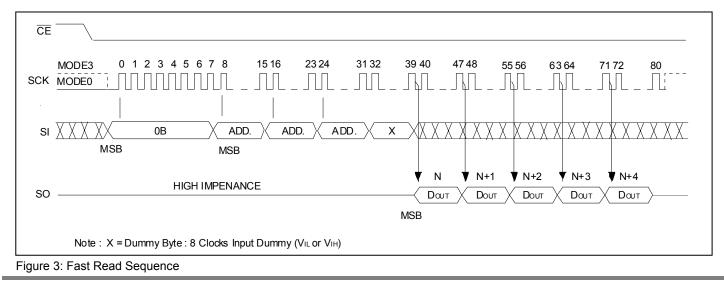

#### Fast Read (50 MHz ~ 100 MHz)

The Fast Read instruction supporting up to 100 MHz is initiated by executing an 8-bit command, 0BH, followed by address bits  $[A_{23}-A_0]$  and a dummy byte.  $\overline{CE}$  must remain active low for the duration of the Fast Read cycle. See Figure 3 for the Fast Read sequence.

Following a dummy byte (8 clocks input dummy cycle), the Fast Read instruction outputs the data starting from the specified address location. The data output stream is continuous through all addresses until terminated by a low to high transition on  $\overline{CE}$ . The internal address pointer will automatically increment until the highest memory address is reached. Once the highest memory address is reached, the address pointer will automatically increment to the beginning (wrap-around) of the address space, i.e. for 16Mbit density, once the data from address location 1FFFFFH has been read, the next output will be from address location 000000H.

Elite Semiconductor Memory Technology Inc.

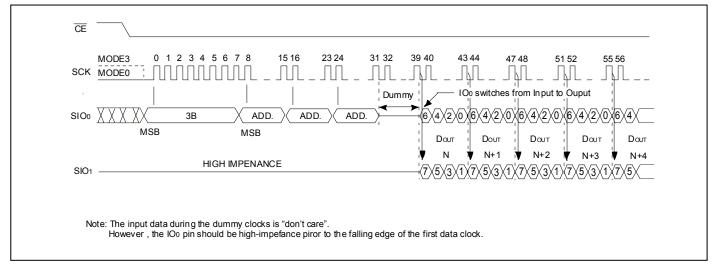

## Fast Read Dual Output (50 MHz ~ 100 MHz)

The Fast Read Dual Output (3BH) instruction is similar to the standard Fast Read (0BH) instruction except the data is output on bidirectional I/O pins (SIO<sub>0</sub> and SIO<sub>1</sub>). This allows data to be transferred from the device at twice the rate of standard SPI devices. This instruction is for quickly downloading code from Flash to RAM upon power-up or for applications that cache code-segments to RAM for execution.

The Fast Read Dual Output instruction is initiated by executing an 8-bit command, 3BH, followed by address bits  $[A_{23}-A_0]$  and a dummy byte.  $\overline{CE}$  must remain active low for the duration of the Fast Read Dual Output cycle. See Figure 4 for the Fast Read Dual Output sequence.

Figure 4: Fast Read Dual Output Sequence

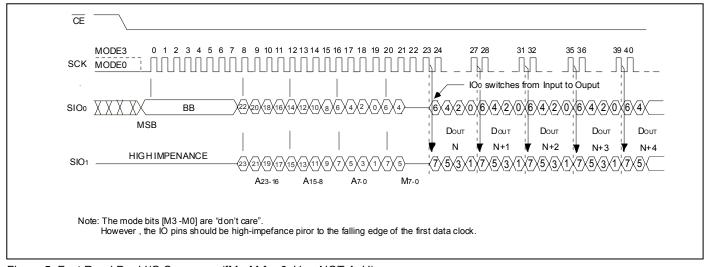

#### Fast Read Dual I/O (50 MHz ~ 100 MHz)

The Fast Read Dual I/O (BBH) instruction is similar to the Fast Read Dual Output (3BH) instruction, but with the capability to input address bits [ $A_{23}$ - $A_0$ ] two bits per clock.

To set mode bits  $[M_7 - M_0]$  after the address bits  $[A_{23} - A_0]$  can further reduce instruction overhead (See Figure 5). The upper mode bits  $[M_7 - M_4]$  controls the length of next Fast Read Dual I/O instruction with/without the first byte command code (BBH). The lower mode bits  $[M_3 - M_0]$  are "don't care".

If  $[M_7 - M_0] = "AxH"$ , the next Fast Read Dual I/O instruction (after  $\overline{CE}$  is raised and the lowered) doesn't need the command code (See Figure 6). This way let the instruction sequence reduce 8 clocks and allows to enter address immediately after  $\overline{CE}$  is asserted low. If  $[M_7 - M_0]$  are the value other than "AxH", the next instruction need the first byte command code, thus returning to normal operation. A Mode Bit Reset (FFH) also can be used to reset mode bits  $[M_7 - M_0]$  before issuing normal instructions.

Figure 5: Fast Read Dual I/O Sequence ([M7-M0] = 0xH or NOT AxH)

Figure 6: Fast Read Dual I/O Sequence ([M<sub>7</sub>-M<sub>0</sub>] = AxH)

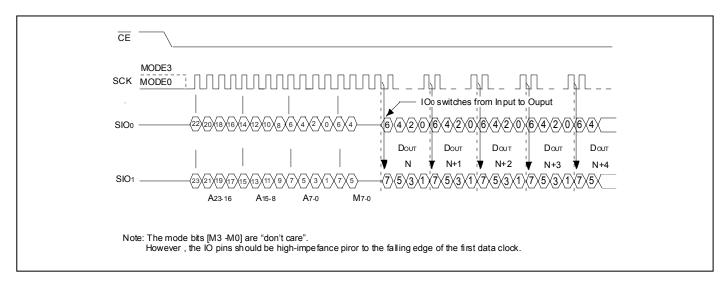

## Fast Read Quad Output (50 MHz ~ 100 MHz)

The Fast Read Quad Output (6B) instruction is similar to the Fast Read Dual Output (3BH) instruction except the data is output on bidirectional I/O pins (SIO0, SIO1, SIO2 and SIO3). A Quad Enable (QE) bit of Status Register must be set "1" to enable Quad function. This allows data to be transferred from the device at four times the rate of standard SPI devices.

The Fast Read Quad Output instruction is initiated by executing an 8-bit command, 6BH, followed by address bits  $[A_{23}-A_0]$  and a dummy byte.  $\overline{CE}$  must remain active low for the duration of the Fast Read Dual Output cycle. See Figure 7 for the Fast Read Quad Output sequence.

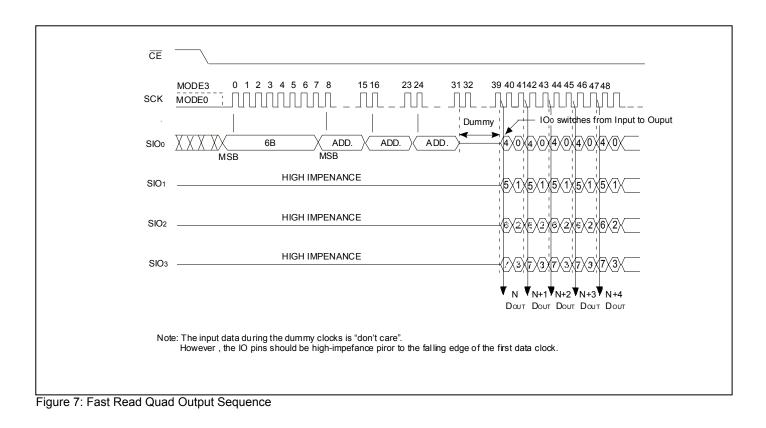

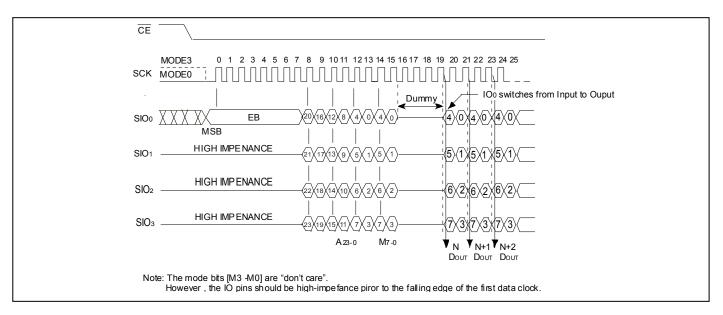

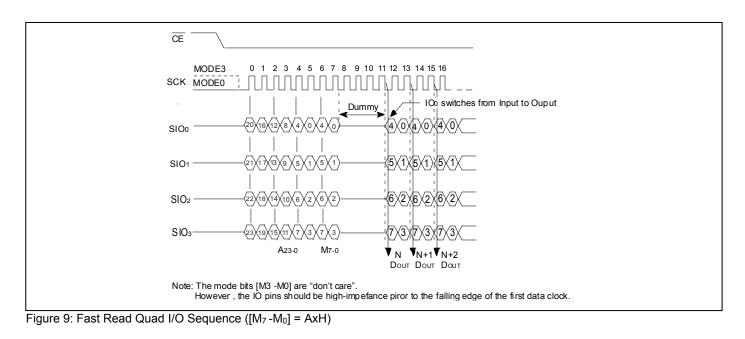

#### Fast Read Quad I/O (50 MHz ~ 100 MHz)

The Fast Read Quad I/O (EBH) instruction is similar to the Fast Read Quad Output (6BH) instruction, but with the capability to input address bits  $[A_{23} - A_0]$  four bits per clock. A Quad Enable (QE) bit of Status Register must be set "1" to enable Quad function.

To set mode bits  $[M_7 - M_0]$  after the address bits  $[A_{23} - A_0]$  can further reduce instruction overhead (See Figure 8). The upper mode bits  $[M_7 - M_4]$  controls the length of next Fast Read Quad I/O instruction with/without the first byte command code (EBH). The lower mode bits  $[M_3 - M_0]$  are "don't care".

If  $[M_7 - M_0] =$  "AxH", the next Fast Read Quad I/O instruction (after  $\overline{CE}$  is raised and the lowered) doesn't need the command code (See Figure 9). This way let the instruction sequence reduce 8 clocks and allows to enter address immediately after  $\overline{CE}$  is asserted low. If  $[M_7 - M_0]$  are the value other than "AxH", the next instruction need the first byte command code, thus returning to normal operation. A Mode Bit Reset (FFH) also can be used to reset mode bits  $[M_7 - M_0]$  before issuing normal instructions.

Figure 8: Fast Read Quad I/O Sequence ([M7-M0] = 0xH or NOT AxH)

Elite Semiconductor Memory Technology Inc.

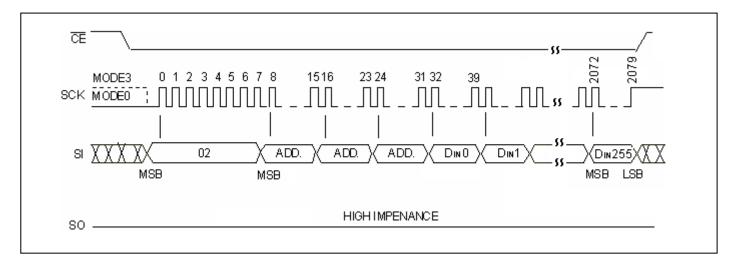

## Page Program (PP)

The Page Program instruction allows many bytes to be programmed in the memory. The bytes must be in the erased state (FFH) when initiating a Program operation. A Page Program instruction applied to a protected memory area will be ignored.

Prior to any Write operation, the Write Enable (WREN) instruction

must be executed.  $\overline{CE}$  must remain active low for the duration of the Page Program instruction. The Page Program instruction is initiated by executing an 8-bit command, 02H, followed by address bits [A<sub>23</sub>-A<sub>0</sub>]. Following the address, at least one byte Data is input (the maximum of input data can be up to 256 bytes). If the 8 least significant address bits [A<sub>7</sub>-A<sub>0</sub>] are not all zero, all transmitted data that goes beyond the end of the current page are programmed from the start address of the same page (from the address whose 8 least significant bits [A<sub>7</sub>-A<sub>0</sub>] are all zero).

If more than 256 bytes Data are sent to the device, previously

latched data are discarded and the last 256 bytes Data are guaranteed to be programmed correctly within the same page. If less than 256 bytes Data are sent to device, they are correctly programmed at the requested addresses without having any effects on the other bytes of the same page.

$\overline{CE}$  must be driven high before the instruction is executed. The user may poll the BUSY bit in the software status register or wait  $T_{PP}$  for the completion of the internal self-timed Page Program operation. While the Page Program cycle is in progress, the Read Status Register instruction may still be accessed for checking the status of the BUSY bit. The BUSY bit is a 1 during the Page Program cycle and becomes a 0 when the cycle is finished and the device is ready to accept other instructions again. After the Page Program cycle has finished, the Write-Enable-Latch (WEL) bit in the Status Register is cleared to 0. See Figure 10 for the Page Program sequence.

Figure 10: Page Program Sequence

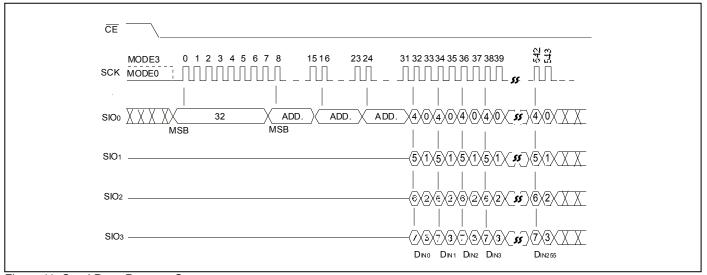

## **Quad Page Program**

The Quad Page Program instruction allows many bytes to be programmed in the memory by using four I/O pins (SIO0, SIO1, SIO2 and SIO3). The instruction can improve programmer performance and the effectiveness of application that have slow clock speed <20MHz. For system with faster clock, this instruction can't provide more actual favors, because the required internal page program time is far more than the time data flows in. Therefore, we suggest that user can execute this command while

the clock speed <20MHz.

Prior to Quad Page Program operation, the Write Enable (WREN) instruction must be executed and Quad Enable (QE) bit of Status Register must be set "1". The other function descriptions are as same as standard Page Program. See Figure 11 for the Quad Page Program sequence.

Figure 11: Quad Page Program Sequence

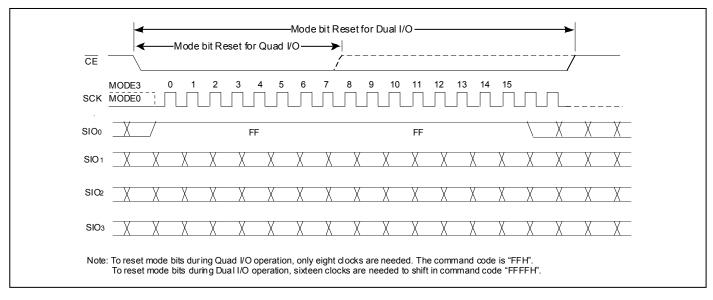

#### Mode Bit Reset

Mode bits  $[M_7 - M_0]$  are issued to further reduce instruction overhead for Fast Read Dual/Quad I/O operation. If  $[M_7 - M_0]$  = "AxH", the next Fast Read Dual/Quad I/O instruction doesn't need the command code.

If the system controller is reset during operation, it will send a standard instruction (such as Read ID) to the Flash memory.

However, the device doesn't have a hardware reset pin, so if  $[M_7-M_0]$  = "AxH", the device will not recognize any standard SPI instruction. After a system reset, it is recommended to issue a Mode Bit Reset instruction first to release the status of  $[M_7-M_0]$  = "AxH" and allow the device to recognize standard SPI instruction. See Figure 16 for the Mode Bit Reset instruction.

Figure 16: Mode Bit Reset Instruction

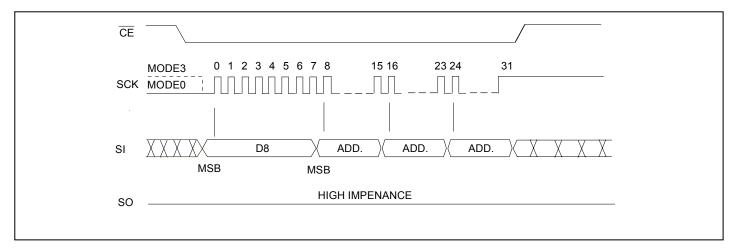

#### 64K Byte Block Erase

The 64K-byte Block Erase instruction clears all bits in the selected block to FFH. A Block Erase instruction applied to a protected memory area will be ignored. Prior to any Write operation, the Write Enable (WREN) instruction must be executed.  $\overline{CE}$  must remain active low for the duration of the any command sequence. The Block Erase instruction is initiated by executing an 8-bit command, D8H, followed by address bits [A<sub>23</sub>

-A<sub>0</sub>]. Address bits [A<sub>MS</sub>-A<sub>16</sub>] (A<sub>MS</sub> = Most Significant address) are used to determine the block address (BA<sub>X</sub>), remaining address bits can be V<sub>IL</sub> or V<sub>IH</sub>.  $\overline{CE}$  must be driven high before the instruction is executed. The user may poll the BUSY bit in the Software Status Register or wait T<sub>BE</sub> for the completion of the internal self-timed Block Erase cycle. See Figure 17 for 64K Byte Block Erase sequence.

Figure 17: 64K-byte Block Erase Sequence

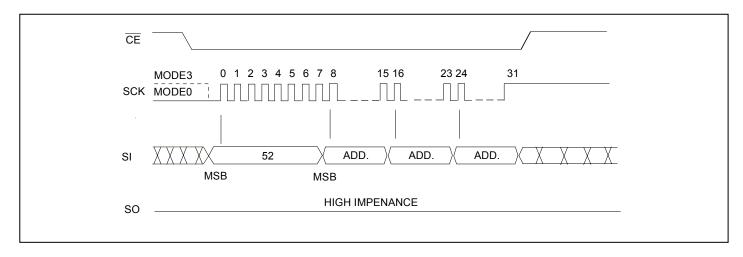

#### 32K Byte Block Erase

The 32K-byte Block Erase instruction clears all bits in the selected block to FFH. A Block Erase instruction applied to a protected memory area will be ignored. Prior to any Write operation, the Write Enable (WREN) instruction must be executed.  $\overline{CE}$  must remain active low for the duration of the any command sequence. The Block Erase instruction is initiated by executing an 8-bit command, 52H, followed by address bits [A<sub>23</sub>

-A<sub>0</sub>]. Address bits [A<sub>MS</sub> -A<sub>15</sub>] (A<sub>MS</sub> = Most Significant address) are used to determine the block address (BA<sub>X</sub>), remaining address bits can be V<sub>IL</sub> or V<sub>IH</sub>.  $\overline{CE}$  must be driven high before the instruction is executed. The user may poll the BUSY bit in the Software Status Register or wait T<sub>BE</sub> for the completion of the internal self-timed Block Erase cycle. See Figure 18 for 32K Byte Block Erase sequence.

Figure 18: 64K-byte Block Erase Sequence

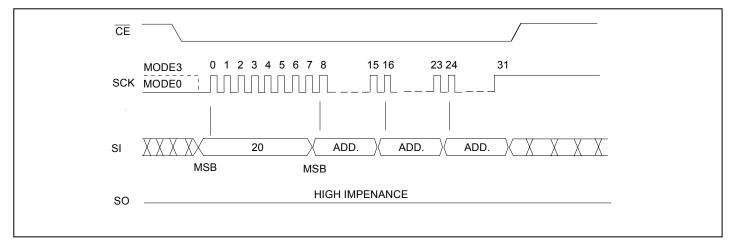

#### **4K Byte Sector Erase**

The Sector Erase instruction clears all bits in the selected sector to FFH. A Sector Erase instruction applied to a protected memory area will be ignored. Prior to any Write operation, the Write Enable (WREN) instruction must be executed.  $\overline{CE}$  must remain active low for the duration of the any command sequence. The Sector Erase instruction is initiated by executing an 8-bit command, 20H, followed by address bits [A<sub>23</sub>-A<sub>0</sub>]. Address bits

Figure 19: 4K-byte Sector Erase Sequence

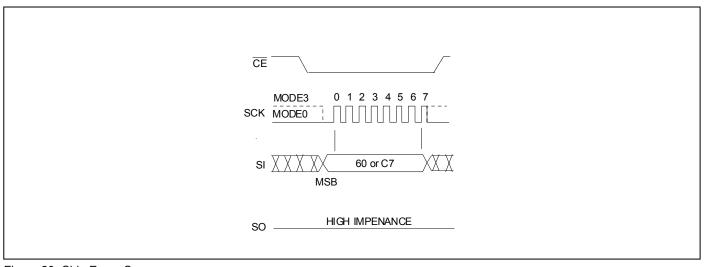

## **Chip Erase**

The Chip Erase instruction clears all bits in the device to FFH. A Chip Erase instruction will be ignored if any of the memory area is protected. Prior to any Write operation, the Write Enable (WREN) instruction must be executed.  $\overline{CE}$  must remain active low for the duration of the Chip Erase instruction sequence. The Chip

Erase instruction is initiated by executing an 8-bit command, 60H or C7H.  $\overline{CE}$  must be driven high before the instruction is executed. The user may poll the BUSY bit in the Software Status Register or wait T<sub>CE</sub> for the completion of the internal self-timed Chip Erase cycle. See Figure 20 for the Chip Erase sequence.

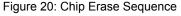

## **Erase Suspend**

The Erase Suspend instruction allows the system to interrupt a Sector or Block Erase operation and then read from any other sector or block. The Write Status Register instruction and Sector / Block Erase instructions are not allowed during suspend. Erase Suspend is valid only during the Sector or Block Erase operation. If written during the Chip Erase or Program operation, the Erase

Suspend instruction is ignored. A maximum of  $T_{SUS}$  is required to suspend the erase operation. The BUSY bit in the Software Status Register will clear to "0" after Erase Suspend. A power-off during the suspend period will reset the device and release the suspend status.

Figure 21: Erase Suspend Instruction

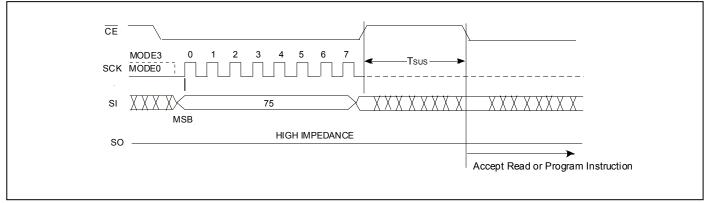

#### **Erase Resume**

The Erase Resume instruction must be written to resume the Sector or Block Erase operation after Erase Suspend. After issued the BUSY bit in the Software Status Register will be set to

"1" and the sector or block will complete the erase operation. Erase Resume instruction will be ignored unless an Erase Suspend operation is active.

Figure 22: Erase Resume Instruction

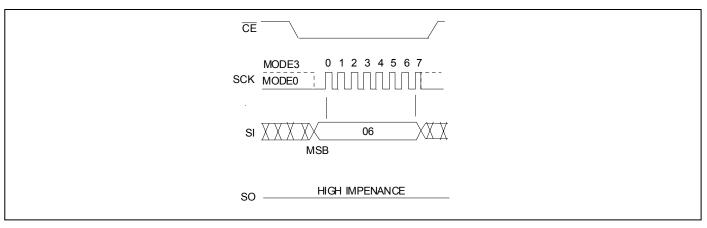

#### Write Enable (WREN)

The Write Enable (WREN) instruction sets the Write-Enable-Latch bit in the Software Status Register to 1 allowing Write operations to occur.

The WREN instruction must be executed prior to any Write

(Program/Erase) operation.  $\overline{CE}$  must be driven high before the WREN instruction is executed.

Figure 23: Write Enable (WREN) Sequence

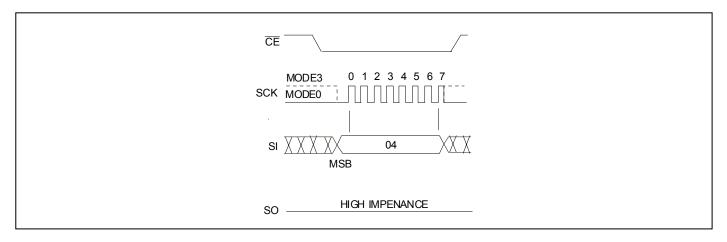

#### Write Disable (WRDI)

The Write Disable (WRDI) instruction resets the Write-Enable-Latch bit to 0 disabling any new Write operations from occurring or exits from OTP mode to normal mode.

$\overline{\text{CE}}$  must be driven high before the WRDI instruction is executed.

Figure 24: Write Disable (WRDI) Sequence

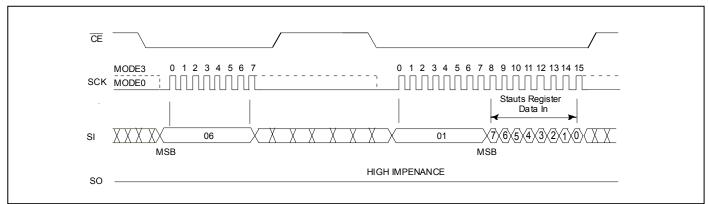

## Write Status Register (WRSR)

The Write Status Register instruction writes new values to the BP3, BP2, BP1, BP0, QE and BPL (Status Register) bits of the status register.  $\overrightarrow{CE}$  must be driven low before the command sequence of the WRSR instruction is entered and driven high before the WRSR instruction is executed.  $\overrightarrow{CE}$  must be driven high after the eighth or sixteenth bit of data that is clocked in. If it is not done, the WRSR instruction will not be issued. If  $\overrightarrow{CE}$  is high after the eighth bits of data, the QE bit will be cleared to 0. See Figure 25 for WREN and WRSR instruction sequences.

Executing the Write Status Register instruction will be ignored when  $\overline{WP}$  is low and BPL bit is set to "1". When the  $\overline{WP}$  is low, the BPL bit can only be set from "0" to "1" to lock down the status register, but cannot be reset from "1" to "0".

When  $\overline{\text{WP}}$  is high, the lock-down function of the BPL bit is disabled and the BPL, BP0, BP1, BP2 and BP3 bits in the status register can all be changed. As long as BPL bit is set to 0 or  $\overline{\text{WP}}$  pin is driven high (V<sub>IH</sub>) prior to the low-to-high transition of the  $\overline{\text{CE}}$  pin at the end of the WRSR instruction, the bits in the status register can all be altered by the WRSR instruction. In this case, a single WRSR instruction can set the BPL bit to "1" to lock down the status register as well as altering the BP0; BP1, BP2 and BP3 bits at the same time. See Table 4 for a summary description of  $\overline{\text{WP}}$  and BPL functions.

Figure 25: Write Enable (WREN) and Write Status Register (WRSR)

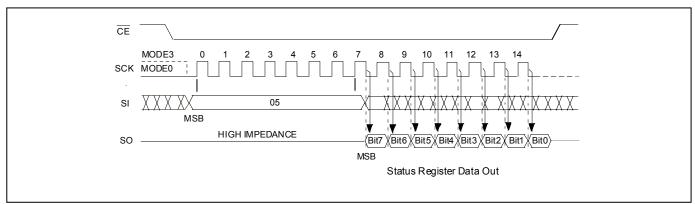

## **Read Status Register (RDSR)**

The Read Status Register (RDSR) instruction allows reading of the status register. The status register may be read at any time even during a Write (Program/Erase) operation. When a Write operation is in progress, the BUSY bit may be checked before sending any new commands to assure that the new commands are properly received by the device.

CE must be driven low before the RDSR instruction is entered and remain low until the status data is read. The RDSR instruction code is "05H" for Status Register. Read Status Register is continuous with ongoing clock cycles until it is terminated by a low to high transition of the  $\overline{CE}$ . See Figure 26 for the RDSR instruction sequence.

Figure 26: Read Status Register (RDSR) Sequence

## Enter OTP Mode (ENSO)

The ENSO (B1H) instruction is for entering the additional 512 bytes secured OTP mode. The additional 512 bytes secured OTP sector is independent from main array, which may use to store unique serial number for system identifier. User must unprotect whole array (BP0=BP1=BP2=BP3=0), prior to any Program operation in OTP sector. After entering the secured OTP mode, only the secured OTP sector can be accessed and user can only follow the Read or Program procedure with OTP address range

(address bits  $[A_{23} - A_9]$  must be "0"). The secured OTP data cannot be updated again once it is lock down or has been programmed. In secured OTP mode, WRSR command will ignore the input data and lock down the secured OTP sector (OTP\_lock bit =1). To exit secured OTP mode, user must execute WRDI command. RES can be used to verify the secured OTP status as shown in Table 6.

Figure 27: Enter OTP Mode (ENSO) Sequence

#### **OTP Sector Address**

| Size      | Address Range     |

|-----------|-------------------|

| 512 bytes | 000000H ~ 0001FFH |