#### **Features**

- 3 identical bidirectional link channels allowing full duplex communication under selectable transmit rate from 1.25 up to 200 Mbit/s in each direction

- A COmmunication Memory Interface (COMI) provides autonomous accesses to a communication memory which are controlled by an arbitration unit, allowing two TSS901E to share one Dual Port Ram without external arbitration

- The scalable databus width (8/16/32 bit) allows flexible integration with any CPU type

- · Little or big endian mode is configurable

- AHOst Control Interface (HOCI) gives read/write accesses to the TSS901E configuration registers and to the DS-link channels for the controlling CPU

- Device control via one of the three links allows its use in systems without a local controller

- Link disconnect detection and parity check at token (data and control) level; possible checksum generation for packet level check

- Power saving mode relying on automatic transmit rate reduction

- A user's manual of the TSS901E (also called SMCS332) is available at: http://www.spacewire.esa.int/tech/spacewire/products/index.htm

- Designed on Atmel MG1140E matrix and packaged into MQFPL196

The TSS901E provides an interface between a Data-Strobe link - according to the IEEE Std 1355-1995 specification carrying a simple interprocessor communication protocol - and a data processing node consisting of a CPU and a communication and data memory.

The TSS901E offers hardware supported execution of the major parts of the interprocessor communication protocol: data transfer between two nodes of a multi-processor system is performed with minimal host CPU intervention. The TSS901E can execute simple commands to provide basic features for system control functions; a provision of fault tolerant features exists as well.

Although the TSS901E initial exploitation is for use in multi-processor systems where the high speed links standardisation is an important issue and where reliability is a requirement, it could be used in applications such as heterogeneous systems or modules without any communication feature like special image compression chips, some signal processors, application specific programmable logic or mass memory.

The TSS901E may also be used in single board systems where standardised high speed interfaces are needed and systems containing "non-intelligent" modules such as A/D-converter or sensor interfaces which can be assembled with the TSS901E thanks to the "control by link" feature.

Triple Point to Point IEEE 1355 High Speed Controller

TSS901E

#### Introduction

The TSS901E provides an interface between a Data-Strobe link according to the IEEE Std 1355-1995 specification carrying the simple interprocessor communication protocol <sup>(1)</sup> and a data processing node consisting of a CPU and communication and data memory. The TSS901E provides HW supported execution of the major parts of the simple interprocessor communication protocol, particularly:

- transfer of data between two modes of a multi-processor system with minimal host CPU intervention.

- execution of simple commands to provide basic features for system control functions,

- · provision of fault tolerant features.

However, with disabling of features such as the protocol handling or with reduction of the transmit rate (TSS901E automatically reduces transmit rate for sending null tokens) also low power usage is supported.

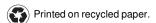

Figure 1. TSS901E Block Diagram

Target applications are heterogeneous multi-processor systems supported by scalable interfaces including the little/big endian swapping. The TSS901E connects modules with different processors (e.g. TSC21020F, ERC32, TSC695E and others). Any kind of network topology could be realized through the high speed point-to-point IEEE1355-links (see chapter Applications).

#### Interfaces

The TSS901E consists of the following blocks (See Figure 1):

1. Rastetter P. et.al., Simple Interprocessor Communication Protocol Specification, DIPSAPII-DAS-31-01, Issue 3, 08.10.96, also available on the same web site as the users guide.

bidirectional link channels, all comprising the DS-link macro cell (DSM), receive and transmit sections (each including FIFOs) and a protocol processing unit (PPU). Each channel allows full duplex communication up to 200 Mbit/s in each direction. With protocol command execution a higher level of communication is supported. Link disconnect detection and parity check at token level are performed. A checksum generation for a check at packet level can be enabled.

The transmit rate is selectable between 1.25 and 200 Mbit/s; an additional power saving mode can be enabled, where the transmit rate is automatically reduced to 10 Mbit/s when only Null tokens are being transmitted over the link. The default transmit rate is 10 Mbit/s. For special applications the data transmit rate can be programmed to values even below 10 Mbit/s; the lowest possible (to be within the IEEE-1355 specification) transmit rate is 1.25 Mbit/s (the next values are 2.5 and 5 Mbit/s).

Communication Memory Interface (COMI) performs autonomous accesses to the

communication memory of the module to store data received via the links or to read data to

be transmitted via the links. The COMI consists of individual memory address generators for

the receive and transmit direction of every DS link channel. The access to the memory is

controlled via an arbitration unit providing a fair arbitration scheme. Two TSS901E can share

one DPRAM without external arbitration.

The data bus width is scalable (8/16/32 bit) to allow flexible integration with any CPU type. Operation in little or big endian mode is configurable through internal registers. The COMI address bus is 16 bit wide allowing direct access of up to 64K words of the DPRAM. Two chip select signals are provided to allow splitting of the 64k address space in two memory banks.

Host Control Interface (HOCI) gives read and write access to the TSS901E configuration registers and to the DS-link channels for the controlling CPU. Viewed from the CPU, the interface behaves like a peripheral that generates acknowledges to synchronize the data transfers and which is located somewhere in the CPU's address space.

Packets can be transmitted or received directly via the HOCI. In this case the Communication Memory (DPRAM) is not strictly needed. However, in this case the packet size should be limited to avoid frequent CPU interaction.

The data bus width is scalable (8/16/32 bit) to allow flexible integration with any CPU type. The byte alignment can be configured for little or big endian mode through an external pin.

Additionally the HOCI contains the interrupt signalling capability of the TSS901E by providing an interrupt output, the interrupt status register and interrupt mask register to the local CPU.

A special pin is provided to select between control of the TSS901E by HOCl or by link. If control by link is enabled, the host data bus functions as a 32-bit general purpose interface (GPIO).

- **Protocol Command Interface (PRCI)** that collects the decoded commands from all PPUs and forwards them to external circuitry via 5 special pins.

- JTAG Test Interface that represents the boundary scan testing provisions specified by IEEE Standard 1149.1 of the Joint Testing Action Group (JTAG). The TSS901E' test access port and on-chip circuitry is fully compliant with the IEEE 1149.1 specification. The test access port enables boundary scan testing of circuitry connected to the TSS901E I/O pins.

### **Operation Modes**

According to the different protocol formats expected for the operation of the TSS901E, two major operation modes are implemented into the TSS901E. The operation modes are chosen individually for each link channel by setting the respective configuration registers via the HOCI or via the link.

• Transparent Mode (default after reset): This mode allows complete transparent data transfer between two nodes without performing any interpretation of the databytes and without generating any acknowledges. It is completely up to the host CPU to interpret the received data and to generate acknowledges if required.

The TSS901E accepts EOP1 and EOP2 control tokens as packet delimiters and generates autonomously EOP1/EOP2 (as configured) markers after each end of a transmission packet.

This mode also includes as a special submode:

- Wormhole routing: This mode allows hardware routing of packets by the TSS901E.

- Simple Interprocessor Communication (SIC) Protocol Mode: This mode executes the simple interprocessor communication protocol as described in the protocol specification <sup>(1)</sup>. The following capabilities of the protocol are implemented into the TSS901E:

- interpretation of the first 4 data tokens as the header bytes of the protocol

- autonomous execution of the simple control commands as described in the protocol specification<sup>(1)</sup>

- autonomous acknowledgement of received packets if configured

In transmit direction no interpretation of the data is performed. This means that for transmit packets, the four header bytes must be generated by the host CPU and must be available as the first data read from the communication memory. EOP1/EOP2 control tokens are automatically inserted by the TSS901E when one configured transfer from the communication memory has finished.

# TSS901E Control by Link

A feature of the TSS901E is the possibility to control the TSS901E not only via HOCI but via one of the three links. This allows to use the TSS901E in systems without a local controller ( $\mu$ Controller, FPGA etc.). Since the HOCI is no longer used in this operation mode, it is instead available as a set of general purpose I/O (GPIO) lines.

### **Wormhole Routing**

The TSS901E introduces a wormhole routing function similar to the routing implemented in the ST-Microelectronics C104 routing switch. Each of the three links and the TSS901E itself can be assigned an eight bit address. When routing is enabled in the TSS901E, the first byte of a packet will be interpreted as the address destination byte, analysed and removed from the packet (header deletion). If this address matches one of the two other link addresses or the TSS901E address assigned previously, the packet will be automatically forwarded to this link or the FIFO of the TSS901E. If the header byte does not match a link address, the packet will be written to the internal FIFO as well and an error interrupt (maskable) will be raised.

# PPU Functional Description

Since the Protocol Processing Unit (PPU) determines a major part of the TSS901E functionality, the principal blocks of the PPU and their function are described here. This functionality is provided for every DS link channel of the TSS901E.

- Protocol Execution Unit: This unit serves as the main controller of the PPU block. It

receives the tokens from the DS macrocell and interprets (in protocol mode) the four header

data characters received after an EOP1/EOP2 control character. If the address field

matches the link channel address and the command field contains a valid command then

forwarding of data into the receive FIFO is enabled. If the command field contains a "simple

control command" then the execution request is forwarded to the command execution unit.

- The protocol execution unit also enables forwarding of header data characters to the acknowledge generator and provides an error signal in case of address mismatch, wrong commands or disabled safety critical "simple control commands".

- The protocol execution unit is disabled in "transparent" or "wormhole routing" operation mode.

- Receive, Transmit, Acknowledge: The transmit and receive FIFOs decouple the DS link related operations from the TSS901E related operations in all modes and such allows to keep the speed of the different units even when the source or sink of data is temporarily blocked.

- In the protocol mode a further FIFO (acknowledge FIFO) is used to decouple sending of acknowledges from receiving new data when the transmit path is currently occupied by a running packet transmission.

- Command Execution Unit: This unit performs activating resp. deactivating of the CPU

reset and the specific external signals and provides the capability to reset one or all links

inside the TSS901E, all actions requested by the decoded commands from the protocol

execution unit.

The unit contains a register controlling the enable/disable state of safety critical commands which is set into the 'enable' state upon command request and which is reset after a safety critical command has been executed.

The CPU reset and the specific external signals are forwarded to the Protocol Command Interface (PRCI).

#### **Fault Tolerance**

The IEEE Std 1355-1995 specifies low level checks as link disconnect detection and parity check at token level. The TSS901E provides, through the Protocol Processing Unit, features to reset a link or all links inside the TSS901E, to reset the local CPU or to send special signals to the CPU commanded via the links.

Additionally it is possible to enable a checksum coder/decoder to have fault detection capabilities at packet level.

#### **Applications**

The TSS901E is a very high speed, scalable link-interface chip with fault tolerance features. The initial exploitation is for use in multi-processor systems where the standardisation or the high speed of the links is an important issue and where reliability is a requirement. Further application examples are heterogeneous systems or modules without any communication features as special image compression chips, certain signal processors (TSC21020F, ERC32, ...), application specific programmable logic or mass memory.

The TSS901E could also be used for single board systems where standardised high speed interfaces are needed. Even "non-intelligent" modules such as A/D-converter or sensor interfaces can be assembled with the TSS901E because of the "control by link" feature. The complete control of the TSS901E can be done via link from a central controller-node.

# **Register Set**

This chapter describes the TSS901E registers which can be read or written by the HOCI or via the link (in case the "control by link" is enabled) to control TSS901E operations. All TSS901E control operations are performed by writes or reads of the respective registers. Most of the control operations are obvious from the content of the registers.

#### General Conventions:

- bit 0 (D0) = least significant bit,

- bit 7 (D7) = most significant bit (or bit 15 resp. bit 31)

- D x:0 means data bit x until bit 0.

### Access by HOCI: HOCI Data Transfer

Big/Little endian selection of the HOCI is done using a special pin (HOSTBIGE) of the TSS901E. By connecting this pin to either Vcc or GND the HOCI is configured to be in little or big endian mode as follows:

When Signal HOSTBIGE = '0' (GND), the HOCI data port is in little endian mode.

When Signal HOSTBIGE = '1' (Vcc), the HOCI data port is in big endian mode.

#### Little endian mode selected:

- 8 bit data port (default after reset)

- register byte 0 is connected with pin HDATA0 HDATA7

- 16 bit data port

- register byte 0 is connected with pin HDATA0 HDATA7

- register byte 1 is connected with pin HDATA8 HDATA15

- 32 bit data port

- register byte 0 is connected with pin HDATA0 HDATA7

- register byte 1 is connected with pin HDATA8 HDATA15

- register byte 2 is connected with pin HDATA16 HDATA23

- register byte 3 is connected with pin HDATA24 HDATA31

#### Big endian mode selected:

- 8 bit data port (default after reset)

- register byte 0 is connected with pin HDATA24 HDATA31

- 16 bit data port

- register byte 0 is connected with pin HDATA24 HDATA31

- register byte 1 is connected with pin HDATA16 HDATA23

- 32 bit data port

- register byte 0 is connected with pin HDATA24 HDATA31

- register byte 1 is connected with pin HDATA16 HDATA23

- register byte 2 is connected with pin HDATA8 HDATA15

- register byte 3 is connected with pin HDATA0 HDATA7

The registers of the TSS901E are 1, 2 or 4 Bytes wide. That means, if the HOCl data port is in 8 bit mode, 4 read or write accesses are necessary to access a 4 Byte register (e. g. the interrupt mask register). In 16/32 bit mode the data bits 31 - 8 are '0' if an 8 bit register is read.

# **Register Address Map**

The addresses of the TSS901E registers are directly mapped with pins HADR7 - 0. The tables below shows the addresses of all the TSS901E registers depending on the HOCI port width.

# TSS901E status and control registers

| Port W | Port Width / Address (hex) |                      |            |                                                       |                   |        |

|--------|----------------------------|----------------------|------------|-------------------------------------------------------|-------------------|--------|

| 32     | 16                         | 8                    | Register   | Function                                              | Reset Value (hex) | Access |

| 00     | 00                         | 00                   | SICR       | TSS901E Interface Control Register                    | 00                | r/w    |

| 01     | 01                         | 01                   | TRS_CTRL   | Transmit-Speed-Base Register                          | 0A                | r/w    |

| 02     | 02                         | 02                   | ROUTE_CTRL | Routing Enable / Status Register                      | 00                | r      |

| 03     | 03                         | 03                   |            | reserved                                              | 00                |        |

| 04     | 04<br>06                   | 04<br>05<br>06<br>07 | ISR        | ISR Interrupt Status Register                         |                   | ro     |

| 08     | 08<br>0A                   | 08<br>09<br>0A<br>0B | IMR        | Interrupt Mask Register                               | 00000000          | r/w    |

| 0C     | 0C                         | 0C                   | COMI_CS0R  | COMI Chip Select 0 upper address boundary<br>Register | FF                | r/w    |

| 0D     | 0D                         | 0D                   |            | reserved                                              |                   |        |

| 0E     | 0E                         | 0E                   | COMI_ACR   | COMI_ACR COMI Arbitration Control Register 08         |                   | r/w    |

| 0F     | 0F                         | 0F                   | PRCIR      | PRCI Register                                         | 00                | r / w  |

# TSS901E channel 1 status and control registers

| Port Width / Address<br>(hex) |    | ldress |              |                                    | Reset Value |        |

|-------------------------------|----|--------|--------------|------------------------------------|-------------|--------|

| 32                            | 16 | 8      | Register     | Function                           | (hex)       | Access |

| 10                            | 10 | 10     | CH1_DSM_MODR | channel 1 DSM mode Register        | 03          | r/w    |

| 11                            | 11 | 11     | CH1_DSM_CMDR | channel 1 DSM command Register     | 00          | r/w    |

| 12                            | 12 | 12     | CH1_DSM_STAR | channel 1 DSM status Register      | 00          | r / w  |

| 13                            | 13 | 13     | CH1_DSM_TSTR | channel 1 DSM test Register        | 00          | r/w    |

| 14                            | 14 | 14     | CH1_ADDR     | channel 1 address Register         | 00          | r/w    |

| 15                            | 15 | 15     | CH1_RT_ADDR  | channel 1 Route Address Register   | 00          | r / w  |

| 16                            | 16 | 16     | CH1_PR_STAR  | channel 1 Protocol Status Register | 04          | r/w    |

| 17                            | 17 | 17     |              | reserved                           |             |        |

| 18                            | 18 | 18     | CH1_CNTRL1   | channel 1 control Register 1       | 00          | r/w    |

| Port Width / Address<br>(hex) |    | dress    |             |                                             | Reset Value |        |

|-------------------------------|----|----------|-------------|---------------------------------------------|-------------|--------|

| 32                            | 16 | 8        | Register    | Function                                    | (hex)       | Access |

| 19                            | 19 | 19       | CH1_CNTRL2  | channel 1 control Register 2                | 00          | r/w    |

| 1A                            | 1A | 1A       | CH1_HTID    | channel 1 Header Transaction ID byte        | 00          | ro     |

| 1B                            | 1B | 1B       | CH1_HCNTRL  | channel 1 Header control byte               | 00          | ro     |

| 1C                            | 1C | 1C       | CH1_ESR1    | channel 1 detailed error source register 1  | 00          | r/w    |

| 1D                            | 1D | 1D       | CH1_ESR2    | channel 1 detailed error source register 2  | 00          | r/w    |

| 1E                            | 1E | 1E       |             | reserved                                    | 00          |        |

| 1F                            | 1F | 1F       | CH1_COMICFG | channel 1 COMI configuration register       | 00          | r/w    |

| 20                            | 20 | 20<br>21 | CH1_TX_SAR  | channel 1 transmit Start Address Register   | 0000        | r/w    |

| 22                            | 22 | 22<br>23 | CH1_TX_EAR  | channel 1 transmit End Address Register     | 0000        | r/w    |

| 24                            | 24 | 24<br>25 | CH1_TX_CAR  | channel 1 transmit Current Address Register | 0000        | ro     |

| 26                            | 26 | 26       | CH1_TX_FIFO | channel 1 transmit FIFO                     |             | wo     |

| 27                            | 27 | 27       | CH1_TX_EOPB | channel 1 transmit EOP Bit Register         |             | wo     |

| 28                            | 28 | 28<br>29 | CH1_RX_SAR  | channel 1 receive Start Address Register    | 0000        | r / w  |

| 2A                            | 2A | 2A<br>2B | CH1_RX_EAR  | channel 1 receive End Address Register      | 0000        | r/w    |

| 2C                            | 2C | 2C<br>2D | CH1_RX_CAR  | channel 1 receive Current Address Register  | 0000        | ro     |

| 2E                            | 2E | 2E       | CH1_RX_FIFO | channel 1 receive FIFO                      | xxxxxxx     | ro     |

| 2F                            | 2F | 2F       | CH1_STAR    | channel 1 Status Register                   | 01          | ro     |

# TSS901E channel 2 status and control registers

| Port Width / Address<br>(hex) |    | ldress |              |                                    | Reset Value |        |

|-------------------------------|----|--------|--------------|------------------------------------|-------------|--------|

| 32                            | 16 | 8      | Register     | Function                           | (hex)       | Access |

| 30                            | 30 | 30     | CH2_DSM_MODR | channel 2 DSM mode Register        | 03          | r/w    |

| 31                            | 31 | 31     | CH2_DSM_CMDR | channel 2 DSM command Register     | 00          | r / w  |

| 32                            | 32 | 32     | CH2_DSM_STAR | channel 2 DSM status Register      | 00          | r / w  |

| 33                            | 33 | 33     | CH2_DSM_TSTR | channel 2 DSM test Register        | 00          | r/w    |

| 34                            | 34 | 34     | CH2_ADDR     | channel 2 address Register         | 00          | r / w  |

| 35                            | 35 | 35     | CH2_RT_ADDR  | channel 2 Route Address Register   | 00          | r/w    |

| 36                            | 36 | 36     | CH2_PR_STAR  | channel 2 Protocol Status Register | 04          | r/w    |

| Port Width / Address<br>(hex) |    |          |             |                                             |                   |        |

|-------------------------------|----|----------|-------------|---------------------------------------------|-------------------|--------|

| 32                            | 16 | 8        | Register    | Function                                    | Reset Value (hex) | Access |

| 37                            | 37 | 37       |             | reserved                                    | 00                |        |

| 38                            | 38 | 38       | CH2_CNTRL1  | channel 2 control Register 1                | 00                | r/w    |

| 39                            | 39 | 39       | CH2_CNTRL2  | channel 2 control Register 2                | 00                | r / w  |

| ЗА                            | ЗА | ЗА       | CH2_HTID    | channel 2 Header Transaction ID byte        | 00                | ro     |

| 3В                            | 3B | 3B       | CH2_HCNTRL  | channel 2 Header control byte               | 00                | ro     |

| 3C                            | 3C | 3C       | CH2_ESR1    | channel 2 detailed error source register 1  | 00                | r / w  |

| 3D                            | 3D | 3D       | CH2_ESR2    | channel 2 detailed error source register 2  | 00                | r / w  |

| 3E                            | 3E | 3E       |             | reserved                                    | 00                |        |

| 3F                            | 3F | 3F       | CH2_COMICFG | channel 2 COMI configuration register       | 00                | r / w  |

| 40                            | 40 | 40<br>41 | CH2_TX_SAR  | channel 2 transmit Start Address Register   | 00                | r/w    |

| 42                            | 42 | 42<br>43 | CH2_TX_EAR  | channel 2 transmit End Address Register     | 00                | r/w    |

| 44                            | 44 | 44<br>45 | CH2_TX_CAR  | channel 2 transmit Current Address Register | 00                | ro     |

| 46                            | 46 | 46       | CH2_TX_FIFO | channel 2 transmit FIFO                     | 00                | wo     |

| 47                            | 47 | 47       | CH2_TX_EOPB | channel 2 transmit EOP Bit Register         | 00                | wo     |

| 48                            | 48 | 48<br>49 | CH2_RX_SAR  | channel 2 receive Start Address Register    | 00                | r/w    |

| 4A                            | 4A | 4A<br>4B | CH2_RX_EAR  | channel 2 receive End Address Register      | 00                | r/w    |

| 4C                            | 4C | 4C<br>4D | CH2_RX_CAR  | channel 2 receive Current Address Register  | 00                | ro     |

| 4E                            | 4E | 4E       | CH2_RX_FIFO | channel 2 receive FIFO                      | xxxxxxx           | ro     |

| 4F                            | 4F | 4F       | CH2_STAR    | channel 2 Status Register                   | 01                | ro     |

## TSS901E channel 3 status and control registers

| Port W | Port Width / Address<br>(hex) |    |              |                                | Reset Value |        |

|--------|-------------------------------|----|--------------|--------------------------------|-------------|--------|

| 32     | 16                            | 8  | Register     | Function                       | (hex)       | Access |

| 50     | 50                            | 50 | CH3_DSM_MODR | channel 3 DSM mode Register    | 03          | r/w    |

| 51     | 51                            | 51 | CH3_DSM_CMDR | channel 3 DSM command Register | 00          | r/w    |

| 52     | 52                            | 52 | CH3_DSM_STAR | channel 3 DSM status Register  | 00          | r/w    |

| 53     | 53                            | 53 | CH3_DSM_TSTR | channel 3 DSM test Register    | 00          | r/w    |

| Port Width / Address (hex) |    |          |             | Reset Value                                 |         |        |

|----------------------------|----|----------|-------------|---------------------------------------------|---------|--------|

| 32                         | 16 | 8        | Register    | Function                                    | (hex)   | Access |

| 54                         | 54 | 54       | CH3_ADDR    | channel 3 address Register                  | 00      | r/w    |

| 55                         | 55 | 55       | CH3_RT_ADDR | channel 3 Route address Register            | 00      | r/w    |

| 56                         | 56 | 56       | CH3PR_STAR  | channel 3 Protocol Status Register          | 04      | r/w    |

| 57                         | 57 | 57       |             | reserved                                    | 00      |        |

| 58                         | 58 | 58       | CH3_CNTRL1  | channel 3 control Register 1                | 00      | r/w    |

| 59                         | 59 | 59       | CH3_CNTRL2  | channel 3 control Register 2                | 00      | r/w    |

| 5A                         | 5A | 5A       | CH3_HTID    | channel 3 Header Transaction ID byte        | 00      | ro     |

| 5B                         | 5B | 5B       | CH3_HCNTRL  | channel 3 Header control byte               | 00      | ro     |

| 5C                         | 5C | 5C       | CH3_ESR1    | channel 3 detailed error source register 1  | 00      | r/w    |

| 5D                         | 5D | 5D       | CH3_ESR2    | channel 3 detailed error source register 2  | 00      | r/w    |

| 5E                         | 5E | 5E       |             | reserved                                    | 00      |        |

| 5F                         | 5F | 5F       | CH3_COMICFG | channel 3 COMI configuration register       | 00      | r/w    |

| 60                         | 60 | 60<br>61 | CH3_TX_SAR  | channel 3 transmit Start Address Register   | 00      | r/w    |

| 62                         | 62 | 62<br>63 | CH3_TX_EAR  | channel 3 transmit End Address Register     | 00      | r/w    |

| 64                         | 64 | 64<br>65 | CH3_TX_CAR  | channel 3 transmit Current Address Register | 00      | ro     |

| 66                         | 66 | 66       | CH3_TX_FIFO | channel 3 transmit FIFO                     | 00      | wo     |

| 67                         | 67 | 67       | CH3_TX_EOPB | channel 3 transmit EOP Bit Register         | 00      | wo     |

| 68                         | 68 | 68<br>69 | CH3_RX_SAR  | channel 3 receive Start Address Register    | 00      | r/w    |

| 6A                         | 6A | 6A<br>6B | CH3_RX_EAR  | channel 3 receive End Address Register      | 00      | r/w    |

| 6C                         | 6C | 6C<br>6D | CH3_RX_CAR  | channel 3 receive Current Address Register  | 00      | ro     |

| 6E                         | 6E | 6E       | CH3_RX_FIFO | channel 3 receive FIFO                      | xxxxxxx | ro     |

| 6F                         | 6F | 6F       | CH3_STAR    | channel 3 Status Register                   | 01      | ro     |

### TSS901E GPIO Control Registers

These registers are only enabled when the TSS901E is configured for "control by link" using the 'BOOTLINK' pin.

| Port Width / Address (hex) |    |    |            |                           |                   |        |  |  | Decet Value |  |

|----------------------------|----|----|------------|---------------------------|-------------------|--------|--|--|-------------|--|

| 32                         | 16 | 8  | Register   | Function                  | Reset Value (hex) | Access |  |  |             |  |

|                            |    | 70 | GPIO_DIR0  | GPIO direction register 0 | 00                | r/w    |  |  |             |  |

|                            |    | 71 | GPIO_DIR1  | GPIO direction register 1 | 00                | r / w  |  |  |             |  |

|                            |    | 72 | GPIO_DIR2  | GPIO direction register 2 | 00                | r / w  |  |  |             |  |

|                            |    | 73 | GPIO_DIR3  | GPIO direction register 3 | 00                | r / w  |  |  |             |  |

|                            |    | 74 | GPIO_DATA0 | GPIO data register 0      | 00                | r/w    |  |  |             |  |

|                            |    | 75 | GPIO_DATA1 | GPIO data register 1      | 00                | r / w  |  |  |             |  |

|                            |    | 76 | GPIO_DATA2 | GPIO data register 2      | 00                | r / w  |  |  |             |  |

|                            |    | 77 | GPIO DATA3 | GPIO data register 3      | 00                | r/w    |  |  |             |  |

# Signal Description

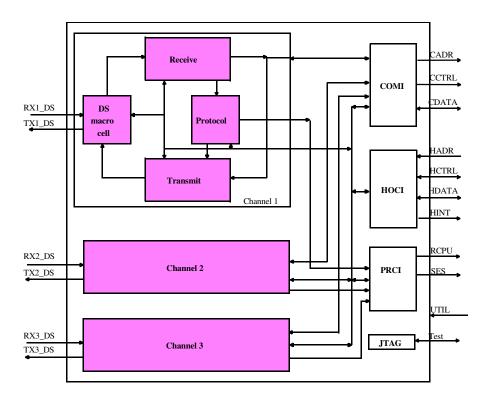

The Figure below shows the TSS901E (also called SMCS332) embedded in a typical module environment:

This section describes the pins of the TSS901E. Groups of pins represent busses where the highest number is the MSB.

O = Output; I = Input; Z = High Impedance; (\*) = active low signal O/Z = if using a configuration with two TSS901Es these signals can directly be connected together (WIROR)

| Signal Name         | Туре | Function                                                                                                                                     | max. output<br>current [mA] | load [pF] |

|---------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------|

| HSEL*               | I    | Select host interface                                                                                                                        |                             |           |

| HRD*                | I    | host interface read strobe                                                                                                                   |                             |           |

| HWR*                | I    | host interface write strobe                                                                                                                  |                             |           |

| HADR(7:0)           | I    | TSS901E register address lines. This address lines will be used to access (address) the TSS901E registers.                                   |                             |           |

| HDATA(31:0)         | IO/Z | TSS901E data                                                                                                                                 | 3                           | 50        |

| HACK                | O/Z  | host acknowledge. TSS901E deasserts this output to add wait states to a TSS901E access. After TSS901E is ready this output will be asserted. | 3                           | 50        |

| HINTR*              | O/Z  | host interrupt request line                                                                                                                  | 3                           | 50        |

| TSS901EADR(3:0<br>) | I    | TSS901E Address. The binary value of this lines will be compared with the value of the TSS901E ID lines.                                     |                             |           |

| TSS901EID(3:0)      | ı    | TSS901E ID lines: offers possibility to use sixteen TSS901E within one HSEL*                                                                 |                             |           |

| Signal Name  | Туре | Function                                                                                                                            | max. output<br>current [mA] | load [pF] |

|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------|

| HOSTBIGE     | I    | 1: host I/F Big Endian<br>0: host I/F Little Endian                                                                                 |                             |           |

| BOOTLINK     | I    | 1: control by link 0: control by host                                                                                               |                             |           |

| CMCS(1:0)*   | O/Z  | Communication memory select lines. These pins are asserted as chip selects for the corresponding banks of the communication memory. | 8                           | 25        |

| CMRD*        | O/Z  | Communication memory read strobe. This pin is asserted when the TSS901E reads data from memory.                                     | 8                           | 25        |

| CMWR*        | O/Z  | Communication memory write strobe. This pin is asserted when the TSS901E writes to data memory.                                     | 8                           | 25        |

| CMADR(15:0)  | O/Z  | Communication memory address. The TSS901E outputs an address on these pins.                                                         | 8                           | 25        |

| CMDATA(31:0) | IOZ  | Communication memory data. The TSS901E inputs and outputs data from and to com. memory on these pins.                               | 3                           | 50        |

| COCI         | I    | Communication interface 'occupied' input signal                                                                                     | 3                           | 50        |

| COCO         | O/Z  | Communication interface 'occupied' output signal                                                                                    |                             |           |

| CAM          | I    | Communication interface arbitration master input signal 1: master 0: slave                                                          |                             |           |

| CPUR*        | O/Z  | CPU Reset Signal                                                                                                                    | 3                           | 50        |

| SES(3:0)*    | O/Z  | Specific External Signals                                                                                                           | 3                           | 50        |

| LDI1         | ı    | Link Data Input channel 1                                                                                                           |                             |           |

| LSI1         | ı    | Link Strobe Input channel 1                                                                                                         |                             |           |

| LDO1         | O/Z  | Link Data Output channel 1                                                                                                          | 12                          | 25        |

| LSO1         | O/Z  | Link Strobe Output channel 1                                                                                                        | 12                          | 25        |

| LEN1         | O/Z  | Link Enable Out (for external drivers)                                                                                              | 3                           | 50        |

| LDI2         | 1    | Link Data Input channel 2                                                                                                           |                             |           |

| LSI2         | I    | Link Strobe Input channel 2                                                                                                         |                             |           |

| LDO2         | O/Z  | Link Data Output channel 2                                                                                                          | 12                          | 25        |

| LSO2         | O/Z  | Link Strobe Output channel 2                                                                                                        | 12                          | 25        |

| LEN2         | O/Z  | Link Enable Out (for external drivers)                                                                                              | 3                           | 50        |

| LDI3         | I    | Link Data Input channel 3                                                                                                           |                             |           |

| LSI3         | I    | Link Strobe Input channel 3                                                                                                         |                             |           |

| LDO3         | O/Z  | Link Data Output channel 3                                                                                                          | 12                          | 25        |

| LSO3         | O/Z  | Link Strobe Output channel 3                                                                                                        | 12                          | 25        |

| LEN3         | O/Z  | Link Enable Out (for external drivers)                                                                                              | 3                           | 50        |

| TRST*        | I    | Test Reset. Resets the test state machine.                                                                                          |                             |           |

| Signal Name | Туре | Function                                                                                                                                                                           | max. output<br>current [mA] | load [pF] |

|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------|

| TCK         | I    | Test Clock. Provides an asynchronous clock for JTAG boundary scan.                                                                                                                 |                             |           |

| TMS         | I    | Test Mode Select. Used to control the test state machine.                                                                                                                          |                             |           |

| TDI         | I    | Test Data Input. Provides serial data for the boundary scan logic.                                                                                                                 |                             |           |

| TDO         | O/Z  | Test Data ( $t_{CK}^{}$ it. Serial scan $out_{CK}^{}$ if the boundary scan path.                                                                                                   | 3                           | 50        |

| RESET*      | ı    | TSS901E Reset. Sets the TSS901E to a known state. This input must be asserted (low) at power-up. The minimum width of RESET low is 5 cycles of CLK10 in parallel with CLK running. |                             |           |

| CLK         | I    | External clock input to TSS901E (max. 25 Mhz). Must be derived from RAM access time.                                                                                               |                             |           |

| CLK10       | I    | External clock input to TSS901E DS-links (application specific, nominal 10 Mhz). Used to generate to transmission speed and link disconnect timeout.                               |                             |           |

| PLLOUT      | 0    | Output of internal PLL. Used to connect a network of external RC devices.                                                                                                          |                             |           |

| VCC         |      | Power Supply                                                                                                                                                                       |                             |           |

| GND         |      | Ground                                                                                                                                                                             |                             |           |

# **Electrical Characteristics**

The following data is provided for information only; for the guaranteed values, refer to Atmel procurement specification.

# **Absolute Maximum Ratings**

| Parameter                             | Symbol           | Value                               | Unit |

|---------------------------------------|------------------|-------------------------------------|------|

| Supply Voltage                        | V <sub>CC</sub>  | -0.5 to +7                          | V    |

| I/O Voltage                           |                  | -0.5 to VCC + 0.5                   | V    |

| Operating Temperature Range (Ambient) | T <sub>A</sub>   | -55 to +125                         | ℃    |

| Junction Temperature                  | TJ               | T <sub>J</sub> < T <sub>A</sub> +20 | ℃    |

| Storage Temperature Range             | T <sub>stg</sub> | -65 to +150                         | ℃    |

Stresses above those listed may cause permanent damage to the device.

### **DC Electrical Characteristics**

Specified at  $V_{CC}$  = + 5 V ± 10% (TSS901E will only work with 5V)

| Parameter                    | Symbol          | Min. | Max.       | Unit     | Conditions                         |

|------------------------------|-----------------|------|------------|----------|------------------------------------|

| Operating Voltage            | V <sub>CC</sub> | 4.5  | 5.5        | ٧        |                                    |

| Input HIGH Voltage           | V <sub>IH</sub> | 2.0  |            | V        |                                    |

| Input LOW Voltage            | V <sub>IL</sub> |      | 0.8        | ٧        |                                    |

| Output HIGH Voltage          | V <sub>OH</sub> | 2.4  |            | V        | max. output current                |

| Output LOW Voltage           | V <sub>OL</sub> |      | 0.4        | ٧        | max. output current                |

| Output Short circuit current | l <sub>os</sub> |      | 160<br>130 | mA<br>mA | $V_{OUT} = VCC$<br>$V_{OUT} = GND$ |

Although specified for TTL outputs, all TSS901E outputs are CMOS compatible and will drive to VCC and GND assuming no dc loads.

Max. power consumption figures (at 5.5V, 125 °C) are:

| Operation Mode   | Power consumption [mA] |

|------------------|------------------------|

| not clocked      | 5                      |

| TSS901E in RESET | 45                     |

| TSS901E in IDLE  | 70                     |

| Maximum          | 190                    |

## **PLL Filter**

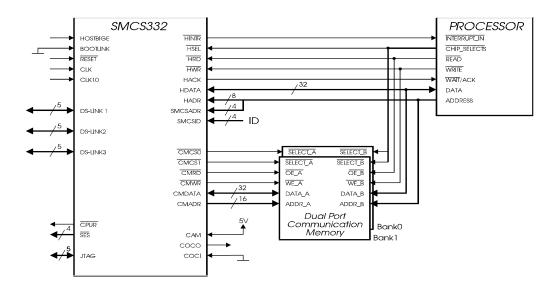

The pin PLLOUT should be connected as shown below:

$R1 = 249\Omega \pm 5\%$ ,  $\frac{1}{4}\frac{1}{4}W$

$C1 = 1nF, \pm 5\%, 20V$

$C2 = 15nF, \pm 5\%, 20V$

# Timing Parameters

# **Clock Signals**

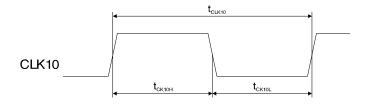

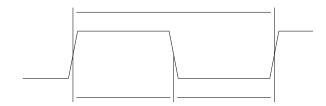

| Description    | Symbol            | Min. | Max. | Unit |

|----------------|-------------------|------|------|------|

| CLK period 1)  | t <sub>CLK</sub>  | 40   |      | ns   |

| CLK width high | t <sub>CLKH</sub> | 17   |      | ns   |

| CLK width low  | t <sub>CLKL</sub> | 17   |      | ns   |

Note: 1) Max. 25 MHz

| Description      | Symbol              | Min. | Max. | Unit |

|------------------|---------------------|------|------|------|

| CLK10 period 1)  | t <sub>CLK10</sub>  | 100  | 100  | ns   |

| CLK10 width high | t <sub>CLK10H</sub> | 40   |      | ns   |

| CLK10 width low  | t <sub>CLK10L</sub> | 40   |      | ns   |

Note: 1) Typically 10 MHz

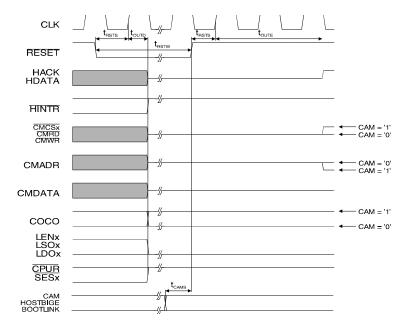

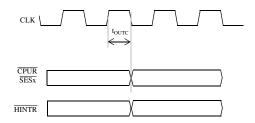

## Reset

| Description                                     | Symbol            | Min.                 | Max.                      | Unit |

|-------------------------------------------------|-------------------|----------------------|---------------------------|------|

| RESET setup before CLK high                     | t <sub>RSTS</sub> | 5                    |                           | ns   |

| RESET low pulse width                           | t <sub>RSTW</sub> | 2 * t <sub>CLK</sub> |                           | ns   |

| Output disable after CLK high                   | t <sub>OUTD</sub> |                      | 42                        | ns   |

| Output enable after CLK high                    | t <sub>oute</sub> |                      | 2 * t <sub>CLK</sub> + 26 | ns   |

| CAM, HOSTBIGE, BOOTLINK setup before RESET high | t <sub>CAMS</sub> | 1                    |                           |      |

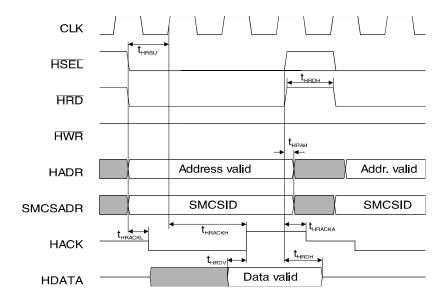

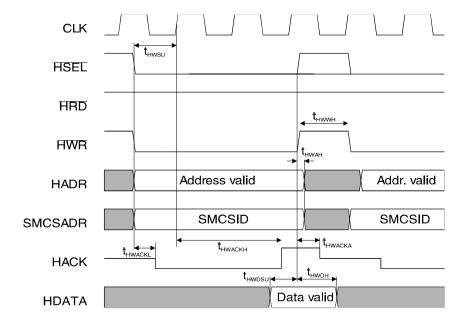

#### **Host Read**

| Description                                                                 | Symbol              | Min.                     | Max.                      | Unit |

|-----------------------------------------------------------------------------|---------------------|--------------------------|---------------------------|------|

| HSEL*, HRD* and TSS901EADR and HADR setup before CLK high                   | t <sub>HRSU</sub>   | 5                        |                           | ns   |

| HADR, TSS901EADR hold after HSEL*, HRD* high                                | t <sub>HRAH</sub>   | 0                        |                           | ns   |

| HRD* pulse width high                                                       | t <sub>HRDH</sub>   | 5                        |                           | ns   |

| HACK low after HRD*, HSEL* active and TSS901EADR valid 1)                   | t <sub>HRACKL</sub> |                          | 16                        | ns   |

| HACK high after CLK high                                                    | t <sub>HRACKH</sub> | 1 * t <sub>CLK</sub> + 5 | 3 * t <sub>CLK</sub> + 23 | ns   |

| HACK disable after HRD*, HSEL* inactive or TSS901EADR invalid <sup>2)</sup> | t <sub>HRACKA</sub> |                          | 12                        | ns   |

| HDATA valid before HACK high                                                | t <sub>HRDV</sub>   | 0                        |                           | ns   |

| HDATA hold after HRD*, HSEL* inactive or TSS901EADR invalid <sup>2)</sup>   | t <sub>HRDH</sub>   | 5                        | 19                        | ns   |

Note: 1) Signal HACK active when HRD\* low and HSEL\* low and TSS901EADR = TSS901EID

2) Signal HACK disable when HRD\* high or HSEL\* high or TSS901EADR 1/4 TSS901EID

# **Host Write**

| Description                                                                   | Symb.               | Min.                     | Max.                        | Unit |

|-------------------------------------------------------------------------------|---------------------|--------------------------|-----------------------------|------|

| HSEL*, HWR* and TSS901EADR and HADR setup before CLK high                     | t <sub>HWSU</sub>   | 5                        |                             | ns   |

| HADR, TSS901EADR hold after HSEL*, HWR* high                                  | t <sub>HWAH</sub>   | 0                        |                             | ns   |

| HWR* pulse width high                                                         | t <sub>HWWH</sub>   | 1 * t <sub>CLK</sub> + 5 |                             | ns   |

| HACK low after HWR*, HSEL* active and TSS901EADR valid 1)                     | t <sub>HWACKL</sub> |                          | 16                          | ns   |

| HACK high after HSEL* and HWR* and TSS901EADR = TSS901EID                     | t <sub>HWACKH</sub> | 1 * t <sub>CLK</sub> + 5 | 2.5 * t <sub>CLK</sub> + 24 | ns   |

| HACK disable after HWR* or HSEL* inactive or TSS901EADR invalid <sup>2)</sup> | t <sub>HWACKA</sub> |                          | 12                          | ns   |

| HDATA setup before HSEL* or HWR* high or TSS901EADR ≠ TSS901EID               | t <sub>HWDSU</sub>  | 5                        |                             | ns   |

| HDATA hold after HWR* or HSEL* inactive or TSS901EADR invalid 2)              | t <sub>HWDH</sub>   | 0                        |                             | ns   |

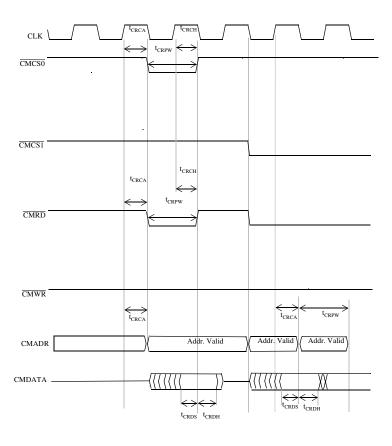

## **COMI Read**

| Description                                                                | Symbol            | Min.                 | Max. | Unit |

|----------------------------------------------------------------------------|-------------------|----------------------|------|------|

| CMCS0*, CMCS1* and CMRD* low and CMADR valid after CLK high                | t <sub>CRCA</sub> |                      | 18   | ns   |

| CMCS0*, CMCS1* or CMRD* high after CLK high                                | t <sub>CRCH</sub> |                      | 18   | ns   |

| CMCS0*, CMCS1*, CMRD*, CMADR pulse width                                   | t <sub>CRPW</sub> | t <sub>CLK</sub> - 1 |      | ns   |

| CMDATA setup before CMCS0* or CMCS1* or CMRD* high or new address on CMADR | t <sub>CRDS</sub> | 4                    |      | ns   |

| CMDATA hold after CMCS0* or CMCS1* or CMRD* high or new address on CMADR   | t <sub>CRDH</sub> | 0                    |      | ns   |

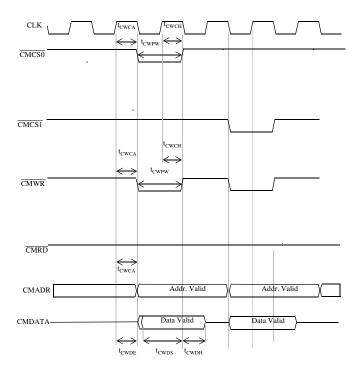

## **COMI Write**

| Description                                                 | Symbol            | Min.                 | Max.                     | Unit |

|-------------------------------------------------------------|-------------------|----------------------|--------------------------|------|

| CMCS0*, CMCS1* and CMWR* low and CMADR valid after CLK high | t <sub>CWCA</sub> |                      | 18                       | ns   |

| CMCS0*, CMCS1* or CMWR* high after CLK high                 | t <sub>CWCH</sub> |                      | 18                       | ns   |

| CMCS0*, CMCS1*, CMWR* pulse width                           | t <sub>CWPW</sub> | t <sub>CLK</sub> - 1 |                          | ns   |

| CMDATA valid after CLK high                                 | t <sub>CWDE</sub> |                      | 15                       |      |

| CMDATA valid before CMCS0* or CMCS1* or CMWR* high          | t <sub>CWDS</sub> | 25                   |                          | ns   |

| CMDATA hold after CMCS0* or CMCS1* or CMWR* high            | t <sub>CWDH</sub> |                      | t <sub>CLK</sub> /2 + 18 | ns   |

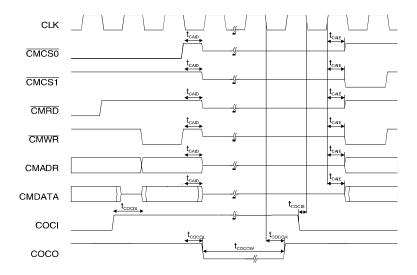

## **COMI Arbitration**

| Description                         | Symbol             | Min. | Max.                   | Unit |

|-------------------------------------|--------------------|------|------------------------|------|

| COM Interface disable after CLK low | t <sub>CAID</sub>  |      | 23                     | ns   |

| COM Interface enable after CLK high | t <sub>CAIE</sub>  |      | 22                     | ns   |

| COCI setup before CLK low           | t <sub>cocis</sub> | 2    |                        | ns   |

| COCO low after CLK low              | t <sub>COCOL</sub> |      | 11                     | ns   |

| COCO high after CLK high            | t <sub>cocoн</sub> |      | 11                     | ns   |

| COCO pulse width 3)                 | t <sub>cocow</sub> |      | N - 1 t <sub>CLK</sub> | ns   |

Note: 3) N = content of COMI\_ACR

# CPUR, SES, Interrupt

| Description                               | Symbol            | Min. | Max. | Unit |

|-------------------------------------------|-------------------|------|------|------|

| CPUR*, SESx*, HINTR* delay after CLK high | t <sub>outc</sub> |      | 22   | ns   |

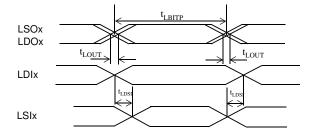

# Links

| Description                 | Symbol             | Min. | Max. | Unit |

|-----------------------------|--------------------|------|------|------|

| Bit Period                  | t <sub>LBITP</sub> | 4    |      | ns   |

| LDOx, LSOx output skew      | t <sub>LOUTS</sub> |      | 0.5  | ns   |

| Data/Strobe edge separation | t <sub>LDSI</sub>  | 1    |      | ns   |

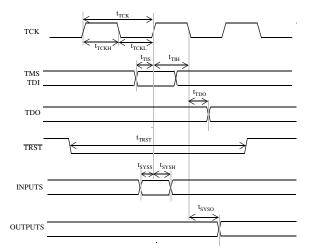

# **Test Port (JTAG)**

| Description                          | Symbol            | Min.                 | Max. | Unit |

|--------------------------------------|-------------------|----------------------|------|------|

| TCK period                           | t <sub>TCK</sub>  | 100                  |      | ns   |

| TCK width high                       | t <sub>TCKH</sub> | 40                   |      | ns   |

| TCK width low                        | t <sub>TCKL</sub> | 40                   |      | ns   |

| TMS, TDI setup before TCK high       | t <sub>TIS</sub>  | 8                    |      | ns   |

| TMS, TDI hold after TCK high         | t <sub>TIH</sub>  | 8                    |      | ns   |

| TDO delay after TCK low              | t <sub>TDO</sub>  |                      | 17   | ns   |

| TRST* pulse width                    | t <sub>TRST</sub> | 2 * t <sub>TCK</sub> |      | ns   |

| TSS901E Inputs setup before TCK high | t <sub>SYSS</sub> | 8                    |      | ns   |

| TSS901E Inputs hold after TCK high   | t <sub>SYSM</sub> | 8                    |      | ns   |

| TSS901E Outputs delay after TCK low  | t <sub>syso</sub> |                      | 27   | ns   |

Note: The BSDL file is printed in the Annex of this document.

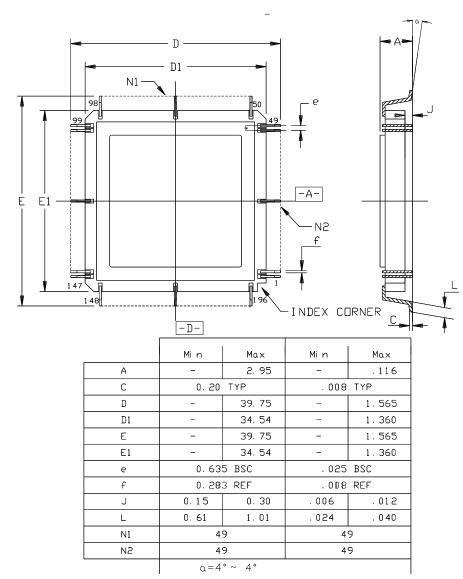

# Package Drawings

MQFPL 196 Code: FX Date:13/10/00

# **Pin Assignment**

| Pin Number | Name        | Pin Number | Name    | Pin Number | Name     |

|------------|-------------|------------|---------|------------|----------|

| 1          | VCC         | 67         | HDATA18 | 133        | CMDATA8  |

| 2          | GND         | 68         | HDATA19 | 134        | VCC      |

| 3          | GND         | 69         | HDATA20 | 135        | GND      |

| 4          | CLK         | 70         | HDATA21 | 136        | CMDATA9  |

| 5          | RESET*      | 71         | HDATA22 | 137        | CMDATA10 |

| 6          | CLK10       | 72         | HDATA23 | 138        | CMDATA11 |

| 7          | HOSTBIGE    | 73         | VCC     | 139        | CMDATA12 |

| 8          | TCK         | 74         | GND     | 140        | CMDATA13 |

| 9          | TMS         | 75         | HDATA24 | 141        | CMDATA14 |

| 10         | TDI         | 76         | HDATA25 | 142        | VCC      |

| 11         | TRST*       | 77         | HDATA26 | 143        | GND      |

| 12         | TDO         | 78         | VCC     | 144        | CMDATA15 |

| 13         | VCC         | 79         | GND     | 145        | CMDATA16 |

| 14         | GND         | 80         | HDATA27 | 146        | CMDATA17 |

| 15         | HSEL*       | 81         | HDATA28 | 147        | CMDATA18 |

| 16         | HRD*        | 82         | HDATA29 | 148        | CMDATA19 |

| 17         | HWR*        | 83         | VCC     | 149        | CMDATA20 |

| 18         | HACK        | 84         | GND     | 150        | VCC      |

| 19         | HINTR*      | 85         | HDATA30 | 151        | GND      |

| 20         | VCC         | 86         | HDATA31 | 152        | CMDATA21 |

| 21         | GND         | 87         | CPUR*   | 153        | CMDATA22 |

| 22         | HADR0       | 88         | SES0*   | 154        | CMDATA23 |

| 23         | HADR1       | 89         | SES1*   | 155        | VCC      |

| 24         | HADR2       | 90         | SES2*   | 156        | GND      |

| 25         | HADR3       | 91         | SES3*   | 157        | CMDATA24 |

| 26         | HADR4       | 92         | CAM     | 158        | CMDATA25 |

| 27         | HADR5       | 93         | COCI    | 159        | CMDATA26 |

| 28         | HADR6       | 94         | COCO    | 160        | VCC      |

| 29         | HADR7       | 95         | CMCS0*  | 161        | GND      |

| 30         | VCC         | 96         | CMCS1*  | 162        | CMDATA27 |

| 31         | GND         | 97         | VCC     | 163        | CMDATA28 |

| 32         | BOOTLINK    | 98         | GND     | 164        | CMDATA29 |

| 33         | TSS901EADR0 | 99         | CMRD*   | 165        | CMDATA30 |

| 34         | TSS901EADR1 | 100        | CMWR*   | 166        | CMDATA31 |

| 35         | TSS901EADR2 | 101        | CMADR0  | 167        | NC       |

| 36         | TSS901EADR3 | 102        | CMADR1  | 168        | NC       |

| 37         | TSS901EID0  | 103        | CMADR2  | 169        | NC       |

| 38         | TSS901EID1  | 104        | CMADR3  | 170        | NC       |

| 39         | TSS901EID2  | 105        | CMADR4  | 171        | NC       |

| 40         | TSS901EID3  | 106        | VCC     | 172        | VCC      |

| 41         | VCC         | 107        | GND     | 173        | GND      |

| 42         | GND         | 108        | CMADR5  | 174        | GND      |

| 43         | HDATA0      | 109        | CMADR6  | 175        | LEN1     |

| 44         | HDATA1      | 110        | CMADR7  | 176        | LDI1     |

| Pin Number | Name    | Pin Number | Name    | Pin Number | Name   |

|------------|---------|------------|---------|------------|--------|

| 45         | HDATA2  | 111        | CMADR8  | 177        | LSI1   |

| 46         | HDATA3  | 112        | CMADR9  | 178        | LDO1   |

| 47         | HDATA4  | 113        | CMADR10 | 179        | LSO1   |

| 48         | HDATA5  | 114        | CMADR11 | 180        | LDI2   |

| 49         | HDATA6  | 115        | VCC     | 181        | LSI2   |

| 50         | VCC     | 116        | GND     | 182        | LEN2   |

| 51         | GND     | 117        | CMADR12 | 183        | VCC    |

| 52         | HDATA7  | 118        | CMADR13 | 184        | VCC    |

| 53         | HDATA8  | 119        | CMADR14 | 185        | VCC    |

| 54         | HDATA9  | 120        | CMADR15 | 186        | LDO2   |

| 55         | HDATA10 | 121        | CMDATA0 | 187        | LSO2   |

| 56         | HDATA11 | 122        | CMDATA1 | 188        | LDI3   |

| 57         | VCC     | 123        | CMDATA2 | 189        | LSI3   |

| 58         | GND     | 124        | VCC     | 190        | LDO3   |

| 59         | HDATA12 | 125        | GND     | 191        | LSO3   |

| 60         | HDATA13 | 126        | CMDATA3 | 192        | LEN3   |

| 61         | HDATA14 | 127        | CMDATA4 | 193        | GND    |

| 62         | HDATA15 | 128        | CMDATA5 | 194        | GND    |

| 63         | HDATA16 | 129        | VCC     | 195        | VCC    |

| 64         | HDATA17 | 130        | GND     | 196        | PLLOUT |

| 65         | VCC     | 131        | CMDATA6 |            |        |

| 66         | GND     | 132        | CMDATA7 |            |        |

# Ordering Information

| Part-number     | Temp. Range | Package  | Quality Flow       |

|-----------------|-------------|----------|--------------------|

| TSS901EMA-E     | 25℃         | MQFPL196 | Engineering sample |

| 5962-01A1701QXC | -55℃ +125℃  | MQFPL196 | QML-Q              |

| 5962-01A1701VXC | -55℃ +125℃  | MQFPL196 | QML-V              |

# **Document Revision History**

Changes from 4167D to 4167E

1. Changed web address of location of TSS901E User's Manual. Page 1.

Changes from to 4167E to 4167F

1. Updated Ordering Information.

#### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA

Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### Regional Headquarters

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland

Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Iayan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Atmel Operations**

#### Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France

Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00

Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300

Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland

Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Chevenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom

Avenue de Rochepleine BP 123

38521 Saint-Egreve Cedex, France

Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically providedotherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

©2007 Atmel Corporation. All rights reserved. Atmel®, logo and combinations thereof, are the trademarks or registered trademarks, of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.