#### **Features**

- Full-duplex Operation Mode without Duplex Frequency Offset to Prevent the Relay Attack against Passive Entry Go (PEG) Systems

- High FSK Sensitivity: -105.5 dBm at 20 Kbit/s/-109 dBm at 2.4 Kbit/s (433.92 MHz)

- High ASK Sensitivity: -111.5 dBm at 10 Kbit/s/-116 dBm at 2.4 Kbit/s (100% ASK, Carrier Level 433.92 MHz)

- Low Supply Current: 10.5 mA in RX and TX Mode (3V/TX with 5 dBm/433.92 MHz)

- Data Rate 1 to 20 Kbit/s Manchester FSK, 1 to 10 Kbit/s Manchester ASK

- ASK/FSK Receiver Uses a Low IF Architecture with High Selectivity, Blocking and Low Intermodulation (Typical 3 dB Blocking 55.5 dBC at ±750 kHz/60.5 dBC at ±1.5 MHz and 67 dBC at ±10 MHz, System I1dBCP = -30 dBm/System IIP3 = -20 dBm)

- Wide Bandwidth AGC to Handle Large Outband Blockers above the System I1dBCP

- 226 kHz IF (Intermediate Frequency) with 30 dB Image Rejection and 220 kHz System Bandwidth to Support TPM Transmitters using ATA5756/ATA5757 Transmitters with Standard Crystals

- Transmitter Uses Closed Loop FSK Modulation with Fractional-N Synthesizer with High PLL Bandwidth and an Excellent Isolation between PLL and PA

- Tolerances of XTAL Compensated by Fractional-N Synthesizer with 800 Hz RF Resolution

- Integrated RX/TX-Switch, Single-ended RF Input and Output

- RSSI (Received Signal Strength Indicator)

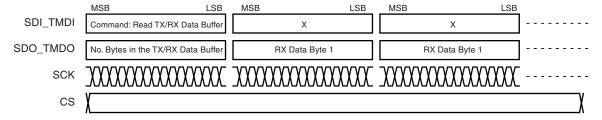

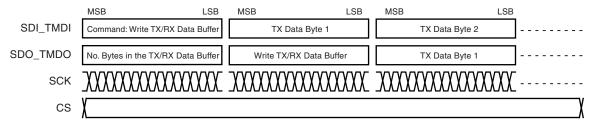

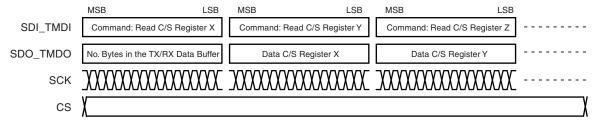

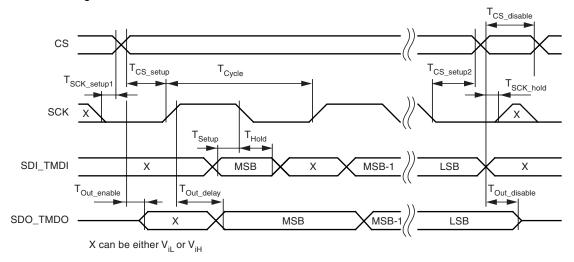

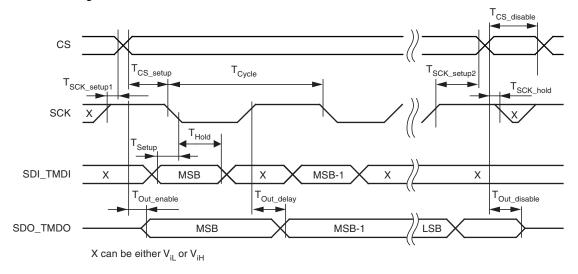

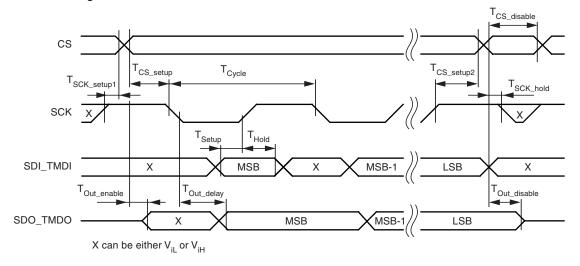

- . Communication to Microcontroller with SPI Interface Working at 500 kBit/s Maximum

- Configurable Self Polling and RX/TX Protocol Handling with FIFO-RAM Buffering of Received and Transmitted Data

- 1 Push Button Input and 1 Wake-up Input are Active in Power-down Mode

- Integrated XTAL Capacitors

- PA Efficiency: up to 38% (433.92 MHz/10 dBm/3V)

- Low In-band Sensitivity Change of Typically ±2.0 dB within ±75 kHz Center Frequency Change in the Complete Temperature and Supply Voltage Range

- Fully Integrated PLL with Low Phase Noise VCO, PLL Loop Filter and full support of multi-channel operation with arbitrary Channel distance due to Fractional-N Synthesizer

- Sophisticated Threshold Control and Quasi-peak Detector Circuit in the Data Slicer

- 433.92 MHz, 868.3 MHz and 315 MHz without External VCO and PLL Components

- Efficient XTO Start-up Circuit (>  $-1.5 \text{ k}\Omega$  Worst Case Start Impedance)

- Changing of Modulation Type ASK/FSK and Data Rate without Component Changes to Allow Different Modulation Schemes in TPM and RKE

- Minimal External Circuitry Requirements for Complete System Solution

- Adjustable Output Power: 0 to 10 dBm Adjusted and Stabilized with External Resistor,

Programmable Output Power with 0.5dB Steps with Internal Resistor

- Clock and Interrupt Generation for Microcontroller

- ESD Protection at all Pins (±2.5 kV HBM, ±200V MM, ±500V FCDM)

- Supply Voltage Range: 2.15V to 3.6V or 4.4V to 5.25V

- Typical Power-down Current < 10 nA</li>

- Temperature Range: -40°C to +105°C

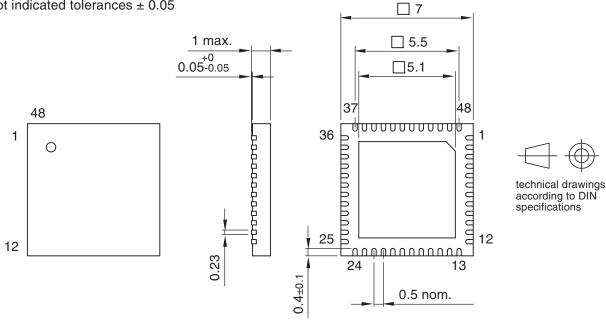

- Small 7 mm × 7 mm QFN48 Package

# UHF ASK/FSK Transceiver

ATA5823 ATA5824

## **Applications**

- Automotive Keyless Entry and Passive Entry Go (Handsfree Car Access)

- Tire Pressure Monitoring Systems

- Remote Control Systems

- Alarm and Telemetering Systems

- Energy Metering

- Home Automation

#### **Benefits**

- No SAW Device Needed in Key Fob Designs to Meet Automotive Specifications

- Low System Cost Due to Very High System Integration Level

- . Only One Crystal Needed in System

- Less Demanding Specification for the Microcontroller Due to Handling of Power-down Mode,

Delivering of Clock and Complete Handling of Receive/Transmit Protocol and Polling

- Single-ended Design with High Isolation of PLL/VCO from PA and the Power Supply Allows a Loop Antenna in the Key Fob to Surround the Whole Application

- Prevention against Relay Attack with Full-duplex Operation Mode

- Integration of Tire Pressure Monitoring, Passive Entry and Remote Keyless Entry

## 1. General Description

The ATA5823/ATA5824 is a highly integrated UHF ASK/FSK multi-channel half-duplex and full-duplex transceiver with low power consumption supplied in a small 7 mm  $\times$  7 mm QFN48 package. The receive part is built as a fully integrated low-IF receiver, whereas direct PLL modulation with the fractional-N synthesizer is used for FSK transmission and switching of the power amplifier for ASK transmission. The additional full-duplex mode makes relay attacks much more difficult, since the attacker has to receive and transmit signals on the same frequency at the same time.

The device supports data rates of 1 Kbit/s to 20 Kbit/s (FSK) and 1 Kbit/s to 10 Kbit/s (ASK) in Manchester, Bi-phase and other codes in transparent mode. The ATA5824 can be used in the 433 MHz to 435 MHz band and the 867 MHz to 870 MHz band, the ATA5823 in the 313 MHz to 316 MHz band. The very high system integration level results in few numbers of external components needed.

Due to its blocking and selectivity performance, together with a typical narrow-band key-fob loop antenna with 15 dB to 20 dB loss, a bulky blocking SAW is not needed in the key fob application. Additionally, the building blocks needed for a typical RKE and access control system on both sides, the base and the mobile stations, are fully integrated.

Its digital control logic with self polling and protocol generation provides a fast challenge response system without using a high-performance microcontroller. Therefore, the ATA5823/ATA5824 contains a FIFO buffer RAM and can compose and receive the physical messages themselves. This provides more time for the microcontroller to carry out other functions such as calculating crypto algorithms, composing the logical messages and controlling other devices. Due to that, a standard 4-/8-bit microcontroller without special periphery and clocked with the delivered CLK output of about 4.5 MHz is sufficient to control the communication link. This is especially valid for passive entry go and access control systems, where within less than 100 ms several communication responses with arbitration of the communication partner have to be handled. It is hence possible to design bi-directional RKE and passive entry go systems with a fast challenge response crypto function and prevention against relay attacks.

2

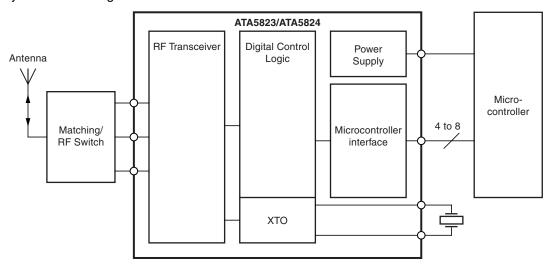

Figure 1-1. System Block Diagram

# 2. Pin Configuration

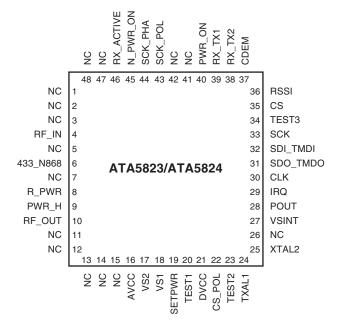

Figure 2-1. Pinning QFN48

Table 2-1.Pin Description

| Pin | Symbol      | Function                                                    |  |  |

|-----|-------------|-------------------------------------------------------------|--|--|

| 1   | NC          | Not connected                                               |  |  |

| 2   | NC          | Not connected                                               |  |  |

| 3   | NC          | Not connected                                               |  |  |

|     |             |                                                             |  |  |

| 4   | RF_IN<br>NC | RF input                                                    |  |  |

| 5   |             | Not connected                                               |  |  |

| 6   | 433_N868    | Selects RF input/output frequency range                     |  |  |

| 7   | NC          | Not connected                                               |  |  |

| 8   | R_PWR       | Resistor to adjust output power                             |  |  |

| 9   | PWR_H       | Pin to select output power                                  |  |  |

| 10  | RF_OUT      | RF output                                                   |  |  |

| 11  | NC          | Not connected                                               |  |  |

| 12  | NC          | Not connected                                               |  |  |

| 13  | NC          | Not connected                                               |  |  |

| 14  | NC          | Not connected                                               |  |  |

| 15  | NC          | Not connected                                               |  |  |

| 16  | AVCC        | Blocking of the analog voltage supply                       |  |  |

| 17  | VS2         | Power supply input for voltage range 4.4V to 5.6V           |  |  |

| 18  | VS1         | Power supply input for voltage range 2.15V to 3.6V          |  |  |

| 19  | SETPWR      | Internal Programmable Resistor to adjust output power       |  |  |

| 20  | TEST1       | Test input, at GND during operation                         |  |  |

| 21  | DVCC        | Blocking of the digital voltage supply                      |  |  |

| 22  | CS_POL      | Select polarity of pin CS                                   |  |  |

| 23  | TEST2       | Test input, at GND during operation                         |  |  |

| 24  | XTAL1       | Reference crystal                                           |  |  |

| 25  | XTAL2       | Reference crystal                                           |  |  |

| 26  | NC          | Not connected                                               |  |  |

| 27  | VSINT       | Microcontroller interface supply voltage                    |  |  |

| 28  | POUT        | Programmable output                                         |  |  |

| 29  | IRQ         | Interrupt request                                           |  |  |

| 30  | CLK         | Clock output to connect a microcontroller                   |  |  |

| 31  | SDO_TMDO    | Serial data out/transparent mode data out                   |  |  |

| 32  | SDI_TMDI    | Serial data in/transparent mode data in                     |  |  |

|     | SCK         |                                                             |  |  |

| 33  |             | Serial clock                                                |  |  |

| 34  | TEST3       | Test output open during operation                           |  |  |

| 35  | CS          | Chip select for serial interface                            |  |  |

| 36  | RSSI        | Output of the RSSI amplifier                                |  |  |

| 37  | CDEM        | Capacitor to adjust the lower cut-off frequency data filter |  |  |

| 38  | RX_TX2      | Has to be connected GND                                     |  |  |

| 39  | RX_TX1      | Switch pin to decouple LNA in TX mode (RKE mode)            |  |  |

| 40  | PWR_ON      | Input to switch on the system (active high)                 |  |  |

| 41  | NC          | Not connected                                               |  |  |

Table 2-1. Pin Description (Continued)

| Pin | Symbol    | Function                                                              |  |

|-----|-----------|-----------------------------------------------------------------------|--|

| 42  | NC        | Not connected                                                         |  |

| 43  | SCK_POL   | Polarity of the serial clock                                          |  |

| 44  | SCK_PHA   | hase of the serial clock                                              |  |

| 45  | N_PWR_ON  | Keyboard input (can also be used to switch on the system, active low) |  |

| 46  | RX_ACTIVE | Indicates RX operation mode                                           |  |

| 47  | NC        | Not connected                                                         |  |

| 48  | NC        | ot connected                                                          |  |

|     | GND       | Ground/Backplane (exposed die pad)                                    |  |

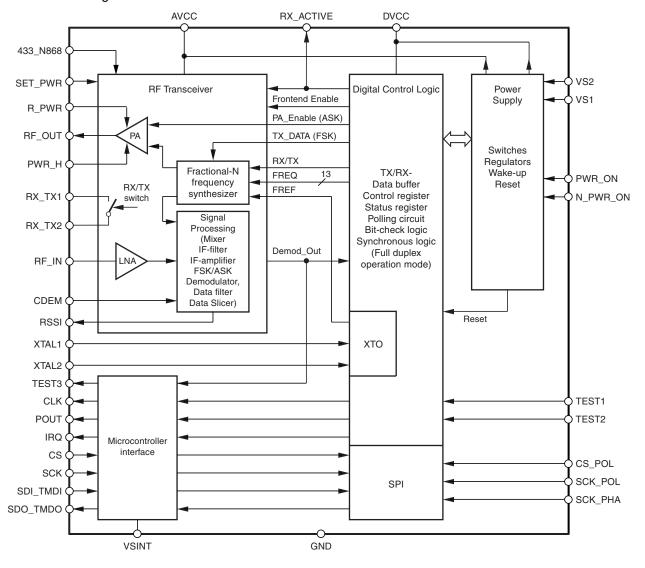

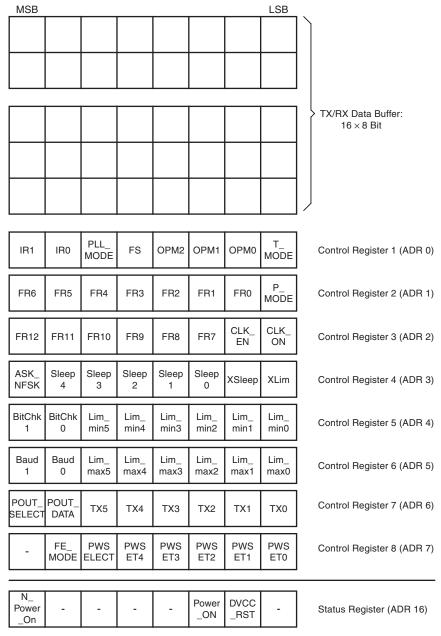

Figure 2-2. Block Diagram

# 3. Typical Key Fob Application for Bi-directional RKE

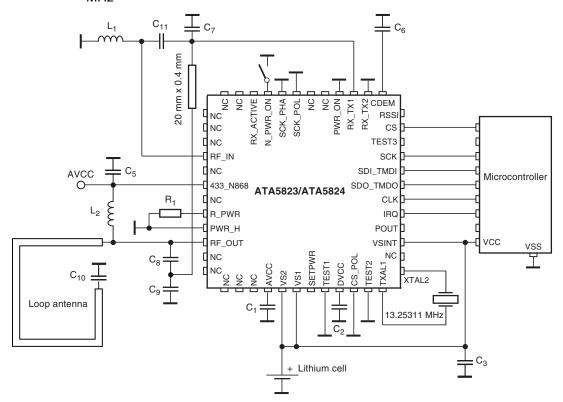

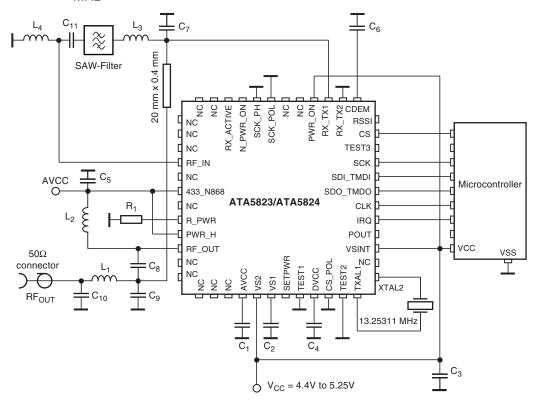

**Figure 3-1.** Typical Key Fob Application for Bi-directional RKE with 5 dBm TX Power, 433.92 MHz

Figure 3-1 shows a typical 433.92 MHz RKE key fob application. The external components are 10 capacitors, 1 resistor, 2 inductors and a crystal. C<sub>1</sub> to C<sub>3</sub> are 68 nF voltage supply blocking capacitors.  $C_5$  is a 10 nF supply blocking capacitor.  $C_6$  is a 15 nF fixed capacitor used for the internal quasi-peak detector and for the high-pass frequency of the data filter. C<sub>7</sub> to C<sub>11</sub> are RF matching capacitors in the range of 1 pF to 33 pF. L<sub>1</sub> is a matching inductor of about 5.6 nH to 56 nH. L2 is a feed inductor of about 120 nH. A load capacitor of 9 pF for the crystal is integrated.  $R_1$  is typically 22 k $\Omega$  and sets the output power to about 5.5 dBm. The loop antenna's quality factor is somewhat reduced by this application due to the quality factor of L2 and the RX/TX switch. On the other hand, this lower quality factor is necessary to have a robust design with a bandwidth that is wide enough for production tolerances. Due to the single-ended and ground-referenced design, the loop antenna can be a free-form wire around the application as it is usually employed in RKE unidirectional systems. The ATA5823/ATA5824 provides sufficient isolation and robust pulling behavior of internal circuits from the supply voltage as well as an integrated VCO inductor to allow this. Since the efficiency of a loop antenna is proportional to the square of the surrounded area, it is beneficial to have a large loop around the application board with a lower quality factor to relax the tolerance specification of the RF matching components and to get a high antenna efficiency in spite of their lower quality factor.

# 4. Typical Car Application for Bi-directional RKE

**Figure 4-1.** Typical Car Application for Bi-directional RKE with 10 dBm TX Power, 433.92 MHz

Figure 4-1 shows a typical 433.92 MHz  $V_{CC}$  = 4.4V to 5.25V RKE car application. The external components are 11 capacitors, 1 resistor, 4 inductors, a SAW filter and a crystal.  $C_1$ ,  $C_3$  and  $C_4$  are 68 nF voltage supply blocking capacitors.  $C_2$  is a 2.2 µF supply blocking capacitor for the internal voltage regulator.  $C_5$  is a 10 nF supply blocking capacitor.  $C_6$  is a 15 nF fixed capacitor used for the internal quasi-peak detector and for the high-pass frequency of the data filter.  $C_7$  to  $C_{11}$  are RF matching capacitors in the range of 1 pF to 33 pF.  $L_2$  to  $L_4$  are matching inductors of about 5.6 nH to 56 nH. A load capacitor for the crystal of 9 pF is integrated.  $R_1$  is typically 22 k $\Omega$  and sets the output power at RF<sub>OUT</sub> to about 10 dBm. Since a quarter wave or PCB antenna, which has high efficiency and wideband operation, is typically used here, it is recommended to use a SAW filter to achieve high sensitivity in case of powerful out-of-band blockers.  $L_1$ ,  $C_{10}$  and  $C_9$  together form a low-pass filter, which is needed to filter out the harmonics in the transmitted signal to meet regulations.

# 5. Typical Key Fob Application for Full-duplex PEG

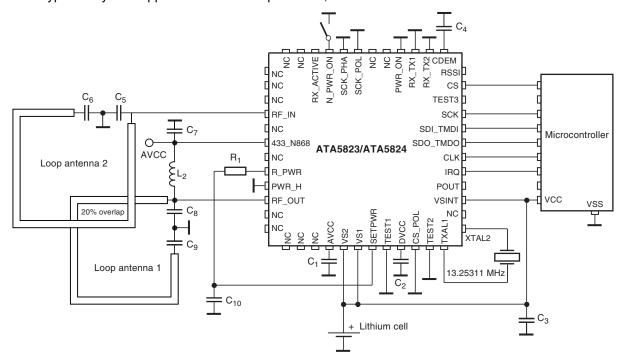

Figure 5-1. Typical Key Fob Application for Full-duplex PEG, 433.92 MHz

Figure 5-1 shows a typical 433.92 MHz PEG key fob application. The external components are 10 capacitors, 1 resistor, 1 inductor and a crystal. C<sub>1</sub> to C<sub>3</sub> are 68 nF voltage supply blocking capacitors. C<sub>7</sub> is a 10 nF supply blocking capacitor. C<sub>4</sub> is a 15 nF fixed capacitor used for the internal quasi-peak detector and for the high-pass frequency of the data filter. C<sub>5</sub>, C<sub>6</sub>, C<sub>8</sub> and C<sub>9</sub> are RF matching capacitors in the range of 1 pF to 33 pF.  $L_2$  is a feed inductor of about 120 nH. C<sub>10</sub> is a 10 nF capacitor which is necessary to prevent that signals couple into the pin R\_PWR, causing amplitude modulation of the output power and a spurious rise of the transmitted signal. R<sub>1</sub> and C<sub>10</sub> should be placed close to the R\_PWR pin. A load capacitor of 9 pF for the crystal is integrated.  $R_1$  is typically 22 k $\Omega$  and SETPWR is programmed to get an output power of -7 dBm in full-duplex mode and 5 dBm in half-duplex mode. The quality factor of the loop antenna 1 is only reduced by the quality factor of L2, the tolerances of C9 and C8 are thus important. The quality factor of the loop antenna 2 is reduced to half due to the loading with the input impedance of RF\_IN. With well designed loop antennas and the correct degree of overlapping, the isolation between RF\_OUT and RF\_IN is about 28 dB and the coupled output power from RF\_OUT to RF IN is about -35 dBm. The decoupling of two loop antennas situated close to each other is due to the effect that the magnetic flux from the part of loop antenna 1 that does not overlap and that of the overlapping part has an opposite direction. Depending on the relative position between the two antennas, a decoupling of 28 dB is achievable. Due to additional capacitive coupling between the loops the position of the components  $C_5$ ,  $C_6$  and  $C_8$ ,  $C_9$  are also important. The receive Sensitivity in full-duplex mode is reduced from -106 dBm without coupled RF-Power at RF IN to -96 dBm with -35 dBm coupled RF power at RF IN.

## 6. Typical Car Application for Full-duplex PEG

500 connector to RX antenna <sup>™</sup> CDEM S S S X N\_PWR\_ON X X, NC CS NC RF IN SCK  $C_5$ NC SDI TMD Microcontroller 433\_N868 SDO TMDO ATA5823/ATA5824 R<sub>1</sub> NC R\_PWR IRQ  $C_2$ PWR H POUT RF OUT VSINT C<sub>10</sub> NC NC TX Loop antenna TXAL1 (located in the control unit) 13.25311 MHz C<sub>11</sub> **\_** C<sub>3</sub>  $V_{CC} = 4.4V \text{ to } 5.25V$

Figure 6-1. Typical Car Application for Full-duplex PEG, 433.92 MHz

Figure 6-1 shows a typical 433.92 MHz V<sub>CC</sub> = 4.4V to 5.25V PEG car application. The external components are 11 capacitors, 1 resistor, 3 inductors, a SAW Filter and a crystal. C<sub>1</sub>, C<sub>3</sub> and C<sub>4</sub> are 68 nF voltage supply blocking capacitors. C2 is a 2.2 µF supply blocking capacitors for the internal voltage regulator. C5 is a 10 nF supply blocking capacitor. C6 is a 15 nF fixed capacitor used for the internal quasi-peak detector and for the high-pass frequency of the data filter. C<sub>7</sub> to C<sub>10</sub> are RF matching capacitors in the range of 1 pF to 33 pF. L<sub>1</sub> is a feed inductor of about 120 nH, L<sub>2</sub> and L<sub>3</sub> are matching inductors to match the RX-antenna to the SAW and the SAW to RF\_IN. A load capacitor of 9 pF for the crystal is integrated. C<sub>11</sub> is a 10 nF capacitor which is necessary to prevent that signals couple into the pin R\_PWR, causing amplitude modulation of the output power and a spurious rise of the transmitted signal. R<sub>1</sub> and C<sub>11</sub> should be placed close to the R\_PWR pin.  $R_1$  is typically 22 k $\Omega$  and SETPWR is programmed to get an output power of 0 dBm in full-duplex mode and 5 dBm in half-duplex mode. The quality factor of the TX-loop antenna is only reduced by the quality factor of  $L_1$ , the tolerances of  $C_9$  and  $C_{10}$  are thus important. Since the 2 Antennas are located at different places the isolation between RF\_OUT and RF\_IN is about 45 dB and the coupled output power from RF\_OUT to RF\_IN is about -45 dBm. The receive Sensitivity in full-duplex mode is reduced from -106 dBm without coupled RF power at RF\_IN to -102 dBm with -45 dBm coupled RF power at RF\_IN. The use of SAW filters in the full-duplex system is unsuitable due to the high group delay which desensitize the receiver.

# 7. RF Transceiver in Half-duplex Mode

According to Figure 2-2 on page 5, the RF transceiver consists of an LNA (Low-Noise Amplifier), PA (Power Amplifier), RX/TX switch, fractional-N frequency synthesizer and the signal processing part with mixer, IF filter, IF amplifier with analog RSSI, FSK/ASK demodulator, data filter and data slicer.

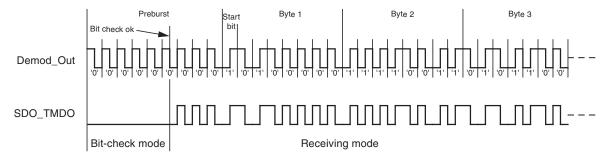

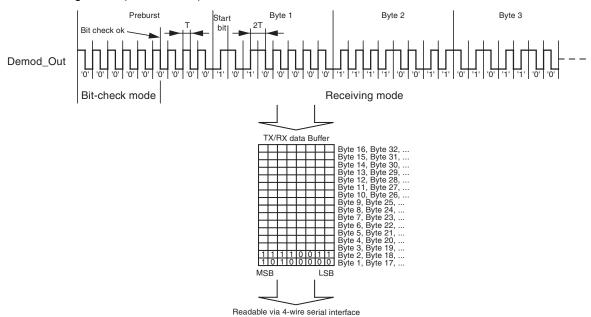

In receive mode the LNA pre-amplifies the received signal which is converted down to 226 kHz intermediate frequency (IF), filtered and amplified before it is fed into an FSK/ASK demodulator, data filter and data slicer. The RSSI (Received Signal Strength Indicator) signal and the raw digital output signal of the demodulator are available at the pins RSSI and on TEST3 (open drain output). The demodulated data signal Demod\_Out is fed into the digital control logic where it is evaluated and buffered as described in section "Digital Control Logic" on page 35.

In transmit mode the fractional-N frequency synthesizer generates the TX frequency which is fed into the PA. In ASK mode the PA is modulated by the signal PA\_Enable. In FSK mode the PA is enabled and the signal TX\_DATA (FSK) modulates the fractional-N frequency synthesizer. The frequency deviation is digitally controlled and internally fixed to about ±19.5 kHz (see Table 9-1 on page 30 for exact values). The transmit data can also be buffered as described in section "Digital Control Logic" on page 35. A lock detector within the synthesizer ensures that the transmission will only start if the synthesizer is locked.

In half-duplex mode the RX/TX switch can be used to combine the LNA input and the PA output to a single antenna with a minimum of losses. In full-duplex mode more isolation between receive and transmit antenna is needed, therefore two antennas have to be used.

Transparent modes without buffering of RX and TX data are also available to allow protocols and coding schemes other than the internal supported Manchester encoding, like PWM and pulse position coding.

#### 7.1 Low-IF Receiver

The receive path consists of a fully integrated low-IF receiver. It fulfills the sensitivity, blocking, selectivity, supply voltage and supply current specification needed to manufacture an automotive key fob for RKE and PEG systems without the use of a SAW blocking filter (see Figure 3-1 on page 6 and Figure 5-1 on page 8). The receiver can be connected to the roof antenna in the car when using an additional blocking SAW front-end filter as shown in Figure 4-1 on page 7.

At 433.92 MHz the receiver has a typical system noise figure of 6.5 dB, a system I1dBCP of -30 dBm and a system IIP3 of -20 dBm. The signal path is linear for disturbers up to the I1dBCP and there is hence no AGC or switching of the LNA needed to achieve a better blocking performance. This receiver uses an IF of about 226 kHz (see table "Electrical Characteristics" number 2.10 for exact values), the typical image rejection is 30 dB and the typical 3 dB system bandwidth is 220 kHz ( $f_{\rm IF} = 226$  kHz  $\pm 110$  kHz,  $f_{\rm Io\_IF} = 116$  kHz and  $f_{\rm hi\_IF} = 336$  kHz). The demodulator needs a signal to noise ratio of 8 dB for 20 Kbit/s Manchester with  $\pm 19.5$  kHz frequency deviation in FSK mode, thus, the resulting sensitivity at 433.92 MHz is typically -105.5 dBm.

Due to the low phase noise and spurious of the synthesizer in receive mode<sup>(1)</sup> together with the eighth order integrated IF filter the receiver has a better selectivity and blocking performance than more complex double superhet receivers, without using external components and without numerous spurious receiving frequencies.

Note: 1. -120 dBC/Hz at  $\pm 1 \text{ MHz}$  and -72 dBC at  $\pm f_{XTO}$  at 433.92 MHz

10

$311\Omega / 2.2 pF$

11

A low-IF architecture is also less sensitive to second-order intermodulation (IIP2) than direct conversion receivers where every pulse or amplitude modulated signal (especially the signals from TDMA systems like GSM) demodulates to the receiving signal band at second-order non-linearities.

#### 7.2 Input Matching at RF\_IN

The measured input impedances as well as the values of a parallel equivalent circuit of these impedances can be seen in Table 7-1. The highest sensitivity is achieved with power matching of these impedances to the source impedance of  $50\Omega$

| · ·                  | <u> </u>                |                        |

|----------------------|-------------------------|------------------------|

| f <sub>RF</sub> /MHz | Z <sub>In</sub> (RF_IN) | $R_{ln_p}/\!/C_{ln_p}$ |

| 315                  | $(44-j233)\Omega$       | 1278Ω//2.1 pF          |

| 433.92               | (32-i169)Ω              | 925Q//2.1 pF           |

$(21-j78)\Omega$

Table 7-1. Measured Input Impedances of the RF\_IN Pin

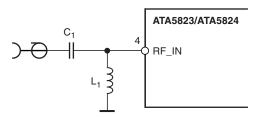

The matching of the LNA Input to  $50\Omega$  was done with the circuit according to Figure 7-1 and with the values of the matching elements given in Table 7-2. The reflection coefficients were always  $\leq$  –10 dB. Note that value changes of  $C_1$  and  $L_1$  may be necessary to compensate individual board layout parasitics. The measured typical FSK and ASK Manchester code sensitivities with a Bit Error Rate (BER) of  $10^{-3}$  are shown in Table 7-3 on page 12 and Table 7-4 on page 12. These measurements were done with multilayer inductors having quality factors according to Table 7-2, resulting in estimated matching losses of 0.8 dB at 315 MHz, 0.8 dB at 433.92 MHz and 0.7 dB at 868.3 MHz. These losses can be estimated when calculating the parallel equivalent resistance of the inductor with  $R_{loss} = 2 \times \pi \times f \times L \times Q_L$  and the matching loss with  $10 \log(1+R_{ln_D}/R_{loss})$ .

With an ideal inductor, for example, the sensitivity at 433.92 MHz/FSK/20 Kbit/s/ $\pm$ 19.5 kHz/Manchester can be improved from –105.5 dBm to –106.7 dBm. The sensitivity also depends on the values in the registers of the control logic which examines the incoming data stream. The examination limits must be programmed in control registers 5 and 6. The measurements in Table 7-3 and Table 7-4 on page 12 are based on the values of registers 5 and 6 according to Table 14-3 on page 60.

**Figure 7-1.** Input Matching to  $50\Omega$

868.3

**Table 7-2.** Input Matching to  $50\Omega$

| f <sub>RF</sub> /MHz | C <sub>1</sub> /pF | L <sub>1</sub> /nH | $Q_{L1}$ |

|----------------------|--------------------|--------------------|----------|

| 315                  | 2.4                | 47                 | 65       |

| 433.92               | 1.8                | 27                 | 67       |

| 868.3                | 1.2                | 6.8                | 50       |

**Table 7-3.** Measured Typical Sensitivity 433.92 MHz, FSK, ±19.5 kHz, Manchester, BER = 10<sup>-3</sup>

| RF Frequency | BR_Range_0<br>1.0 Kbit/s | BR_Range_0<br>2.4 Kbit/s | BR_Range_1<br>5.0 Kbit/s | BR_Range_2<br>10 Kbit/s | BR_Range_3<br>20 Kbit/s |

|--------------|--------------------------|--------------------------|--------------------------|-------------------------|-------------------------|

| 315 MHz      | –109.5 dBm               | –110.0 dBm               | -109.0 dBm               | −107.5 dBm              | –106.5 dBm              |

| 433.92 MHz   | –108.5 dBm               | -109.0 dBm               | -108.0 dBm               | –106.5 dBm              | -105.5 dBm              |

| 868.3 MHz    | −105.5 dBm               | −106.5 dBm               | −105.5 dBm               | −103.5 dBm              | -103.0 dBm              |

**Table 7-4.** Measured Typical Sensitivity 433.92 MHz, 100% ASK, Manchester, BER = 10<sup>-3</sup>

| RF Frequency | BR_Range_0<br>1.0 Kbit/s | BR_Range_0<br>2.4 Kbit/s | BR_Range_1<br>5.0 Kbit/s | BR_Range_2<br>10 Kbit/s |

|--------------|--------------------------|--------------------------|--------------------------|-------------------------|

| 315 MHz      | –117.0 dBm               | -117.0 dBm               | –114.5 dBm               | –112.5 dBm              |

| 433.92 MHz   | -116.0 dBm               | -116.0 dBm               | -113.5 dBm               | –111.5 dBm              |

| 868.3 MHz    | −113.0 dBm               | -113.0 dBm               | –111.5 dBm               | -109.0 dBm              |

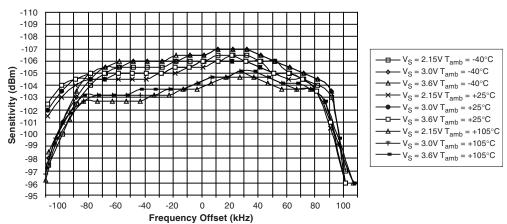

## 7.3 Sensitivity versus Supply Voltage, Temperature and Frequency Offset

To calculate the behavior of a transmission system it is important to know the reduction of the sensitivity due to several influences. The most important are frequency offset due to crystal oscillator (XTO) and crystal frequency (XTAL) errors, temperature and supply voltage dependency of the noise figure and IF filter bandwidth of the receiver. Figure 7-2 shows the typical sensitivity at 433.92 MHz/FSK/20 Kbit/s/ $\pm$ 19.5 kHz/Manchester versus the frequency offset between transmitter and receiver at  $T_{amb} = -40\,^{\circ}\text{C}$ ,  $+25\,^{\circ}\text{C}$  and  $+105\,^{\circ}\text{C}$  and supply voltage  $V_{S} = V_{S1} = V_{S2} = 2.15V$ , 3.0V and 3.6V.

**Figure 7-2.** Measured Sensitivity 433.92 MHz/FSK/20 Kbit/s/±19.5 kHz/Manchester versus Frequency Offset, Temperature and Supply Voltage

As can be seen in Figure 7-2 on page 12 the supply voltage has almost no influence on the sensitivity. The temperature has an influence of about  $\pm 1.5/-0.7$  dB and a frequency offset of  $\pm 85$  kHz also influences by about  $\pm 1$  dB. All these influences, combined with the sensitivity of a typical IC ( $\pm 105.5$ dBm), are then within a range of  $\pm 102.5$ dBm and  $\pm 107$ dBm overtemperature, supply voltage and frequency offset. The integrated IF filter has an additional production tolerance of  $\pm 10$  kHz, hence, a frequency offset between the receiver and the transmitter of  $\pm 75$  kHz can be accepted for XTAL and XTO tolerances.

Note: For the demodulator used in the ATA5823/ATA5824, the tolerable frequency offset does not change with the data frequency, hence, the value of ±75 kHz is valid for 1 Kbit/s to 20 Kbit/s.

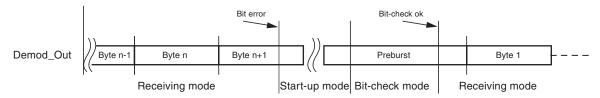

This small sensitivity change over supply voltage, frequency offset and temperature is very unusual in such a receiver. It is achieved by an internal, very fast and automatic frequency correction in the FSK demodulator after the IF filter, which leads to a higher system margin. This frequency correction tracks the input frequency very quickly, if however, the input frequency makes a larger step (e.g., if the system changes between different communication partners), the receiver has to be restarted. This can be done by switching back to IDLE mode and then again to RX mode. For that purpose, an automatic mode is also available. This automatic mode switches to IDLE mode and back into RX mode every time a bit error occurs (see section "Digital Control Logic" on page 35).

## 7.4 Frequency Accuracy of the Crystals in Bi-directional RKE/PEG

The XTO is an amplitude regulated Pierce type oscillator with integrated load capacitors. The initial tolerances (due to the frequency tolerance of the XTAL, the integrated capacitors on XTAL1, XTAL2 and the XTO's initial transconductance gm) can be compensated to a value within  $\pm 0.5$  ppm by measuring the CLK output frequency and tuning of  $f_{RF}$  by programming the control registers 2 and 3 (see Table 12-7 on page 38 and Table 12-10 on page 39). The XTO then has a remaining influence of less than  $\pm 2$  ppm overtemperature and supply voltage due to the bandgap controlled gm of the XTO. Thus only 2.5 ppm add to the frequency stability of the used crystals overtemperature and aging.

The needed frequency stability of the used crystals **overtemperature and aging** is hence  $\pm 75 \text{ kHz}/433.92 \text{ MHz} - 2 \times \pm 2.5 \text{ ppm} = \pm 167.84 \text{ ppm}$  for 433.92 MHz and  $\pm 75 \text{ kHz}/868.3 \text{ MHz} - 2 \times \pm 2.5 \text{ ppm} = \pm 81.4 \text{ ppm}$  for 868.3 MHz. Thus, the used crystals in receiver and transmitter each need to be better than  $\pm 83.9 \text{ ppm}$  for 433.92 MHz and  $\pm 40.7 \text{ ppm}$  for 868.3 MHz.

## 7.5 Frequency Accuracy of the Crystals in a Combined RKE/PEG and TPM System

In a tire pressure measurement system working at 433.92 MHz and using a TPM transmitter ATA5757 and a transceiver ATA5824 as a receiver, the higher frequency tolerances and the tolerance of the frequency deviation of this transmitter has to be considered.

In the TPM transmitter the crystal has an frequency error overtemperature  $-40^{\circ}$ C to  $+125^{\circ}$ C, aging and tolerance of  $\pm 80$  ppm ( $\pm 34.7$  kHz at 433.92 MHz). The tolerances of the XTO, the capacitors used for FSK-Modulation and the stray capacitors, causing an additional frequency error of  $\pm 30$  ppm ( $\pm 13$  kHz at 433.92 MHz). The frequency deviation of such a transmitter varies between  $\pm 16$  kHz and  $\pm 24$  kHz, since a higher frequency deviation is equivalent to an frequency error, this has to be considered as an additional  $\pm 24$  kHz –  $\pm 19.5$  kHz =  $\pm 4.5$ kHz frequency tolerance. All tolerances added, these transmitters have a worst case frequency offset of  $\pm 52.2$  kHz.

For the transceiver in the car a tolerance of  $\pm 75$  kHz –  $\pm 52.2$  kHz =  $\pm 22.8$  kHz ( $\pm 52.5$  ppm) remains. The needed frequency stability of the used crystals **overtemperature and aging** is  $\pm 52.5$  ppm –  $\pm 2.5$  ppm =  $\pm 50$  ppm. The aging of such a crystal is  $\pm 10$  ppm leaving reasonable  $\pm 40$  ppm for the temperature dependency of the crystal frequency in the car.

Since the transceiver in the car is able to receive these TPM transmitter signals with high frequency offsets, the component specification in the key can be largely relaxed.

This system calculation is based on worst case tolerances of all the components, this leads in practice to a system with margin.

For a 315 MHz TPM system using a TPM transmitter ATA5756 and a transceiver ATA5823 as receiver the same calculation must be done, but since the RF frequency is lower, every ppm of crystal tolerances results in less frequency offset and either the system can have higher tolerances or a higher margin there.

For 868 MHz it is not possible to use the transceiver ATA5824 in a combined RKE/PEG and TPM system since all the tolerances double because of the higher RF frequency.

#### 7.6 RX Supply Current versus Temperature and Supply Voltage

Table 7-5 shows the typical supply current at 433.92 MHz of the transceiver in RX mode versus supply voltage and temperature with  $V_S = V_{S1} = V_{S2}$ . As can be seen the supply current at  $V_S = 2.15 \text{V}$  and  $V_S = 2.15 \text{V}$  and  $V_S = 3 \text{V}$  and  $V_S = 3 \text{V}$  which helps to enlarge the battery lifetime within a key fob application because this is also the operation point where a lithium cell has the worst performance. The typical supply current at 315 MHz or 868.3 MHz in RX mode is about the same as for 433.92 MHz.

| $V_S = V_{S1} = V_{S2}$  | 2.15V   | 3.0V    | 3.6V    |

|--------------------------|---------|---------|---------|

| $T_{amb} = -40$ °C       | 8.2 mA  | 8.8 mA  | 9.2 mA  |

| T <sub>amb</sub> = 25°C  | 9.7 mA  | 10.3 mA | 10.8 mA |

| T <sub>amb</sub> = 105°C | 11.2 mA | 11.9 mA | 12.4 mA |

**Table 7-5.** Measured 433.92 MHz Receive Supply Current in FSK mode

## 7.7 Blocking, Selectivity

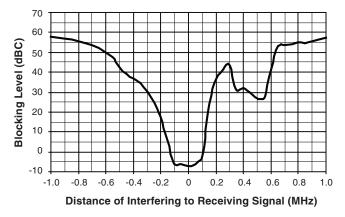

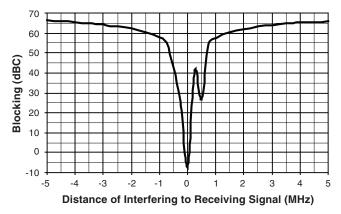

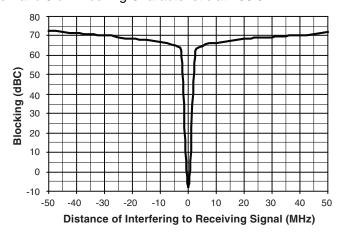

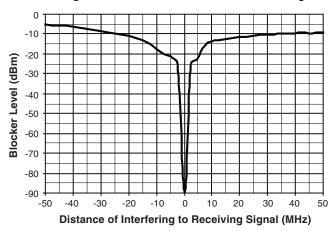

As can be seen in Figure 7-3, Figure 7-4 and Figure 7-5 on page 15, the receiver can receive signals 3 dB higher than the sensitivity level in presence of large blockers of -44.5 dBm/-36.0 dBm with small frequency offsets of  $\pm 1/ \pm 10$  MHz.

Figure 7-3 and Figure 7-4 on page 15 shows the close-in and narrow-band blocking and Figure 7-5 on page 15 the wide-band blocking characteristic. The measurements were done with a useful signal of 433.92 MHz/FSK/20 Kbit/s/ $\pm$ 19.5 kHz/Manchester with a level of -105.5 dBm + 3 dB = -102.5 dBm which is 3 dB above the sensitivity level. The figures show by how much a continuous wave signal can be larger than -102.5 dBm until the BER is higher than  $10^{-3}$ . The measurements were done at the  $50\Omega$  input according to Figure 7-1 on page 11. At 1 MHz, for example, the blocker can be 58 dBC higher than -102.5 dBm which is -102.5 dBm +58 dBC = -44.5 dBm. These blocking figures, together with the good intermodulation performance, avoid the additional need of a SAW filter in the key fob application.

Figure 7-3. Close In 3 dB Blocking Characteristic and Image Response at 433.92 MHz

Figure 7-4. Narrow Band 3 dB Blocking Characteristic at 433.92 MHz

Figure 7-5. Wide Band 3 dB Blocking Characteristic at 433.92 MHz

Table 7-6 shows the blocking performance measured relative to -102.5 dBm for some frequencies. Note that sometimes the blocking is measured relative to the sensitivity level -105.5 dBm (denoted dBS) instead of the carrier -102.5 dBm (denoted dBC).

**Table 7-6.** Blocking 3 dB Above Sensitivity Level with BER < 10<sup>-3</sup>

| Frequency Offset | Blocker Level | Blocking          |

|------------------|---------------|-------------------|

| +0.75 MHz        | –47.5 dBm     | 55.0 dBC/58.0 dBS |

| −0.75 MHz        | –47.5 dBm     | 55.0 dBC/58.0 dBS |

| +1.0 MHz         | –44.5 dBm     | 58.0 dBC/61.0 dBS |

| -1.0 MHz         | –44.5 dBm     | 58.0 dBC/61.0 dBS |

| +1.5 MHz         | -42.0 dBm     | 60.5 dBC/63.5 dBS |

| -1.5 MHz         | -42.0 dBm     | 60.5 dBC/63.5 dBS |

| +10 MHz          | −35.5 dBm     | 67.0 dBC/70.0 dBS |

| -10 MHz          | −35.5 dBm     | 67.0 dBC/70.0 dBS |

The ATA5823/ATA5824 can also receive FSK and ASK modulated signals if they are much higher than the I1dBCP. It can typically receive useful signals at +10 dBm. This is often referred to as the nonlinear dynamic range which is the maximum to minimum receiving signal which is 115.5 dB for 433.92 MHz/FSK/20 Kbit/s/±19.5 kHz/ Manchester. This value is useful if two transceivers have to communicate and are very close to each other.

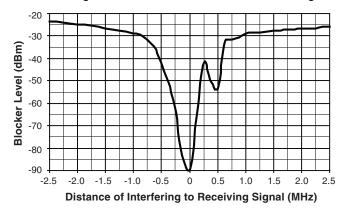

In a keyless entry system there is another blocking characteristic that has to be considered. A keyless entry system has a typical service range of about 30 m with a receiver sensitivity of about –106 dBm to –109 dBm. In some cases, large blockers limit this service range, and it is important to know how large this blockers can be until the system doesn't work anymore and the user has to use its key. With a recommended sensitivity of about –85 dBm, the system works just around the car. Figure 7-6 and Figure 7-7 on page 17 show the blocking performance in this important case with a useful signal of –85dBm 433.92 MHz/FSK/20 Kbit/s/±19.5 kHz/ Manchester.

As can be seen the system works even with blockers above the compression point. This is due to a wide bandwidth automatic gain control that begins to work if blockers above the compression point are at the antenna input and increasing the current in the LNA/Mixer to get a better compression point needed to handle these large blockers.

Figure 7-6. ±2.5 MHz Blocking Characteristic for –85 dBm Useful Signal at 433.92 MHz

Figure 7-7. ±50 MHz Blocking Characteristic for –85 dBm Useful Signal at 433.92 MHz

This high blocking performance makes it even possible for some applications using quarter wave whip antennas to use a simple LC band-pass filter instead of a SAW filter in the receiver. When designing such a LC filter, take into account that the 3 dB blocking at 433.92 MHz/2 = 216.96 MHz is 42 dBC and at 433.92 MHz/3 = 144.64 MHz is 47 dBC and at  $2 \times (433.92 \text{ MHz} + 226 \text{ kHz}) + -226 \text{ kHz} = 868.066 \text{ MHz/868.518 MHz}$  is 50 dBC. And especially that at  $3 \times (433.92 \text{ MHz} + 226 \text{ kHz}) + 226 \text{ kHz} = 1302.664 \text{ MHz}$  the receiver has a second LO harmonic receiving frequency with only 17 dBC blocking.

#### 7.8 Inband Disturbers, Data Filter, Quasi-peak Detector, Data Slicer

If a disturbing signal falls into the received band, or a blocker is not a continuous wave, the performance of a receiver strongly depends on the circuits after the IF filter. Hence the demodulator, data filter and data slicer are important in that case.

The data filter of the ATA5823/ATA5824 implies a quasi-peak detector. This results in a good suppression of above mentioned disturbers and exhibits a good carrier to noise performance. The required ratio of useful signal to disturbing signal, at a BER of 10<sup>-3</sup> is less than 12 dB in ASK mode and less than 3 dB (BR\_Range\_0 ... BR\_Range\_2) and 6 dB (BR\_Range\_3) in FSK mode. Due to the many different possible waveforms these numbers are measured for signal as well as for disturbers with peak amplitude values. Note that these values are worst case values and are valid for any type of modulation and modulating frequency of the disturbing signal as well as the receiving signal. For many combinations, lower carrier to disturbing signal ratios are needed.

#### 7.9 TEST3 Output

The internal raw output signal of the demodulator Demod\_Out is available at pin TEST3. TEST3 is an open drain output and must be connected to a pull-up resistor if it is used (typically 100 k $\Omega$ ), otherwise no signal is present at that pin. This signal is mainly used for debugging purposes during the setup of a new application, since the received data signal can be seen there without any digital processing.

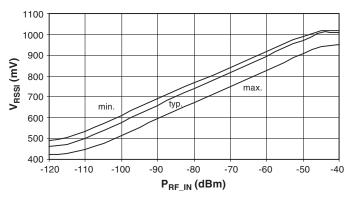

## 7.10 RSSI Output

The output voltage of the pin RSSI is an analog voltage, proportional to the input power level. Using the RSSI output signal, the signal strength of different transmitters can be distinguished. The usable dynamic range of the RSSI amplifier is 70 dB, the input power range  $P_{RFIN}$  is –115 dBm to –45 dBm and the gain is 8 mV/dB. Figure 7-8 on page 18 shows the RSSI characteristic of a typical device at 433.92 MHz with  $V_{S1} = V_{S2} = 2.15V$  to 3.6V and  $T_{amb} = -40^{\circ}C$  to +105°C with a matched input according to Table 7-2 on page 12 and Figure 7-1 on page 11. At 868.3 MHz about 2.7 dB more signal level and at 315 MHz about 1 dB less signal level is needed for the same RSSI results.

**Figure 7-8.** Typical RSSI Characteristic at 433.92 MHz versus Temperature and Supply Voltage

## 7.11 Frequency Synthesizer and Channel Selection

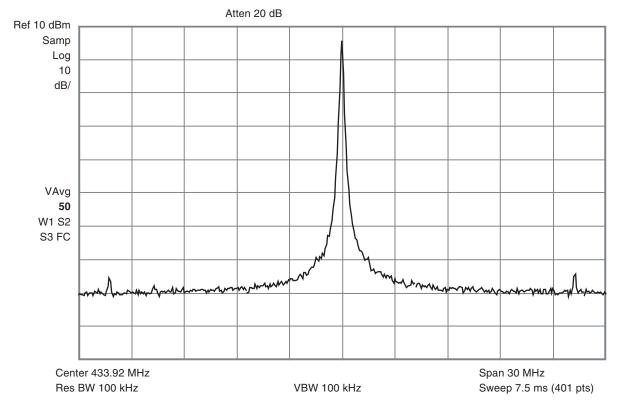

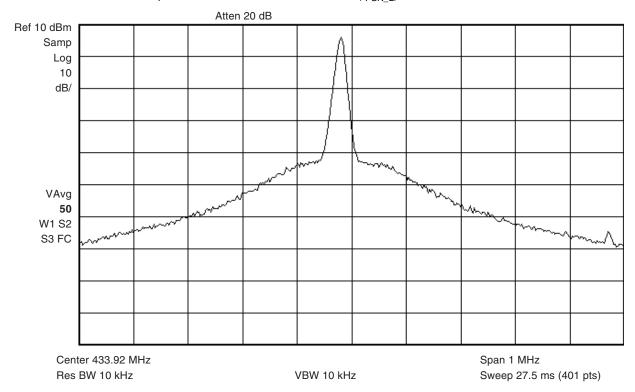

The synthesizer is a fully integrated fractional-N design with internal loop filters for receive and transmit mode. The XTO frequency  $f_{\rm XTO}$  is the reference frequency FREF for the synthesizer. The bits FR0 to FR12 in control registers 2 and 3 (see Table 12-7 on page 38 and Table 12-10 on page 39) are used to adjust the deviation of  $f_{\rm XTO}$ . In half-duplex transmit mode, at 433.92 MHz, the carrier has a phase noise of –111 dBC/Hz at 1 MHz and spurious at FREF of –70 dBC with a high PLL loop bandwidth allowing the direct modulation of the carrier with 20 Kbit/s Manchester data. Due to the closed loop modulation, any spurious caused by this modulation are effectively filtered out as can be seen in Figure 7-11 on page 20. In RX mode the synthesizer has a phase noise of –120 dBC/Hz at 1 MHz and spurious of –72 dBC.

The initial tolerances of the crystal oscillator due to crystal frequency tolerances, internal capacitor tolerances and the parasitics of the board have to be compensated at manufacturing setup with control registers 2 and 3 as can be seen in Table 9-1 on page 30. The other control words for the synthesizer needed for ASK, FSK and receive/transmit switching are calculated internally. The RF (Radio Frequency) resolution is equal to the XTO frequency divided by 16384 which is 777.1 Hz at 315.0 MHz, 808.9 Hz at 433.92 MHz and 818.59 Hz at 868.3 MHz.

The frequency control word FREQ in control registers 2 and 3 can be programmed in the range of 1000 to 6900, hence every frequency within the 433 MHz and 868 MHz ISM bands can be programmed as receive and as transmit frequency and the position of channels within these ISM bands can be chosen arbitrarily (see Table 9-1 on page 30).

Care must be taken regarding the harmonics of the CLK output signal as well as to the harmonics produced by a microprocessor clocked with it, since these harmonics can disturb the reception of signals. In a single channel system using FREQ = 3803 to 4053 ensures that harmonics of this signal, do not disturb the receive mode.

#### 7.12 FSK/ASK Transmission

Due to the fast modulation capability of the synthesizer and the high resolution, the carrier can be internally FSK modulated which simplifies the application of the transceiver. The deviation of the transmitted signal is  $\pm 24$  digital frequency steps of the synthesizer which is equal to  $\pm 18.65$  kHz for 315 MHz,  $\pm 19.41$  kHz for 433.92 MHz and  $\pm 19.64$  kHz for 868.3 MHz.

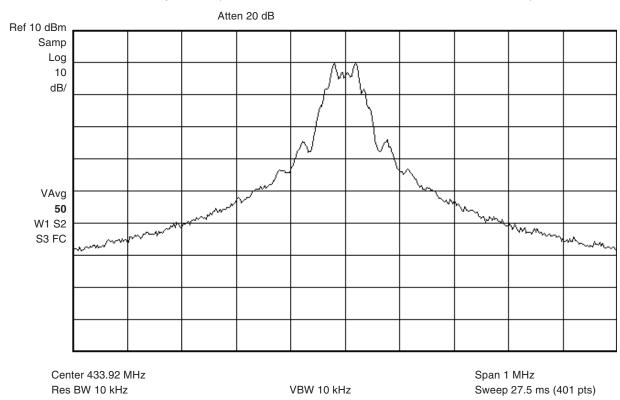

Due to closed loop modulation with PLL filtering, the modulated spectrum is very clean, meeting ETSI and CEPT regulations when using a simple LC filter for the power amplifier harmonics as it is shown in Figure 4-1. In ASK mode the frequency is internally connected to the center of the FSK transmission and the power amplifier is switched on and off to perform the modulation. Figure 7-9 to Figure 7-11 on page 20 show the spectrum of the FSK modulation with pseudo-random data with 20 Kbit/s/±19.41 kHz/Manchester and 5 dBm output power.

Figure 7-9. FSK-modulated TX Spectrum (433.92 MHz/20 Kbit/s/±19.41 kHz/Manchester Code)

Figure 7-10. Unmodulated TX Spectrum 433.92 MHz - 19.41 kHz (f<sub>FSK\_L</sub>)

Figure 7-11. FSK-modulated TX Spectrum (433.92 MHz/20 Kbit/s/±19.41 kHz/Manchester Code)

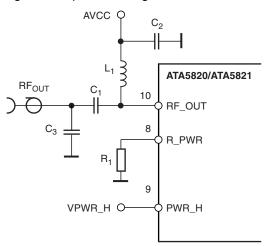

## 7.13 Output Power Setting and PA Matching at RF\_OUT

The Power Amplifier (PA) is a single-ended open collector stage which delivers a current pulse which is nearly independent of supply voltage, temperature and tolerances due to band-gap stabilization. Resistor R<sub>1</sub> (see Figure 7-12 on page 22) sets a reference current which controls the current in the PA. A higher resistor value results in a lower reference current, a lower output power and a lower current consumption of the PA. The usable range of R<sub>1</sub> is 15 k $\Omega$ to 56 k $\Omega$  The PWR\_H pin switches the output power range between about 0 dBm to 5 dBm (PWR\_H = GND) and 5 dBm to 10 dBm (PWR\_H = AVCC) by multiplying this reference current with a factor 1 (PWR\_H = GND) and 2.5 (PWR\_H = AVCC) which corresponds to about 5 dB more output power.

If the PA is switched off in TX mode, the current consumption without output stage and with  $V_{S1} = V_{S2} = 3V$ ,  $T_{amb} = 25^{\circ}C$  is typically 6.5 mA for 868.3 MHz and 6.95 mA for 315 MHz and 433.92 MHz.

The maximum output power is achieved with optimum load resistances  $R_{Lopt}$  according to Table 7-7 on page 22. The compensation of the 1.0 pF output capacitance of the RF\_OUT pin will be achieved by absorbing it into the matching network, consisting of  $L_1$ ,  $C_1$ ,  $C_3$  as shown in Figure 7-12 on page 22. There must be also a low resistive DC path to AVCC to deliver the DC current of the power amplifier's last stage. The matching of the PA output was done with the circuit according to Figure 7-12 on page 22 with the values in Table 7-7. Note that value changes of these elements may be necessary to compensate individual board layout parasitics.

#### Example:

According to Table 7-7 on page 22, with a frequency of 433.92 MHz and output power of 11 dBm, the overall current consumption is typically 17.8 mA. Hence the PA needs 17.8 mA - 6.95 mA = 10.85 mA in this mode which corresponds to an overall power amplifier efficiency of the PA of  $(10^{(11dBm/10)} \times 1 \text{ mW})/(3V \times 10.85 \text{ mA}) \times 100\% = 38.6\%$  in this case.

Using a higher resistor in this example of R1 =  $1.091 \times 22 \text{ k}\Omega$  = 24 k $\Omega$  results in 9.1% less current in the PA of 10.85 mA/1.091 = 9.95 mA and 10 × log(1.091) = 0.38 dB less output power if using a new load resistance of  $300\Omega \times 1.091 = 327\Omega$ . The resulting output power is then 11 dBm – 0.38 dB = 10.6 dBm and the overall current consumption is 6.95 mA + 9.95 mA = 16.9 mA.

The values of Table 7-7 on page 22 were measured with standard multi-layer chip inductors with quality factors Q according to Table 7-7 on page 22.

Looking to the 433.92 MHz/11 dBm case with the quality factor of  $Q_{L1}=43$  the loss in this inductor  $L_1$  is estimated with the parallel equivalent resistance of the inductor  $R_{loss}=2\times\pi\times f\times L1\times Q_{L1}$  and the matching loss with 10 log (1 +  $R_{Lopt}/R_{loss}$ ) which is equal to 0.32 dB losses in this inductor. Taking this into account the PA efficiency is then 42% instead of 38.6%.

Be aware that the high power mode (PWR\_H = AVCC) can only be used with a supply voltage higher than 2.7V, whereas the low power mode (PWR\_H = GND) can be used down to 2.15V as can be seen in the section "Electrical Characteristics: General" on page 72.

The supply blocking capacitor  $C_2$  (10 nF) in Figure 7-12 on page 22 has to be placed close to the matching network because of the RF current flowing through it.

An internal programmable resistor SETPWR is programmable with the control register 8, described in Table 12-25 on page 43. It can be used in conjunction with an external resistor to adjust the output power by connection it like in the application Figure 5-1 on page 8 or Figure 6-1 on page 9. To do that the output power should be adjusted with an external resistor about 50% lower than needed for the target output power and reduced with the programmable resistor during production test until the target power is as close as possible to the target. For example, if using 433.92 MHz at 5 dBm, a resistor of 12k instead of 24k is used and values of PWSET between 25 and 29 can be used to achieve an output power within 5 dBm  $\pm$ 0.5 dB over production. In full-duplex mode this internal resistor is used to reduce the output power for full-duplex operation versus the power in half-duplex operation. Note that this resistor is temperature stable but has tolerances of  $\pm$ 20% and introduces, therefore, additional output power tolerances, it is recommended to adjust output power during the production test if using the SETPWR resistor.

Figure 7-12. Power Setting and Output Matching

**Table 7-7.** Measured Output Power and Current Consumption with  $V_{S1} = V_{S2} = 3V$ ,  $T_{amb} = 25^{\circ}C$

| Frequency<br>(MHz) | TX Current (mA) | Output Power (dBm) | R1<br>(kΩ) | VPWR_H | R <sub>Lopt</sub> (Ω) | L <sub>1</sub><br>(nH) | Q <sub>L1</sub> | C <sub>1</sub> (pF) | C <sub>3</sub><br>(pF) |

|--------------------|-----------------|--------------------|------------|--------|-----------------------|------------------------|-----------------|---------------------|------------------------|

| 315                | 8.5             | 0.4                | 56         | 0      | 2500                  | 82                     | 28              | 1.5                 | 0                      |

| 315                | 10.5            | 5.7                | 27         | 0      | 920                   | 68                     | 32              | 2.2                 | 0                      |

| 315                | 16.7            | 10.5               | 27         | AVCC   | 350                   | 56                     | 35              | 3.9                 | 0                      |

| 433.92             | 8.6             | 0.1                | 56         | 0      | 2300                  | 56                     | 40              | 0.75                | 0                      |

| 433.92             | 11.2            | 6.2                | 22         | 0      | 890                   | 47                     | 38              | 1.5                 | 0                      |

| 433.92             | 17.8            | 11                 | 22         | AVCC   | 300                   | 33                     | 43              | 2.7                 | 0                      |

| 868.3              | 9.3             | -0.3               | 33         | 0      | 1170                  | 12                     | 58              | 1.0                 | 3.3                    |

| 868.3              | 11.5            | 5.4                | 15         | 0      | 471                   | 15                     | 54              | 1.0                 | 0                      |

| 868.3              | 16.3            | 9.5                | 22         | AVCC   | 245                   | 10                     | 57              | 1.5                 | 0                      |

## 7.14 Output Power and TX Supply Current versus Supply Voltage and Temperature

Table 7-8 shows the measurement of the output power for a typical device with  $V_{S1} = V_{S2} = V_S$  in the 433.92 MHz and 6.2 dBm case versus temperature and supply voltage measured according to Figure 7-12 on page 22 with components according to Table 7-7 on page 22. As opposed to the receiver sensitivity the supply voltage has here the major impact on output power variations because of the large signal behavior of a power amplifier. Thus a 5V system using the internal voltage regulator shows much less variation than a 2.15V to 3.6V battery system because the AVCC supply voltage is 3.25V  $\pm 0.25$ V for a 5V system.

The reason is that the amplitude at the output RF\_OUT with optimum load resistance is AVCC – 0.4V and the power is proportional to  $(AVCC – 0.4V)^2$  if the load impedance is not changed. This means that the theoretical output power reduction if reducing the supply voltage from 3.0V to 2.15V is  $10 \log ((3V – 0.4V)^2/(2.15V – 0.4V)^2) = 3.4$  dB. Table 7-8 shows that principle behavior in the measurements. This is not the same case for higher voltages, since here, increasing the supply voltage from 3V to 3.6V should theoretical increase the power by 1.8 dB, but only 0.9 dB in the measurements shows that the amplitude does not increase with the supply voltage because the load impedance is optimized for 3V and the output amplitude stays more constant because of the current source nature of the output.

**Table 7-8.** Measured Output Power and Supply Current at 433.92 MHz, PWR\_H = GND

| $V_S = V_{S1} = V_{S2}$   | 2.15V   | 3.0V     | 3.6V     |

|---------------------------|---------|----------|----------|

| $T_{amb} = -40^{\circ}C$  | 9.25 mA | 10.19 mA | 10.78 mA |

|                           | 3.2 dBm | 5.5 dBm  | 6.2 dBm  |

| T <sub>amb</sub> = +25°C  | 10.2 mA | 11.19 mA | 11.79 mA |

|                           | 3.4 dBm | 6.2 dBm  | 7.1 dBm  |

| T <sub>amb</sub> = +105°C | 10.9 mA | 12.02 mA | 12.73 mA |

|                           | 3.0 dBm | 5.4 dBm  | 6.3 dBm  |

Table 7-9 shows the relative changes of the output power of a typical device compared to 3.0V/25°C. As can be seen, a temperature change to –40°C as well as to +105°C reduces the power by less than 1 dB due to the band-gap regulated output current. Measurements of all the cases in Table 7-7 on page 22 overtemperature and supply voltage have shown about the same relative behavior as shown in Table 7-9.

**Table 7-9.** Measurements of Typical Output Power Relative to 3 V/25°C

| $V_S = V_{S1} = V_{S2}$  | 2.15V   | 3.0V    | 3.6V    |

|--------------------------|---------|---------|---------|

| $T_{amb} = -40^{\circ}C$ | −3.0 dB | −0.7 dB | 0 dB    |

| $T_{amb} = +25^{\circ}C$ | –2.8 dB | 0 dB    | +0.9 dB |

| $T_{amb} = +105$ °C      | −3.2 dB | -0.8 dB | +0.1 dB |

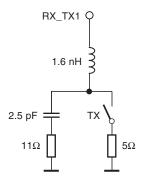

#### 7.15 RX/TX Switch

The RX/TX switch decouples the LNA from the PA in TX mode, and directs the received power to the LNA in RX mode. To do this, it has a low impedance to GND in TX mode and a high impedance to GND in RX mode. The pin 38 (RX\_TX2) must always be connected to GND in the application. To design a proper RX/TX decoupling a linear simulation tool for radio frequency design together with the measured device impedances of Table 7-1 on page 11, Table 7-7 on page 22, Table 7-10 on page 24 and Table 7-11 on page 25 should be used. The exact element values have to be found on board. Figure 7-13 on page 24 shows an approximate equivalent circuit of the switch. The principal switching operation is described here according to the application of Figure 3-1 on page 6. The application of Figure 4-1 on page 7 works similarly.

Table 7-10. Impedance of the RX/TX Switch RX\_TX2 Shorted to GND

| Frequency  | Z(RX_TX1) TX mode    | Z(RX_TX1) RX mode |

|------------|----------------------|-------------------|

| 315 MHz    | $(4.8 + j3.2)\Omega$ | (11.3 – j214)Ω    |

| 433.92 MHz | $(4.5 + j4.3)\Omega$ | (10.3 – j153)Ω    |

| 868.3 MHz  | (5 + j9)Ω            | (8.9 − j73)Ω      |

Figure 7-13. Equivalent Circuit of the Switch

#### 7.16 Matching Network in TX Mode

In TX mode the 20 mm long and 0.4 mm wide transmission line which is much shorter than  $\lambda/4$  is approximately switched in parallel to the capacitor  $C_9$  to GND. The antenna connection between  $C_8$  and  $C_9$  has an impedance of about  $50\Omega$  looking from the transmission line into the loop antenna with pin RF\_OUT,  $L_2$ ,  $C_{10}$ ,  $C_8$  and  $C_9$  connected (using a  $C_9$  without the added 7.6 pF capacitor as discussed later). The transmission line can be approximated with a 16 nH inductor in series with a  $1.5\Omega$  resistor, the closed switch can be approximated according to Table 7-10 with the series connection of 1.6 nH and  $5\Omega$  in this mode. To have a parallel resonant high impedance circuit with little RF power going into it looking, from the loop antenna into the transmission line a capacitor of about 7.6 pF to GND is needed at the beginning of the transmission line (this capacitor is later absorbed into  $C_9$ , which is then higher as needed for  $50\Omega$  transformation). To keep the  $50\Omega$  impedance in RX mode at the end of this transmission line  $C_7$  has to be also about 7.6 pF. This reduces the TX power by about 0.5 dB at 433.92 MHz compared to the case where the LNA path is completely disconnected.

#### 7.17 Matching Network in RX Mode

In RX mode the RF\_OUT pin has a high impedance of about 7 k $\Omega$  in parallel with 1.0 pF at 433.92 MHz as can be seen in Table 7-11 on page 25. This together with the losses of the inductor L $_2$  with 120 nH and Q $_{L2}$  = 25 gives about 3.7 k $\Omega$  loss impedance at RF\_OUT. Since the optimum load impedance in TX mode for the power amplifier at RF\_OUT is 890 $\Omega$  the loss associated with the inductor L $_2$  and the RF\_OUT pin can be estimated to be  $10 \times \log(1+890/3700)=0.95$  dB compared to the optimum matched loop antenna without L $_2$  and RF\_OUT. The switch represents, in this mode at 433.92 MHz, about an inductor of 1.6 nH in series with the parallel connection of 2.5 pF and 2.0 k $\Omega$ . Since the impedance level at pin RX\_TX1 in RX mode is about  $50\Omega$  there is only a negligible damping of the received signal by about 0.1 dB. When matching the LNA to the loop antenna the transmission line and the 7.6 pF part of C $_9$  has to be taken into account when choosing the values of C $_{11}$  and L $_1$  so that the impedance seen from the loop antenna into the transmission line with the 7.6 pF capacitor connected is  $50\Omega$

Since the loop antenna in RX mode is loaded by the LNA input impedance the loaded Q of the loop antenna is lowered by about a factor of 2 in RX mode hence the antenna bandwidth is higher than in TX mode.

Table 7-11. Impedance RF\_OUT Pin in RX mode

| Frequency  | Z(RF_OUT)RX  | R <sub>P</sub> //C <sub>P</sub> |

|------------|--------------|---------------------------------|

| 315 MHz    | 36Ω –j 502 Ω | 7 kΩ/ / 1.0 pF                  |

| 433.92 MHz | 19Ω –j 366 Ω | 7 kΩ/ / 1.0 pF                  |

| 868.3 MHz  | 2.8Ω –j 141Ω | 7 kΩ/ / 1.3 pF                  |

Note that if matching to  $50\Omega$ , like in Figure 4-1 on page 7, a high Q wire wound inductor with a Q > 70 should be used for L<sub>2</sub> to minimize its contribution to RX losses which will otherwise be dominant. The RX and TX losses will be in the range of 1.0 dB there.

# 8. RF Transceiver in Full-duplex Mode

The full-duplex mode of the ATA5823/ATA5824 is intended to be used for the purpose of security against a so called relay attack in passive entry systems. A property of such a passive entry system is that the user has not to push a key fob button like in a keyless entry system. If the user approaches to the door of the car it will wake up the key (in most cases with a low frequency 125 kHz signal) and the communication between the key and the car starts without interaction of the user and afterwards the door opens.

Due to this new feature of the system there is a new possibility of entering a car without permission. One can trigger this communication, take the 125 kHz signal from the car, remodulate it on another carrier and transmit it over a much longer distance than intended by the system. Than receive this signal and remodulate it onto the 125 kHz carrier and retransmit this signal close to the user having the key fob with permission for the car. Such a system is called an RF-Relay and therefore this kind of attack is called relay attack. The high frequency signals of the ATA5823/ATA5824 could be treated the same way if only a half-duplex mode is used within a passive entry system. If using half-duplex RF transceivers, the attacker can switch the direction of the relay with a transmit power detector.

To prevent that the ATA5823/ATA5824 receives and transmit its RF-signals on the same frequency and at the same time. Since the attacker has then to receive and transmit RF signals at the same frequency and time it will be much more difficult to built the hardware for this kind of attack, since its own transmitted output power couples back to its receiver.

#### This mode works as follows:

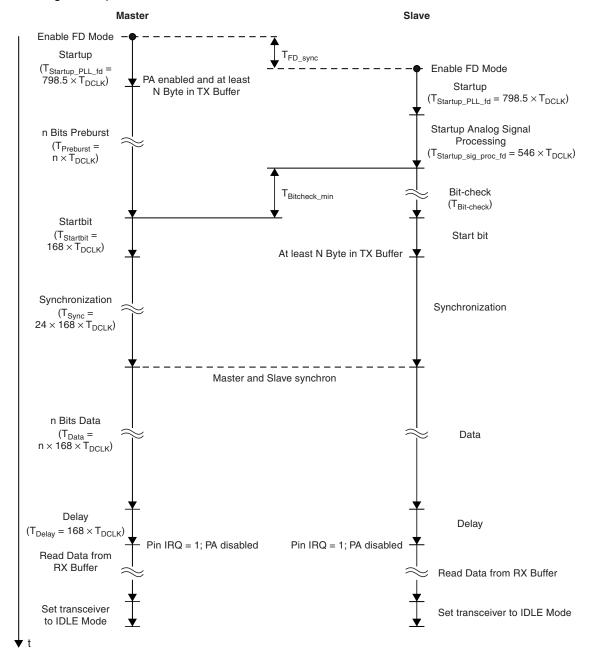

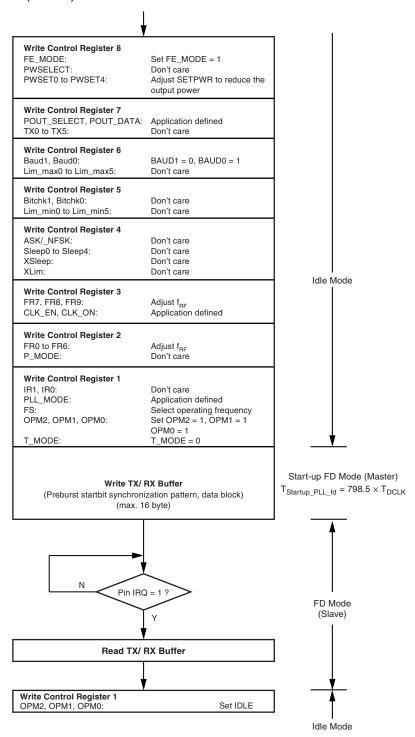

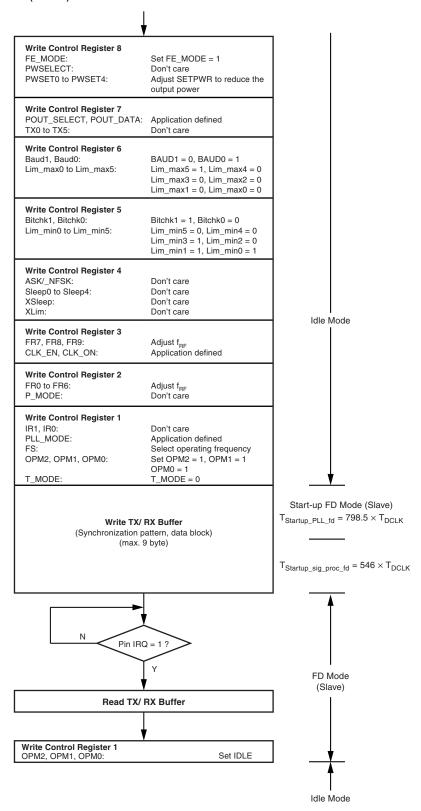

Both transceivers transmit FSK with a modulation deviation of half the IF (a frequency deviation of about ±113 kHz), switches the image rejection in the receive path off and uses the transmit frequency as local oscillator for the receiver. If both transceivers send FSK-low or both send FSK-high, the resulting IF is close to zero and is filtered out by the IF-filter. Both receivers receive than a low-signal by using the ASK demodulator as receiver. If the transceivers send different symbols e.g. FSK-low/FSK-high or FSK-high/FSK-low the resulting IF is close to 226 kHz and the ASK demodulator receives a high-signal. Since the transceivers are synchronized at the beginning of the data transfer, they can calculate the transmitted data of the other transceiver from their own transmitted data and the data received from the ASK demodulator.

To use that mode, the received power from the transmitter side of a transceiver should not couple with a to high magnitude to its LNA otherwise the receive path will be desensitized. Therefore, two different antennas for transmit and receive are used with good decoupling (see Figure 5-1 on page 8 and Figure 6-1 on page 9).

Since defined packets are transmitted in FD-mode and the critical point in the transmission is the synchronization and not the data transfer, the sensitivity in FD-mode is defined for packets with 8 bytes of useful data (usually the response from a crypto-challenge response transmission) and for a **P**acket **E**rror **R**ate PER of 5%. For the full-duplex mode the data rate is fixed to 5 Kbit/s

The sensitivity of the receiver in full-duplex mode is dependant on the absolute power value and the phase of the power coupled from the PA to the LNA. Due to the phase dependency, three values are given in the Table 8-1, the first is the typical and the second and third one shows the sensitivity variation.

**Table 8-1.** Typical Full-duplex Sensitivity Dependent on the Parasitic Received Power and Coupling Phase from the PA 433.92 MHz/Full-duplex Mode/5 Kbit/s PER = 5% at 3V, 25°C

| Power from RF <sub>OUT</sub> at RF <sub>IN</sub> /dBm | Typical Sensitivity/dBm | Sensitivity Variation/dBm |

|-------------------------------------------------------|-------------------------|---------------------------|

| -30                                                   | <b>–</b> 91             | -88.5/-92.5               |

| -35                                                   | <b>-96</b>              | -93.5/-97.5               |

| -40                                                   | -100                    | <b>-97.5/-101.5</b>       |

| -45                                                   | -103                    | -100.5/-104.5             |

| -50                                                   | -104                    | -101.5/-105.5             |

The IC internal decoupling of the RF<sub>IN</sub> from RF<sub>OUT</sub> with a power amplifier load impedance optimized for +5dBm is 65 dB on a well designed PCB, hence the coupling is mainly due to the cross-coupling of the antennas.

**Table 8-2.** Typical Measured Supply Current and Output Power in Full-duplex Mode 433.92 MHz/Power Amplifier is Load Optimized for +5 dBm,  $R_1 = 22k$ , PWRSET = 20, (Battery Application)

| $V_S = V_{S1} = V_{S2} = V_{SINT}$ | 2.15V            | 3.0V             | 3.6V             |

|------------------------------------|------------------|------------------|------------------|

| $T_{amb} = -40$ °C                 | 10.2 mA/-6.2 dBm | 10.9 mA/-5.2 dBm | 11.4 mA/-4.6 dBm |

| T <sub>amb</sub> = +25°C           | 11.8 mA/-6.4 dBm | 12.5 mA/-5.2 dBm | 13.1 mA/-4.5 dBm |

| $T_{amb} = +105$ °C                | 13.4 mA/–7.5 dBm | 14.2 mA/-5.9 dBm | 14.8 mA/-5.0 dBm |

**Table 8-3.** Typical Measured Supply Current and Output Power in Full-duplex Mode/ 433.92 MHz/Power Amplifier is Load Optimized for +5 dBm, R<sub>1</sub> = 22k, PWRSET = 31, (Car Application)

| $V_S = V_{S2} = V_{SINT}$ | 4.4V             | 5V              | 5.25V           |

|---------------------------|------------------|-----------------|-----------------|

| $T_{amb} = -40^{\circ}C$  | 13.6 mA/3.7 dBm  | 13.6 mA/3.7 dBm | 13.6 mA/3.7 dBm |

| $T_{amb} = +25^{\circ}C$  | 15.6 mA/4.3 dBm  | 15.6 mA/4.3 dBm | 15.6 mA/4.3 dBm |

| $T_{amb} = +105$ °C       | 17.6 mA/ 4.6 dBm | 17.6 mA/4.6 dBm | 17.6 mA/4.6 dBm |

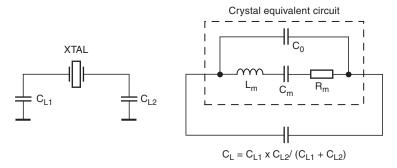

#### **XTO**

The XTO is an amplitude regulated Pierce oscillator type with integrated load capacitances  $(2 \times 18 \text{ pF})$  with a tolerance of  $\pm 17\%$ ) hence  $C_{\text{Lmin}} = 7.4 \text{ pF}$  and  $C_{\text{Lmax}} = 10.6 \text{ pF}$ . The XTO oscillation frequency f<sub>XTO</sub> is the reference frequency FREF for the fractional-N synthesizer. When designing the system in terms of receiving and transmitting frequency offset the accuracy of the crystal and XTO have to be considered.

The synthesizer can adjust the local oscillator frequency for the initial frequency error in f<sub>XTO</sub>. This is done at nominal supply voltage and temperature with the control registers 2 and 3 (see Table 12-7 on page 38 and Table 12-10 on page 39). The remaining local oscillator tolerance at nominal supply voltage and temperature is then < ±0.5 ppm. The XTO's gm has very low influence of less than ±2 ppm on the frequency at nominal supply voltage and temperature.

In a single channel system less than ±150 ppm should be corrected to avoid that harmonics of the CLK output disturb the receive mode. If the CLK is not used, or carefully layouted on the application PCB (as needed for multi channel systems), more than ±150 ppm can be compensated.

The additional XTO pulling is only ±2 ppm, overtemperature and supply voltage. The XTAL versus temperature and its aging is then the main source of frequency error in the local oscillator.

The XTO frequency depends on XTAL properties and the load capacitances C<sub>L1,2</sub> at pin XTAL1 and XTAL2. The pulling of  $f_{XTO}$  from the nominal  $f_{XTAL}$  is calculated using the following formula:  $P = \frac{C_m}{2} \times \frac{C_{LN} - C_L}{(C_0 + C_{LN}) \times (C_0 + C_L)} \times 10^6 \text{ ppm}.$

$$P = \frac{C_{m}}{2} \times \frac{C_{LN} - C_{L}}{(C_{0} + C_{LN}) \times (C_{0} + C_{L})} \times 10^{6} \text{ ppm}$$

$C_{m}$  is the crystal's motional,  $C_{0}$  the shunt and  $C_{LN}$  the nominal load capacitance of the XTAL found in its datasheet.  $C_L$  is the total actual load capacitance of the crystal in the circuit and consists of  $C_{L1}$  and  $C_{L2}$  in series connection.

Figure 9-1. XTAL with Load Capacitances

With  $C_m \le 14$  fF,  $C_0 \ge 1.5$  pF,  $C_{LN} = 9$  pF and  $C_L = 7.4$  pF to 10.6 pF the pulling amounts to  $P \le \pm 100$  ppm and with  $C_m \le 7$  fF,  $C_0 \ge 1.5$  pF,  $C_{LN} = 9$  pF and  $C_L = 7.4$  pF to 10.6 pF the pulling is  $P \le \pm 50$  ppm.

Since typical crystals have less than  $\pm 50$  ppm tolerance at 25°C, the compensation is not critical and can, in both cases, be done with the  $\pm 150$  ppm.

$C_0$  of the XTAL has to be lower than  $C_{Lmin}/2 = 3.7$  pF for a Pierce oscillator type in order to not enter the steep region of pulling versus load capacitance where there is a risk of an unstable oscillation.

To ensure proper start-up behavior the small signal gain, and thus the negative resistance provided by this XTO at start is very large. For example oscillation starts up, even in worst case, with a crystal series resistance of 1.5 k $\Omega$  at C<sub>0</sub>  $\leq$ 2.2 pF with this XTO. The negative resistance is approximately given by

$$\text{Re}\{\!Z_{\text{XTOcore}}\} = \text{Re}\!\left\{\!\frac{Z_1 \!\times Z_3 \!+\! Z_2 \!\times Z_3 \!+\! Z_1 \!\times Z_2 \!\times Z_3 \!\times g_m}{Z_1 \!+\! Z_2 \!+\! Z_3 \!+\! Z_1 \!\times Z_2 \!\times g_m}\right\}$$

with Z<sub>1</sub>, Z<sub>2</sub> as complex impedances at pin XTAL1 and XTAL2 hence Z<sub>1</sub> = -j/(2 ×  $\pi$  × f<sub>XTO</sub> × C<sub>L1</sub>) + 5 $\Omega$  and Z<sub>2</sub> = -j/(2 ×  $\pi$  × f<sub>XTO</sub> × C<sub>L2</sub>) + 5 $\Omega$

$Z_3$  consists of crystals  $C_0$  in parallel with an internal 110 k $\Omega$  resistor hence  $Z_3 = -j/(2 \times \pi \times f_{XTO} \times C_0)$  /110 k $\Omega$ , gm is the internal transconductance between XTAL1 and XTAL2 with typically 19 ms at 25°C.

With  $f_{XTO}$  = 13.5 MHz, gm = 19 ms,  $C_L$  = 9 pF,  $C_0$  = 2.2 pF this results in a negative resistance of about 2 k $\Omega$ . The worst case for technological, supply voltage and temperature variations is then for  $C_0 \le 2.2$  pF always higher than 1.5 k $\Omega$

Due to the large gain at start, the XTO is able to meet a very low start-up time. The oscillation start-up time can be estimated with the time constant  $\tau$ .

$$\tau = \frac{2}{4 \times \pi^2 \times f_m^2 \times C_m \times (Re(Z_{XTOcore}) + R_m)}$$

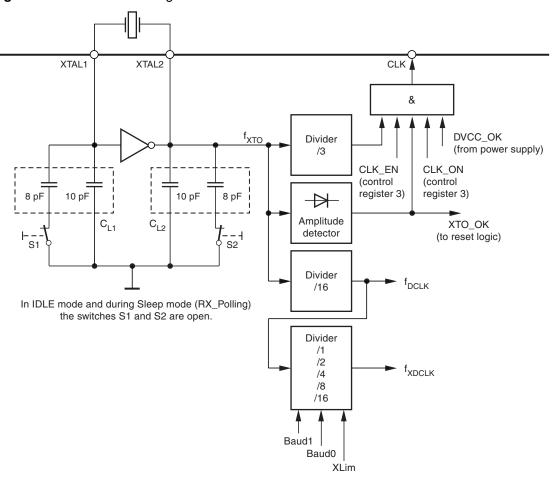

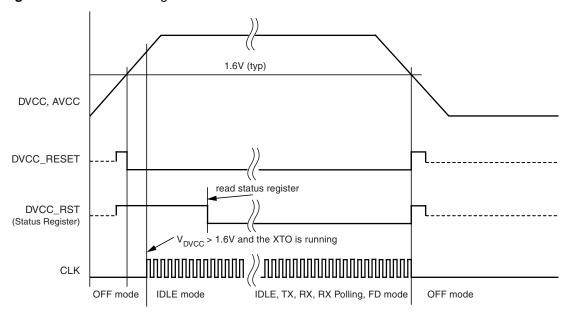

After 10  $\tau$  to 20  $\tau$ , an amplitude detector detects the oscillation amplitude and sets XTO\_OK to High if the amplitude is large enough. This activates the CLK output if CLK\_ON and CLK\_EN in control register 3 are High (see Table 12-12 on page 39). Note that the necessary conditions of the DVCC voltage also have to be fulfilled (see Figure 9-2 on page 29 and Figure 10-1 on page 31).

To save current in IDLE and Sleep mode, the load capacitors partially are switched off in this modes with  $S_1$  and  $S_2$  seen in Figure 9-2 on page 29.

It is recommended to use a crystal with  $C_m$  = 3.0 fF to 7.0 fF,  $C_{LN}$  = 9 pF,  $R_m$  < 120 $\Omega$  and  $C_0$  = 1.0 pF to 2.2 pF.

Lower values of  $C_m$  can be used, this increases slightly the start-up time. Lower values of  $C_0$  or higher values of  $C_m$  (up to 15 fF) can also be used, this has only little influence to pulling.

Figure 9-2. XTO Block Diagram

To find the right values used in the control registers 2 and 3 (see Table 12-7 on page 38 and Table 12-10 on page 39) the relationship between  $f_{XTO}$  and the  $f_{RF}$  is shown in Table 9-1. To determine the right content, the frequency at pin CLK, as well as the output frequency at RF\_OUT in ASK mode can be measured, than the FREQ value can be calculated according to Table 9-1 so that  $f_{RF}$  is exactly the desired radio frequency.

**Table 9-1.** Calculation of f<sub>RF</sub>

| Frequency<br>(MHz) | Pin 6<br>433_N868 | CREG1<br>Bit(4)<br>FS | f <sub>XTO</sub> (MHz) | f <sub>RF</sub> = f <sub>TX_ASK</sub> = f <sub>RX</sub>         | f <sub>TX_FSK_L</sub> =<br>f <sub>TX_FSK_L(FD)</sub> | f <sub>TX_FSK_H</sub>          | f <sub>TX_FSK_H(FD)</sub>       | Frequency<br>Resolution |

|--------------------|-------------------|-----------------------|------------------------|-----------------------------------------------------------------|------------------------------------------------------|--------------------------------|---------------------------------|-------------------------|

| 315.0              | AVCC              | 1                     | 12.73193               | $f_{XTO} \times \left(24, 5 + \frac{FREQ + 24,5}{16384}\right)$ | f <sub>RF</sub> -<br>18.65 kHz                       | f <sub>RF</sub> +<br>18.65 kHz | f <sub>RF</sub> +<br>208.23 kHz | 777.1 Hz                |

| 868.3              | GND               | 0                     | 13.41180               | $f_{XTO} \times \left(64, 5 + \frac{FREQ + 24,5}{16384}\right)$ | f <sub>RF</sub> -<br>19.64 kHz                       | f <sub>RF</sub> +<br>19.64 kHz | f <sub>RF</sub> + 206.26 kHz    | 818.6 Hz                |

| 433.92             | AVCC              | 0                     | 13.25311               | $f_{XTO} \times \left(32, 5 + \frac{FREQ + 24,5}{16384}\right)$ | f <sub>RF</sub> -<br>19.41 kHz                       | f <sub>RF</sub> +<br>19.41 kHz | f <sub>RF</sub> +<br>203.74 kHz | 808.9 Hz                |

The variable FREQ depends on the bit PLL\_MODE in control register 1 and the parameter FREQ2 and FREQ3, which are defined by the bits FR0 to FR12 in control register 2 and 3 and is calculated as follows:

FREQ = FREQ2 + FREQ3

Care must be taken with the harmonics of the CLK output signal  $f_{CLK}$ , as well as to the harmonics produced by an microprocessor clocked with it, since these harmonics can disturb the reception of signals if they get to the RF input. In a single channel system the use of FREQ = 3803 to 4053 ensures that harmonics of this signal do not disturb the receive mode. In a multichannel system the CLK signal can either be not used or carefully layouted on the application PCB. The supply voltage of the microcontroller must also be carefully blocked in a multichannel system.

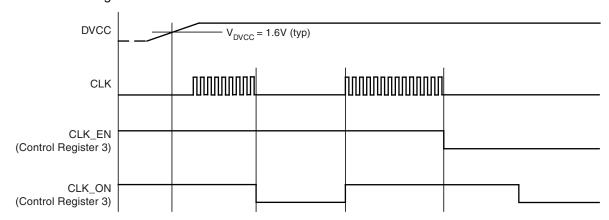

#### 9.1 Pin CLK

Pin CLK is an output to clock a connected microcontroller. The clock frequency f<sub>CLK</sub> is calculated as follows:

$$f_{CLK} = \frac{f_{XTO}}{3}$$

The signal at CLK output has a nominal 50% duty cycle.

If the bit CLK EN in control register 3 is set to 0, the clock is disabled permanently.

If the bit CLK\_EN is set to 1 and bit CLK\_ON (control register 3) is set to 0, the clock is disabled as well. If bit CLK\_ON is set to 1 and thus the clock is enabled if the Bit-check is ok (RX, RX Polling, FD mode (Slave)), an event on pin N\_PWR\_ON occurs or the bit Power\_On in the status register is 1.

Figure 9-3. Clock Timing

## 9.2 Basic Clock Cycle of the Digital Circuitry

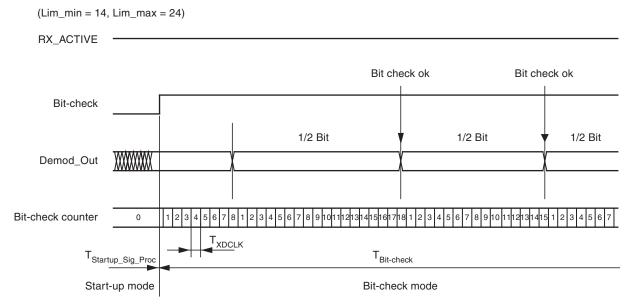

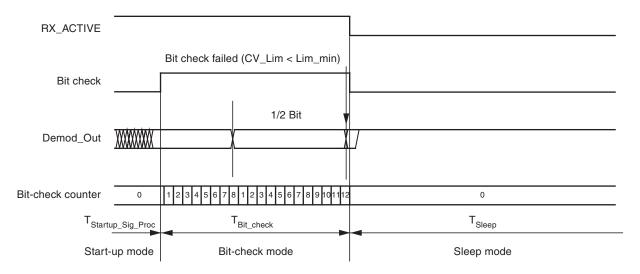

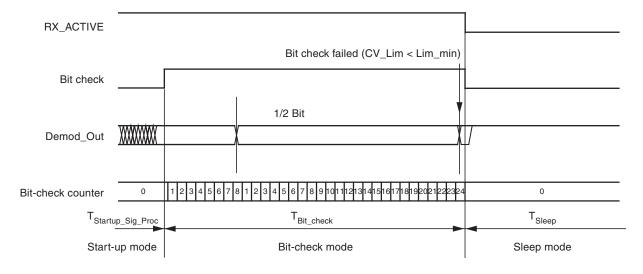

The complete timing of the digital circuitry is derived from one clock. According to Figure 9-2 on page 29, this clock cycle T<sub>DCLK</sub> is derived from the crystal oscillator (XTO) in combination with a divider.

$$f_{DCLK} = \frac{f_{XTO}}{16}$$

T<sub>DCLK</sub> controls the following application relevant parameters:

- Timing of the polling circuit including bit-check

- TX bit rate

The clock cycle of the Bit-check and the TX bit rate depends on the selected bit-rate range (BR\_Range) which is defined in control register 6 (see Table 12-19 on page 41) and  $X_{Lim}$  which is defined in control register 4 (see Table 12-16 on page 40). This clock cycle  $T_{XDCLK}$  is defined by the following formulas for further reference:

$\begin{array}{ccc} \text{BR\_Range 0: } T_{\text{XDCLK}} = 8 \times T_{\text{DCLK}} \times X_{\text{Lim}} \\ \text{BR\_Range 1: } T_{\text{XDCLK}} = 4 \times T_{\text{DCLK}} \times X_{\text{Lim}} \\ \text{BR\_Range 2: } T_{\text{XDCLK}} = 2 \times T_{\text{DCLK}} \times X_{\text{Lim}} \\ \text{BR\_Range 3: } T_{\text{XDCLK}} = 1 \times T_{\text{DCLK}} \times X_{\text{Lim}} \end{array}$

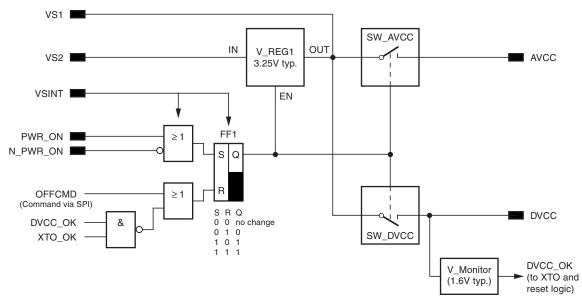

# 10. Power Supply

Figure 10-1. Power Supply

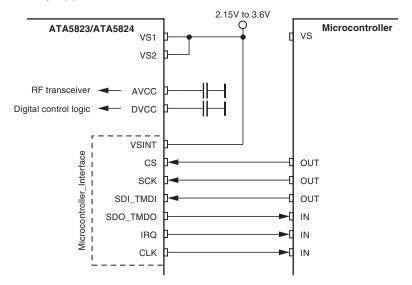

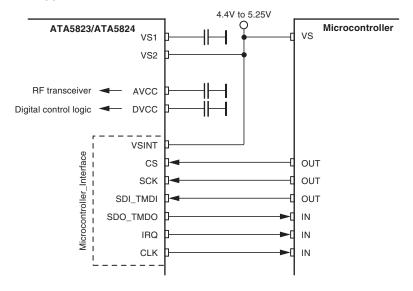

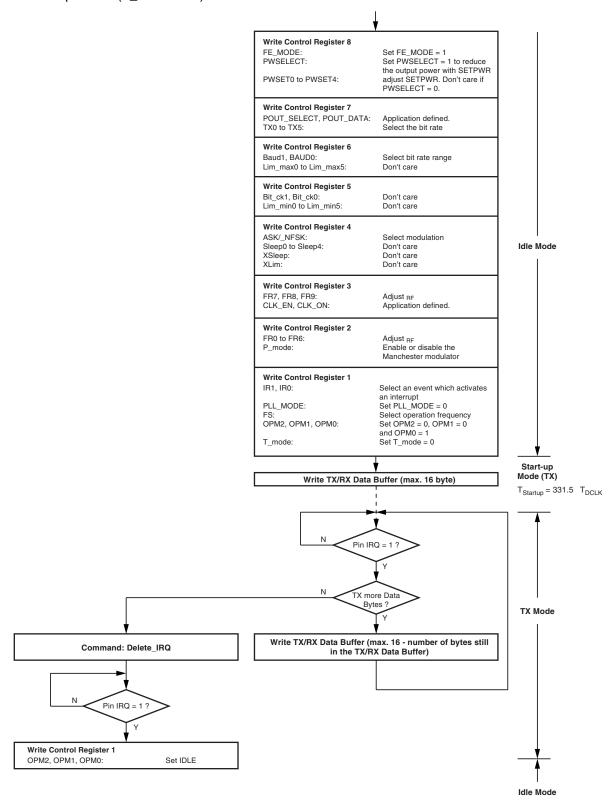

The supply voltage range of the ATA5823/ATA5824 is 2.15V to 3.6V or 4.4V to 5.25V.

Pin VS1 is the supply voltage input for the range 2.15V to 3.6V and is used in battery applications using a single lithium 3V cell. Pin VS2 is the voltage input for the range 4.4V to 5.25V (car applications), in this case the voltage regulator  $V_REG$  regulates VS1 to typically 3.25V. If the voltage regulator is active, a blocking capacitor of 2.2  $\mu F$  has to be connected to VS1.

Pin VSINT is the voltage input for the Microcontroller\_Interface and must be connected to the power supply of the microcontroller. The voltage range of  $V_{VSINT}$  is 2.25V to 5.25V (see Figure 10-5 and Figure 10-6 on page 35).

AVCC is the internal operation voltage of the RF transceiver and is feed via the switch SW\_AVCC by VS1. AVCC must be blocked on pin AVCC with a 68 nF capacitor (see Figure 3-1 on page 6, Figure 4-1 on page 7, Figure 5-1 on page 8 and Figure 6-1 on page 9).

DVCC is the internal operation voltage of the digital control logic and is fed via the switch SW\_DVCC by VS1. DVCC must be blocked on pin DVCC with 68 nF (see Figure 3-1 on page 6, Figure 4-1 on page 7, Figure 5-1 on page 8 and Figure 6-1 on page 9).

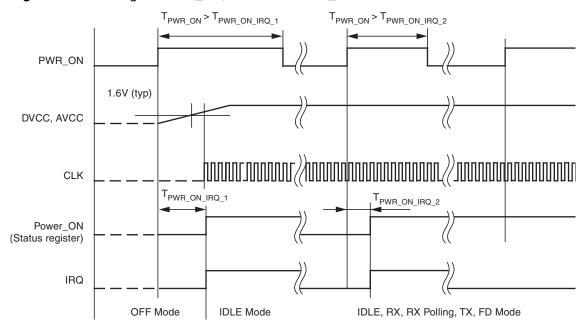

Pin PWR ON is an input to switch on the transceiver (active high).

Pin N\_PWR\_ON is an input for a push button and can also be used to switch on the transceiver (active low).

For current consumption reasons it is recommended to set N\_PWR\_ON to GND only temporarily. Otherwise an additional current flows because of a 50 k $\Omega$  pull-up resistor.

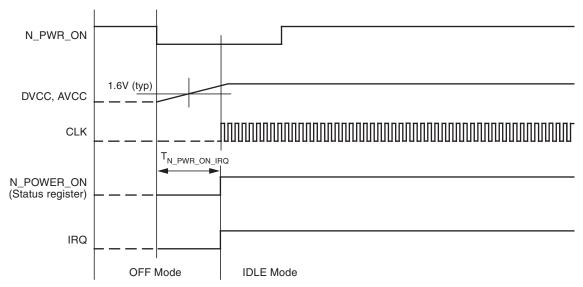

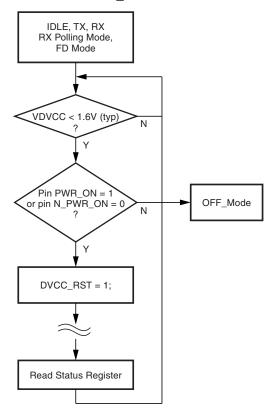

A voltage monitor generates the signal DVCC\_OK if DVCC ≥ 1.6V typically.

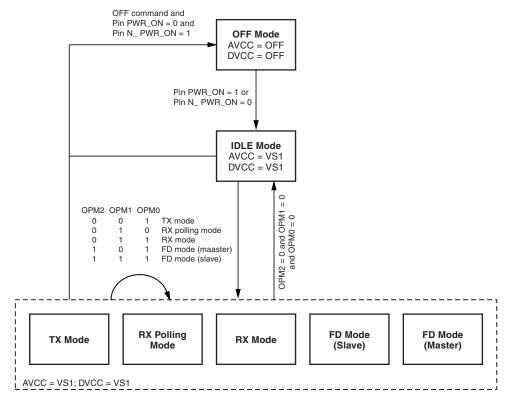

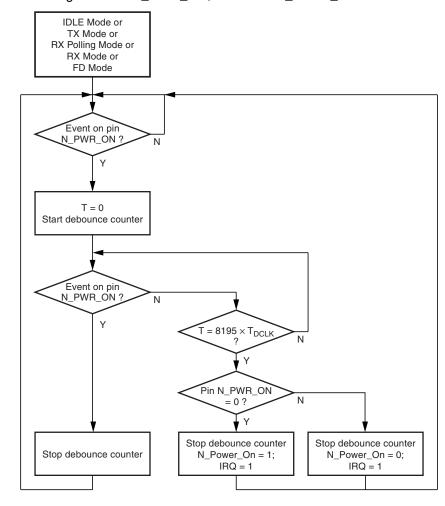

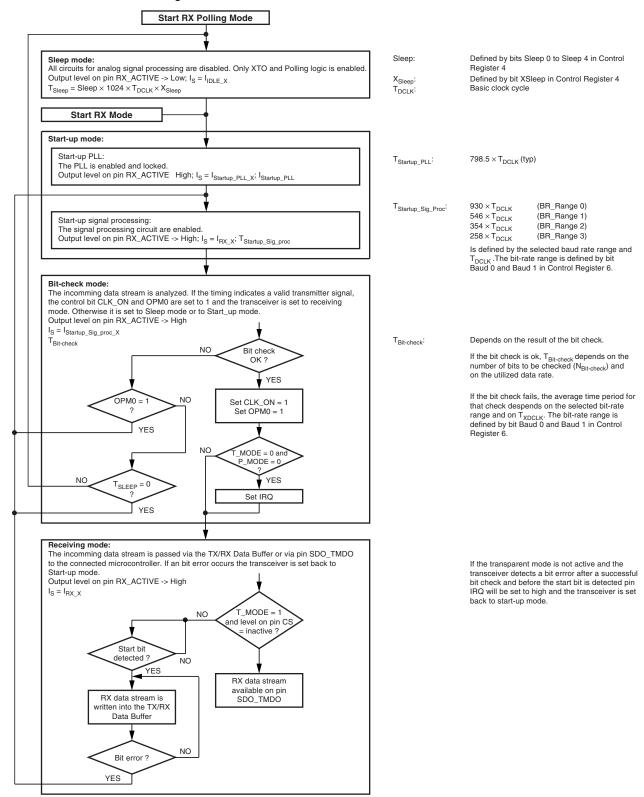

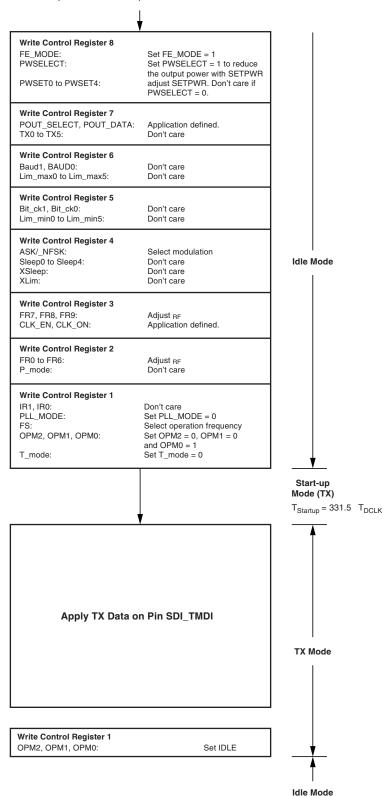

Figure 10-2. Flow Chart Operation Modes

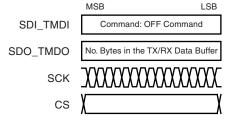

#### 10.1 OFF Mode

After connecting the power supply (battery) to pin VS1 and/or VS2 and VSINT, the transceiver is in OFF mode. In OFF mode AVCC and DVCC are disabled, resulting in very low power consumption ( $I_{S\_OFF}$  is typically  $\leq 10$  nA in the key fob application Figure 3-1 on page 6 and Figure 5-1 on page 8 and  $\leq 0.5~\mu A$  in the car application Figure 4-1 on page 7 and Figure 6-1 on page 9). In OFF mode the transceiver is not programmable via the 4-wire serial interface.

#### 10.2 IDLE Mode

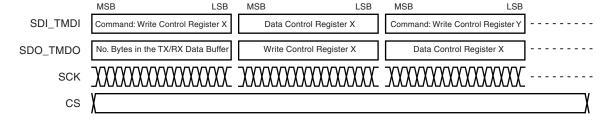

In IDLE mode AVCC and DVCC are connected to the battery voltage (VS1).