### 0.5W POWER pHEMT

Package Style: Bare Die

#### **Product Description**

The FPD750 is an AlGaAs/InGaAs pseudomorphic High Electron Mobility Transistor (pHEMT), featuring a 0.25  $\mu m \times 750\,\mu m$  Schottky barrier gate, defined by high -resolution stepper-based photolithography. The double recessed gate structure minimizes parasitics to optimize performance. The epitaxial structure and processing have been optimized for reliable high-power applications. The FPD750 also features Si $_3N_4$  passivation and is available in the low-cost plastic SOT89, SOT343, and DFN packages.

#### **Features**

- 27.5dBm Linear Output Power at 12GHz

- 11.5dB Power Gain at 12GHz

- 14.5 dB Max Stable Gain at 12 GHz

- 38dBm O<sub>IP3</sub>

- 50% Power-Added Efficiency

### **Applications**

- Narrowband and Broadband High-Performance Amplifiers

- SATCOM Uplink Transmitters

- PCS/Cellular Low-Voltage High-Efficiency Output Amplifiers

- Medium-Haul Digital Radio Transmitters

| Parameter                                          | Specification |      |      | Linis | Open disting                                                  |

|----------------------------------------------------|---------------|------|------|-------|---------------------------------------------------------------|

| Parameter                                          | Min. Typ.     |      | Max. | Unit  | Condition                                                     |

| Electrical Specifications                          |               |      |      |       |                                                               |

| P <sub>1dB</sub> Gain Compression                  | 26.5          | 27.5 |      | dBm   | V <sub>DS</sub> =8V, I <sub>DS</sub> =50% I <sub>DSS</sub>    |

| Maximum Stable Gain (S21/S12)                      | 13.5          | 14.5 |      | dB    | V <sub>DS</sub> =8V, I <sub>DS</sub> =50% I <sub>DSS</sub>    |

| Power Gain at P <sub>1dB</sub> (G <sub>1dB</sub> ) | 10.5          | 11.5 |      | dB    | V <sub>DS</sub> =8V, I <sub>DS</sub> =50% I <sub>DSS</sub>    |

| Power-Added Efficiency (PAE)                       |               | 45   |      | %     | $V_{DS}$ =8V, $I_{DS}$ =50% $I_{DSS}$ , $P_{OUT}$ = $P_{1dB}$ |

| OIP <sub>3</sub>                                   |               | 38   |      | dBm   | V <sub>DS</sub> =8V, I <sub>DS</sub> =50% I <sub>DSS</sub>    |

|                                                    |               | 40   |      | dBm   | Matched for optimal power, tuned for best IP <sub>3</sub>     |

| Saturated Drain-Source Current (I <sub>DSS</sub> ) | 185           | 230  | 280  | mA    | V <sub>DS</sub> =1.3V, V <sub>GS</sub> =0V                    |

| Maximum Drain-Source Current (I <sub>MAX</sub> )   |               | 370  |      | mA    | V <sub>DS</sub> =1.3V, V <sub>GS</sub> ≈+1V                   |

| Transconductance (G <sub>M</sub> )                 |               | 200  |      | ms    | V <sub>DS</sub> =1.3V, V <sub>GS</sub> =0 V                   |

| Gate-Source Leakage Current (I <sub>GSO</sub> )    |               | 10   |      | μΑ    | VGS=-5V                                                       |

| Pinch-Off Voltage (V <sub>P</sub> )                |               | 1.0  |      | V     | V <sub>DS</sub> =1.3V, I <sub>DS</sub> =0.36mA                |

| Gate-Source Breakdown Voltage (V <sub>BDGS</sub> ) | 12.0          | 14.0 |      | V     | I <sub>GS</sub> =0.75mA                                       |

| Gate-Drain Breakdown Voltage (V <sub>BDGD</sub> )  | 14.5          | 16.0 |      | V     | I <sub>GD</sub> =0.75mA                                       |

| Thermal Resistivity (θJC)                          |               | 65   |      | °C/W  | V <sub>DS</sub> >6V                                           |

Note: T<sub>AMBIENT</sub> = 22 °C, RF specifications measured at f = 12 GHz using CW signal.

#### Absolute Maximum Ratings<sup>1</sup>

| Parameter                                                                               | Rating           | Unit |  |

|-----------------------------------------------------------------------------------------|------------------|------|--|

| Drain-Source Voltage (V <sub>DS</sub> )<br>(-3V <v<sub>GS&lt;-0.5V)<sup>2</sup></v<sub> | 10               | V    |  |

| Gate-Source Voltage (V <sub>GS</sub> )<br>(0V < V <sub>DS</sub> < +8V)                  | -3               | V    |  |

| Drain-Source Current (I <sub>DS</sub> )<br>(For V <sub>DS</sub> <2V)                    | I <sub>DSS</sub> |      |  |

| Gate Current (I <sub>G</sub> )<br>(Forward or reverse current)                          | 7.5              | mA   |  |

| RF Input Power (P <sub>IN</sub> )<br>(Under any acceptable bias state)                  | 22               | dBm  |  |

| Channel Operating Temperature (T <sub>CH</sub> )<br>(Under any acceptable bias state)   | 175              | °C   |  |

| Storage Temperature (T <sub>STG</sub> )<br>(Non-Operating Storage)                      | -65 to 150       | °C   |  |

| Total Power Dissipation (P <sub>TOT</sub> ) <sup>3, 4, 5</sup>                          | 2.3              | W    |  |

| Simultaneous Combination of Limits <sup>6</sup> (2 or more max. limits)                 | 80               | %    |  |

$<sup>^{1}\</sup>mathrm{T}_{\mathrm{AMBIENT}}$  = 22 °C unless otherwise noted; exceeding any one of these absolute maximum ratings may cause permanent damage to the device.

# **A**

Caution! ESD sensitive device.

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. Specified typical performance or functional operation of the device under Absolute Maximum Rating conditions is not implied.

RoHS status based on EUDirective 2002/95/EC (at time of this document revision).

The information in this publication is believed to be accurate and reliable. However, no responsibility is assumed by RF Micro Devices, Inc. ("RFMD") for its use, nor for any infringement of patents, or other rights of third parties, resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of RFMD. RFMD reserves the right to change component circuitry, recommended application circuitry and specifications at any time without prior notice.

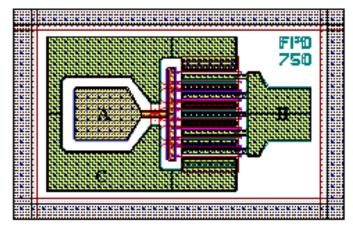

## **Pad Layout**

| Pad | Description | Pin Coordinates (μm) |

|-----|-------------|----------------------|

| Α   | Gate Pad    | 130, 170             |

| В   | Drain Pad   | 380, 170             |

| С   | Source Pad  |                      |

Note: Coordinates are referenced from the bottom left hand corner of the die to the center of the bond pad opening.

| Die Size (μm) | Die Thickness (μm) | Min. Bond Pad Opening (μmxμm) |

|---------------|--------------------|-------------------------------|

| 470x340       | 75                 | 56x76                         |

$<sup>^2</sup>$  Operating at absolute maximum  $\rm V_D$  continuously is not recommended. If operation at 10V is considered then  $\rm I_{DS}$  must be reduced in order to keep the part within its thermal power dissipation limits. Therefore  $\rm V_{GS}$  is restricted to <-0.5V.

$<sup>^3</sup>$ Total Power Dissipation to be de-rated as follows above 22 °C:  $P_{TOT} = 2.3 - (0.015\,\text{W/}\,^\circ\text{C})xT_{HS},$  where  $T_{HS} =$  heatsink or ambient temperature above 22 °C. Example: For a 85 °C carrier temperature:  $P_{TOT} = 2.3 - (0.015\,\text{x}(85 - 22)) = 1.4\,\text{W}$

<sup>&</sup>lt;sup>4</sup>Total Power Dissipation ( $P_{TOT}$ ) defined as ( $P_{DC} + P_{IN}$ ) –  $P_{OUT}$ , where  $P_{DC}$ : DC Bias Power,  $P_{IN}$ : RF Input Power,  $P_{OUT}$ . RF Output Power.

<sup>&</sup>lt;sup>5</sup> Users should avoid exceeding 80% of 2 or more Limits simultaneously.

<sup>&</sup>lt;sup>6</sup>Thermal Resistivity specification assumes a Au/Sn eutectic die attach onto an Auplated copper heatsink or rib.

#### **Preferred Assembly Instructions**

GaAs devices are fragile and should be handled with great care. Specially designed collets should be used where possible.

The back of the die is metallized and the recommended mounting method is by the use of conductive epoxy. Epoxy should be applied to the attachment surface uniformly and sparingly to avoid encroachment of epoxy on to the top face of the die, and ideally should not exceed half the chip height. For automated dispense Ablestick LMISR4 is recommended, and for manual dispense Ablestick 84-1 LMI or 84-1 LMIT are recommended. These should be cured at a temperature of 150°C for 1 hour in an oven especially set aside for epoxy curing only. If possible the curing oven should be flushed with dry nitrogen. The gold-tin (80% Au 20% Sn) eutectic die attach has a melting point of approximately 280°C but the absolute temperature being used depends on the leadframe material used and the particular application. The maximum time at used should be kept to a minimum.

This part has gold (Au) bond pads requiring the use of gold (99.99% pure) bondwire. It is recommended that  $25.4\mu m$  diameter gold wire be used. Recommended lead bond technique is thermocompression wedge bonding with 0.001" ( $25\mu m$ ) diameter wire. The bond tool force shall be  $35\, grams$  to  $38\, grams$ . Bonding stage temperature shall be  $230\, ^{\circ}C$  to  $240\, ^{\circ}C$ , heated tool ( $150\, ^{\circ}C$ ) is recommended. Ultrasonic or thermosonic bonding is not recommended.

Bonds should be made from the die first and then to the mounting substrate or package. The physical length of the bondwires should be minimized especially when making RF or ground connections.

#### **Handling Precautions**

To avoid damage to the devices, care should be exercised during handling. Proper Electrostatic Discharge (ESD) precautions should be observed at all stages of storage, handling, assembly, and testing.

#### **ESD/MSL Rating**

These devices should be treated as Class 0 (0V to 250V) using the human body model as defined in JEDEC Standard No. 22-A114. Further information on ESD control measures can be found in MIL-STD-1686 and MIL-HDBK-263. This is an unpackaged part and therefore no MSL rating applies.

## **Application Notes and Design Data**

Application Notes and design data including S-parameters, noise parameters, and device model are available on request from www.rfmd.com.

#### Reliability

An MTTF of 4.2 million hours at a channel temperature of 150 °C is achieved for the process used to manufacture this device.

#### **Disclaimers**

This product is not designed for use in any space-based or life-sustaining/supporting equipment.

### **Ordering Information**

| Delivery Quantity   | Ordering Code |  |

|---------------------|---------------|--|

| Full Pack (100)     | FPD750-000    |  |

| Small Quantity (25) | FPD750-000SQ  |  |

| Sample Quantity (3) | FPD750-000S3  |  |

# **FPD750**