rfmd.com

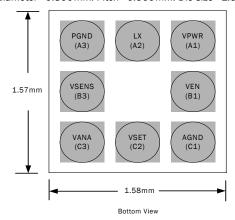

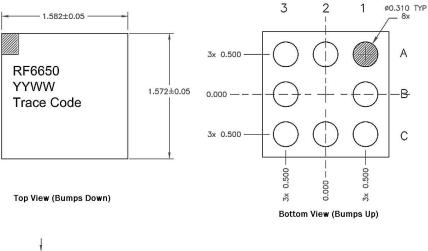

Package: 8-Bump WLCSP, 3x3 Array, 1.58mm x1.57mm

### **Features**

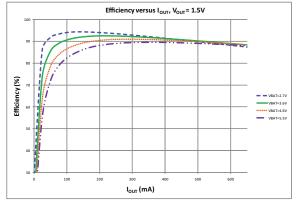

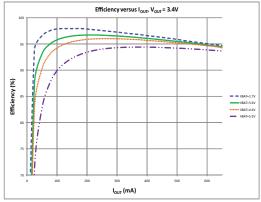

- High Efficiency > 95%

- Transient Response < 25 us

- 650mA Load Current Capability

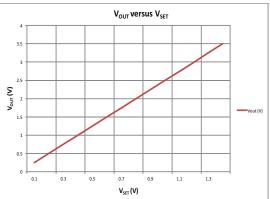

- Programmable Output Voltage

- Bypass FET

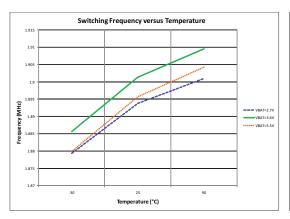

- Constant Switching Frequency

- V<sub>BAT</sub> Range = 2.7 V to 5.1 V

- Over-Temperature Shutdown

- Over-Current Shutdown

## **Applications**

W-CDMA Handsets

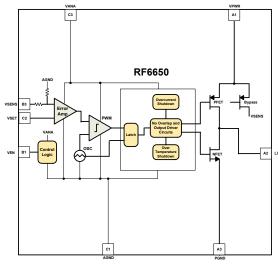

Functional Block Diagram

### **Product Description**

The RF6650 is a pulse width modulated (PWM), voltage-mode controlled DC-DC converter unit designed to supply power to a W-CDMA power amplifier. The output voltage is continuously programmable through the VSET analog input pin according to the transfer function  $V_{\text{OUT}} = V_{\text{SET}} \times 2.5$ . The converter has been optimized for high efficiency at light current load conditions, fast transient response times to meet W-CDMA  $25\,\mu \text{s}$  slot-to-slot transition specifications, and low noise by maintaining a constant switching frequency, while supplying up to 650 mA in PWM controlled or bypass modes. Bypass mode is automatically enabled when  $V_{\text{BAT}} < 3.3 \text{V}$  and  $V_{\text{SET}} > 1.55 \text{V}$ . The converter is enabled when  $V_{\text{EN}} > 1.3 \text{V}$ . The RF6650 is a  $1.58\,\text{mmx}\,1.57\,\text{mm}$ , 8-bump, WLCSP device.

#### **Ordering Information**

RF6650 Power Management IC

RF6650PCBA-410 Fully Assembled Evaluation Board

| Optimum Technology Watching® Applied |               |              |            |  |  |  |  |  |

|--------------------------------------|---------------|--------------|------------|--|--|--|--|--|

| ☐ GaAs HBT                           | ☐ SiGe BiCMOS | ☐ GaAs pHEMT | ☐ GaN HEMT |  |  |  |  |  |

| ☐ GaAs MESFET                        | ☐ Si BiCMOS   | ☑ Si CMOS    | ☐ RF MEMS  |  |  |  |  |  |

| ☐ InGaP HBT                          | ☐ SiGe HBT    | ☐ Si BJT     | LDMOS      |  |  |  |  |  |

# **RF6650**

#### **Absolute Maximum Ratings**

| Parameter                                                   | Rating                        | Unit |

|-------------------------------------------------------------|-------------------------------|------|

| Input Supply Voltage (V <sub>PWR</sub> , V <sub>ANA</sub> ) | -0.2 to +6.0                  | V    |

| Analog Input (V <sub>SET</sub> , V <sub>EN</sub> )          | -0.2 to V <sub>ANA</sub> -0.2 | V    |

| Ground Voltage                                              | -0.2 to +0.2                  | V    |

| Operating Ambient Temperature (T <sub>A</sub> )             | -30 to +85                    | °C   |

| Storage Temperature (T <sub>STORE</sub> )                   | -40 to +150                   | °C   |

#### Caution! ESD sensitive device.

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. Specified typical performance or functional operation of the device under Absolute Maximum Rating conditions is not implied.

RoHS status based on EUDirective 2002/95/EC (at time of this document revision).

The information in this publication is believed to be accurate and reliable. However, no responsibility is assumed by RF Micro Devices, Inc. ("RFMD") for its use, nor for any infringement of patents, or other rights of third parties, resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of RFMD. RFMD reserves the right to change component circuitry, recommended application circuitry and specifications at any time without prior notice.

| Dawanatan                                                    | Specification |      |      | Unit             | Condition                                                                                                                                              |  |  |

|--------------------------------------------------------------|---------------|------|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter                                                    | Min.          | Тур. | Max. | Unit             | Condition                                                                                                                                              |  |  |

| Operating Conditions                                         |               |      |      |                  | See app schematic for component values. Typ: $V_{BAT}$ =3.6V, $V_{EN}$ =1.3V, $T_A$ =25 °C. Min/max: $V_{BAT}$ =2.7V to 5.1V, $T_A$ =-30 °C to +85 °C. |  |  |

| Supply Voltage                                               | 2.7           | 3.6  | 5.1  | V                | V <sub>BAT</sub> =V <sub>PWR</sub> and V <sub>ANA</sub> connected together                                                                             |  |  |

| Output Load Current                                          |               |      | 650  | mA               |                                                                                                                                                        |  |  |

| Junction Temperature                                         | -30           |      | +125 | °C               |                                                                                                                                                        |  |  |

| Operating Temperature                                        | -30           |      | +85  | °C               |                                                                                                                                                        |  |  |

| General Specifications                                       |               |      |      |                  |                                                                                                                                                        |  |  |

| Quiescent Current                                            |               | 700  | 1400 | μΑ               | V <sub>SET</sub> =0V, no load                                                                                                                          |  |  |

| Shut Down Current                                            |               |      | 20   | μΑ               | V <sub>EN</sub> =Low                                                                                                                                   |  |  |

| Logic High Input Threshold V <sub>IH</sub>                   | 1.3           |      |      | V                | V <sub>EN</sub>                                                                                                                                        |  |  |

| Logic Low Input Threshold V <sub>IL</sub>                    |               |      | 0.5  | V                | V <sub>EN</sub>                                                                                                                                        |  |  |

| Input Current                                                |               |      | 1    | μА               | V <sub>EN</sub> , V <sub>SET</sub>                                                                                                                     |  |  |

| Thermal Shutdown                                             |               | 160  |      | °C               | Rising temperature                                                                                                                                     |  |  |

|                                                              |               | 30   |      | °C               | Hysteresis                                                                                                                                             |  |  |

| Over-Current Shutdown Trip Point                             |               | 2.2  |      | Α                | Full FET. V <sub>OUT</sub> = 3.4 V, V <sub>BAT</sub> = 4.2 V                                                                                           |  |  |

|                                                              |               | 1.4  |      | Α                | 1/3 FET. V <sub>OUT</sub> =0.6V.                                                                                                                       |  |  |

| DC Specifications                                            |               |      |      |                  |                                                                                                                                                        |  |  |

| V <sub>SET</sub> Range                                       | 0.2           |      | 1.4  | V                | See note 1.                                                                                                                                            |  |  |

| Transfer Function Gain (V <sub>OUT</sub> /V <sub>SET</sub> ) |               | 2.50 |      | V/V              | V <sub>OUT</sub> ≤V <sub>BAT</sub> -V <sub>DO</sub>                                                                                                    |  |  |

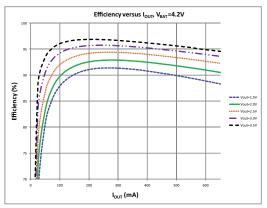

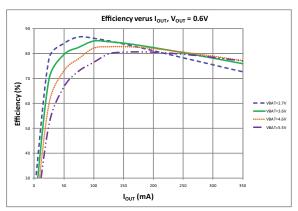

| Efficiency                                                   |               | 69   |      | %                | V <sub>OUT</sub> =0.6V, I <sub>OUT</sub> =25mA                                                                                                         |  |  |

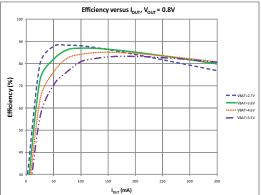

|                                                              |               | 83   |      | %                | V <sub>OUT</sub> =0.8V, I <sub>OUT</sub> =65mA                                                                                                         |  |  |

|                                                              |               | 91   |      | %                | V <sub>OUT</sub> =1.5V, I <sub>OUT</sub> =200mA                                                                                                        |  |  |

|                                                              |               | 95   |      | %                | V <sub>OUT</sub> =3.4V, I <sub>OUT</sub> =460 mA, V <sub>BAT</sub> ≥4.2V                                                                               |  |  |

| FET Segmentation Threshold                                   |               | 0.45 |      | V                | Rising V <sub>SET</sub> , activates all FETs. Full FET mode.                                                                                           |  |  |

|                                                              |               | 0.35 |      | V                | Falling V <sub>SET</sub> , disables 2/3 of the FETs, 1/3 FET mode.                                                                                     |  |  |

| Output Voltage Ripple                                        |               | 10   |      | mV <sub>PP</sub> | V <sub>OUT</sub> =1.5V                                                                                                                                 |  |  |

| Dropout Voltage (V <sub>DO</sub> )                           |               | 170  |      | mV               | V <sub>SET</sub> =1.2V, V <sub>BAT</sub> =3.0V, I <sub>OUT</sub> =500 mA<br>Dropout=V <sub>BAT</sub> -V <sub>OUT</sub>                                 |  |  |

| Load Regulation                                              |               | 5    |      | mV/A             | V <sub>OUT</sub> =3.0V, I <sub>OUT</sub> =100 mA to 500 mA                                                                                             |  |  |

| Line Regulation                                              |               | 2    |      | mV/V             | V <sub>OUT</sub> =3.0V, I <sub>OUT</sub> =300mA, V <sub>BAT</sub> =3.6V to 5.5V                                                                        |  |  |

| Baramatar                              |      | Specification |      |      | Condition                                                                                                              |  |

|----------------------------------------|------|---------------|------|------|------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                              | Min. | Тур.          | Max. | Unit | Condition                                                                                                              |  |

| AC Specifications                      |      |               |      |      |                                                                                                                        |  |

| Switching Frequency                    |      | 1.9           |      | MHz  |                                                                                                                        |  |

| V <sub>OUT</sub> Startup Time          |      |               | 25   | μs   | V <sub>OUT</sub> =0V to 0.6V±10%, I <sub>OUT</sub> <1mA                                                                |  |

|                                        |      |               | 25   | μs   | V <sub>OUT</sub> =0V to 3.4V±10%, I <sub>OUT</sub> <1mA, V <sub>BAT</sub> ≥4.2V                                        |  |

| V <sub>OUT</sub> Response Time         |      |               | 25   | μs   | $V_{OUT}$ =0.6V to 3.4V±100mV, $R_{LOAD}$ =5 $\Omega$ , $V_{BAT}$ $\geq$ 4.2V                                          |  |

|                                        |      |               | 25   | μѕ   | $V_{OUT}$ =3.4V to 0.6V±100 mV, $R_{LOAD}$ =25 $\Omega$ , $V_{BAT}$ ≥4.2V                                              |  |

| SMPS to BYPASS Time                    |      |               | 5    | μѕ   | $V_{SET}$ =1.0V to 1.7V, $I_{OUT}$ =460 mA, $V_{BAT}$ =3.0V. See note 2.                                               |  |

|                                        |      |               | 20   | μs   | V <sub>BAT</sub> = 4.6V to 3.0V, I <sub>OUT</sub> = 460 mA, V <sub>SET</sub> = 1.7V.<br>See note 2.                    |  |

| BYPASS to SMPS Time                    |      |               | 50   | μs   | V <sub>SET</sub> =1.7V to 1.0V, I <sub>OUT</sub> =460 mA, V <sub>OUT</sub> =3.0V                                       |  |

|                                        |      |               | 50   | μs   | V <sub>BAT</sub> =3.0V to 4.6V, I <sub>OUT</sub> =460 mA, V <sub>SET</sub> =1.7V                                       |  |

| Load Transient                         |      |               | 100  | mVpk | $V_{OUT}$ =1.8V, $I_{OUT}$ =20 mA to 200 mA,<br>$T_{RISE}$ = $T_{FALL}$ =10 $\mu$ s                                    |  |

|                                        |      |               | 50   | mVpk | $V_{OUT}$ =3.4V, $I_{OUT}$ =400 mA to 550 mA, $V_{BAT}$ =4.2V, $T_{RISE}$ = $T_{FALL}$ =10 $\mu$ s                     |  |

| Line Transient                         |      |               | 40   | mVpk | $V_{OUT}$ =600 mV, $I_{OUT}$ =25 mA, $\Delta V_{BAT}$ =600 mV, $T_{RISE}$ = $T_{FALL}$ =10 $\mu s$                     |  |

|                                        |      |               | 150  | mVpk | $V_{OUT}$ =3.4V, $I_{OUT}$ =450 mA, $\Delta V_{BAT}$ =600 mV, $T_{RISE}$ = $T_{FALL}$ =10 $\mu$ s, $V_{BAT}$ =4.2 V    |  |

| Bypass Specifications                  |      |               |      |      |                                                                                                                        |  |

| Resistance                             |      | 150           |      | mΩ   | V <sub>SET</sub> =1.7V, V <sub>BAT</sub> =3.0V, I <sub>OUT</sub> =500 mA                                               |  |

| Enable Trip Point (V <sub>SET</sub> )  |      | 1.55          |      | V    | Rising V <sub>SET</sub> , I <sub>OUT</sub> =500 mA, V <sub>BAT</sub> =3.0V                                             |  |

| Enable Trip Point (V <sub>BAT</sub> )  |      | 3.3           |      | V    | Falling V <sub>BAT</sub> , I <sub>OUT</sub> =500 mA, V <sub>SET</sub> =1.7 V                                           |  |

| Disable Trip Point (V <sub>SET</sub> ) |      | 1.45          |      | V    | Falling V <sub>SET</sub> , I <sub>OUT</sub> =500 mA, V <sub>BAT</sub> =3.0V                                            |  |

| Disable Trip Point (V <sub>BAT</sub> ) |      | 3.5           |      | V    | Rising V <sub>BAT</sub> , I <sub>OUT</sub> =500 mA, V <sub>SET</sub> =1.7 V                                            |  |

| Dropout Voltage                        |      | 75            |      | mV   | V <sub>SET</sub> =1.7V, V <sub>BAT</sub> =3.0V, I <sub>OUT</sub> =500 mA<br>Dropout=V <sub>BAT</sub> -V <sub>OUT</sub> |  |

| V <sub>OUT</sub> Startup Time          |      |               | 15   | μs   | $V_{SET}$ =0V to 1.7V, $V_{BAT}$ =3.0V, $I_{OUT}$ $\leq$ 1mA                                                           |  |

#### Notes:

#### Bypass Control Table (both conditions must be met)

| Mode           | V <sub>SET</sub> | V <sub>BAT</sub> |  |

|----------------|------------------|------------------|--|

| Bypass Enable  | >1.55V           | <3.3V            |  |

| Bypass Disable | <1.45V           | >3.5V            |  |

#### **FET Segmentation Control Table**

| Mode     | V <sub>SET</sub> |

|----------|------------------|

| Full FET | >0.45V           |

| 1/3 FET  | <0.35V           |

<sup>1.</sup> The  $V_{SET}$  range under normal SMPS operation is 1.4V resulting in  $V_{OUT}$ =3.5V; however, the only limit to this value is imposed by the Absolute Maximum Rating of the VSET pin. This pin also is used to activate the bypass mode when supply voltage is low. For this reason, a value of  $V_{SET}$ =1.7V is often used in this specification to enable the bypass mode.

<sup>2.</sup> Differences in timing result from capacitance on triggered pin. For example, V<sub>BAT</sub> has greater capacitance as seen in the application schematic.

# **RF6650**

| Pin | Function                                                                                                   | Description                                                                                                         |  |  |

|-----|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|

| A1  | VPWR                                                                                                       | Supply used for the final output stage. Local 2.2µF decoupling capacitor required.                                  |  |  |

| A2  | 2 LX DC-DC Converter Switch Output. Connect to the filter inductor as recommended on application schematic |                                                                                                                     |  |  |

| А3  | PGND                                                                                                       | DC-DC Converter Power Ground.                                                                                       |  |  |

| B1  | VEN                                                                                                        | This pin enables the DC to DC converter.                                                                            |  |  |

| В3  | VSENS                                                                                                      | Feedback node from the output. Connect to a point after the V <sub>OUT</sub> inductor.                              |  |  |

| C1  | AGND                                                                                                       | Ground for the analog circuits. Isolate from PGND to help reduce noise.                                             |  |  |

| C2  | VSET Analog reference input used to set the output voltage.                                                |                                                                                                                     |  |  |

| C3  | VANA                                                                                                       | Supply used for the analog circuitry inside the power management IC. Separate 2.2 µF decoupling capacitor required. |  |  |

### Pin Out

3x3 array, 8 bumps. Bump diameter=0.300mm. Pitch=0.500mm. Die size=1.58mmx1.57mm=2.48mm<sup>2</sup>.

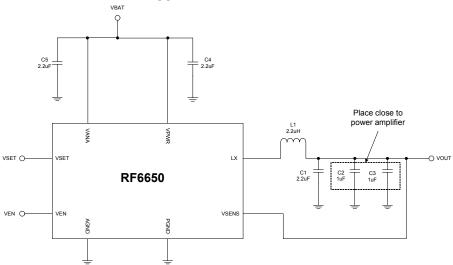

# **Application Schematic**

#### Notes:

- The LC filter (power filter) consists of L1 and C1 near the DUT and the distributed capacitances C2 and C3 near the load.

The main loop of L1 and C1 should be as small as possible with a large ground plane connecting C1 to the PGND pin.

Capacitors C2 and C3 are placed at the VDD pins of the load and should also have a clear return path to PGND. The loop filter is designed to have a total capacitance of 4.2 μF (C1=2.2 μF, C2=1 μF, C3=1 μF).

- 2. Capacitors C2 and C3 are placed a small distance away from the DUT on the evaluation board to emulate the distributed effects of the trace resistance as would be expected in the application. If the evaluation board is used to power a separate board that contains decoupling capacitors on the VOUT trace, capacitors C2 and C3 should be removed or decreased in value so that the total capacitance is approximately 4.2 µF.

- 3. A separate decoupling capacitor should be used for the VPWR and VANA pins. The current return path for the analog and power sections should be kept separate. To decrease the number of component types, a value of 2.2μF is selected. Additional 100μF decoupling capacitors are used on the evaluation board to more closely model a battery at the DUT. The 100μF capacitors will not be needed in a battery-supplied system.

- 4. The parasitic resistance of L1 and C1 should be kept within the limits  $R_{ESRL} < 100 \, \text{m}\Omega$ ,  $R_{ESRC} = 10 \, \text{m}\Omega$ . Recommended components are given in the table below. Selecting alternate components will have an impact on the reported performance including, but not limited to, changes in the efficiency.

#### **Application Schematic Components**

| Designator | Designator         Case Size         Quantity           L1         2.5x2.0x1.0         1           C1, C4, C5         0603         3 |   | Quantity Value |             | Part Number        |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------|---|----------------|-------------|--------------------|--|

| L1         |                                                                                                                                      |   | 2.2 μΗ         | Murata      | LQM2HPN2R2MG0L     |  |

| C1, C4, C5 |                                                                                                                                      |   | 2.2μF          | Murata      | GRM188R61A225KE34D |  |

| C2, C3     | 0603                                                                                                                                 | 2 | 1μF            | Taiyo Yuden | RMTMK107BJ105KA-T  |  |

# **RF6650**

### **Theory of Operation**

DC-DC buck converter operation involves the stepping down of a higher battery voltage to a lower output voltage by alternately switching a PFET and NFET pair through an external LC filter. At a 2MHz switching frequency the PFET is enabled every 500 ns. The duty cycle at the LX switching node, which is continuously variable from 0% to 100%, is set by the PWM controller based on the  $V_{SET}$  analog voltage and  $V_{BAT}$  voltage to realize the desired output voltage. The PWM controller maintains accuracy, stability, and accounts for losses in the system by feedback through the VSENS pin. The controller has been designed with non-overlapping control circuitry to prevent  $V_{RAT}$  shoot-through current to ground.

The converter has been optimized for high efficiency at light load by balancing DC and AC switching losses incurred in the output FETs, the switching frequency, and the external LC filter. In addition, output FET segmentation and selective biasing have been employed to further enhance light load efficiencies.

Unlike other DC-DC converter solutions on the market, the RF6650 does not alter the switching frequency at light load conditions to boost efficiency. This type of efficiency enhancement has a severe detriment on the system by injecting spurious noise at various frequencies. With our expertise in front-end transmit module design, RFMD proposes to operate this converter at a constant switching frequency to minimize system level interference. The ripple voltage, also a major component of noise injection into the PA, has also been minimized by selecting a larger inductance value.

Despite the attention to high efficiency, the transient performance of the device, defined as an output voltage transient from 600 mV to 3.4V or vice-versa, has not been overlooked. The PWM controller has been properly tuned with a fast type III loop filter to mate with an external LC filter (L=2.2 $\mu$ H and C=2.2  $\mu$ F+1  $\mu$ F+1  $\mu$ F=4.2  $\mu$ F). The result is a converter with sufficient bandwidth to meet 25  $\mu$ s W-CDMA slot-to-slot transition time requirements. The slew rate of the V<sub>SET</sub> pin should be limited to 100 mV/ $\mu$ s to achieve the best performance.

Lastly, the external inductor and capacitors were specifically selected to balance efficiency over the load current operating range and transient performance while minimizing total board area. Inductors and capacitors of different values may be used at risk to converter stability and performance (i.e., efficiency).

#### Shutdown

When  $V_{EN}$  < 0.5 V the device enters shutdown mode. In this mode all features are disabled to minimize battery quiescent current.

### **Over-Temperature Protection**

An internal over-temperature shutdown circuit is employed to protect the device from excessively high junction temperatures. The shutdown occurs at typically 160°C and will re-enable when the temperature drops below the activation point typically by 30°C.

#### **Over-Current Protection**

For the RF6650, an over-current shutdown (OCSD) circuit is employed to provide over-current fault protection. This methodology deactivates the output FETs in the case of an over-current fault as opposed to limiting the current. In this way the device only experiences the over-current condition for a short transient period and is not subject to continuous high current flow. Once the DUT is shut down, it will not restart automatically if the fault condition is removed. Toggling the V<sub>EN</sub> pin is required for restart.

### **Bypass Mode**

The RF6650 contains a bypass mode that activates a large PFET device in parallel with the switched-mode power supply (SMPS) PFET when both  $V_{BAT}$ < 3.3V and  $V_{SET}$ >1.55V. Such a condition results in a 100% duty cycle and activates the bypass FET to reduce the output resistance and dropout voltage.

### **FET Segmentation**

The main power FETs are designed in three sections to improve efficiency during light load conditions expected with low output voltages. When  $V_{SET}$  is raised to >0.45V, all three sections of the output FETs are on (full FET mode). When  $V_{SET}$  is reduced to <0.35V, one of the three sections is used (1/3 FET mode). Approximately 100 mV of hysteresis is used to avoid switching between the modes unintentionally.

### **Board Layout**

Good DC-DC converter layout practices in this application are strongly recommended to reduce radiated and conducted system noise. Placement of the VPWR bypass capacitor is critical and must be such to minimize the AC supply and ground return current loop through the PFET. In addition, the placements of the LC filter (L1 and C1) are also critical to minimize the AC supply and ground return current loop through the NFET.

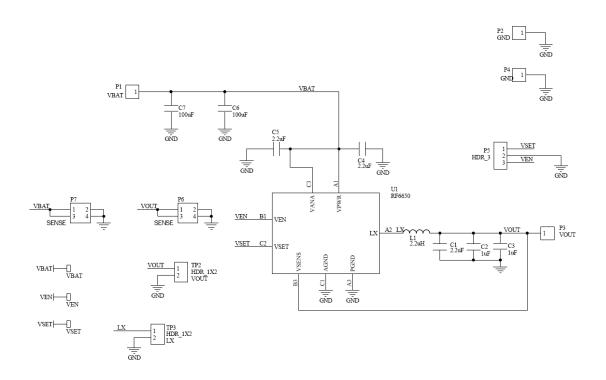

### **Evaluation Board Schematic**

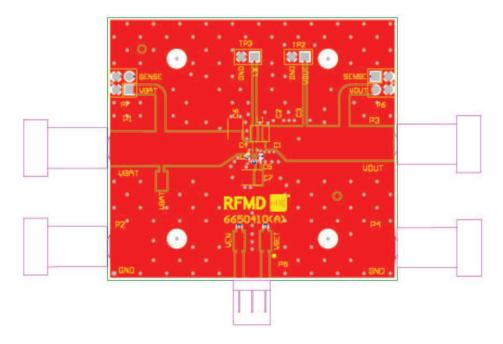

# **Evaluation Board Layout**

Board size: 2.2" x 2.0"

Board thickness: 0.062", Board material: FR4, Multilayer

# **Package Drawing**

#### Notes:

- 1. Shaded area represents Pin 1 location.

- 2. YY indicates year, WW indicates work week, and Trace Code is a sequential number assigned at device assembly.

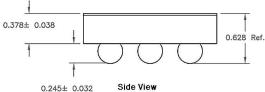

# **PCB Design Requirements**

#### **PCB Surface Finish**

(The PCB surface finish used for RFMD's qualification process is electroless nickel, immersion gold. Typical thickness is 3 inch to 8 inch gold over 180 inch nickel.

#### **PCB Land Pattern Recommendation**

PCB land patterns for RFMD components are based on IPC-7351 standards and RFMD empirical data. The pad pattern shown has been developed and tested for optimized assembly at RFMD. The PCB land pattern has been developed to accommodate lead and package tolerances. Since surface mount processes vary from company to company, careful process development is recommended.

#### Notes:

1. Shaded area represents Pin 1 location.

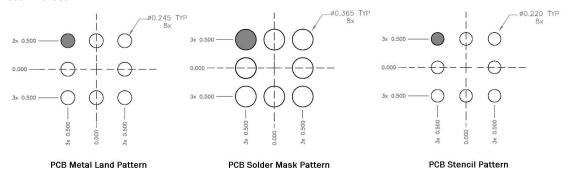

### **Tape and Reel**

Carrier tape basic dimensions are based on EIA 481. The pocket is designed to hold the part for shipping and loading onto SMT manufacturing equipment, while protecting the body and the solder terminals from damaging stresses. The individual pocket design can vary from vendor to vendor, but width and pitch will be consistent.

Carrier tape is wound or placed onto a shipping reel either 330mm (13 inches) in diameter or 178mm (7 inches) in diameter. The center hub design is large enough to ensure the radius formed by the carrier tape around it does not put unnecessary stress on the parts.

Prior to shipping, moisture sensitive parts (MSL level 2a-5a) are baked and placed into the pockets of the carrier tape. A cover tape is sealed over the top of the entire length of the carrier tape. The reel is sealed in a moisture barrier ESD bag with the appropriate units of desiccant and a humidity indicator card, which is placed in a cardboard shipping box. It is important to note that unused moisture sensitive parts need to be resealed in the moisture barrier bag. If the reels exceed the exposure limit and need to be rebaked, most carrier tape and shipping reels are not rated as bakeable at 125°C. If baking is required, devices may be baked according to section 4, table 4-1, of Joint Industry Standard IPC/JEDEC J-STD-033.

The table below provides information for carrier tape and reels used for shipping the devices described in this document.

#### Tape and Reel

| RFMD<br>Part<br>Number | Reel<br>Diameter<br>Inch (mm) | Hub<br>Diameter<br>Inch (mm) | Width<br>(mm) | Pocket<br>Pitch<br>(mm) | Feed   | Units<br>per<br>Reel |

|------------------------|-------------------------------|------------------------------|---------------|-------------------------|--------|----------------------|

| RF6650TR7              | 7 (178)                       | 2.4 (61)                     | 8             | 4                       | Single | 2500                 |

#### Notes:

1. Shaded area represents Pin 1 location.

# **Material Declaration**

| RFMD<br>Part<br>Number                                                                                                | Unit<br>Mass in<br>Grams<br>(Average) | Breakdown of<br>Component<br>(e.g. Filter,<br>Resistor,<br>Connector | Material Name<br>(e.g. Copper,<br>Matte Tin, Alloy) | Substance Name (e.g. Cu, Au,<br>Sn, SiO2) | CAS No.         | PPM    | Substance<br>Mass (mg) |  |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------|-----------------|--------|------------------------|--|

| RF6650                                                                                                                | 0.003                                 | Die                                                                  | Silicon                                             | Si                                        | 7440-21-3       | 608173 | 2.022929               |  |

| Pb-free Compliant?                                                                                                    | Yes                                   | Polyimide                                                            | Polyimide                                           | Polyimide                                 | 60842-76-4      | 8355   | 0.027792               |  |

| RoHS Compliant?                                                                                                       | Yes                                   | Under Bump                                                           | Titanium                                            | Ti                                        | 7440-32-6       | 41     | 0.000136               |  |

| D/C Compliance:                                                                                                       | N/A                                   | Metalizitaion                                                        | Copper                                              | Cu                                        | 7440-50-8       | 112    | 0.000373               |  |

| Pb Category:                                                                                                          | e4                                    |                                                                      | Nickel                                              | Ni                                        | 7440-02-0       | 1615   | 0.005373               |  |

|                                                                                                                       |                                       |                                                                      | Gold                                                | Au                                        | 7440-57-5       | 875    | 0.002911               |  |

|                                                                                                                       |                                       |                                                                      |                                                     | Polyethylene Terephthalate,<br>Silicone   | 25038-59-9      | 24763  | 0.082369               |  |

|                                                                                                                       |                                       |                                                                      | Filled                                              | Silica                                    | 7631-86-9       | 4866   | 0.016187               |  |

|                                                                                                                       |                                       | Back-side Coat-                                                      | Silicone                                            | Epoxy Resin                               | Proprietary     | 649    | 0.002158               |  |

|                                                                                                                       |                                       | ing                                                                  | Coating                                             | Acrylic Resin                             | Proprietary     | 649    | 0.002158               |  |

|                                                                                                                       |                                       |                                                                      |                                                     | Carbon Black                              | 7440-44-0       | 324    | 0.001079               |  |

|                                                                                                                       |                                       |                                                                      | Tin                                                 | Sn                                        | 7440-31-5       | 333846 | 1.110452               |  |

|                                                                                                                       |                                       | Lead-free Sol-<br>der Sphere                                         | Silver                                              | Ag                                        | 7440-22-4       | 13633  | 0.045348               |  |

|                                                                                                                       |                                       | dei Spriere                                                          | Copper                                              | Cu                                        | 7440-50-8       | 2098   | 0.006977               |  |

|                                                                                                                       |                                       |                                                                      |                                                     | ·                                         |                 |        |                        |  |

|                                                                                                                       |                                       |                                                                      |                                                     |                                           | Total Mass (mg) |        | 3.326                  |  |

| This Material Declaration is based solely on information, including analytical data, provided to RFMD by its vendors. |                                       |                                                                      |                                                     |                                           |                 |        |                        |  |