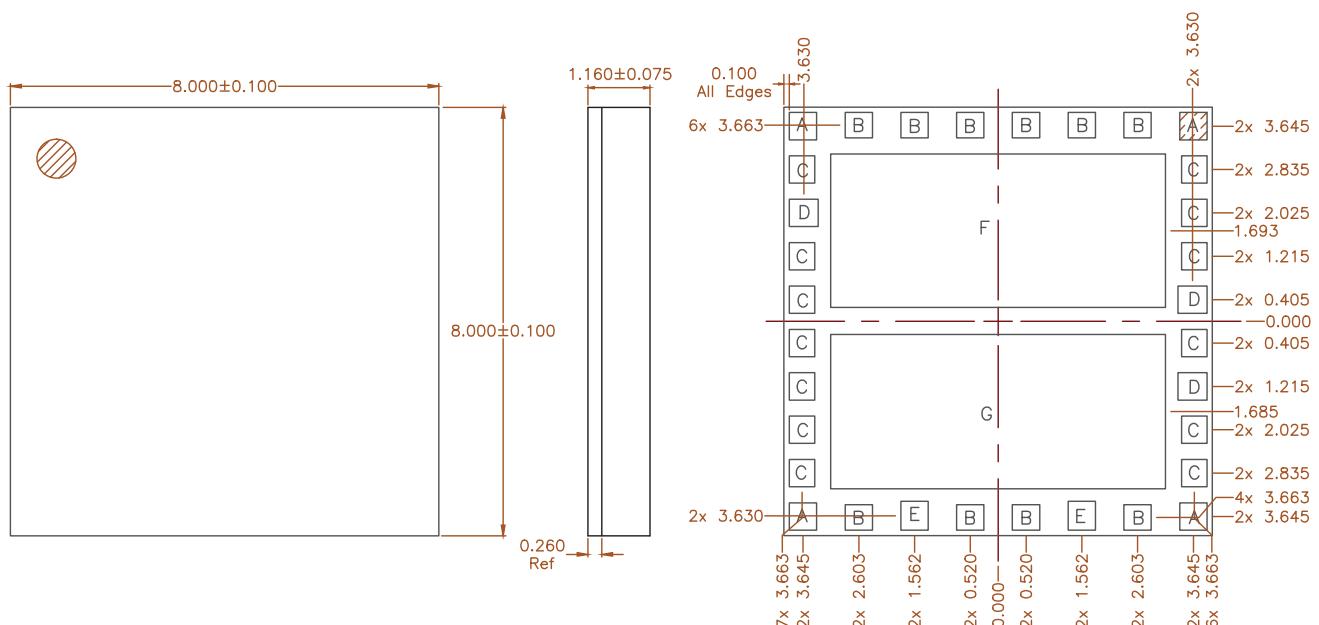

Package Style: LGA, 32 pin, 8mm x 8mm x 1.2mm

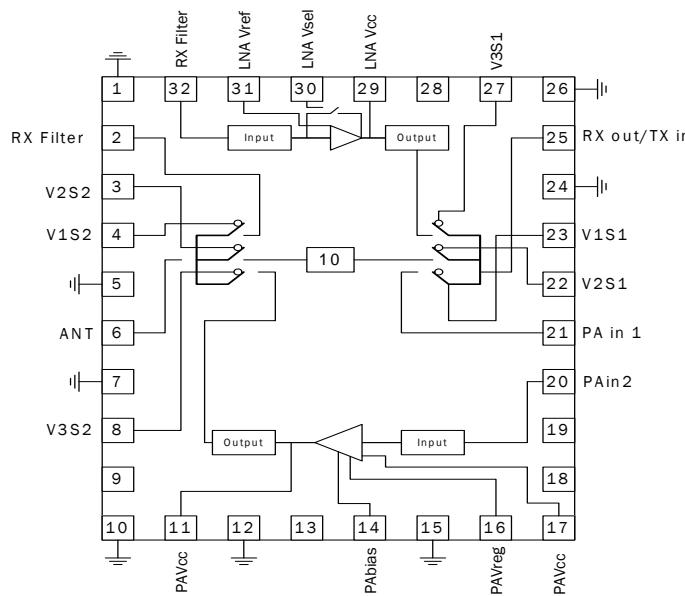

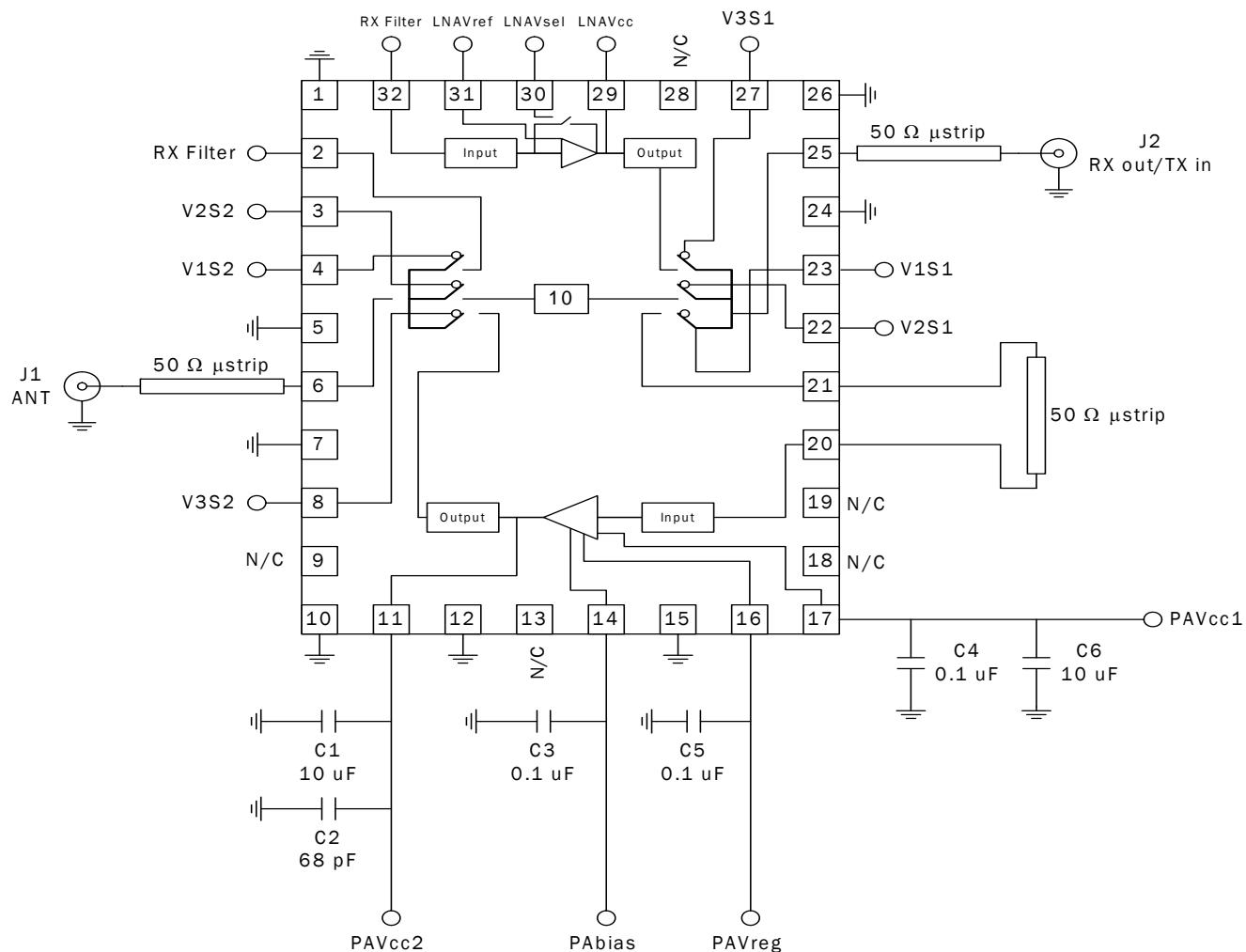

Functional Block Diagram

## Features

- Tx Output Power: 29.5dBm

- Tx Gain: 31dBm

- Rx Gain: 18dB

- Rx Noise Figure: 2.5dB

- Integrated LNA with Bypass Mode

## Applications

- 868MHz/900MHz ISM Band Application

- Single Chip RF Front End Module

- Portable Battery Powered Equipment

- Wireless Automatic Metering Applications

## Product Description

The RF6509 integrates a complete solution in a single Front-End Module (FEM) for AMR and Smart Grid solutions. The RF6509 integrates a 915MHz PA, some transmit (Tx) filtering, input and output switches, a Tx or receive (Rx) attenuation path, and an LNA with bypass mode. The RF6509 has a single-ended input and output for optimized ease of use and implementation. The pin-out of the FEM enables users to implement additional filtering external to the module, if needed. The device is provided in a LGA, 32 pin, 8mm x 8mm x 1.2mm package.

## Ordering Information

|               |                                                                  |

|---------------|------------------------------------------------------------------|

| RF6509        | 2.7V to 3.6V Module for Integration with 900MHz Smart Energy AMI |

| RF6509PCK-410 | Fully Assembled Evaluation Board and 5 loose pieces.             |

## Optimum Technology Matching® Applied

|                                              |                                      |                                                |                                    |

|----------------------------------------------|--------------------------------------|------------------------------------------------|------------------------------------|

| <input checked="" type="checkbox"/> GaAs HBT | <input type="checkbox"/> SiGe BiCMOS | <input checked="" type="checkbox"/> GaAs pHEMT | <input type="checkbox"/> GaN HEMT  |

| <input type="checkbox"/> GaAs MESFET         | <input type="checkbox"/> Si BiCMOS   | <input type="checkbox"/> Si CMOS               | <input type="checkbox"/> BiFET HBT |

| <input type="checkbox"/> InGaP HBT           | <input type="checkbox"/> SiGe HBT    | <input type="checkbox"/> Si BJT                | <input type="checkbox"/> LDMOS     |

RF MICRO DEVICES®, RFMD®, Optimum Technology Matching®, Enabling Wireless Connectivity™, PowerStar®, POLARIS™ TOTAL RADIO™ and UltimateBlue™ are trademarks of RFMD, LLC. BLUETOOTH is a trademark owned by Bluetooth SIG, Inc., U.S.A. and licensed for use by RFMD. All other trade names, trademarks and registered trademarks are the property of their respective owners. ©2006, RF Micro Devices, Inc.

## Absolute Maximum Ratings

| Parameter                      | Rating      | Unit |

|--------------------------------|-------------|------|

| <b>Overall</b>                 |             |      |

| DC Supply Voltage              | +5.0        | V    |

| Operating Ambient Temperature  | -40 to +85  | °C   |

| Storage Temperature            | -40 to +150 | °C   |

| <b>Low Noise Amplifier</b>     |             |      |

| DC Supply Current              | 32          | mA   |

| Input RF Power                 | 5           | dBm  |

| <b>Power Amplifier</b>         |             |      |

| DC Supply Current              | 1200        | mA   |

| Input RF Power                 | 10          | dBm  |

| <b>Transmit/Receive Switch</b> |             |      |

| Input RF Power                 | 33          | dBm  |

## Caution! ESD sensitive device.

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. Specified typical performance or functional operation of the device under Absolute Maximum Rating conditions is not implied.

The information in this publication is believed to be accurate and reliable. However, no responsibility is assumed by RF Micro Devices, Inc. ("RFMD") for its use, nor for any infringement of patents, or other rights of third parties, resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of RFMD. RFMD reserves the right to change component circuitry, recommended application circuitry and specifications at any time without prior notice.

RoHS (Restriction of Hazardous Substances): Compliant per EU Directive 2002/95/EC.

| Parameter                                     | Specification |            |       | Unit | Condition                                                                                                                                 |

|-----------------------------------------------|---------------|------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------|

|                                               | Min.          | Typ.       | Max.  |      |                                                                                                                                           |

| <b>Overall</b>                                |               |            |       |      | T = 25 °C, PAV <sub>CC1</sub> and PAV <sub>CC1</sub> = 3.2V, PA <sub>BIAS</sub> = 3.2V PAV <sub>REG</sub> = 2.85V, unless otherwise noted |

| Usable Frequency Range                        | 868           | 902 to 928 |       | MHz  |                                                                                                                                           |

| Input Impedance                               |               | 50         |       | Ω    |                                                                                                                                           |

| Input VSWR                                    |               | 2:1        |       |      |                                                                                                                                           |

| Output Load VSWR                              |               | 6:1        |       |      |                                                                                                                                           |

| <b>PA Section</b>                             |               |            |       |      |                                                                                                                                           |

| CW Output Power                               | 29            | 29.5       |       | dBm  | PA <sub>BIAS</sub> , P <sub>IN</sub> = -3 < 0 < 3dBm                                                                                      |

| Small Signal Gain                             | 29            | 31         |       | dB   | PA <sub>BIAS</sub> , P <sub>IN</sub> = -20dBm                                                                                             |

| Second Harmonic                               |               | -42.5      |       | dBc  | PA <sub>BIAS</sub> , P <sub>OUT</sub> = 29.5dBm at ANT port                                                                               |

| Third Harmonic                                |               | -72.5      |       | dBc  | PA <sub>BIAS</sub> , P <sub>OUT</sub> = 29.5dBm at ANT port                                                                               |

| Fourth Harmonic                               |               | -42.5      |       | dBc  | PA <sub>BIAS</sub> , P <sub>OUT</sub> = 29.5dBm at ANT port                                                                               |

| Input VSWR                                    |               | 2:1        |       |      |                                                                                                                                           |

| Output VSWR                                   |               | 6:1        |       |      | Oscillations <-60dBc                                                                                                                      |

| Power Supply Voltage                          | 2.7           | 3.2        | 3.6   | V    |                                                                                                                                           |

| Power Supply Current                          |               | 730        | 850   | mA   | PA <sub>BIAS</sub>                                                                                                                        |

|                                               |               | 70         | 100   | μA   | V <sub>CCPA</sub> = 3.2V, PA <sub>BIAS</sub> = 3.2V, PAV <sub>REG</sub> = 0V,                                                             |

| Power Supply Current for PA V <sub>BIAS</sub> |               | 18.0       | 20.0  | mA   |                                                                                                                                           |

| Power Supply Current for PA V <sub>REG</sub>  |               | 70.0       | 100.0 | μA   |                                                                                                                                           |

| <b>LNA Section</b>                            |               |            |       |      |                                                                                                                                           |

| HIGH GAIN MODE                                |               |            |       |      | LNAV <sub>CC</sub> = 3.0V, LNAV <sub>REF</sub> = 3.0V, LNAV <sub>SEL</sub> = 0.0V, PA <sub>BIAS</sub> = 0.0V, PAV <sub>REG</sub> = 0.0V   |

| Gain                                          | 17.5          | 18         | 18.5  | dB   | 902MHz to 928MHz                                                                                                                          |

|                                               | 15.5          | 16.5       | 17.5  | dB   | 868MHz                                                                                                                                    |

| Noise Figure                                  |               | 2.4        | 3.4   | dB   |                                                                                                                                           |

| Input IP3                                     | 7.5           | 9.5        | 12    | dBm  |                                                                                                                                           |

| Output VSWR                                   | 1.6:1         | 2:1        | 2.4:1 |      |                                                                                                                                           |

| Supply Current                                |               |            | 12    | mA   |                                                                                                                                           |

| Parameter                               | Specification |      |      | Unit | Condition                                                                                                                                               |

|-----------------------------------------|---------------|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | Min.          | Typ. | Max. |      |                                                                                                                                                         |

| <b>LNA Section (continued)</b>          |               |      |      |      |                                                                                                                                                         |

| LOW GAIN MODE                           |               |      |      |      | LNAV <sub>CC</sub> = 3.0V, LNAV <sub>REF</sub> = 3.0V, LNAV <sub>SEL</sub> = 0.0V, PA <sub>BIAS</sub> = 0.0V, PA <sub>REG</sub> = 0.0V                  |

| Gain                                    |               | -6   |      | dB   |                                                                                                                                                         |

| Noise Figure                            |               | 6    |      | dB   |                                                                                                                                                         |

| Supply Current                          |               | 3    |      | mA   |                                                                                                                                                         |

| LNAV <sub>CC</sub> Voltage              | 2.7           | 3.0  |      | V    |                                                                                                                                                         |

| LNAV <sub>REF</sub> Logic Level HIGH    | 2.7           | 3.0  |      | V    |                                                                                                                                                         |

| LNAV <sub>REF</sub> Logic Level LOW     | 0.0           |      | 0.3  | V    |                                                                                                                                                         |

| LNAV <sub>SEL</sub> Logic Level HIGH    | 1.8           | 3.0  |      | V    |                                                                                                                                                         |

| LNAV <sub>SEL</sub> Logic Level LOW     |               |      | 0.8  | V    |                                                                                                                                                         |

| Power Down Current                      |               |      | 10   | µA   | LNA_EN = LOW, LNAV <sub>SEL</sub> = LOW                                                                                                                 |

| <b>Transceiver Switch Section</b>       |               |      |      |      |                                                                                                                                                         |

| Insertion Loss TXin-PAin                | 0.9           | 1    | 1.1  | dB   | V <sub>1S1</sub> = 3.0V, V <sub>2S1</sub> = 0.0V, V <sub>3S1</sub> = 0.0V                                                                               |

| Isolation TXin-PAin                     | 25            | 27   |      | dB   | V <sub>1S1</sub> = 0.0V, V <sub>2S1</sub> = 3.0V, V <sub>3S1</sub> = 0.0V or V <sub>1S1</sub> = 0.0V, V <sub>2S1</sub> = 0.0V, V <sub>3S1</sub> = 3.0V  |

| TXin/RXout Return Loss (Thru path)      |               | -15  | -14  | dB   | V <sub>1S1</sub> = 0.0V, V <sub>2S1</sub> = 3.0V, V <sub>3S1</sub> = 0.0V and V <sub>1S2</sub> = 0.0V, V <sub>2S2</sub> = 3.0V, V <sub>3S2</sub> = 0.0V |

| TXin/RXout Return Loss (Transmit path)' |               |      | -9   | dB   | V <sub>1S1</sub> = 3.0V, V <sub>2S1</sub> = 0.0V, V <sub>3S1</sub> = 0.0V and V <sub>1S2</sub> = 0.0V, V <sub>2S2</sub> = 0.0V, V <sub>3S2</sub> = 3.0V |

| TXin/RXout Return Loss (Receive path)   |               |      | -9   | dB   | V <sub>1S1</sub> = 0.0V, V <sub>2S1</sub> = 0.0V, V <sub>3S1</sub> = 3.0V and V <sub>1S2</sub> = 3.0V, V <sub>2S2</sub> = 0.0V, V <sub>3S2</sub> = 0.0V |

| Switch Control Logic HIGH               | 2.7           | 3.0  |      | V    |                                                                                                                                                         |

| Switch Control Logic LOW                | 0.0           |      | 0.4  | V    |                                                                                                                                                         |

| Switch Control Current                  |               | 13.0 | 15.0 | µA   |                                                                                                                                                         |

| Parameter                       | Specification |      |      | Unit | Condition                                                                                               |

|---------------------------------|---------------|------|------|------|---------------------------------------------------------------------------------------------------------|

|                                 | Min.          | Typ. | Max. |      |                                                                                                         |

| <b>Antenna Switch Section</b>   |               |      |      |      |                                                                                                         |

| Insertion Loss ANT-LNAin        | 0.9           | 1    | 1.1  | dB   | $V_{1S2} = 3.0V, V_{2S2} = 0.0V, V_{3S2} = 0.0V$                                                        |

| Isolation ANT-LNAin             | 25            | 27   |      | dB   | $V_{1S2} = 0.0V, V_{2S2} = 3.0V, V_{3S2} = 0.0V$ or<br>$V_{1S2} = 0.0V, V_{2S2} = 3.0V, V_{3S2} = 0.0V$ |

| ANT Return Loss (Thru Path)     |               | -15  | -14  | dB   | $V_{1S1} = 0.0V, V_{2S1} = 3.0V, V_{3S1} = 0.0V$ or<br>$V_{1S2} = 0.0V, V_{2S2} = 3.0V, V_{3S2} = 0.0V$ |

| ANT Return Loss (Transmit Path) |               |      | -9   | dB   | $V_{1S1} = 3.0V, V_{2S1} = 0.0V, V_{3S1} = 0.0V$ or<br>$V_{1S2} = 0.0V, V_{2S2} = 0.0V, V_{3S2} = 3.0V$ |

| ANT Return Loss (Receive Path)  |               |      | -9   | dB   | $V_{1S1} = 0.0V, V_{2S1} = 0.0V, V_{3S1} = 3.0V$ or<br>$V_{1S2} = 3.0V, V_{2S2} = 0.0V, V_{3S2} = 0.0V$ |

| Switch Control Logic HIGH       | 2.7           | 3.0  |      | V    |                                                                                                         |

| Switch Control Logic LOW        | 0.0           |      | 0.4  | V    |                                                                                                         |

| Switch Control Current          |               | 13.0 | 15.0 | µA   |                                                                                                         |

| Pin       | Function               | Description                                                                                                                                                                                                                   |

|-----------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>1</b>  | <b>GND</b>             | Ground.                                                                                                                                                                                                                       |

| <b>2</b>  | <b>RX Filter Input</b> | RF output to enter the Rx filter (if used), 50Ω nominal impedance.                                                                                                                                                            |

| <b>3</b>  | <b>V2S2</b>            | Logic input to the Tx Switch arm 2 , selects/deselects thru path if Logic high/low respectively, see truth table.                                                                                                             |

| <b>4</b>  | <b>V1S2</b>            | Logic input to the Tx Switch arm 1, selects/deselects Low Noise Amplifier if Logic high/low respectively, see truth table.                                                                                                    |

| <b>5</b>  | <b>GND</b>             | Ground.                                                                                                                                                                                                                       |

| <b>6</b>  | <b>ANT</b>             | RF output to Antenna for the Tx/thru path and RF input from Antenna for the Rx/thru path, 50Ω nominal impedance.                                                                                                              |

| <b>7</b>  | <b>GND</b>             | Ground.                                                                                                                                                                                                                       |

| <b>8</b>  | <b>V3S2</b>            | Logic input to the Tx Switch arm 3, selects/deselects PA if Logic high/low respectively, see truth table.                                                                                                                     |

| <b>9</b>  | <b>NC</b>              | Not connected.                                                                                                                                                                                                                |

| <b>10</b> | <b>GND</b>             | Ground.                                                                                                                                                                                                                       |

| <b>11</b> | <b>PA VCC2</b>         | Collector power supply for Power Amplifier. Nominal 3.6V.                                                                                                                                                                     |

| <b>12</b> | <b>GND</b>             | Ground.                                                                                                                                                                                                                       |

| <b>13</b> | <b>NC</b>              | Not connected.                                                                                                                                                                                                                |

| <b>14</b> | <b>PA BIAS</b>         | Power supply for the PA Bias Network. Nominal 3.6V.                                                                                                                                                                           |

| <b>15</b> | <b>GND</b>             | Ground.                                                                                                                                                                                                                       |

| <b>16</b> | <b>PA VREG</b>         | Voltage set to PA Bias Level. Nominal 2.85V.                                                                                                                                                                                  |

| <b>17</b> | <b>PA VCC1</b>         | Collector power supply for PA driver stage. Nominal 3.6V.                                                                                                                                                                     |

| <b>18</b> | <b>NC</b>              | Not connected.                                                                                                                                                                                                                |

| <b>19</b> | <b>NC</b>              | Not connected.                                                                                                                                                                                                                |

| <b>20</b> | <b>PA IN</b>           | RF Input to the PA, 50Ω nominal impedance, needs to be connected externally to PA IN to SWITCH PIN through as short as possible 50Ω transmission line.                                                                        |

| <b>21</b> | <b>PA IN to SWITCH</b> | PA input to be connected to the Rx Switch through this pin, 50Ω nominal Impedance.                                                                                                                                            |

| <b>22</b> | <b>V2S1</b>            | Logic input to the Rx switch arm 2, selects/deselects Thru path if Logic high/low respectively, see truth table.                                                                                                              |

| <b>23</b> | <b>V1S1</b>            | Logic input to the Rx switch arm 1, selects/deselects PA if Logic high/low respectively, see truth table.                                                                                                                     |

| <b>24</b> | <b>GND</b>             | Ground.                                                                                                                                                                                                                       |

| <b>25</b> | <b>RX OUT/TX IN</b>    | Transceiver IN/OUT.                                                                                                                                                                                                           |

| <b>26</b> | <b>GND</b>             | Ground.                                                                                                                                                                                                                       |

| <b>27</b> | <b>V3S1</b>            | Logic input to the Rx switch arm 3, selects/deselects LNA if Logic high/low respectively, see truth table.                                                                                                                    |

| <b>28</b> | <b>NC</b>              | Not connected.                                                                                                                                                                                                                |

| <b>29</b> | <b>LNA VCC</b>         | Collector power supply for LNA. Nominal 3.0V.                                                                                                                                                                                 |

| <b>30</b> | <b>LNA VSEL</b>        | A logic low selects the high gain mode of the LNA, logic high selects the low gain mode.                                                                                                                                      |

| <b>31</b> | <b>LNA VREF</b>        | Voltage to set the bias of the LNA, nominal 3.0V, can be adjusted to shut the LNA off or set the quiescent current of the LNA to desired level.                                                                               |

| <b>32</b> | <b>LNA IN</b>          | RF input to LNA, nominal impedance 50Ω, the Rx filter output should be connected to this pin, If Rx filter is bypassed, pin 2 should be connected to this pin through an external 50Ω transmission line as short as possible. |

## Control Logic Table

| SW1  |      |      | SW2  |      |      | LNA      |          |         | PA            |         |         | PATH                                  |

|------|------|------|------|------|------|----------|----------|---------|---------------|---------|---------|---------------------------------------|

| V1S1 | V2S1 | V3S1 | V1S2 | V2S2 | V3S2 | LNA VSEL | LNA VREF | LNA VCC | PA VCC1 and 2 | PA Bias | PA VREG |                                       |

| High | Low  | Low  | Low  | Low  | High | High     | OFF      | OFF     | ON            | ON      | ON      | Tx path thru PA                       |

| Low  | High | Low  | Low  | High | Low  | High     | OFF      | OFF     | X*            | OFF     | OFF     | Tx/Rx Thru path with 10dB attenuation |

| Low  | Low  | High | High | Low  | Low  | Low      | ON       | ON      | X*            | OFF     | OFF     | Rx path thru LNA (High gain mode)     |

| Low  | Low  | High | High | Low  | Low  | High     | ON       | ON      | X*            | OFF     | OFF     | Rx path thru LNA (Low gain mode)      |

High indicates logic High of >2.7V and Low indicates logic Low of <0.2V.

\*An X means that the state of the pin doesn't matter.

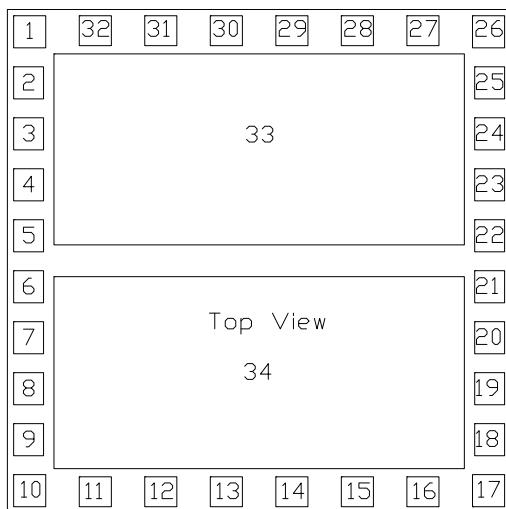

## Pin Out

## Package Drawing

### Notes:

Notes:

1. Shaded area represents Pin 1 location.

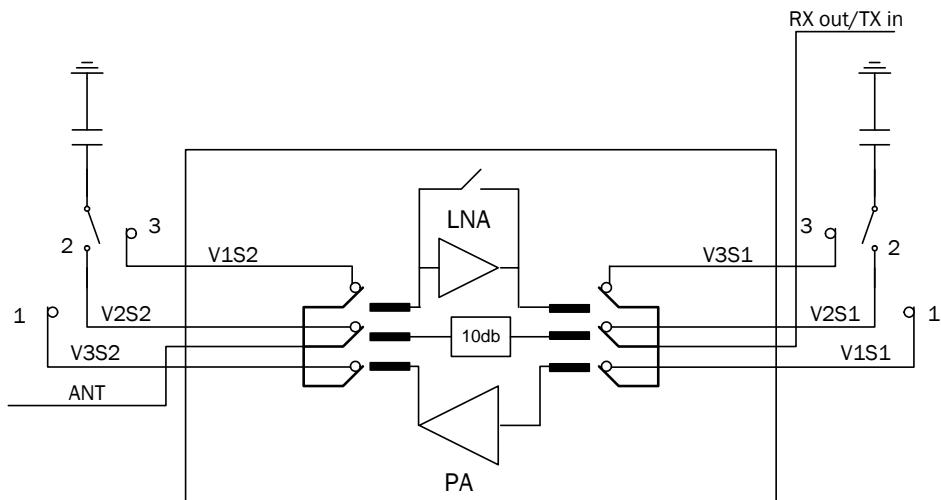

## Evaluation Board Schematic

Note: 1. If extra isolation is needed between Tx and Rx path, the filter can be used otherwise for  $\leq 50$ dB isolation, 50Ω micro-strip should be okay.

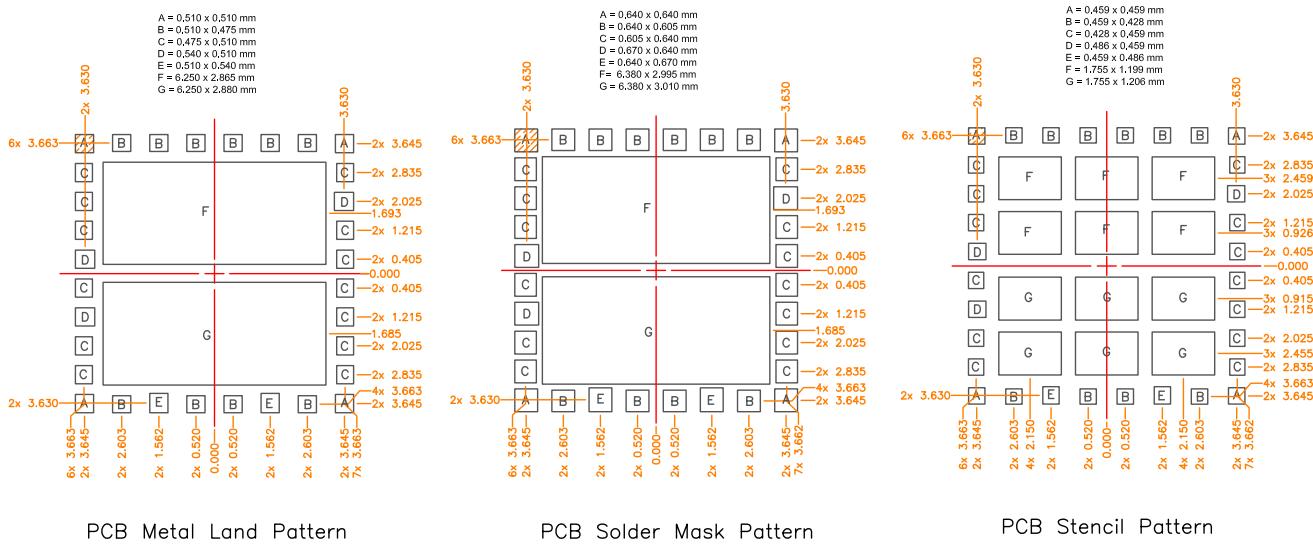

## PCB Design Requirements

## PCB Surface Finish

The PCB surface finish used for RFMD's qualification process is electroless nickel, immersion gold. Typical thickness is 3 $\mu$ inch to 8 $\mu$ inch gold over 180 $\mu$ inch nickel.

## PCB Land Pattern Recommendation

PCB land patterns are based on IPC-SM-782 standards when possible. The pad pattern shown has been developed and tested for optimized assembly at RFMD; however, it may require some modifications to address company specific assembly processes. The PCB land pattern has been developed to accommodate lead and package tolerances.

## PCB Solder Mask Pattern

Liquid Photo-Imageable (LPI) solder mask is recommended. The solder mask footprint will match what is shown for the PCB metal land pattern with a 2mil to 3mil expansion to accommodate solder mask registration clearance around all pads. The center-grounding pad shall also have a solder mask clearance. Expansion of the pads to create solder mask clearance can be provided in the master data or requested from the PCB fabrication supplier.

## Thermal Pad and Via Design

The PCB metal land pattern has been designed with a thermal pad that matches the die paddle size on the bottom of the device.

Thermal vias are required in the PCB layout to effectively conduct heat away from the package. The via pattern has been designed to address thermal, power dissipation and electrical requirements of the device as well as accommodating routing strategies.

The via pattern used for the RFMD qualification is based on thru-hole vias with 0.203mm to 0.330mm finished hole size on a 0.5mm to 1.2mm grid pattern with 0.025mm plating on via walls. If micro vias are used in a design, it is suggested that the quantity of vias be increased by a 4:1 ratio to achieve similar results.

## Notes:

1. Shaded area represents Pin 1 location.

**RoHS\* Banned Material Content**

RoHS Compliant: Yes

Package total weight in grams (g): 0.038

Compliance Date Code: 0547

Bill of Materials Revision: A

Pb Free Category: e3

| Bill of Materials | Parts Per Million (PPM) |    |    |       |     |      |

|-------------------|-------------------------|----|----|-------|-----|------|

|                   | Pb                      | Cd | Hg | Cr VI | PBB | PBDE |

| Die               | 0                       | 0  | 0  | 0     | 0   | 0    |

| Molding Compound  | 0                       | 0  | 0  | 0     | 0   | 0    |

| Lead Frame        | 0                       | 0  | 0  | 0     | 0   | 0    |

| Die Attach Epoxy  | 0                       | 0  | 0  | 0     | 0   | 0    |

| Wire              | 0                       | 0  | 0  | 0     | 0   | 0    |

| Solder Plating    | 0                       | 0  | 0  | 0     | 0   | 0    |

This RoHS banned material content declaration was prepared solely on information, including analytical data, provided to RFMD by its suppliers, and applies to the Bill of Materials (BOM) revision noted above.

\* DIRECTIVE 2002/95/EC OF THE EUROPEAN PARLIAMENT AND OF THE COUNCIL of 27 January 2003 on the restriction of the use of certain hazardous substances in electrical and electronic equipment