**√RoHS**

# Four Channel Squib Driver IC

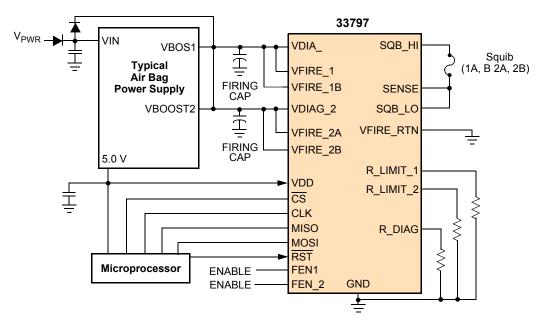

The Four Channel Squib Driver IC is a complete squib diagnostic and deployment interface for use in automotive air bag modules. Extensive diagnostics and system control features are incorporated to provide fail-safe operation. The device contains a serial peripheral interface (SPI) compatible 8-bit interface to allow microprocessor control.

The device has the capability to be used in a standard four channel squib driver IC or in a cross-coupled state with the high and low side squib drivers located on separate squib driver ICs. Both the high and low side output drivers are protected against temporary shorts to battery or ground. The current limit threshold is set by an external resistor.

#### **Features**

- · Four channel high side and low side 2.0 A FET switches

- Externally adjustable FET current limiting

- Adjustable current limit range: 0.8 to 2.0 A

- Individual channel current limit detection with timing duration measurement, communicated via the SPI

- · 8-Bit SPI for diagnostics and FET switch activation

- · Diagnostics for high side safing sensor status

- · Resistance and voltage diagnostics for squibs

- Squib driver IC capability to be used for cross-coupled driver firing application (allows high and low side FET switches to be located on separate squib driver ICs)

#### **SQUIB DRIVER**

| ORDERING INFORMATION |                                        |          |  |  |

|----------------------|----------------------------------------|----------|--|--|

| Device               | Temperature<br>Range (T <sub>A</sub> ) | Package  |  |  |

| MC33797BPEW/R2       | -40 to 85 °C                           | 32 SOICW |  |  |

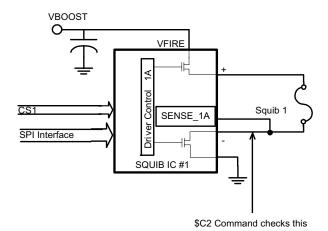

Figure 1. 33797 Simplified Application Diagram

<sup>\*</sup> This document contains certain information on a new product.

Specifications and information herein are subject to change without notice.

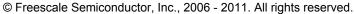

# INTERNAL BLOCK DIAGRAM

Figure 2. 33797 Simplified Internal Block Diagram

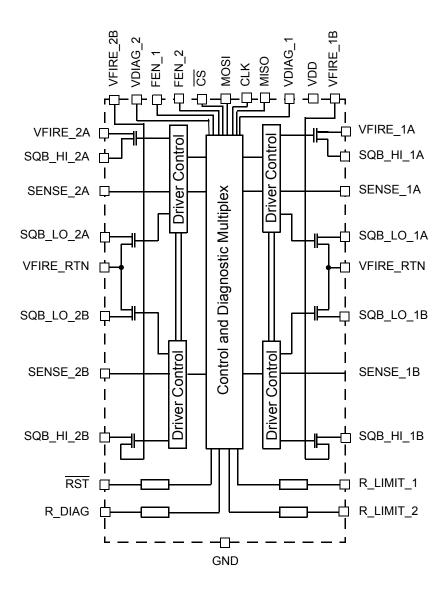

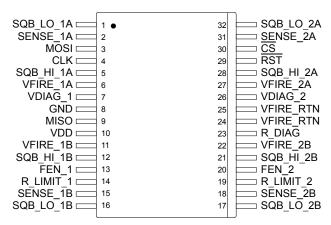

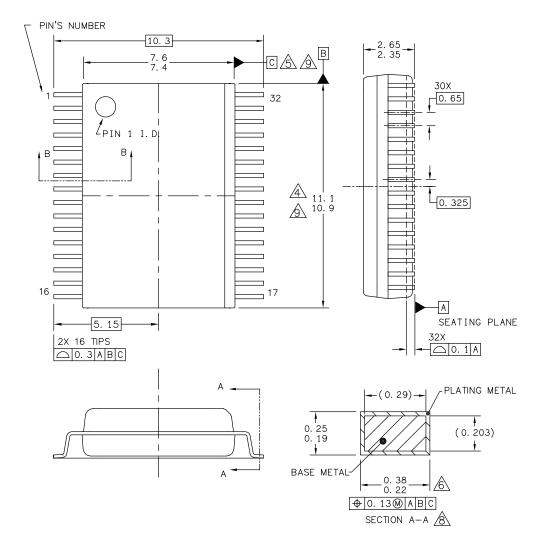

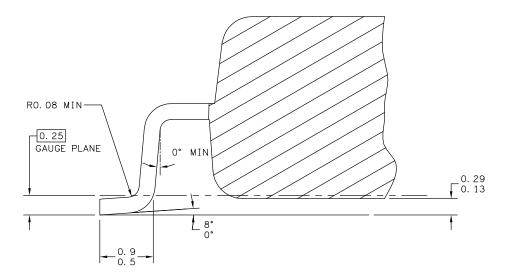

# **PIN CONNECTIONS**

**Figure 3. Pin Function Description**

**Table 1. Pin Function Description**

| Pin | Pin Name  | Pin Function | Formal Name                | Pin Description                                                                                                                                                                                            |

|-----|-----------|--------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SQB_LO_1A | Output       | Squib Lo 1A                | Drain of the low side switch that connects to the low pin of Squib_1A                                                                                                                                      |

| 2   | SENSE_1A  | Input        | Squib Sense 1A             | Used during standard applications involving a four channel squib driver IC or during cross-coupling applications involving two four channel squib driver ICs (squib driver IC #1 and squib driver IC #2).  |

| 3   | MOSI      | Input        | Data Input 1               | Serial data input for SPI interface.                                                                                                                                                                       |

| 4   | CLK       | Input        | Serial Clock               | Serial clock input for SPI interface.                                                                                                                                                                      |

| 5   | SQB_HI_1A | Output       | Squib Hi 1A                | Drain of the high side switch that connects to the low pin of Squib_1A                                                                                                                                     |

| 6   | VFIRE_1A  | Supply       | Squib Firing Supply<br>1A  | Firing supply pin for Squib_1A.                                                                                                                                                                            |

| 7   | VDIAG_1   | Input        | Squib Diagnostic 1A and 1A | Diagnostic pin for high side safing sensor for squibs 1A and 1B and the VFIRE supply voltage.                                                                                                              |

| 8   | GND       | Ground       | Device Ground              | Device ground pin for internal logic and diagnostic circuitry.                                                                                                                                             |

| 9   | MISO      | Output       | Data Output 0              | Serial data output for SPI interface.                                                                                                                                                                      |

| 10  | VDD       | Input        | Logic Power                | Device power pin for internal logic and diagnostic circuitry.                                                                                                                                              |

| 11  | VFIRE_1B  | Supply       | Squib Firing Supply<br>1B  | Firing supply pin for Squib_1B.                                                                                                                                                                            |

| 12  | SQB_HI_1B | Output       | Squib Hi 1B                | Drain of the high side switch that connects to the low pin of Squib_1B                                                                                                                                     |

| 13  | FEN_1     | Input        | FET Driver 1A and 1B       | Active high input signal to enable operation of the squib_1A and Squib_1BFET drivers.                                                                                                                      |

| 14  | R_LIMIT_1 | Output       | Limit Resistor - 1A and 1B | External resistor to ground is used to set current limit for Squib_1A and squib_1B FET drivers.                                                                                                            |

| 15  | SENSE_1B  | Input        | Squib Sense 1B             | Used during standard applications involving a four channel squib driver IC and during cross-coupling applications involving two four channel squib driver ICs (squib driver IC #1 and squib driver IC #2). |

Table 1. Pin Function Description (continued)

| Pin | Pin Name  | Pin Function | Formal Name                    | Pin Description                                                                                                                                                                                            |

|-----|-----------|--------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16  | SQB_LO_1B | Output       | Squib Lo 1B                    | Drain of the low side switch that connects to the low pin of Squib_1B                                                                                                                                      |

| 17  | SQB_LO_2B | Output       | Squib Lo 2B                    | Drain of the low side switch that connects to the low pin of Squib_2B                                                                                                                                      |

| 18  | SENSE_2B  | Input        | Squib Sense 2B                 | Used during standard applications involving a four channel squib driver IC and during cross-coupling applications involving two four channel squib driver ICs (squib driver IC #1 and squib driver IC #2). |

| 19  | R_LIMIT_2 | Output       | Limit Resistor - 2A and 2B     | External resistor to ground is used to set current limit for Squib_2A and squib_2B FET drivers.                                                                                                            |

| 20  | FEN_2     | Input        | FET Driver 2A and 2B           | Active high input signal to enable operation of the squib_2A and Squib_2B FET drivers.                                                                                                                     |

| 21  | SQB_HI_2B | Output       | Squib Hi 2B                    | Drain of the high side switch that connects to the low pin of Squib_2B.                                                                                                                                    |

| 22  | VFIRE_2B  | Supply       | Squib Firing Supply<br>2B      | Firing supply pin for squib_2B.                                                                                                                                                                            |

| 23  | R_DIAG    | Input        | Limit Resistor -<br>Diagnostic | External resistor to ground is used to set the diagnostic current for squib resistance.                                                                                                                    |

| 24  | VFIRE_RTN | Ground       | Squib Fire Power<br>Ground     | Power Ground for squibs 1A, 1B, 2A, and 2B                                                                                                                                                                 |

| 25  | VFIRE_RTN | Ground       | Squib Fire Power<br>Ground     | Power Ground for squibs 1A, 1B, 2A, and 2B                                                                                                                                                                 |

| 26  | VDIAG_2   | Supply       | Squib Diagnostic 2A and 2b     | Diagnostic pin for high side safing sensor for squibs 2A and 2B and the VFIRE supply voltage.                                                                                                              |

| 27  | VFIRE_2A  | Supply       | Squib Firing Supply<br>2A      | Firing supply pin for squib_ 2A                                                                                                                                                                            |

| 28  | SQB_HI_2A | Output       | Squib Hi 2A                    | Drain of the high side switch that connects to the low pin of Squib_2A                                                                                                                                     |

| 29  | RST       | Input        | Reset                          | Reset, Active Low                                                                                                                                                                                          |

| 30  | CS        | Input        | Chip Select                    | Chip Select for SPI interface, Active Low                                                                                                                                                                  |

| 31  | SENSE_2A  | Input        | Squib Sense 2A                 | Used during standard applications involving a four channel squib driver IC or during cross-coupling applications involving two four channel squib driver ICs (squib driver IC #1 and squib driver IC #2).  |

| 32  | SQB_LO_2A | Output       | Squib Lo 2A                    | Drain of the low side switch that connects to the low pin of Squib_2A                                                                                                                                      |

### **ELECTRICAL CHARACTERISTICS**

#### **MAXIMUM RATINGS**

#### **Table 2. Maximum Ratings**

All voltages are with respect to ground, unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Rating                                                                                                                                                                                                                                                                     | Symbol                                               | Value                            | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------|------|

| INPUT ELECTRICAL RATINGS                                                                                                                                                                                                                                                   |                                                      |                                  |      |

| Voltage on VDD                                                                                                                                                                                                                                                             | V <sub>DD</sub>                                      | 7.0                              | V    |

| Voltage on Input pins CS, CLK, D1, D0, FEN_1, FEN_2, RESET, R_DIAG, R_LIMIT_X                                                                                                                                                                                              | VI                                                   | -0.3 to V <sub>DD</sub> + 0.3    |      |

| Voltage on Squib pins SQB_HI_XX, SQB_LO_XX, SENSE_XX                                                                                                                                                                                                                       | V <sub>VFIRE_XX</sub>                                | -0.3 to V <sub>VFIRE</sub> + 0.3 | V    |

| Voltage on pins VDIAG_X, VFIRE_XX                                                                                                                                                                                                                                          | VDIAG_X                                              | -0.3 to 35                       | V    |

| ESD Voltage <sup>(1)</sup> Human Body Model Machine Model                                                                                                                                                                                                                  | V <sub>ESD1</sub>                                    | ±2000<br>±200                    | V    |

| Maximum $V_{VFIRE}$ with Pulsed Output $^{(2)}$ , $^{(3)}$ $R_{SQUIB}$ = 2.0 $\Omega$ , $t_{ON}$ = 0.8 ms, $I_{SQUIB}$ = 2.24 A $R_{SQUIB}$ = 1.2 $\Omega$ , $t_{ON}$ = 0.8 ms, $I_{SQUIB}$ = 2.24 A $R_{SQUIB}$ = 0.1 $\Omega$ , $t_{ON}$ = 0.60 ms, $I_{SQUIB}$ = 2.24 A | V <sub>FPULSE</sub>                                  | 35<br>25<br>25                   | V    |

| THERMAL RATINGS                                                                                                                                                                                                                                                            |                                                      |                                  |      |

| Storage Temperature                                                                                                                                                                                                                                                        | T <sub>STG</sub>                                     | 155                              | °C   |

| Junction Temperature Ambient $ \begin{array}{c} \text{Continuous (Prior to Squib Deployment)} \\ t \leq 5.0 \text{ ms (Post-squib Deployment)} \end{array} $                                                                                                               | T <sub>A</sub> T <sub>JCONT</sub> T <sub>JDPYD</sub> | 85<br>100<br>300                 | °C   |

| Peak Package Reflow Temperature During Reflow (4), (5)                                                                                                                                                                                                                     | T <sub>PPRT</sub>                                    | Note 5.                          | °C   |

| Thermal Resistance (Junction-to-Ambient)                                                                                                                                                                                                                                   | $R_{	hetaJA}$                                        | 74                               | °C/W |

- 1 ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ), ESD2 testing is performed in accordance with the Machine Model ( $C_{ZAP}$  = 200 pF,  $R_{ZAP}$  = 0  $\Omega$ ).

- With a nominal squib load, the FET squib driver will not enter thermal shutdown until the driver has been active for a minimum of 2.1 ms. The individual squib driver thermal shutdown will not affect other squib driver firing "ON" times. With a shorted squib load, the FET squib driver will not enter thermal shutdown until the driver has been active for a minimum of 2.1 ms. When the thermal shutdown limit is exceeded, the FET driver will turn OFF and the thermal status bit will be set to 1. The FET squib driver can be activated through the arm/fire command when the TEMP<sub>RENABLE</sub> (MIN) is reached (thermal shutdown status "0"). Nominal squib load is  $2.15 \Omega \pm 0.15 \Omega$ . Shorted squib load is  $0.1 \Omega$ .

- Three squib driver with  $R_{SQUIB}$  = 0.1  $\Omega$  conditions. Remaining squib driver conditions:  $R_{SQUIB}$  = 1.2  $\Omega$ ,  $t_{ON}$  = 4.0 ms,  $t_{SQUIB}$  = 2.0 A,  $t_{SQUIB}$  = 4.0 ms,  $t_{SQUIB}$  = 4.0 ms, t

- 4 Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 5. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

# ELECTRICAL CHARACTERISTICS MAXIMUM RATINGS

### **Table 2. Maximum Ratings**

All voltages are with respect to ground, unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Rating                | Symbol | Value | Unit |

|-----------------------|--------|-------|------|

| OPERATING RATINGS (6) |        |       |      |

Low Side FET Fire Conditions

$\begin{array}{l} R_{SQUIB},\,t_{ON},\,l_{SQUIB},\,V_{SQUIBHI} \\ 2.0\;\Omega,\,2.6\;ms,\,3.0\;A,\,16\;V \\ 1.2\;\Omega,\,2.6\;ms,\,3.0\;A,\,16\;V \\ 0.1\;\Omega,\,2.6\;ms,\,3.0\;A,\,16\;V \end{array}$

#### Notes

6 Operating ratings indicate conditions for which the device is intended to be functional. For guaranteed specifications and test conditions, refer to the static and dynamic electrical characteristics tables on the following pages.

# STATIC ELECTRICAL CHARACTERISTICS

#### **Table 3. Static Electrical Characteristics**

Characteristics noted under conditions 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V; 7.0 V  $\leq$  V<sub>VFIRE\_XX</sub>  $\leq$  35 V; V<sub>VDIAG\_X</sub> = V<sub>VFIRE\_XX</sub>; FEN 1 = FEN 2 = V<sub>DD</sub>; R<sub>R\_LIMIT\_X</sub> = 10 k $\Omega$  ±1%, R<sub>R\_DIAG</sub> = 10 k $\Omega$  ±1%, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  +85 °C, GND = 0, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                                                                                                   | Symbol                 | Min                    | Тур              | Max                   | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|------------------|-----------------------|------|

| INPUT VOLTAGE (VDD)                                                                                                                                                                                                                              |                        |                        |                  |                       |      |

| Input Voltage                                                                                                                                                                                                                                    | V <sub>DD</sub>        | 4.75                   | 5.0              | 5.25                  | V    |

| FET DRIVERS                                                                                                                                                                                                                                      | •                      |                        |                  |                       |      |

| Leakage Current at Minimum High Side Driver Breakdown Voltage                                                                                                                                                                                    | I <sub>DHSD</sub>      | _                      | 39               | 100                   | μA   |

| Leakage Current at Minimum Low Side Driver Breakdown Voltage                                                                                                                                                                                     | I <sub>DLSD</sub>      | -                      | 65               | 100                   | μA   |

| High Side Driver Current Limit Range Set via Rlimit Resistor with Low Battery Condition $t_{ON} \leq 4.0 \text{ ms, } R_{R\_LIMIT\_X} = 10 \text{ k}\Omega,  5.0 \text{ V} \leq \text{V}_{VFIRE} \leq 7.0 \text{ V}, \\ R_{SQUIB} = 2.0  \Omega$ | I <sub>HS(LBAT)</sub>  | 1.09                   | 1.4              | 2.9                   | A    |

| High Side Driver Low Current Limit Range Set via Rlimit Resistor $t_{ON} \leq 2.6 \text{ ms}, \ R_{R\_LIMIT\_X} = R_L = 4.32 \ k\Omega, \ 7.0 \ V \leq V_{VFIRE} \leq 35 \ V$                                                                    | I <sub>HS(LOSET)</sub> | 0.81                   | 0.93             | 1.03                  | Α    |

| High Side Driver Nominal Current Limit Range Set via Rlimit Resistor $t_{ON} \leq 2.6 \text{ ms}, \ R_{R\_LIMIT\_X} = R_L = 10 \text{ k}\Omega, \ 7.0 \text{ V} \leq \text{V}_{VFIRE} \leq 35 \text{ V}$                                         | I <sub>HS(NOM)</sub>   | 1.21                   | 1.4              | 1.54                  | А    |

| High Side Driver High Current Limit Range Set via Rlimit Resistor $t_{ON} \le 0.8 \text{ ms}, R_{R\_LIMIT\_X} = R_L = 45.3 \text{ k}\Omega, 7.0 \text{ V} \le V_{VFIRE} \le 35 \text{ V}$                                                        | I <sub>HS(HISET)</sub> | 1.76                   | 2.0              | 2.24                  | А    |

| Low Side Drivers Current Limit 7.0 V = SQLO < 16 V SQLO = 16 V                                                                                                                                                                                   | I <sub>LS</sub>        | 2.1<br>2.24            | 2.47<br>2.65     | 3.0<br>3.14           | A    |

| High Side Driver Current Limit Detect Threshold $^{(7)}$<br>7.0 V $\leq$ V <sub>VFIRE</sub> $\leq$ 35 V                                                                                                                                          | I <sub>MEAS</sub>      | I <sub>HS</sub> x 0.85 | -                | I <sub>HS</sub> x 1.0 | Α    |

| Driver ON Resistance (per FET)  V <sub>VFIRE</sub> = 5.0 V, I <sub>LOAD</sub> = 0.5 A                                                                                                                                                            | R <sub>DS(ON)</sub>    | _                      | -                | 1.0                   | Ω    |

| VDD Operating Current Standby (Diagnostics off, SPI "OFF") No Fire—Worst Case Diagnostics (\$83/\$2F Command Active) Firing (with All FET Drivers "ON")                                                                                          | I <sub>DD</sub>        |                        | 2.0<br>15<br>4.3 | 5.0<br>18.5<br>6.0    | mA   |

| VFIRE Quiescent Current <sup>(8)</sup> With Diagnostics Off                                                                                                                                                                                      | I <sub>RRE</sub>       | 22                     | 34               | 55                    | μА   |

| VDIAG Current During Squib Diagnostics With Squib Resistance Diagnostics Active                                                                                                                                                                  | I <sub>RRE</sub>       | 32                     | 37               | 43                    | mA   |

| VFIRE Operating Current During Firing Excluding Firing Current, I <sub>HS</sub> = 2.0 A                                                                                                                                                          | I <sub>RRE</sub>       | _                      | 1.8              | 11                    | mA   |

| VDIAG Operating Current During Firing Per V <sub>DIAG</sub> pin, excluding Firing Current, I <sub>HS</sub> = 2.0 A                                                                                                                               | I <sub>RRE</sub>       | _                      | 140              | 200                   | μА   |

### Notes

- 7 Guaranteed by design

- 8 VFIRE quiescent current includes any leakage current through squib.

33797

Characteristics noted under conditions 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V; 7.0 V  $\leq$  V<sub>VFIRE\_XX</sub>  $\leq$  35 V; V<sub>VDIAG\_X</sub> = V<sub>VFIRE\_XX</sub>; FEN 1 = FEN 2 = V<sub>DD</sub>; R<sub>R\_LIMIT\_X</sub> = 10 k $\Omega$  ±1%, R<sub>R\_DIAG</sub> = 10 k $\Omega$  ±1%, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  +85 °C, GND = 0, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                      | Symbol                   | Min | Тур | Max  | Unit |

|-------------------------------------------------------------------------------------|--------------------------|-----|-----|------|------|

| VFIRE1A / VFIRE2A Current During High Side Safing Sensor Diagnostics (Command \$CO) | I <sub>RRE</sub>         |     |     |      | μA   |

| Per VFIREXA pin, with High Side Safing Sensor Diagnostic active                     |                          | 260 | 350 | 415  |      |

| VFIRE1B / VFIRE2B Current During High Side Safing Sensor Diagnostics (Command \$CO) | I <sub>RRE</sub>         |     |     |      | μA   |

| Per VFIREXB pin, with High Side Safing Sensor Diagnostic active                     |                          | 22  | 32  | 55   |      |

| VFIRE1B / VFIRE2B Current During VFIRE Diagnostics (Command \$C5)                   | I <sub>RRE</sub>         |     |     |      | mA   |

| Either VFIRE!B or VFIRE2B Diagnostic active                                         |                          | 0.3 | 2.0 | 3.8  |      |

| VFIRE Quiescent Current - Total                                                     | I <sub>QVFIRETOTAL</sub> |     |     |      | μA   |

| All VFIRE pins measured together, with Diagnostics Off                              |                          | 90  | 135 | 180  |      |

| Maximum Allowable External Capacitance to Ground (9)                                | CS <sub>MAX</sub>        |     |     |      | μF   |

| Per Squib pin SQB_LO and SQB_HI                                                     |                          | _   | -   | 0.12 |      |

| Maximum Allowable External Resistance to Ground During Firing (9)                   | RS <sub>MAX</sub>        |     |     |      | Ω    |

| VFIRE_RTN pin to Ground                                                             |                          | _   | -   | 0.15 |      |

| Individual FET Driver Thermal Shutdown (9), (10)                                    | T <sub>SD</sub>          | 160 | -   | 190  | С    |

| FET Driver Thermal Shutdown Re-enable Threshold After Drive Cool down (9), (10)     | T <sub>REN</sub>         | 90  | -   | 110  | С    |

#### FET DRIVERS HIGH AND LOW SIDE DRIVER TRANSISTOR STATUS/DIAGNOSTICS (\$82, \$83 COMMANDS)

| Voltage Transistor Test Threshold for High Side Driver Transistor             | V <sub>TRANTST1</sub> | 5.5 | 6.0 | 6.5 | V  |

|-------------------------------------------------------------------------------|-----------------------|-----|-----|-----|----|

| High Side Driver Current Limit During High Side Driver Transistor Diagnostics | ITRANTST1             |     |     |     | mA |

| $15 \text{ V} \leq \text{V}_{\text{VFIRE}\_XX} \leq 35 \text{ V}$             |                       | 2.0 | 10  | 50  |    |

| Voltage Transistor Test Threshold for Low Side Driver Transistor              | V <sub>TRANTST2</sub> | 1.0 | 1.4 | 2.0 | V  |

| Low Side Driver Current Limit During Low Side Driver Transistor Diagnostics   | I <sub>TRANTST2</sub> |     |     |     | mA |

| 15 V ≤ V <sub>VFIRE_XX</sub> ≤ 35 V                                           |                       | 2.0 | 10  | 50  |    |

### FEN INPUT PIN (FEN\_1 AND FEN\_2)

| Internal Current Pull-down       | I <sub>FEN</sub>     | -25                    | -40 | -50                    | μА |

|----------------------------------|----------------------|------------------------|-----|------------------------|----|

| Logic Low Level                  | V <sub>FEN(LO)</sub> | 0.0                    | 2.5 | 0.35 x V <sub>DD</sub> | V  |

| Fire Enable Pin Logic High Level | V <sub>FEN(HI)</sub> | 0.65 x V <sub>DD</sub> | 2.5 | 1.0 x V <sub>DD</sub>  | V  |

- 9 Guaranteed by design.

- With a nominal squib load, the FET squib driver will not enter thermal shutdown until the driver has been active for a minimum of 2.1 ms. The individual squib driver thermal shutdown will not affect other squib driver firing ON times. With a shorted squib load, the FET squib driver will not enter thermal shutdown until the driver has been active for a minimum of 2.1 ms. When the thermal shutdown limit is exceeded, the FET driver will turn OFF and the thermal status bit will be set to 1. The FET squib driver can be activated through the arm/fire command when the TEMP<sub>RENABLE</sub> (MIN) is reached (thermal shutdown status "0"). Nominal squib load:  $2.15 \Omega \pm 0.15 \Omega$ . Shorted squib load:  $2.15 \Omega \pm 0.15 \Omega$ .

Characteristics noted under conditions 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V; 7.0 V  $\leq$  V<sub>VFIRE\_XX</sub>  $\leq$  35 V; V<sub>VDIAG\_X</sub> = V<sub>VFIRE\_XX</sub>; FEN 1 = FEN 2 = V<sub>DD</sub>; R<sub>R\_LIMIT\_X</sub> = 10 k $\Omega$  ±1%, R<sub>R\_DIAG</sub> = 10 k $\Omega$  ±1%, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  +85 °C, GND = 0, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                  | Symbol               | Min                    | Тур | Max                    | Unit |

|---------------------------------|----------------------|------------------------|-----|------------------------|------|

| RST INPUT PIN (ACTIVE LOW) (11) |                      |                        |     |                        |      |

| System Reset Threshold          | V <sub>DDRST</sub>   | _                      | -   | 4.1                    | V    |

| Internal Current Pull-down      | I <sub>RST</sub>     | -6.0                   | -10 | -15                    | μΑ   |

| RST Logic Low Level             | V <sub>RST(LO)</sub> | 0.0                    | 2.5 | 0.35 x V <sub>DD</sub> | V    |

| RST Logic High Level            | V <sub>RST(HI)</sub> | 0.65 x V <sub>DD</sub> | 2.5 | 1.0 x V <sub>DD</sub>  | V    |

# SQUIB DIAGNOSTICS (\$D0-\$D3 COMMANDS) (12)

| Diagnostic Current Through Squib (13)  | I <sub>DIAG</sub> | 30  | 34  | 40.5 | mA |

|----------------------------------------|-------------------|-----|-----|------|----|

| Resistance Threshold 1 <sup>(13)</sup> | R <sub>TH1</sub>  | 1.2 | 1.4 | 1.6  | Ω  |

| Resistance Threshold 2 (13)            | R <sub>TH2</sub>  | 1.6 | 1.8 | 2.1  | Ω  |

| Resistance Threshold 3 (13)            | R <sub>TH3</sub>  | 2.1 | 2.4 | 2.6  | Ω  |

| Resistance Threshold 4 <sup>(13)</sup> | R <sub>TH4</sub>  | 2.6 | 2.9 | 3.2  | Ω  |

| Resistance Threshold 5 <sup>(13)</sup> | R <sub>TH5</sub>  | 3.3 | 3.7 | 4.4  | Ω  |

| Resistance Threshold 6 <sup>(13)</sup> | R <sub>TH6</sub>  | 4.6 | 5.4 | 6.0  | Ω  |

| Resistance Threshold 7 <sup>(13)</sup> | R <sub>TH7</sub>  | 5.7 | 6.5 | 7.1  | Ω  |

| Resistance Threshold 8 <sup>(13)</sup> | R <sub>TH8</sub>  | 6.7 | 7.8 | 8.5  | Ω  |

# SQUIB SHORT-TO-BATTERY/GROUND DIAGNOSTICS AND SQUIB HARNESS SHORT-TO-BATTERY/GROUND DIAGNOSTICS WITH AN OPEN SQUIB (\$C1, \$C3 COMMANDS)

| Voltage Threshold for SQB_LO and SQB_HI Shorted to V <sub>PWR</sub>                                                  | V <sub>THSB</sub>      |      |      |      | V  |

|----------------------------------------------------------------------------------------------------------------------|------------------------|------|------|------|----|

| $7.0 \text{ V} \leq \text{V}_{\text{VDIAG}_{X}} \leq 35 \text{ V}$                                                   |                        | 5.7  | 6.0  | 6.4  |    |

| Voltage Threshold for SQB_LO and SQB_HI Shorted to Ground                                                            | $V_{THSG}$             |      |      |      | V  |

| $7.0 \text{ V} \leq \text{V}_{\text{VDIAG}_{\text{X}}} \leq 35 \text{ V}$                                            |                        | 1.3  | 1.4  | 1.6  |    |

| Current Sink Shorts Measurements I_SQB_LO_XX (14)                                                                    | I <sub>SINKSHRTS</sub> |      |      |      | μА |

| 1.0 V ≤ SENSE_XX ≤ 16 V, Typical = 800 μA                                                                            |                        | -500 | -800 | -900 |    |

| Current Source Shorts Measurements I_SQB_HI_XX (14)                                                                  | I <sub>SOURSHRTS</sub> |      |      |      | mA |

| $1.0 \text{ V} \le \text{SENSE\_XX} \le 16 \text{ V}, 7.0 \text{ V} \le \text{V}_{\text{VDIAG\_X}} \le 35 \text{ V}$ |                        | 1.7  | 3.5  | 3.7  |    |

| Voltage Threshold for SQB_LO or SQB_HI Shorted to V <sub>PWR</sub> with an Open Squib using \$C3 Command             | V <sub>THSB_SO</sub>   |      |      |      | V  |

| R <sub>SQUIB</sub> = Open                                                                                            |                        | 5.75 | -    | 6.79 |    |

- 11 Reset Bar range of operation: The minimum system reset bar threshold/active will be set to "0" for a value of V<sub>DD</sub> ≤ 4.1 V.

- By changing the R\_DIAG resistor value, the resistance thresholds can be varied in a linear relationship. The R\_DIAG resistance can be changed by ±10% to shift the thresholds by ±10%. Design goal for resistance threshold change is ±15%. R\_DIAG threshold limit may have to be changed to accommodate ±15% change. Example: Shifting the R\_DIAG resistance value ±10%, the resistance threshold will change by ±10%. Refer to Table 4, page 12.

- 13  $R_{R DIAG} = 10 \text{ k}\Omega \pm 1.0\%$

- 14 XX = 1A, 1B, 2A, or 2B.

Characteristics noted under conditions 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V; 7.0 V  $\leq$  V<sub>VFIRE\_XX</sub>  $\leq$  35 V; V<sub>VDIAG\_X</sub> = V<sub>VFIRE\_XX</sub>; FEN 1 = FEN 2 = V<sub>DD</sub>; R<sub>R\_LIMIT\_X</sub> = 10 k $\Omega$  ±1%, R<sub>R\_DIAG</sub> = 10 k $\Omega$  ±1%, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  +85 °C, GND = 0, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                  | Min                                                                                                                                                                        | Тур       | Max                  | Unit                 |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------|----------------------|

| V <sub>THSG_SO</sub>    | 1.3                                                                                                                                                                        | 1.8       | 2.0                  | V                    |

| QB_LO_XX (\$C2          | COMMAND                                                                                                                                                                    | )         | •                    | I                    |

| I <sub>THSQB</sub> CON  | 150                                                                                                                                                                        | _         | 350                  | μА                   |

| 3, \$E8 COMMAN          | DS)                                                                                                                                                                        | ı         | ı                    |                      |

| V <sub>THSQBNOM</sub>   | 1.0                                                                                                                                                                        | 1.4       | 2.0                  | V                    |

| V <sub>THSSQB</sub>     |                                                                                                                                                                            |           |                      | V                    |

|                         | 1.0                                                                                                                                                                        | 1.4       | 2.0                  |                      |

|                         |                                                                                                                                                                            |           |                      |                      |

| V <sub>DHI</sub>        | 15                                                                                                                                                                         | 17        | 19.0                 | V                    |

| $V_{DLO}$               | 5.7                                                                                                                                                                        | 6.5       | 7.2                  | V                    |

| ND)                     |                                                                                                                                                                            |           |                      | •                    |

| V <sub>FDHI</sub>       | 15                                                                                                                                                                         | 17        | 19.0                 | V                    |

| V <sub>FLO</sub>        | 5.7                                                                                                                                                                        | 6.5       | 7.2                  | V                    |

| OLTAGE THRE             | SHOLDS) (\$                                                                                                                                                                | C6 COMMAN | ND)                  | 1                    |

| V <sub>VDIAG_X</sub> V4 | 29.8                                                                                                                                                                       | 32.8      | 38.5                 | V                    |

| V <sub>VDIAG_X</sub> V3 | 25.5                                                                                                                                                                       | 27.7      | 30.5                 | V                    |

| V <sub>VDIAG_X</sub> V2 | 20.5                                                                                                                                                                       | 22.6      | 26.5                 | V                    |

| V <sub>VDIAG_X</sub> V1 | 16                                                                                                                                                                         | 18.4      | 21.0                 | V                    |

|                         |                                                                                                                                                                            | 1         | •                    | 1                    |

| R <sub>RTN1</sub>       | 0.15                                                                                                                                                                       | _         | 0.6                  | Ω                    |

| R <sub>RTN2</sub>       | 0.15                                                                                                                                                                       | -         | 0.6                  | Ω                    |

|                         |                                                                                                                                                                            | 1         | •                    | 1                    |

| R <sub>HS</sub>         | 4.1                                                                                                                                                                        | 5.1       | 6.1                  | kΩ                   |

| R <sub>HSO</sub>        |                                                                                                                                                                            |           |                      | kΩ                   |

|                         | VTHSG_SO  QB_LO_XX (\$C2  ITHSQB CON  3, \$E8 COMMAN  VTHSQBNOM  VTHSQBNOM  VDHI  VDLO  VDHI  VDLO  VOLTAGE THRE  VVDIAG_X V4  VVDIAG_X V3  VVDIAG_X V1  RRTN1  RRTN2  RHS | VTHSG_SO  | V <sub>THSG_SO</sub> | V <sub>THSG_SO</sub> |

- 15 XX = 1A, 1B, 2A, or 2B

- 16 XX and YY = 1A, 1B, 2A, or 2B

Characteristics noted under conditions 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V; 7.0 V  $\leq$  V<sub>VFIRE\_XX</sub>  $\leq$  35 V; V<sub>VDIAG\_X</sub> = V<sub>VFIRE\_XX</sub>; FEN 1 = FEN 2 = V<sub>DD</sub>; R<sub>R\_LIMIT\_X</sub> = 10 k $\Omega$  ±1%, R<sub>R\_DIAG</sub> = 10 k $\Omega$  ±1%, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  +85 °C, GND = 0, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                        | Symbol            | Min | Тур | Max | Unit |

|-----------------------------------------------------------------------------------------------------------------------|-------------------|-----|-----|-----|------|

| R_HS Short Threshold                                                                                                  | R <sub>HSS</sub>  | 2.8 | _   | 4.1 | kΩ   |

| VFIRE_XA & VFIRE_XB Current during High Side Safing Test at Open Threshold VFIRE 1A & VFIRE 1B or VFIRE 2A & VFIRE 2B | I <sub>1HSO</sub> |     |     |     | μА   |

| VFIRE_IA & VFIRE_IB 01 VFIRE_ZA & VFIRE_ZB                                                                            |                   | 270 | 360 | 410 |      |

| VFIRE_XA & VFIRE_XB Current during High Side Safing Test at Short Threshold                                           | I <sub>1HSS</sub> |     |     |     | μА   |

| VFIRE_1A & VFIRE_1B or VFIRE_2A & VFIRE_2B                                                                            |                   | 287 | 385 | 439 |      |

# HIGH SIDE SAFING SENSOR DIAGNOSTICS WITH 1 SAFING SENSOR IN FIRING PATH CONNECTED TO VFIRE\_1A AND VFIRE\_2A PINS (GUARANTEED BY DESIGN) (\$C0 COMMAND)

| Total VFIRE_XX Current during High Side Safing Test at Open Threshold VFIRE 1A, VFIRE 1B, VFIRE 2A & VFIRE 2B pins | I <sub>2HSO</sub> | F74  | 705  | 0.40 | μА |

|--------------------------------------------------------------------------------------------------------------------|-------------------|------|------|------|----|

| VI INC_17, VI INC_15, VI INC_27 & VI INC_25 pino                                                                   |                   | 574  | 705  | 848  |    |

| Total VFIRE_XX Current during High Side Safing Test at Short Threshold                                             | I <sub>2HSS</sub> |      |      |      | μА |

| VFIRE_1A, VFIRE_1B, VFIRE_2A & VFIRE_2B pins                                                                       |                   | 605  | 748  | 892  |    |

| R_HS Valid Resistor Range                                                                                          | R <sub>2HS</sub>  |      |      |      | kΩ |

| $15 \text{ V} \leq \text{V}_{\text{VDIAG}_{X}} \leq 35 \text{ V}$                                                  |                   | 2.10 | _    | 2.93 |    |

| R_HS Open Threshold                                                                                                | R <sub>2HSO</sub> |      |      |      | kΩ |

| $15 \text{ V} \leq \text{V}_{\text{VDIAG}_{X}} \leq 35 \text{ V}$                                                  |                   | 2.93 | 3.35 | 4.43 |    |

| R_HS Short Threshold                                                                                               | R <sub>2HSS</sub> |      |      |      | kΩ |

| $15 \text{ V} \leq \text{V}_{\text{VDIAG}_{X}} \leq 35 \text{ V}$                                                  |                   | 1.14 | 1.61 | 2.10 |    |

#### **R\_LIMIT RESISTOR DIAGNOSTICS (\$C8 COMMAND)**

| R_LIMIT Valid Resistor Range                                 | R <sub>RL</sub>  | 4.32 | -   | 45.3 | kΩ |

|--------------------------------------------------------------|------------------|------|-----|------|----|

| R_LIMIT Open Threshold ("Out of Range Threshold")            | R <sub>RLO</sub> | 60   | 76  | 105  | kΩ |

| R_LIMIT Short-to-Ground Threshold ("Out of Range Threshold") | R <sub>RLS</sub> | 2.82 | 3.5 | 4.31 | kΩ |

| Maximum External Capacitance to Ground                       | C <sub>RL</sub>  | _    | _   | 20   | pF |

### R\_DIAG RESISTOR DIAGNOSTICS (\$C8 COMMAND) (17)

| R_DIAG Valid Resistor Range                                 | R <sub>RD</sub>  | 8.0 | 1   | 13  | kΩ |

|-------------------------------------------------------------|------------------|-----|-----|-----|----|

| R_DIAG Open Threshold ("Out of Range Threshold")            | R <sub>RDO</sub> | 13  | 23  | 60  | kΩ |

| R_DIAG Short-to-Ground Threshold ("Out of Range Threshold") | R <sub>RDS</sub> | 3.0 | 5.4 | 8.0 | kΩ |

| Maximum External Capacitance to Ground                      | C <sub>RD</sub>  | -   | ı   | 20  | pF |

#### Notes

By changing the R\_DIAG resistor value, the resistance thresholds can be varied by a linear relationship. The R\_DIAG resistance could be changed by ±10% to shift the thresholds by ±10%. Design goal for resistance threshold change is ±15%. R\_DIAG threshold limit may have to be changed to accommodate ±15% change. Example: Shifting the R\_DIAG resistance value ±10%, the resistance threshold will change by ±10%. Refer to Table 4.

Characteristics noted under conditions 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V; 7.0 V  $\leq$  V<sub>VFIRE\_XX</sub>  $\leq$  35 V; V<sub>VDIAG\_X</sub> = V<sub>VFIRE\_XX</sub>; FEN 1 = FEN 2 = V<sub>DD</sub>; R<sub>R\_LIMIT\_X</sub> = 10 k $\Omega$  ±1%, R<sub>R\_DIAG</sub> = 10 k $\Omega$  ±1%, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  +85 °C, GND = 0, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                            | Symbol             | Min  | Тур | Max  | Unit              |

|-----------------------------------------------------------|--------------------|------|-----|------|-------------------|

| SERIAL INTERFACE                                          |                    |      | •   | •    |                   |

| Output Logic Low Level (D0) I <sub>SINK</sub> = -800 μA   | V <sub>OLOW</sub>  | 0.0  | _   | 0.2  | x V <sub>DD</sub> |

| Output Logic High Level (D0) I <sub>SOURCE</sub> = 800 μA | V <sub>OHIGH</sub> | 0.7  | _   | 1.0  | x V <sub>DD</sub> |

| Input Logic Threshold (D1, CS, CLK)                       | V <sub>LTHR</sub>  | 0.35 | _   | 0.65 | x V <sub>DD</sub> |

| D1 Pull-down Current                                      | I <sub>D1</sub>    | -6.0 | -10 | -15  | μA                |

| CLK Pull-down Current                                     | I <sub>CLK</sub>   | -6.0 | -10 | -15  | μA                |

| CS Pull-up Current                                        | I <sub>CSBAR</sub> | 10   | 20  | 30   | μA                |

| HI-Z Leakage (D0)                                         | I <sub>HI-Z</sub>  | -    | _   | ±10  | μA                |

### Table 4. Resistance Range vs. R\_DIAG

| R_DIAG            | I <sub>DIAG</sub><br>(NOM) | R <sub>TH1</sub><br>Min/Max | R <sub>TH2</sub><br>Min/Max | R <sub>TH3</sub><br>Min/Max | R <sub>TH4</sub><br>Min/Max | R <sub>TH5</sub><br>Min/Max | R <sub>TH6</sub><br>Min/Max | R <sub>TH7</sub><br>Min/Max | R <sub>TH8</sub><br>Min/Max |

|-------------------|----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| 8.0 kΩ<br>(-20%)  | 41                         | 0.9 / 1.3                   | 1.2 / 1.7                   | 1.6 / 2.1                   | 2.0 / 2.6                   | 2.6 / 3.6                   | 3.6 / 4.8                   | 4.5 / 5.7                   | 5.3 / 6.8                   |

| 9.0 kΩ<br>(-10%)  | 38                         | 1.0 / 1.4                   | 1.4 / 1.9                   | 1.9 / 2.3                   | 2.3 / 2.9                   | 2.0 / 4.0                   | 4.1 / 5.4                   | 5.1 / 6.4                   | 6.0 / 7.7                   |

| 10.0 kΩ           | 35                         | 1.2 / 1.6                   | 1.6 / 2.1                   | 2.1 / 2.6                   | 2.6 / 3.2                   | 3.3 / 4.4                   | 4.6 / 6.0                   | 5.7 / 7.1                   | 6.7 / 8.5                   |

| 11.0 kΩ<br>(+10%) | 32                         | 1.3 / 1.8                   | 1.8 / 2.3                   | 2.3 / 2.9                   | 2.9 / 3.6                   | 3.6 / 4.9                   | 5.0 / 6.6                   | 6.2 / 7.8                   | 7.4 / 9.4                   |

| 12.0 kΩ<br>(+20%) | 29                         | 1.4 / 1.9                   | 1.9 / 2.5                   | 2.5 / 3.1                   | 3.1 / 3.9                   | 3.9 / 5.3                   | 5.5 / 7.2                   | 6.8 / 8.6                   | 8.0 / 10.2                  |

| 13.0 kΩ<br>(+30%) | 26                         | 1.5 / 2.1                   | 2.1 / 2.7                   | 2.7 / 3.4                   | 3.4 / 4.2                   | 4.2 / 5.8                   | 6.0 / 7.8                   | 7.4 / 9.3                   | 8.7 / 11.1                  |

# **DYNAMIC ELECTRICAL CHARACTERISTICS**

### **Table 5. Dynamic Electrical Characteristics**

Characteristics noted under conditions 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V; 7.0 V  $\leq$  V<sub>VFIRE\_XX</sub>  $\leq$  35 V; V<sub>VDIAG\_X</sub> = V<sub>VFIRE\_XX</sub>; FEN 1 = FEN 2 = V<sub>DD</sub>; R<sub>R\_LIMIT\_X</sub> = 10 k $\Omega$  ±1%, R<sub>R\_DIAG</sub> = 10 k $\Omega$  ±1%, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  +85 °C, GND = 0, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A =</sub> 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                 | Symbol            | Min | Тур | Max | Unit |

|----------------------------------------------------------------|-------------------|-----|-----|-----|------|

| SERIAL INTERFACE                                               | ·                 |     |     | •   |      |

| CLK Cycle Time (1/FCLK) (18)                                   | t <sub>CYC</sub>  | 200 | _   | _   | ns   |

| CLK High Time (18)                                             | t <sub>HI</sub>   |     |     |     | ns   |

| $V_{CLK} > V_{DD} \times 70\%$                                 |                   | 73  | _   | _   |      |

| CLK Low Time (18)                                              | t <sub>LO</sub>   |     |     |     | ns   |

| V <sub>CLK</sub> < V <sub>DD</sub> x 20%                       |                   | 73  | _   | _   |      |

| Clock Rise Time (18)                                           | t <sub>RISE</sub> |     |     |     | ns   |

| $V_{CLK}$ = 20% $V_{DD}$ to 70% $V_{DD,}$ $C_{LOAD}$ = 100 pF  |                   | _   | _   | 20  |      |

| Clock Fall Time (18)                                           | t <sub>FALL</sub> |     |     |     | ns   |

| $V_{CLK}$ = 70% $V_{DD}$ to 20% $V_{DD}$ , $C_{LOAD}$ = 100 pF |                   | _   | _   | 20  |      |

| Data Out Rise Time (19)                                        | t <sub>R</sub>    |     |     |     | ns   |

| $V_{DO} = 20\% V_{DD}$ to 70% $V_{DD}$ , $C_{LOAD} = 100 pF$   |                   | _   | _   | 20  |      |

| Data Out Fall Time (19)                                        | t <sub>F</sub>    |     |     |     | ns   |

| $V_{DO} = 70\% V_{DD}$ to 20% $V_{DD,} C_{LOAD} = 100 pF$      |                   | _   | _   | 20  |      |

| Chip Select Setup Time (19)                                    | t <sub>LEAD</sub> |     |     |     | ns   |

| CSB ↓ Before CLK ↑                                             |                   | 73  | _   | _   |      |

| Chip Select Hold Time (19)                                     | t <sub>LAG</sub>  |     |     |     | ns   |

| CLK ↓ Before CSB ↑                                             |                   | 73  | _   | _   |      |

| Data In Setup Time (19)                                        | t <sub>SU</sub>   |     |     |     | ns   |

| D1 Valid Before CLK ↑                                          |                   | 30  | _   | _   |      |

| Data In Hold Time (19)                                         | t <sub>H</sub>    |     |     |     | ns   |

| D1 Hold Time After CLK ↑                                       |                   | 30  | _   | _   |      |

| Data Out Access Time (19)                                      | t <sub>A</sub>    |     |     |     | ns   |

| CSB ↓ to D0 Valid                                              |                   | _   | _   | 73  |      |

| Data Out Disable Time (19)                                     | t <sub>DIS</sub>  |     |     |     | ns   |

| CSB ↑ to D0 HI-Z                                               |                   | _   | _   | 73  |      |

| Data Out Valid Time (19)                                       | t <sub>V</sub>    |     |     |     | ns   |

| CLK ↑ to D0 Valid, C <sub>LOAD</sub> = 100 pF                  |                   | _   | _   | 75  |      |

| Data Out Hold Time (19)                                        | t <sub>HO</sub>   |     |     |     | ns   |

| D0 held After CLK ↑                                            |                   | 0.0 | _   | _   |      |

| Diagnostic Delay Time (Between Two Successive Commands)        | t <sub>DIAG</sub> | 2.5 | _   | -   | μS   |

- 18 Determined by Design

- 19 Guaranteed by Characterization

Characteristics noted under conditions 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V; 7.0 V  $\leq$  V<sub>VFIRE\_XX</sub>  $\leq$  35 V; V<sub>VDIAG\_X</sub> = V<sub>VFIRE\_XX</sub>; FEN 1 = FEN 2 = V<sub>DD</sub>; R<sub>R\_LIMIT\_X</sub> = 10 k $\Omega$  ±1%, R<sub>R\_DIAG</sub> = 10 k $\Omega$  ±1%, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  +85 °C, GND = 0, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                                                                                                                                                            | Symbol                  | Min   | Тур | Max   | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------|-----|-------|------|

| FET DRIVERS                                                                                                                                                                                                                                                                                               |                         |       |     |       |      |

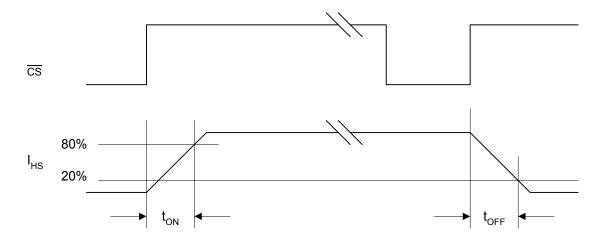

| Turn-On Delay Time<br>CS ↑ to 80% I <sub>HS</sub>                                                                                                                                                                                                                                                         | t <sub>ON</sub>         | _     | _   | 72    | μs   |

| Turn-Off Delay Time CS ↑ to 20% I <sub>HS</sub>                                                                                                                                                                                                                                                           | t <sub>OFF</sub>        | -     | _   | 10    | μs   |

| Diagnostic Timing/Resolution $5.0~V \leq V_{VDIAG\_X} \leq 35~V,~I_{HS} \geq I_{MEAS},~0~s \leq t_{MEASURE\_TIME} \leq 6.375~ms,\\ C_{SQUIB\_HI} = 0.12~\mu F,~C_{SQUIB\_LO} = 0.12~\mu F$                                                                                                                | <sup>t</sup> RESOLUTION | 21.25 | 25  | 28.75 | μs   |

| DIAGNOSTIC DELAY TIME                                                                                                                                                                                                                                                                                     | 1                       |       | l   | •     |      |

| Squib Resistance Diagnostic Delay Time $^{(20)}$<br>From CSB $\uparrow$ Until Transistor Test Results Are Valid, $C_{SQUIB\_HI}$ = 0.12 $\mu$ F, $C_{SQUIB\_LO}$ = 0.12 $\mu$ F                                                                                                                           | <sup>†</sup> DIAG1      | _     | _   | 300   | μЅ   |

| Squib Open/Short Diagnostic Delay Time <sup>(20)</sup> From CSB ↑ Until Squib Open/Short Diagnostic Results Are Valid, C <sub>SQUIB_HI</sub> = 0.12 μF, C <sub>SQUIB_LO</sub> = 0.12 μF                                                                                                                   | <sup>†</sup> DIAG2      | _     | _   | 3000  | μS   |

| VDIAG Supply Diagnostic Delay Time From CSB ↑ until VDIAG Diagnostic Results Are Valid (20)                                                                                                                                                                                                               | t <sub>DIAG4</sub>      | _     | _   | 100   | μS   |

| $V_{FIRE}$ Supply Diagnostic Delay Time $^{(20)}$<br>15 V $\leq$ V <sub>VDIAG_X</sub> $\leq$ 35 V, From CSB $\uparrow$ Until High Side Safing Sensor Diagnostic Results Are Valid, C <sub>VDIAG</sub> $<$ 0.015 $\mu$ F                                                                                   | <sup>t</sup> DIAG6      | _     | _   | 500   | μS   |

| High Side Safing Sensor Diagnostic Delay Time $^{(20)}$<br>15 V $\leq$ V <sub>VDIAG_X</sub> $\leq$ 35 V, From CSB $\uparrow$ Until High-Side Safing Sensor Diagnostic Results Are Valid, C <sub>VDIAG</sub> $<$ 0.015 $\mu$ F                                                                             | <sup>†</sup> DIAG7      | _     | _   | 500   | μS   |

| FET Drivers High and Low Side Driver Transistor Diagnostic Delay Time $^{(20)}$ 15 V $\leq$ V <sub>VDIAG_X</sub> $\leq$ 35 V, From CSB $\uparrow$ Until Transistor Test Results Are Valid, C <sub>SQUIB_HI</sub> = 0.12 $\mu$ F, C <sub>SQUIB_LO</sub> = 0.12 $\mu$ F, C <sub>VDIAG</sub> < 0.015 $\mu$ F | <sup>†</sup> DIAG9      | _     | _   | 1000  | μS   |

| VFIRE_RTN Diagnostic Delay Time <sup>(20)</sup> From CSB ↑ Until VFIRE_RTN Diagnostic Results Are Valid                                                                                                                                                                                                   | <sup>t</sup> DIAG10     | _     | -   | 300   | μ\$  |

| Squib Continuity Diagnostic Delay Time (20)  From CSB ↑ Until V <sub>THSQBCON</sub> Diagnostic Results Are Valid                                                                                                                                                                                          | t <sub>DIAG11</sub>     | -     | _   | 3000  | μS   |

| Squib Short Between Firing Loops Diagnostic Delay Time From CSB ↑ Until V <sub>THSSQB</sub> Diagnostic Results Are Valid <sup>(20)</sup>                                                                                                                                                                  | t <sub>DIAG12</sub>     | -     | _   | 3000  | μS   |

| FEN INPUT PIN                                                                                                                                                                                                                                                                                             |                         |       | •   | •     | •    |

| Minimum Pulse Width                                                                                                                                                                                                                                                                                       | FEN <sub>FILTER</sub>   | 12    | 14  | 16    | μS   |

| Notes                                                                                                                                                                                                                                                                                                     | ı                       |       | 1   | 1     | 1    |

Notes

20 Guaranteed by Characterization

# **TIMING DIAGRAMS**

Figure 4. Driver Timing Diagram

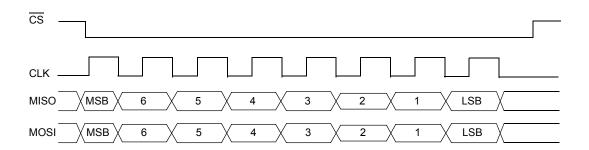

Figure 5. Freescale SPI

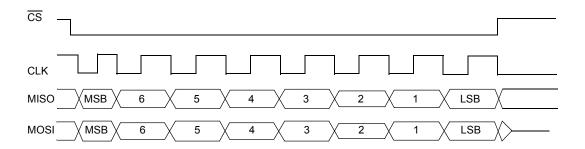

Figure 6. Alternative SCI Mode

### **FUNCTIONAL DESCRIPTION**

#### INTRODUCTION

The Four Channel Squib Driver IC is a complete squib diagnostic and deployment interface for use in automotive air bag modules. Extensive diagnostics and system control features are incorporated to provide fail-safe operation.

The device contains a serial peripheral interface (SPI) compatible 8-bit interface for microprocessor control. This interface allows the microprocessor to set up and read back the results of all internal diagnostic functions. Squib resistance level, along with possible shorts-to-battery or ground, open ground connections, or shorts between squib firing loops, are included in the diagnostic set. Additionally, the squib supply voltage levels can be checked and the low

side fire return can be checked for an open condition (open ground connection). The SPI interface, along with the additional FEN pin, is used to arm and fire a selected squib.

The device has the capability to be used in a standard fourchannel squib driver IC or in a cross-coupled state with the high and low side squib drivers located on separate squib driver ICs.

Both the high side and low side output drivers are protected against temporary shorts to battery or ground. The current limit threshold is set by an external resistor.

#### **FUNCTIONAL PIN DESCRIPTION**

#### INTRODUCTION

In this section references are made to XX; e.g., in SENSE\_XX, SQB\_LO\_XX, and SQB\_LO\_XX\_CONT. In these and similar instances, XX denotes 1A, 1B, 2A, and 2B.

#### **SERIAL CLOCK (SCLK)**

Serial clock input for SPI interface. Data on the D1 pin is clocked into the device on the rising edge. Data is clocked out of the device via the D0 pin on the falling edge. Default state is low with no connection.

# CHIP SELECT (CS)

Chip select for SPI interface. Active low. On rising edge, data shifted into the shift register is internally latched. On falling edge, diagnostic results are latched into shift register. Default state is high with no connection.

# **MASTEROUT/SLAVE IN (MOSI)**

Serial data input to 33797 SPI interface. Default state is low with no connection.

#### **MASTER IN/SLAVE OUT (MISO)**

Serial data output from 33797 SPI interface.

#### FET DRIVER 1A AND 1B (FEN 1)

Active high input signal to enable operation of squibs 1A and 1B FET drivers. All diagnostic functions are available while pin is low. Default state is low with no connection.

### FET DRIVER 2A AND 2B (FEN\_2)

Active high input signal to enable operation of squibs 2A and 2B FET drivers. All diagnostic functions are available while pin is low. Default state is low with no connection.

#### **DEVICE GROUND (GND)**

Device ground pin for internal logic and diagnostic circuitry.

#### **DEVICE POWER (VDD)**

Device power pin for internal logic and diagnostic circuitry.

## **RESET (RST)**

Reset Bar. Active low. With low input signal the internal functions of the squib driver IC are disabled and all data in the serial interface shift registers is cleared. Default state is low with no connection.

### LIMIT RESISTOR - DIAGNOSTIC (R DIAG)

External resistor to ground is used to set the diagnostic current for squib resistance.

#### LIMIT RESISTOR 1A AND 1B (R LIMIT 1)

External resistor to ground is used to set current limit for squibs 1A and 1B FET drivers.

### LIMIT RESISTOR 2A AND 2B (R LIMIT 2)

External resistor to ground is used to set current limit for squibs 2A and 2B FET drivers.

### SQUIB DIAGNOSTIC 1A AND 1B (VDIAG 1)

Diagnostic pins for the high side safing sensors for squibs 1A and 1B, as well as the VFIRE supply voltage.

#### SQUIB DIAGNOSTIC 2A AND 2B (VDIAG\_2)

Diagnostic pins for the high side safing sensors for squibs 2A and 2B, as well as the VFIRE supply voltage.

### SQUIB SENSE XX (SENSE XX)

The Sense pins are used *exclusively* for diagnostics related to the squib, driver FETs, or harness. Commands using the Sense pins include:

- C1, C2, C3, C9

- D<3:0>

- E<3:0>

- E9

- 82/1x

- 83/2x

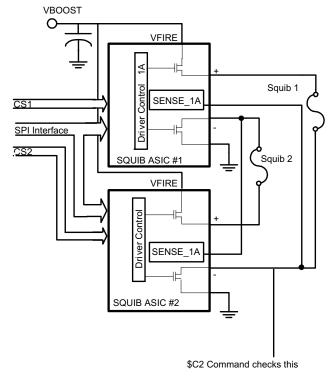

Independent of the system configuration, normal or cross coupled, the Sense pin, xx and SquibHi, xx of a single IC are always connected to the same squib with the SquibHi pin connected to the high pin of the squib and the Sense pin connected to the low pin of the squib. A cross coupled configuration is achieved by only cross coupling the squib low pins. See Figure 7 and Figure 8.

#### STANDARD APPLICATIONS

In the standard mode, the \$C2 (SQUIB\_LO\_XX\_CONT) command will be used to check continuity of the low side driver from the SQB\_LO\_XX pin to the high side driver FET (see Figure 6).

### **CROSS-COUPLED APPLICATIONS**

Used during cross-coupling applications involving two four channel squib driver ICs (squib driver IC #1 and squib driver IC #2). SENSE\_XX pins from squib driver IC #1 are connected to their respective squib minus pins (Squib Low/SQB\_LO\_XX) from squib driver IC #2 (Figure 8). SENSE\_XX pins are used to feed diagnostic signals back to squib driver IC #1 for determining squib resistance, short-to-battery/ground, and squib loop-to-loop short conditions. During a fire event, the fire current passes from squib driver IC #1 high side driver though the squib to squib driver IC #2 low side driver (Figure 8). In the cross-coupled mode, the squib driver IC #2 \$C2 (SQUIB\_LO\_XX\_CONT) command will be used to check continuity of the low side driver from the SQB\_LO\_XX pin to the low side driver FET.

#### **DESIGN NOTES**

Diagnostics always have the form of a forcing function and a measurement or sense function. In a cross couple

configuration, most diagnostics are unaffected and are single commands except for \$C2 Low Side FET Continuity and \$E<3:0> Harness Shorts, and 83/2x Low Side FET test. This command must be sent to each IC to be executed. For these three diagnostics, two commands are required because the forcing function and sensing function are on separate ICs.

Harness Shorts Diagnostics: Force using \$E<3:0> on IC#1, Sense \$E8 on IC2

Low Side FET Continuity: Force using \$C1 on IC#1, Sense using \$C2 on IC#2

Low Side FET Test: Force using \$C1 on IC#1, Sense using \$C2 on IC#2

An active 600  $\mu$ A current sink is located in the SENSE\_XX pin. The sink current is used to pull the charge off of the external EMC/filter caps after a diagnostic measurement has been made.

### SQUIB HI XX (SQB\_HI\_XX)

Squib high pins for squibs 1A, 1B, 2A, and 2B. These pins are connected to the sources of the high side FET drivers, as well as the diagnostic circuitry.

#### SQUIB LOW XX (SQB LO XX)

Squib low pins for squibs 1A, 1B, 2A, and 2B. These pins are connected to the drains of the low side FET drivers, as well as the diagnostic circuitry.

#### SQUIB FIRING SUPPLY XX (VFIRE XX)

Firing supply pins for squibs 1A, 1B, 2A, and 2B. These pins are connected to the drains of the high side FET drivers. Feedback for high side safing for squibs 1A and 1B will be referenced from VFIRE\_1A and squibs 2A and 2B from VFIRE\_2A. For high side safing, VFIRE\_1B should be connected to VFIRE\_1A pin and VFIRE\_2B to VFIRE\_2A pin.

### SQUIB FIRE POWER GROUND (VFIRE\_RTN)

Return for squibs 1A, 1B, 2A AND 2B. The pins are tied to the source pins of both low side FET drivers, as well as the diagnostic circuitry. The RTN pins are tied internally.

Figure 7. Standard Squib Firing

Figure 8. Cross-coupled Squib Firing

### **FUNCTIONAL DEVICE OPERATION**

#### **OPERATIONAL MODES**

#### INTRODUCTION

In this section references are made to XX; e.g., in SQB\_HI\_XX, SQB\_LO\_XX, and SENSE\_XX pins. SQB\_HI\_XX refers to SQB\_HI\_1A, SQB\_HI\_1B, SQB\_HI\_2A or SQB\_HI\_2B, SQB\_LO\_1A, etc.

#### **SERIAL INTERFACE**

An 8-bit shift register is provided for communication through the serial port to a microprocessor. The four wire SPI interface is used to read from, and write to, the shift register. Data written to the shift register will control the firing of the FET switches or select a diagnostic mode. Data is sequentially shifted into and out of the shift register, most significant bit first.

Data read from the shift register will contain the results of the diagnostic mode selected in the previous 8-bit write. If a NOP command is written, all diagnostic modes are cleared and the data in the shift registers will be read out. With any undefined commands, all diagnostic modes are cleared and the data in the shift registers will be read out. All functions are set when  $\overline{\text{CS}}$  goes high. All diagnostic commands are cleared on the next valid SPI command.

#### SPI INTERFACE INTEGRITY CHECK

The \$96 command with corresponding \$69 return byte during the next 8-bit write is used as an echo function to diagnose the SPI integrity (refer to Table 8).

The Diagnostic Data Out bits not containing data are set to zero.

Only 8-bit words will be accepted. Any words that are  $\leq 7$  bits or  $\geq 9$  bits will be ignored or cleared.

The second byte for command programming will be treated as a NOP if any FET is firing. The programming commands must be sequential or they will be treated as a NOP.

The four channel squib driver IC is a slave peripheral device designed to interface to a Freescale SPI or other serial peripheral interface. Data is read on the rising edge of CLK, and data is transferred out on the rising edge of CLK. On the falling edge of  $\overline{\text{CS}}$ , the IC configures itself for one of two SPI modes. If CLK is low, the IC will configure itself to be in Freescale SPI mode (see Figure 5). If CLK is high, the IC will configure itself to be in an alternative SCI mode (see Figure 5). In both cases, data is still read off the rising edge and transferred off the falling edge of the CLK. When the IC is deselected  $\overline{(\text{CS})}$  goes high), then D0 is a high-impedance output.

Response bit 7 of command \$C8 (refer to Table 7, page 23) is hard-wired to "1" or "0" to identify the squib IC as a four or two channel squib driver IC. When a \$C8 command is issued for the four channel squib driver IC, the response bit

7 is set to a "0". When a \$C8 command is issued for the two channel squib driver IC, the response bit 7 is set to a "1".

#### STANDARD SQUIB IC FUNCTION

The standard squib IC application utilizes the high and low side squib drivers from the same squib driver ICs (see Figure 6, Standard Squib Firing).

The SENSE\_XX (1A, 1B, 2A, 2B) pin is connected to SQB\_LO\_XX (1A, 1B, 2A, 2B). Squib diagnostics are conducted using this pin. In the standard mode, the \$C2 (SQUIB\_LO\_XX\_CONT) command will be used to check continuity of the low side driver from the SQB\_LO\_XX pin (1A, 1B, 2A, 2B) to the low side driver FET (Figure 6).

The low side driver continuity is checked during the continuity test. The driver continuity information will be cleared after the information is transmitted on the next valid SPI command.

# EXAMPLE—STANDARD SQUIB COMMAND SPI SEQUENCE FROM MICROCONTROLLER

- TX: Request squib short-to-battery/GND diagnostic measurement (\$C1).

- RX: Previous executed command information.

- TX: Request squib 1A resistance measurement (\$D0-\$D3).

- RX: Receive results from short-to-battery/GND diagnostics.

- TX: Request squib 1B resistance measurement (\$D0-\$D3).

- RX: Receive measured squib 1A resistance information.

- TX: Request squib 2A resistance measurement (\$D0-\$D3).

- RX: Receive measured squib 1B resistance information.

- TX: Request squib 2B resistance measurement (\$D0-\$D3).

- RX: Receive measured squib 2A resistance information

- TX: Request continuity command (\$C2).