# SG6518 LCD Power Supply Supervisor

#### **Features**

- Two Adjustable Voltage Sense Input Pins: VSV1 and VSV2

- Over-voltage Protection (OVP) for 5V, 12V, and two outputs: V1, V2

- Over-current Protection (OCP) for 5V, 12V, and two outputs: V1, V2

- Adjustable Voltage Control Sense Input of V1 and V2 (ADJ-V1, ADJ-V2)

- Open-drain Output for FPO Pin

- 13ms PSON Control Delay

- No Lockup During the Fast AC Power-on/off

- Wide Supply Voltage Range: 4V to 15V

- Programmable Over-temperature Protection (OTP)

## **Applications**

LCD Power Supply

#### **Description**

SG6518 provides the over-voltage protection (OVP) for 5V, 12V, and outputs V1 and V2 as well as over-current protection (OVP) for 5V, 12V, and outputs V1 and V2. When the voltage of OTP pin decreases to 1.2V, the over-temperature protection (OTP) function is enabled. FPO is set to HIGH to turn off the PWM control IC. The voltage difference across the external current shunt is used for OCP functions. An external resistor can be used to adjust protection threshold.

The power supply is turned on after a 13ms delay time when the PSON signal is set from LOW to HIGH. To turn off the power supply, PSON signal is set from HIGH to LOW with the delay time 13ms.

### **Ordering Information**

| Part Number | Operating Temperature Range | Package | Packing Method |

|-------------|-----------------------------|---------|----------------|

| SG6518DZ    | -40°C to +85°C              | 16-DIP  | Rail           |

| SG6518SZ    | -40°C to +85°C              | 16-SOP  | Reel & Tape    |

All packages are lead free per JEDEC: J-STD-020B standard.

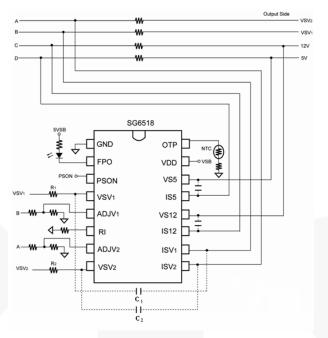

### **Application Diagram**

Figure 1. Typical Application

- 1.  $R_1 = 200\Omega$  and  $R_2 = 200\Omega$  are suggested. 2.  $C_1$  and  $C_2$  are suggested to be 100nF to 2.2uF.

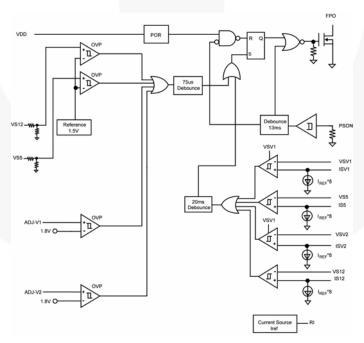

### **Internal Block Diagram**

Figure 2. Function Block Diagram

#### Note:

3. The VSV1 pin is the power pin for the two OCP comparators.

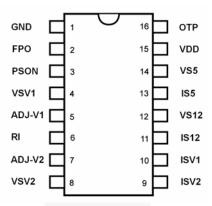

## **Pin Configuration**

Figure 3. Pin Configuration

#### **Pin Definitions**

| Pin# | Name   | Description                                                                                                                                                                                                                                             |  |  |  |  |

|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1    | GND    | Ground.                                                                                                                                                                                                                                                 |  |  |  |  |

| 2    | FPO    | Fault protection output. Output signal to control the primary PWM IC through an opto-coupler. When FPO is LOW, the PWM IC is enabled.                                                                                                                   |  |  |  |  |

| 3    | PSON   | Remote on/off logic input from CPU or main-board. The power supply is turned on/off after 13ms delay.                                                                                                                                                   |  |  |  |  |

| 4    | VSV1   | V1 voltage sense input. (4)                                                                                                                                                                                                                             |  |  |  |  |

| 5    | ADJ-V1 | V1 over-voltage control sense input.                                                                                                                                                                                                                    |  |  |  |  |

| 6    | RI     | Reference setting. One external resistor, $R_i$ , connected between the RI and GND pins determines a reference current, $I_{REF} = 1.5 V/R_i$ , for OCP programming.                                                                                    |  |  |  |  |

| 7    | ADJ-V2 | V2 over-voltage control sense input.                                                                                                                                                                                                                    |  |  |  |  |

| 8    | VSV2   | V2 voltage sense input.                                                                                                                                                                                                                                 |  |  |  |  |

| 9    | ISV2   | /2 over-current protection sense input. In typical applications, this pin is connected to the positive end of a current shunt through one resistor. When the voltage on ISV2 is higher than hat of VSV2 by 6mV, OCP is enabled.                         |  |  |  |  |

| 10   | ISV1   | VSV1 over-current protection sense input. In typical applications, this pin is connected to the positive end of a current shunt through one resistor. When the voltage on ISV1 is higher than that of VSV1 by 6mV, OCP is enabled.                      |  |  |  |  |

| 11   | IS12   | 12V over-current protection sense input. In typical applications, this pin is connected to the positive end of a current shunt through one resistor. When the voltage on IS12 is higher than that of VS12 by 6mV, OCP is enabled.                       |  |  |  |  |

| 12   | VS12   | 12V over-voltage control sense input.                                                                                                                                                                                                                   |  |  |  |  |

| 13   | IS5    | 5V over-current protection sense input. In typical applications, this pin is connected to the positive end of a current shunt through one resistor. When the voltage on IS5 is higher than tha of VS5 by 6mV, OCP is enabled.                           |  |  |  |  |

| 14   | VS5    | 5V over-voltage control sense input.                                                                                                                                                                                                                    |  |  |  |  |

| 15   | VDD    | Supply voltage, 4V ~ 15V. For general applications, it is connected to 5V-standby for supply voltage.                                                                                                                                                   |  |  |  |  |

| 16   | ОТР    | For over-temperature protection. An external NTC thermistor is connected from this pin to ground. The impedance of the NTC decreases at high temperatures. Once the voltage of the OTP pin drops below a fixed limit of 1.2V, FPO is open-drain output. |  |  |  |  |

#### Note:

4. The VSV1 pin is the power pin for the two OCP comparators; it must be higher than VSV2.

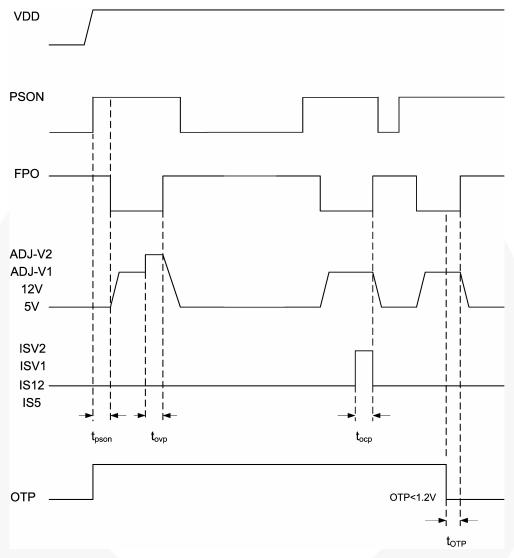

### **Timing Diagram**

Figure 4. PSON On/Off and 5V, 12V, V1, V2, OVP, and OCP Functions

#### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only. All voltage values, except differential voltages, are given with respect to GND pin. Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device.

| Symbol           |                     | Parameter                         | Min. | Max. | Unit |  |

|------------------|---------------------|-----------------------------------|------|------|------|--|

| $V_{DD}$         | DC Supply Voltage   |                                   | 16   | V    |      |  |

|                  |                     | ISV1, ISV2, VSV1, VSV2            | -0.3 | 30.0 | V    |  |

| Vı               | Input Voltage       | PSON, IS12,VS12                   | -0.3 | 15.0 |      |  |

|                  |                     | ADJ-V1, ADJ-V2, IS5, VS5, OTP, RI | -0.3 | 7.0  |      |  |

| V <sub>OUT</sub> | Output Voltage      | -0.3                              | 15.0 | V    |      |  |

| $P_D$            | Power Dissipation   |                                   | 400  | mW   |      |  |

| TJ               | Operating Free Jui  | -40                               | +125 | °C   |      |  |

| T <sub>STG</sub> | Storage Temperate   | -55                               | +150 | °C   |      |  |

| TL               | Lead Temperature    | (Wave Soldering, 10 Seconds)      |      | +260 | °C   |  |

| ESD              | Electrostatic Disch |                                   | 2.5  | kV   |      |  |

| ESD              | Electrostatic Disch |                                   | 200  | V    |      |  |

#### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol   | Parameter                           | Min. | Max. | Unit |

|----------|-------------------------------------|------|------|------|

| $V_{DD}$ | DC Supply Voltage                   | 4    | 15   | V    |

| $T_A$    | Operating Ambient Temperature Range | -40  | +85  | °C   |

#### **Electrical Characteristics**

Unless otherwise noted, operating specifications are  $V_{DD} = 5V,\, T_A \text{=+}25^{\circ}C$

| Symbol               | Parameter                                                                                  | Conditions                          | Min.  | Тур.  | Max.  | Units |

|----------------------|--------------------------------------------------------------------------------------------|-------------------------------------|-------|-------|-------|-------|

| VDD SECT             | <b>FION</b>                                                                                |                                     |       |       |       |       |

| $V_{DD}$             | DC Supply Voltage                                                                          |                                     | 4     |       | 15    | V     |

| I <sub>DD</sub>      | Supply Current                                                                             |                                     |       | 1.5   |       | mA    |

| t <sub>R</sub>       | Supply Voltage Rising Time                                                                 |                                     | 1     |       |       | ms    |

| V <sub>ST</sub>      | V <sub>DD</sub> Start Threshold Voltage                                                    |                                     |       |       | 4     | V     |

| Over-Volta           | age and Over-Current Protection (O                                                         | /P, OCP)                            |       |       |       |       |

| .,                   | Over-Voltage Protection VS5                                                                | 5.7                                 | 6.1   | 6.5   | .,    |       |

| $V_{OVP}$            | Over-Voltage Protection VS12                                                               |                                     | 13.2  | 13.8  | 14.4  | V     |

| I <sub>REF</sub>     | Ratio of Current Sense Sink Current to<br>Current Sense Setting Pin (RI) Source<br>Current | $R_{I} = 23K\Omega \sim 120K\Omega$ | 7.6   | 8.0   | 8.4   |       |

| V <sub>OFFSET</sub>  | OCP Comparator Input Offset Voltage                                                        |                                     | -7    |       | 7     | mV    |

| I <sub>LKG-FPO</sub> | Leakage Current (FPO)                                                                      | FPO = 5V                            |       |       | 5     | μA    |

| V <sub>OL-FPO</sub>  | Low Level Output Voltage (FPO)                                                             | Isink 10mA                          |       |       | 0.5   | V     |

| t <sub>OVP</sub>     | OVP Delay Time                                                                             |                                     | 33    | 75    | 110   | μs    |

| tocp                 | OCP Delay Time                                                                             |                                     | 12.5  | 20.0  | 27.5  | ms    |

| $V_{RI}$             | RI Pin Voltage                                                                             |                                     | 1.455 | 1.50  | 1.545 | V     |

| t <sub>ST-OCP</sub>  | Start-up OCP Protection Delay Time                                                         | FPO = LOW                           | 158   | 200   | 242   | ms    |

| ADJ Section          | on                                                                                         |                                     |       |       |       |       |

| V <sub>ADJNOR</sub>  | Normal Voltage of ADJ-V1 & ADJ-V2                                                          |                                     | 1.455 | 1.50  | 1.545 | V     |

| V <sub>ADJOVP</sub>  | Over-Voltage Protection of ADJ-V1 & ADJ-V2                                                 |                                     | 1.455 | 1.80  | 1.545 | V     |

| PSON Cor             | ntrol                                                                                      |                                     |       |       |       |       |

| RPSON                | Input Pull-low Resistor                                                                    |                                     | 50    | 1     | 100   | ΚΩ    |

| V <sub>IH</sub>      | High-level Input Voltage                                                                   |                                     | 2     |       |       | V     |

| V <sub>IL</sub>      | Low-level Input Voltage                                                                    |                                     | 7     |       | 1     | V     |

|                      | Timing DCON to On 10#                                                                      | PSON HIGH to FPO<br>LOW             | 6     | 13    | 20    | ms    |

| t <sub>PSON</sub>    | Timing PSON to On/Off                                                                      | PSON LOW to FPO<br>HIGH             | 6     | 13    | 20    | ms    |

| Over-Tem             | perature Protection (OTP)                                                                  |                                     |       |       |       |       |

| I <sub>OTP</sub>     | Ratio of OTP Source Current to Current<br>Sense Setting Pin (RI) Source Current            |                                     | 5.82  | 6.00  | 6.18  |       |

| $V_{OTP\text{-}OFF}$ | Threshold Voltage for OTP                                                                  |                                     | 1.164 | 1.200 | 1.236 | V     |

| t <sub>OTP</sub>     | Over-Temperature Debounce                                                                  |                                     | 225   | 325   | 425   | μs    |

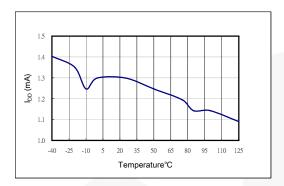

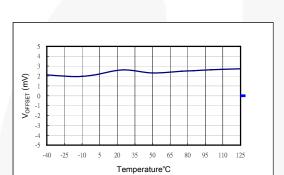

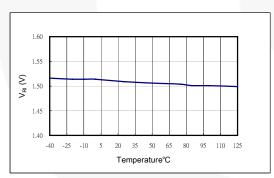

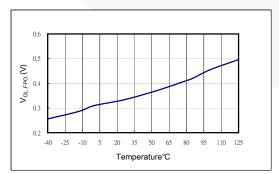

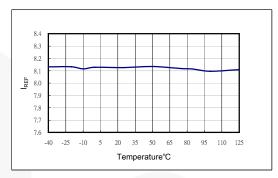

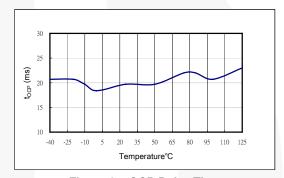

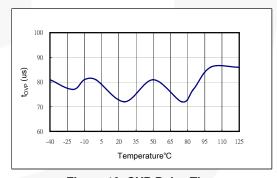

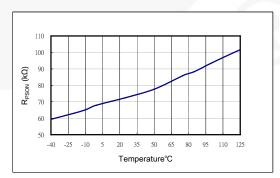

### **Typical Performance Characteristics**

These characteristic graphs are normalized at  $T_A = 25$ °C.

Figure 5. Supply Current

Figure 7. OCP Comparator Input Offset Voltage

Figure 9. RI Pin Voltage

Figure 11. Low Level Output Voltage

Figure 6. Ratio of Sense Sink Current Sense Setting

Pin (RI) Source Current

Figure 8. OCP Delay Time

Figure 10. OVP Delay Time

Figure 12. Input Pull-low Resistor

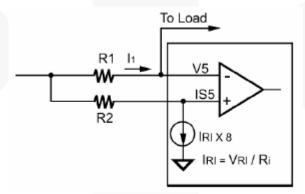

### **Applications Information (OCP)**

The SG6518 provides over-current protection for the 5V, 12V, and two outputs: V1, V2. When an OCP condition occurs at any of the voltage rails, FPO opens. The internal OCP comparators have a very small offset voltage ( $\pm 6$ mV). The sink currents of IS5, IS12, ISV1, and ISV2 are eight times the current at the RI pin. The current at the RI pin is  $V_{RI}/R_{I}$ . Here is an example demonstrating how to set the over-current protection.

If  $I_1 \cdot R1 > (I_{R1} \cdot 8) \cdot R2$ , OCP is active.

To select R2 Resistor:

If R1 = 5m $\Omega$ , R<sub>i</sub> = 51k, OCP Protection Level is 5A, then R2 = (I<sub>1</sub> • R1)/(I<sub>R1</sub> • 8)

=  $(5A \cdot 5m\Omega) / \{(1.5V / 51K) \cdot 8\}$

$= 106\Omega$

**Figure 13. Over-Current Protection**

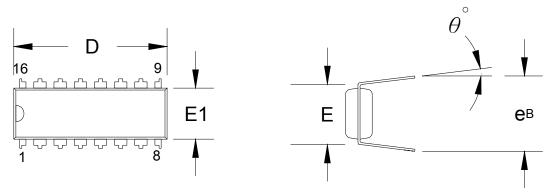

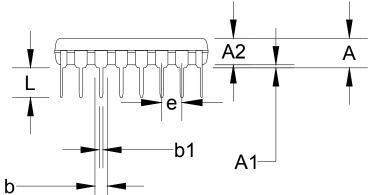

### **Physical Dimensions**

Figure 14. 16-Pin, Dual Inline Package (DIP)(D)

#### **Dimensions**

| Symbol         | Millimeter Inch |        |        |       |       |        |

|----------------|-----------------|--------|--------|-------|-------|--------|

|                | Min.            | Тур.   | Max.   | Min.  | Тур.  | Max.   |

| Α              |                 |        | 5.334  |       |       | 0.210  |

| A1             | 0.381           |        |        | 0.015 |       |        |

| A2             | 3.175           | 3.302  | 3.429  | 0.125 | 0.130 | 0.135  |

| b              |                 | 1.524  |        |       | 0.060 |        |

| b1             |                 | 0.457  |        |       | 0.018 |        |

| D              | 18.669          | 19.177 | 19.685 | 0.735 | 0.755 | 0.775  |

| Е              |                 | 7.620  |        |       | 0.300 |        |

| E1             | 6.121           | 6.299  | 6.477  | 0.241 | 0.248 | 0.255  |

| е              |                 | 2.540  |        |       | 0.100 | // 100 |

| L              | 2.921           | 3.302  | 3.810  | 0.115 | 0.130 | 0.150  |

| e <sub>B</sub> | 8.509           | 9.017  | 9.525  | 0.335 | 0.355 | 0.375  |

| $\theta$ °     | 0°              | 7°     | 15°    | 0°    | 7°    | 15°    |

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

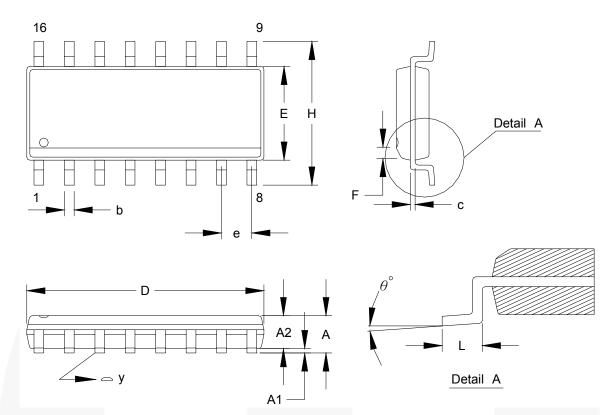

### Physical Dimensions (Continued)

Figure 15. 16-Pin, Small-Outline Package (SOP)(S)

#### **Dimensions**

| Compleal   | Millimeter | Millimeter |        |       | Inch      |       |  |  |

|------------|------------|------------|--------|-------|-----------|-------|--|--|

| Symbol     | Min.       | Тур.       | Max.   | Min.  | Тур.      | Max.  |  |  |

| Α          | 1.346      |            | 1.753  | 0.053 | /         | 0.069 |  |  |

| A1         | 0.101      |            | 0.254  | 0.004 |           | 0.010 |  |  |

| A2         | 1.244      |            | 1.499  | 0.049 | /         | 0.059 |  |  |

| b          |            | 0.406      |        |       | 0.016     |       |  |  |

| С          |            | 0.203      |        |       | 0.008     |       |  |  |

| D          | 9.804      |            | 10.008 | 0.386 |           | 0.394 |  |  |

| Е          | 3.810      |            | 3.988  | 0.150 |           | 0.157 |  |  |

| е          |            | 1.270      |        |       | 0.050     |       |  |  |

| Н          | 5.791      |            | 6.198  | 0.228 |           | 0.244 |  |  |

| L          | 0.406      |            | 1.270  | 0.016 |           | 0.050 |  |  |

| F          |            | 0.381X45°  |        |       | 0.015X45° |       |  |  |

| у          |            |            | 0.101  |       |           | 0.004 |  |  |

| $\theta$ ° | 0°         |            | 8°     | 0°    |           | 8°    |  |  |

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

#### **TRADEMARKS**

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

ACEx<sup>®</sup> Build it Now™ CorePLUS™ CROSSVOLT™ CTL TM

Current Transfer Logic™ EcoSPARK® EZSWITCH™ \*

**E**7

Fairchild<sup>®</sup> Fairchild Semiconductor®

FACT Quiet Series™ FACT® FAST® FastvCore™

**FPS™** FRFET® Global Power Resources Green FPS™

Green FPS™e-Series™ **GTO™** i-Lo™ IntelliMAX™ ISOPLANAR™ MICROCOUPLER™

MegaBuck™ MicroFET™ MicroPak™ MillerDrive™ Motion-SPM™ OPTOLOGIC® OPTOPLANAR® PDP-SPM™ Power220® Power247® POWEREDGE® Power-SPM™ PowerTrench®

Programmable Active Droop™ OFFI QSTM

QT Optoelectronics™ Quiet Series™ RapidConfigure™ SMART START™ SPM®

STEALTH\*\* SuperFET™ SuperSOT™3 SuperSOT™6 SuperSOT™-8 SvncFET™ SYSTEM ® The Power Franchise®

p wer TinyBoost™ TinyBuck™ TinyLogic<sup>®</sup> TINYOPTO™ TinyPower™ TinyPWM™ TinyWire™ μSerDes™ UHC<sup>®</sup>

Ultra FRFET™ UniFET™  $VCX^{TM}$

\* EZSWITCH™ and FlashWriter® are trademarks of System General Corporation, used under license by Fairchild Semiconductor.

#### DISCLAIMER

FlashWriter®\*

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

- 1. Life support devices or systems are devices or systems 2. A critical component in any component of a life support, which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### PRODUCT STATUS DEFINITIONS

#### Definition of Terms

| Datasheet Identification | Product Status         | Definition                                                                                                                                                                                               |

|--------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production       | This datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production        | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production      | This datasheet contains specifications on a product that has been discontinued by Fairchild Semiconductor. The datasheet is printed for reference information only.                                      |

Rev. 132