February 2008

# FDG901D Slew Rate Control IC for P-Channel MOSFETs

#### **Features**

- Three Programmable Slew Rates

- Reduces Inrush Current

- Minimizes EMI

- Normal Turn-Off Speed

- Low-Power CMOS Operates Over Wide Voltage Range

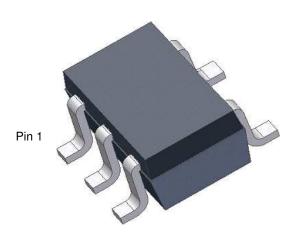

- Compact Industry Standard SC70-5 Surface Mount Package

- RoHS Compliant

### **Applications**

- Battery Load switch

- Power management

### **General Description**

The FDG901D is specifically designed to control the turn on of a P-Channel MOSFET in order to limit the inrush current in battery switching applications with high capacitance loads. During turn-on, the FDG901D drives the MOSFET's gate low with a regulated current source, thereby controlling the MOSFET's turn on. For turn-off, the IC pulls the MOSFET gate up quickly for efficient turn off.

### **Package Marking and Ordering Information**

| Device Marking | Device  | Reel Size | Tape Width | Quantity   |

|----------------|---------|-----------|------------|------------|

| 91             | FDG901D | 7"        | 8mm        | 3000 units |

SC70-5

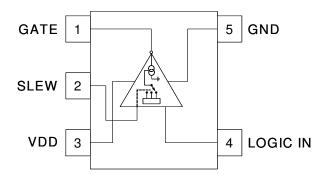

## **Pin Configuration**

## **Absolute Maximum Ratings**

| Parameter                                        | Min. | Max. | Unit |  |

|--------------------------------------------------|------|------|------|--|

| Supply Voltage                                   | -0.5 | 10   | V    |  |

| DC Input Voltage (Logic Inputs)                  | -0.7 | 9    | V    |  |

| Power Dissipation for Single Operation @ 85 ℃    |      | 150  | mW   |  |

| Operating and Storage Junction Temperature       | -65  | 150  | ℃    |  |

| Thermal Resistance, Junction to Ambient (note 1) |      | 425  | °C/W |  |

## **Recommended Operating Range**

| Parameter                      | Min. | Max. | Unit |  |

|--------------------------------|------|------|------|--|

| Supply Voltage                 | 2.7  | 6    | V    |  |

| Operating Junction Temperature | -40  | 150  | ℃    |  |

### **Electrical Characteristics**

T<sub>A</sub> = 25 °C unless otherwise noted

| Parameter                                     | Symbol             | Conditions                                                         |                            | Min. | Тур. | Max. | Units |

|-----------------------------------------------|--------------------|--------------------------------------------------------------------|----------------------------|------|------|------|-------|

| Logic Levels                                  | <b>-</b>           | 1                                                                  |                            | ·    | •    | •    | •     |

| Logic High Input Voltage                      | V <sub>IH</sub>    | V <sub>DD</sub> = 2.7V to 6.0V                                     |                            | 2.55 |      |      | V     |

| Logic Low Input Voltage                       | V <sub>IL</sub>    | $V_{DD} = 2.7V \text{ to } 6.0$                                    | V                          |      |      | 2.0  | V     |

| Off Characteristics - Slew Rate Co            | ntrol Driver       |                                                                    |                            |      |      |      |       |

| Supply Input Breakdown Voltage                | BV <sub>DG</sub>   | $I_{DG} = 10\mu A, V_{IN} = 0V, V_{SLEW} = 0V$                     |                            | 9    |      |      | V     |

| Slew Input Breakdown Voltage                  | BV <sub>SLEW</sub> | $I_{SLEW} = 10\mu A, V_{IN} = 0V$                                  |                            | 9    |      |      | V     |

| Logic Input Breakdown Voltage                 | BV <sub>IN</sub>   | $I_{IN} = 10\mu A$ , $V_{SLEW} = 0V$                               |                            | 9    |      |      | V     |

| Supply Input Leakage Current                  | IR <sub>DG</sub>   | V <sub>DG</sub> = 8V, V <sub>IN</sub> = 0V, V <sub>SLEW</sub> = 0V |                            |      |      | 100  | nA    |

| Slew Input Leakage Current                    | IR <sub>SLEW</sub> | V <sub>SLEW</sub> = 8V, V <sub>IN</sub> = 0V                       |                            |      |      | 100  | nA    |

| Logic Input Leakage Current                   | IR <sub>IN</sub>   | V <sub>IN</sub> = 8V, V <sub>SLEW</sub> = 0V                       |                            |      |      | 100  | nA    |

| On Characteristics - Slew Rate Control Driver |                    |                                                                    |                            |      |      |      |       |

| Gate Current                                  |                    | V <sub>IN</sub> = 6V,<br>V <sub>GATE</sub> = 2V                    | Slew Pin = Open            |      | 90   | 120  | μA    |

|                                               | $I_{G}$            |                                                                    | Slew Pin = GND             |      | 1    | 10   | μΑ    |

|                                               |                    |                                                                    | Slew Pin = V <sub>DD</sub> |      | 10   | 50   | nA    |

Notes:  $R_{\theta \ JA}$  is the sum of the junction-to-case and case-to-ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of the drain pins.  $R_{\theta \ JC}$  is guaranteed by design while  $R_{\theta \ CA}$  is determined by the user's board design.

2

### **Electrical Characteristics Cont.**

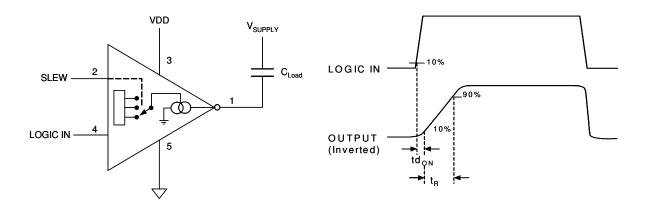

**Test Circuit**

T<sub>A</sub> = 25 °C unless otherwise noted

| Parameter                                                                                                                                | Symbol           | Ol Conditions |                   | Min. | Тур. | Max. | Units |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|-------------------|------|------|------|-------|

| P-Channel Switching Times (V <sub>SUPPLY</sub> = 5.5V, V <sub>DD</sub> = 5.5V, Logic IN = 5.5V, C <sub>LOAD</sub> = 510pF, Test Circuit) |                  |               |                   |      |      |      |       |

| Delay On Time                                                                                                                            | td <sub>ON</sub> | Slew Pin      | = Open            |      | 8.3  |      | μs    |

|                                                                                                                                          |                  |               | = GND             |      | 0.6  |      | ms    |

|                                                                                                                                          |                  |               | = V <sub>DD</sub> |      | 2.2  |      | ms    |

| V <sub>OUT</sub> Rise Time                                                                                                               |                  | Slew Pin      | = Open            |      | 28   |      | μs    |

|                                                                                                                                          | t <sub>R</sub>   |               | = GND             |      | 1.8  |      | ms    |

|                                                                                                                                          |                  |               | = V <sub>DD</sub> |      | 11   |      | ms    |

|                                                                                                                                          | dv/dt            | Slew Pin      | = Open            |      | 162  |      | V/ms  |

| Output Slew Rate                                                                                                                         |                  |               | = GND             |      | 26   |      | V/ms  |

|                                                                                                                                          |                  |               | = V <sub>DD</sub> |      | 0.3  |      | V/ms  |

Switching Waveform

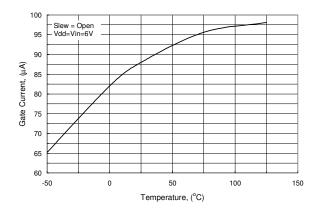

### **Typical Characteristics**

Figure 1. Gate Output Current vs. Temperature (SLEW = OPEN)

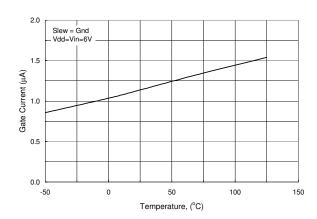

Figure 2. Gate Output Current vs. Temperature (SLEW = GROUND)

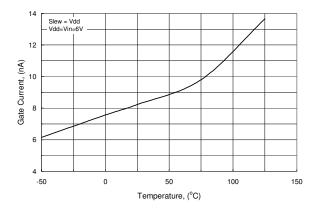

Figure 3. Gate Output Current vs. Temperature  $(\text{SLEW} = \text{V}_{\text{DD}})$

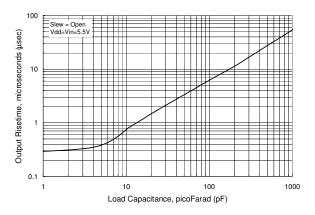

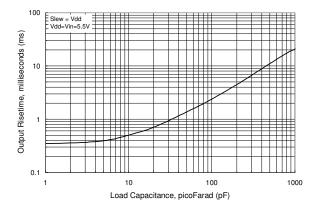

Figure 4. t<sub>RISE</sub> vs. Load Capacitance (SLEW = OPEN)

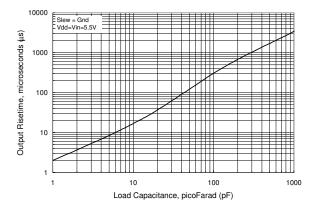

Figure 5. t<sub>RISE</sub> vs. Load Capacitance (SLEW = GROUND)

Figure 6.  $t_{RISE}$  vs. Load Capacitance (SLEW =  $V_{DD}$ )

4

## **Typical Characteristics**

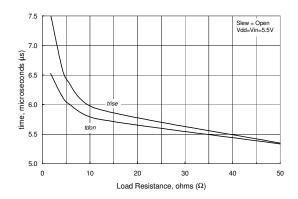

Figure 7. Switching Time vs. Load Resistance (SLEW = OPEN)

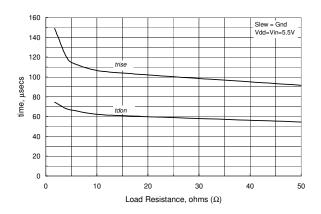

Figure 8. Switching Time vs. Load Resistance (SLEW = GROUND)

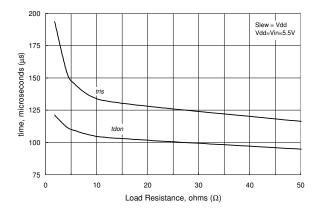

Figure 9. Switching Time vs. Load Resistance  $(\mathsf{SLEW} = \mathsf{V}_\mathsf{DD})$

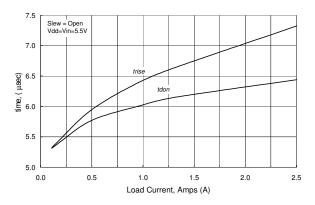

Figure 10. Switching Time vs. Load Current (SLEW = OPEN)

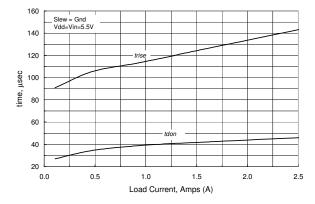

Figure 11. Switching Time vs. Load Current (SLEW = GROUND)

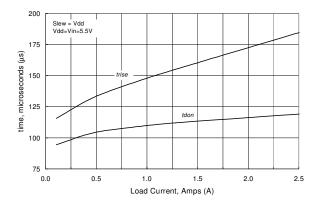

Figure 12. Switching Time vs. Load Current  $(SLEW = V_{DD})$

5 www.fairchildsemi.com

### **Application Information**

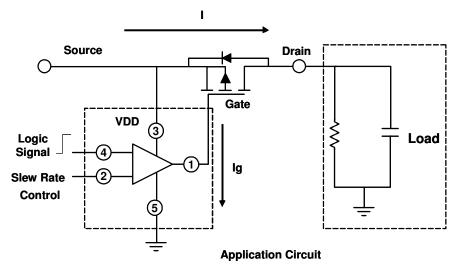

#### **Typical Application**

Battery powered systems make extensive usage of load switching, turning the power to subsystems off, in order to extend battery life. Power MOSFETs are used to accomplish this task. In PDA's and Cell phones, these MOSFETs are usually low threshold P-Channels. Since the loads typically include bypass capacitor components (high capacitive component), a high inrush current can occur when the load is switched on. This inrush current can cause transients on the main power supply disturbing circuitry supplied by it.

The simplest method of limiting the inrush current is to control the slew rate of the MOSFET switch. This can be done with external R/C circuits, but this approach can occupy significant PCB area, and involves other compromises in performance. The slew rate control driver IC FDG901D is specifically designed to interface low voltage digital circuitry with power MOSFETs and reduce the rapid inrush current in load switch applications. The IC limits inrush current by controlling the current, which drives the gate of the P-Channel MOSFET switch.

The control input is a CMOS compatible input with a minimum high input voltage of 2.55V with a power rail voltage of 6V. Therefore, it is compatible with any CMOS logic voltages between 2.55V and 5V and under these conditions there is no additional configuration required.

The Slew Rate Control Driver (FDG901D) is designed to give a programmed choice of one of three steady dv/dt states on the output during turn-on. To change the dv/dt value, the user needs to use the Slew Rate Control Pin (Pin 2). To utilize the smallest current setting ( 10 nA) from the IC, a voltage equal to  $V_{DD}$  must be applied to the Slew Rate Control Pin 2. To use the next higher current setting (  $\sim\!1\mu\text{A})$  a voltage equal to Ground must be applied to Pin 2. To achieve the highest current setting (  $\sim\!80\mu\text{A})$  or obtain a faster switching speed, the Slew Rate Pin2 must be open (floating). A higher value of capacitance will result in a slower switching rate. To determine the switching times of each setting use the simple equation:

$$t = \frac{Q_g}{I_C}$$

where Qg is the Gate charge in nC for a given MOSFET and IG is the gate current controlled by the slew rate pin.

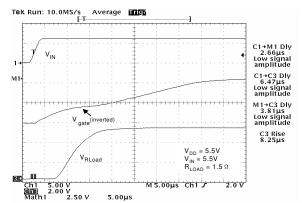

Below is a captured image from an oscilloscope depicting the device response. The FDG901D was connected to control an FDG258P P-Channel DMOS. The Slew Rate control pin was set to open (floating state).

Circuit waveforms for an FDG901D controlling a P-Channel FDG258P MOFET

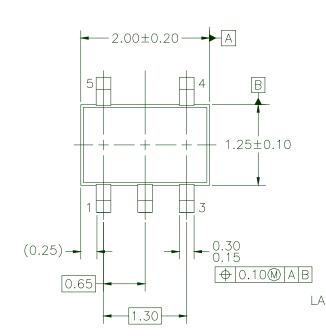

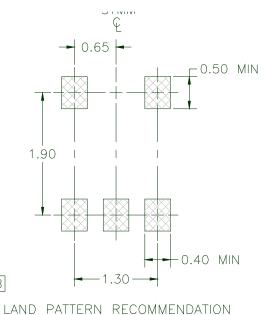

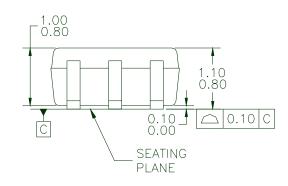

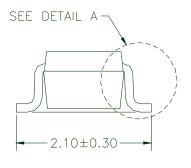

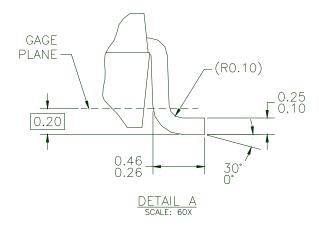

## **Dimensional Outline and Pad Layout**

NOTES: UNLESS OTHERWISE SPECIFIED

- A) THIS PACKAGE CONFORMS TO EIAJ SC-88A, 1996.

- B) ALL DIMENSIONS ARE IN MILLIMETERS.

- C) DIMENSIONS DO NOT INCLUDE BURRS OR MOLD FLASH.

#### **TRADEMARKS**

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

ACEX<sup>®</sup>

Build it Now<sup>™</sup>

CorePLUS<sup>™</sup>

CROSSVOLT<sup>™</sup>

CTL<sup>™</sup>

Current Transfer Logic™ EcoSPARK<sup>®</sup> EZSWITCH™ \*

EZ™ F®

Fairchild<sup>®</sup>

Fairchild Semiconductor<sup>®</sup>

FACT Quiet Series™

FACT<sup>®</sup>

FAST<sup>®</sup>

FastvCore<sup>™</sup>

FlashWriter<sup>®</sup>

FPS™ FRFET®

Global Power Resource<sup>sм</sup>

Green FPS™

Green FPS™ e-Series™

GTOTM

i-LoTM

IntelliMAXTM

ISOPLANARTM

MegaBuckTM

MICROCOUPLERTM

MicroFETTM

MicroPakTM

MillerDrive™

Motion-SPM™

OPTOLOGIC®

OPTOPLANAR®

PDP-SPM™ Power220® POWEREDGE® Power-SPM™ PowerTrench®

Programmable Active Droop™ OFFT®

QFE1° QS™

QT Optoelectronics™

Quiet Series™

RapidConfigure™

SMART START™

SPM®

STEALTH™

SuperFET™

SuperSOT™-3

SuperSOT™-6

SuperSOT™-8

Franchise

TinyBoost™

TinyBuck™

TinyLogic®

TINYOPTO™

TinyPower™

TinyPWM™

TinyWire™

µSerDes™

UHC®

SupreMOS™

The Power Franchise®

SyncFET™

SYSTEM®

GENERAL

Ultra FRFET™ UniFET™ VCX™

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification | Product Status         | Definition                                                                                                                                                                                               |

|--------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production       | This datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production        | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production      | This datasheet contains specifications on a product that has been discontinued by Fairchild Semiconductor. The datasheet is printed for reference information only.                                      |

Rev. I33

<sup>\*</sup> EZSWITCH™ and FlashWriter® are trademarks of System General Corporation, used under license by Fairchild Semiconductor.