# 1A Buck-Boost DC/DC Converter with Programmable Input Current Limit

### **FEATURES**

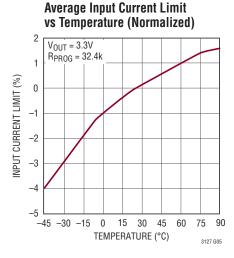

- Programmable (0.2A to 1A) ±4% Accurate Average Input Current Limit

- Regulated Output with Input Voltages Above, Below or Equal to the Output

- 1.8V to 5.5V (Input) and 1.8V to 5.25V (Output) Voltage Range

- 0.6A Continuous Output Current: V<sub>IN</sub> > 1.8V

- 1A Continuous Output Current: V<sub>IN</sub> > 3V

- Single Inductor

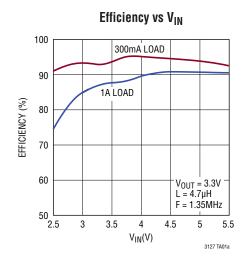

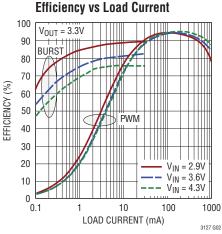

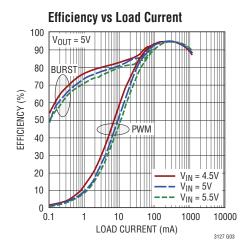

- Synchronous Rectification: Up to 96% Efficiency

- Burst Mode® Operation:  $I_0 = 35\mu A$  (Pin Selectable)

- Output Disconnect in Shutdown

- <1uA Shutdown Current</p>

- Small, Thermally Enhanced 10-Lead (3mm × 3mm × 0.75mm) DFN and 12-Lead MSOP Packages

### **APPLICATIONS**

- USB Powered GSM Modems

- Supercap Charger

- Handheld Test Instruments

- PC Card Modems

- Wireless Terminals

# DESCRIPTION

The LTC®3127 is a wide  $V_{IN}$  range, highly efficient, 1.35MHz fixed frequency buck-boost DC/DC converter that operates from input voltages above, below or equal to the output voltage. The LTC3127 features programmable average input current limit, making it ideal for power-limited input sources. The input current limit is programmed with a single resistor and is accurate from 0.2A to 1A of average input current.

The topology incorporated provides a continuous transfer function through all operating modes. Other features include <1  $\mu$ A shutdown current, pin-selectable Burst Mode operation and thermal overload protection. The LTC3127 is housed in thermally enhanced 10-lead (3mm  $\times$  3mm  $\times$  0.75mm) DFN packages and 12-lead MSOP packages.

∠T, LTC, LTM, Linear Technology, Burst Mode and the Linear logo are registered trademarks and PowerPath and ThinSOT are trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

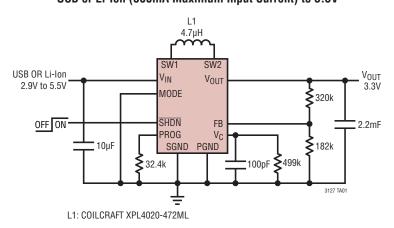

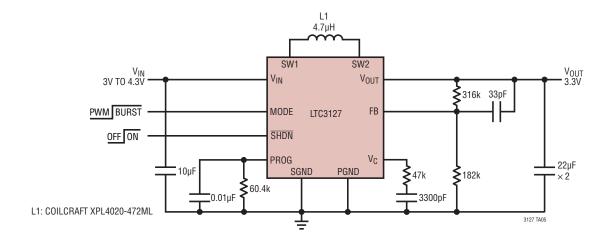

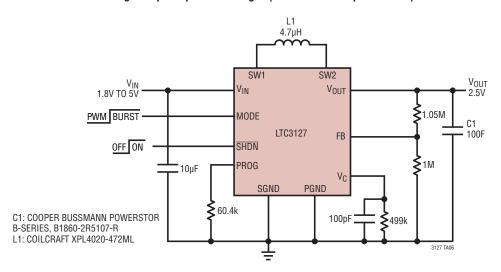

# TYPICAL APPLICATION

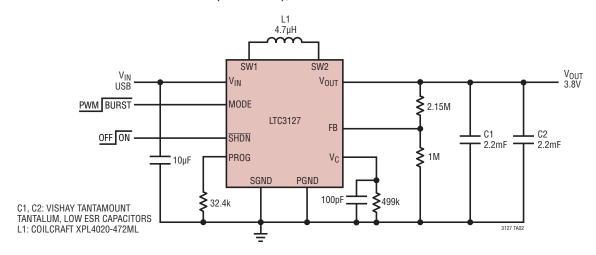

USB or Li-Ion (500mA Maximum Input Current) to 3.3V

# **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| V <sub>IN</sub> , V <sub>OUT</sub> Voltage | 0.3 to 6V   |

|--------------------------------------------|-------------|

| SW1, SW2 DC Voltage                        | – 0.3 to 6V |

| SW1, SW2 Pulsed (<100ns) Voltage           | 0.3 to 7V   |

| MODE, FB, V <sub>C</sub> Voltage           | – 0.3 to 6V |

| SHDN Voltage                               |             |

| PROG Voltage0.3 to 6V                       |

|---------------------------------------------|

| Operating Junction Temperature Range        |

| (Note 2)40°C to 85°C                        |

| Maximum Junction Temperature (Note 5) 125°C |

| Storage Temperature Range65°C to 125°C      |

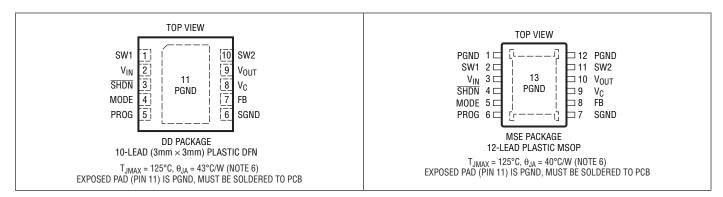

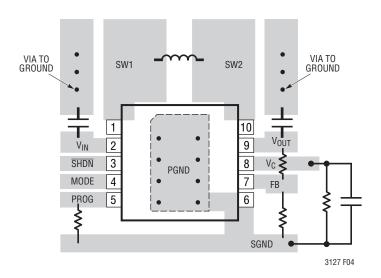

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|-------------------|--------------|---------------------------------|-------------------|

| LTC3127EDD#PBF   | LTC3127EDD#TRPBF  | LDYD         | 10-Lead (3mm × 3mm) Plastic DFN | -40°C to 85°C     |

| LTC3127EMSE#PBF  | LTC3127EMSE#TRPBF | 3127         | 12-Lead Plastic MSOP            | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_J = 25 \,^{\circ}\text{C}$ . $V_{IN} = 3.6 \,^{\circ}\text{V}$ , $V_{OUT} = 3.3 \,^{\circ}\text{V}$ , unless otherwise noted.

| PARAMETER                              | CONDITIONS                                                            | - | MIN       | TYP        | MAX   | UNITS     |

|----------------------------------------|-----------------------------------------------------------------------|---|-----------|------------|-------|-----------|

| Input Operating Range                  |                                                                       | • | 1.8       |            | 5.5   | V         |

| Output Voltage Adjust                  |                                                                       | • | 1.8       |            | 5.25  | V         |

| Feedback Voltage                       |                                                                       | • | 1.165     | 1.195      | 1.225 | V         |

| Feedback Input Current                 | V <sub>FB</sub> = 1.25V                                               |   |           | 1          | 50    | nA        |

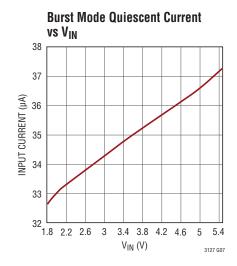

| Quiescent Current—Burst Mode Operation | V <sub>FB</sub> > 1.225, V <sub>MODE</sub> = V <sub>IN</sub> (Note 4) |   |           | 35         |       | μА        |

| Quiescent Current—Shutdown             | V <sub>SHDN</sub> = 0V, Including SW Leakage                          |   |           | 0.1        | 4     | μА        |

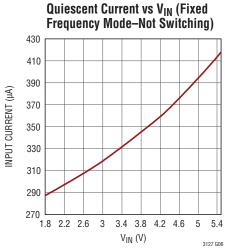

| Quiescent Current—Active               | V <sub>FB</sub> > 1.225V, V <sub>MODE</sub> = 0V (Note 4)             |   |           | 400        |       | μА        |

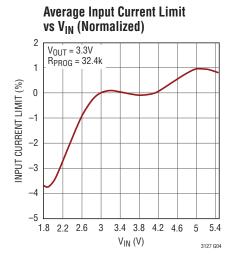

| Input Current Limit                    | R <sub>PROG</sub> = 32.4k (Note 3)                                    |   | 480       | 500        | 520   | mA        |

|                                        | 0°C to 85°C (Note 3)                                                  | • | 465       | 500        | 540   | mA        |

|                                        | -40°C to 85°C (Note 3)                                                | • | 430       | 500        | 540   | mA        |

| Peak Current Limit                     |                                                                       | • | 2         | 2.5        |       | А         |

| Reverse-Current Limit                  |                                                                       |   | 0.15      | 0.3        | 0.45  | А         |

| P-Channel MOSFET Leakage               | Switches A and D                                                      |   |           | 0.1        | 4     | μА        |

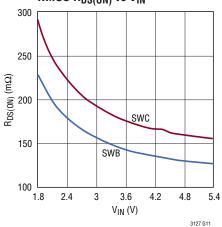

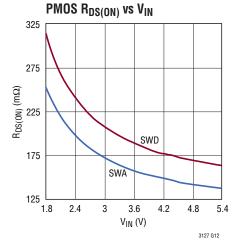

| N-Channel MOSFET On-Resistance         | Switch B<br>Switch C                                                  |   |           | 140<br>170 |       | mΩ        |

| P-Channel MOSFET On-Resistance         | Switch A<br>Switch D                                                  |   |           | 160<br>190 |       | $m\Omega$ |

| Maximum Duty Cycle                     | Boost( % Switch C On)<br>Buck (% Switch A On)                         | • | 80<br>100 | 90         |       | %<br>%    |

| Minimum Duty Cycle                     |                                                                       | • |           |            | 0     | %         |

| Frequency Accuracy                     |                                                                       | • | 1         | 1.35       | 1.7   | MHz       |

| SHDN Input High Voltage                |                                                                       | • | 1.2       |            |       | V         |

| SHDN Input Low Voltage                 |                                                                       | • |           |            | 0.3   | V         |

| SHDN Input Current                     | V <sub>SHDN</sub> = 5.5V                                              |   |           | 0.01       | 1     | μА        |

| MODE Input High Voltage                |                                                                       | • | 1.2       |            |       | V         |

| MODE Input Low Voltage                 |                                                                       | • |           |            | 0.3   | V         |

| MODE Input Current                     | V <sub>MODE</sub> = 5.5V                                              |   |           | 0.01       | 1     | μА        |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC3127 is guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the -40°C to 85°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. Note that the maximum ambient temperature is determined by specific operating conditions in conjunction with board layout, the rated package thermal resistance and other environmental factors.

**Note 3:** Specification is guaranteed when the inductor current is in continuous conduction.

**Note 4:** Current measurements are made when the output is not switching.

**Note 5**: This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may result in device degradation or failure.

**Note 6:** Failure to solder the exposed backside of the package to the PC board ground plane will result in a thermal resistance much higher than 40°C/W.

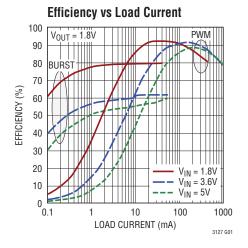

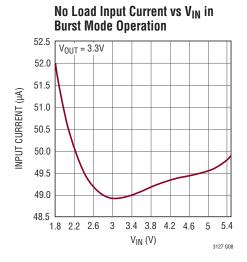

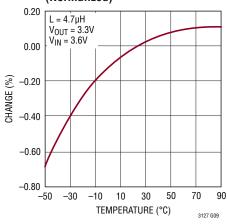

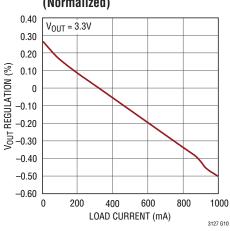

# TYPICAL PERFORMANCE CHARACTERISTICS ( $T_J = 25$ °C, unless otherwise noted)

TECHNOLOGY TECHNOLOGY

# TYPICAL PERFORMANCE CHARACTERISTICS $(T_J = 25^{\circ}C, unless otherwise noted)$

#### Vout Regulation vs Load Current (Normalized)

# NMOS R<sub>DS(ON)</sub> vs V<sub>IN</sub>

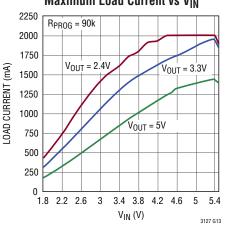

# Maximum Load Current vs V<sub>IN</sub>

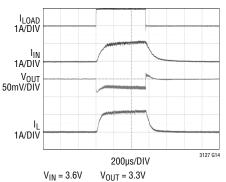

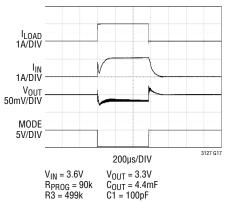

**Load Transient Response in Fixed** Frequency Mode, No Load to 1A, **Not in Input Current Limit**

R<sub>PROG</sub> = 90k R3 = 499k C<sub>OUT</sub> = 4.4mF C1 = 100pF

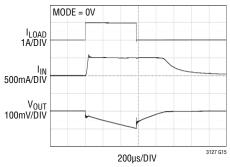

#### **Load Transient Response in Fixed** Frequency Mode, No Load to 1A, in Input Current Limit

$V_{IN} = 3.6V$  $V_{OUT} = 3.3V$ R<sub>PROG</sub> = 32.4k R3 = 499k C<sub>OUT</sub> = 4.4mF C1 = 100pF

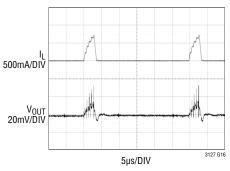

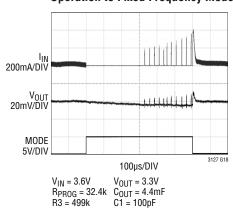

#### **Burst Mode Operation**

$V_{OUT} = 3.3V$  $V_{IN} = 3.6V$ R<sub>PROG</sub> = 32.4k R3 = 499k C<sub>OUT</sub> = 4.4mF C1 = 100pF

# TYPICAL PERFORMANCE CHARACTERISTICS ( $T_J = 25$ °C, unless otherwise noted)

#### **Load Transient Response in Burst Mode Operation, No Load** to 1A, Not in Input Current Limit

#### **Transition from Burst Mode Operation to Fixed Frequency Mode**

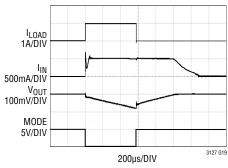

#### Load Transient Response in **Burst Mode Operation, No Load** to 1A, in Input Current Limit

$V_{IN} = 3.6V$   $R_{PROG} = 32.4k$  R3 = 499k $\begin{array}{l} V_{OUT} = 3.3V \\ C_{OUT} = 4.4 mF \\ C1 = 100 pF \end{array}$

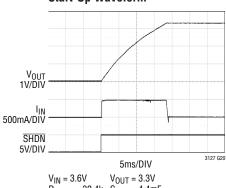

#### Start-Up Waveform

V<sub>OUT</sub> = 3.3V C<sub>OUT</sub> = 4.4mF C1 = 100pF R<sub>PROG</sub> = 32.4k R3 = 499k

# PIN FUNCTIONS (DD Package)

**SW1 (Pin 1):** Switch Pin Where Internal Switches A and B Are Connected. Connect inductor from SW1 to SW2. Minimize trace length to reduce EMI.

$V_{IN}$  (Pin 2): Input Supply Pin. Internal  $V_{CC}$  for the IC. A  $10\mu F$  or greater ceramic capacitor should be placed as close to  $V_{IN}$  and PGND as possible.

SHDN (Pin 3): Logic-Controlled Shutdown Input.

SHDN = High: Normal Operation

SHDN = Low: Shutdown

**MODE (Pin 4):** Pulse Width Modulation/Burst Mode Selection Input.

MODE = High: Burst Mode Operation

MODE = Low: PWM Operation Only. Forced continuous conduction mode.

**PROG** (Pin 5): Sets the Average Input Current Limit Threshold. Connect a resistor from PROG to ground. See below for component value selection.

$R_{PROG} = 54.92 \bullet I_{LIMIT} (A) + 4.94 (k\Omega)$

**SGND (Pin 6):** Signal Ground for the IC. Terminate the PROG resistor, compensation components and the output voltage divider to SGND.

**FB (Pin 7):** Feedback Pin. Connect resistor divider tap here. The output voltage can be adjusted from 1.8V to 5.25V. The feedback reference voltage is 1.195V.

$$V_{OUT} = 1.195 \bullet \left(1 + \frac{R2}{R1}\right) V$$

**V<sub>C</sub>** (**Pin 8**): Error Amplifier Output. Place compensation components from this pin to SGND.

$V_{OUT}$  (**Pin 9**): Output of the Synchronous Rectifier. Connect the output filter capacitor from this pin to GND. A minimum value of  $22\mu F$  is recommended. Output capacitors must be low ESR.

**SW2 (Pin 10):** Switch Pin Where Internal Switches C and D Are Connected. Minimize trace length to reduce EMI.

PGND (Exposed Pad Pin 11): Power Ground. The exposed pad must be soldered to the PCB ground plane.

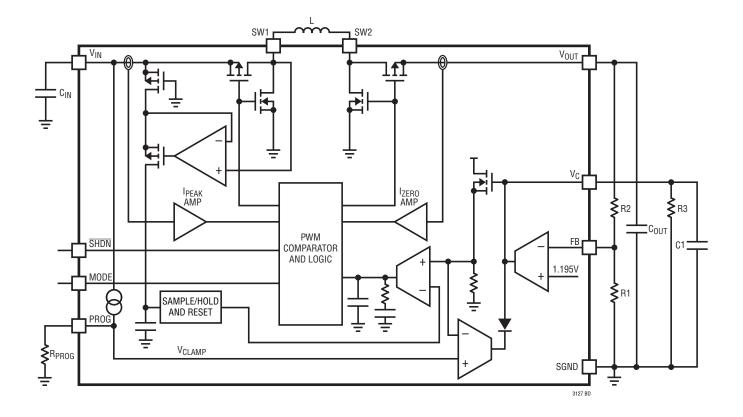

# **BLOCK DIAGRAM**

# **OPERATION**

The LTC3127 is an average input current controlled buckboost DC/DC converter offered in both a thermally enhanced 3mm  $\times$  3mm DFN package and a thermally enhanced 12-lead MSOP package. The buck-boost converter utilizes a proprietary switching algorithm which allows its output voltage to be regulated above, below or equal to the input voltage. The low  $R_{DS(ON)}$ , low gate charge synchronous switches efficiently provide high frequency PWM control. High efficiency is achieved at light loads when Burst Mode operation is commanded.

#### **PWM Mode Operation**

The LTC3127 uses fixed frequency, average input current PWM control. The MODE pin can be used to select automatic Burst Mode operation (MODE connected to  $V_{\text{IN}}$ ) or to disable Burst Mode operation and select forced continuous conduction operation for low noise applications (MODE grounded).

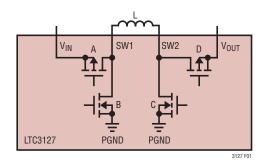

A proprietary switching algorithm allows the converter to switch between buck, buck-boost and boost modes without discontinuity in inductor current or loop characteristics. The switch topology for the buck-boost converter is shown in Figure 1.

When the input voltage is significantly greater than the output voltage, the buck-boost converter operates in buck mode. Switch D turns on continuously and switch C remains off. Switches A and B are pulse width modulated to produce the required duty cycle to support the output regulation voltage. As the input voltage decreases, switch A remains on for a larger portion of the switching cycle. When the duty cycle reaches approximately 85%, the switch pair AC begins turning on for a small fraction of the switching period. As the input voltage decreases further,

the AC switch pair remains on for longer durations and the duration of the BD phase decreases proportionally. As the input voltage drops below the output voltage, the AC phase will eventually increase to the point that there is no longer any BD switching. At this point, switch A remains on continuously while switch pair CD is pulse width modulated to obtain the desired output voltage. At this point, the converter is operating solely in boost mode.

This switching algorithm provides a seamless transition between operating modes and eliminates discontinuities in average inductor current, inductor current ripple, and loop transfer function throughout all three operational modes. These advantages result in increased efficiency and stability in comparison to the traditional 4-switch buck-boost converter. In forced PWM mode operation, the inductor is forced to have continuous conduction. This allows for a constant switching frequency and better noise performance.

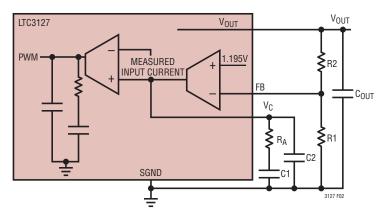

#### **Error Amplifier and Compensation**

The buck-boost converter utilizes two control loops. The outer voltage loop determines the amount of current required to regulate the output voltage. The voltage loop is externally compensated and can be configured with either integral compensation or proportional control. The inner current loop is internally compensated and forces the input current to equal the commanded current.

When  $V_C$  is compensated via proportional control, the dominant pole of the output capacitor is used to ensure stability with a minimum of  $1000\mu F$  of capacitance on the output when a 499k resistor is used. There is no maximum capacitance limitation with proportional compensation.

Figure 1. Buck-Boost Switch Topology

# **OPERATION**

Integral compensation is required if an output capacitor less than  $1000\mu F$  but greater than  $44\mu F$  is used, otherwise using proportional compensation is recommended.

When compensating the converter with integral compensation it is important to consider that the total bandwidth of the network must be below 15kHz. The inner current loop of the LTC3127 eliminates one of the double poles caused by the inductor. The output capacitor causes a dominant pole and also a zero, and the resistor divider sets the gain.

$$G_{DC} = 1 + \frac{R2}{R1}$$

$$f_{POLE1} = \frac{1}{2 \cdot \pi \cdot R_{LOAD} \cdot C_{OUT}}$$

$$f_{ZERO1} = \frac{1}{2 \cdot \pi \cdot R_{ESR} \cdot C_{OUT}}$$

Using the compensation network show in Figure 2, the voltage loop compensation can be approximated with the following transfer function:

$$H_{COMP}(s) = \frac{g_{m} \bullet (C1 \bullet R_{A} \bullet s + 1)}{s \bullet (C1 \bullet C2 \bullet R_{A} \bullet s + C1 + C2)}$$

where  $g_m = 150 \cdot 10^{-6}$

This causes poles and zeros to occur at the following locations:

$$f_{POLE2} \cong DC$$

$$f_{POLE3} = \frac{1}{2 \cdot \pi \cdot R_A \cdot C2}$$

$$f_{ZERO2} = \frac{1}{2 \cdot \pi \cdot R_A \cdot C1}$$

The poles and zeros of the compensation should be determined by looking at where  $f_{POLE1}$  lands at the minimum load where the LTC3127 will be continuously conducting, which places the dominant pole at its lowest frequency. After setting the poles and zeros for the compensation, the phase margin of the system should be greater than 45° and the gain margin should be greater than 3dB. Following these two criteria will help to ensure stability.

#### **Current Limit Operation**

The buck-boost converter has two current limit circuits. The primary current limit is an average input current limit circuit that clamps the output of the outer voltage loop. This limits the amount of input current that can be commanded, and the inner current loop regulates to that clamped value.

Figure 2. Buck-Boost External Compensation

# **OPERATION**

The input current limit is set by the R<sub>PROG</sub> resistor placed on the PROG pin to SGND. The resistor value can be calculated using the following formula:

$$R_{PROG} = 54.92 \bullet I_{LIMIT} (A) + 4.94 (k\Omega)$$

Where I<sub>LIMIT</sub> is the average input current limit in amps.

A secondary 2.5A (typical) current limit forces switches B and D on and A and C off if tripped. This current limit is not affected by the value of  $R_{PROG}$ .

#### **Reverse Current Limit**

The reverse current comparator on switch D monitors the inductor current supplied from the output. When this current exceeds 300mA (typical) switch D will be turned off for the remainder of the switching cycle.

#### **Burst Mode Operation**

When the MODE pin is held high the LTC3127 will function in Burst Mode operation as long as the load current is typically less than 35mA. In Burst Mode operation, the LTC3127 still switches at a fixed frequency of 1.35MHz, using the same error amplifiers and loop compensation for average input current mode control. This control method eliminates any output transient when switching between modes. In Burst Mode operation, energy is delivered to the output until the output voltage reaches the nominal regulation value. At this point, the LTC3127 transitions to sleep mode where the output switches are shut off and the LTC3127 consumes only 35 $\mu$ A of quiescent current from  $V_{IN}$ . When the output voltage droops slightly, switching resumes. This maximizes efficiency at very light loads by minimizing switching and quiescent losses.

#### **Zero Current Comparator**

The zero current comparator monitors the inductor current to the output and shuts off the synchronous rectifier when this current reduces to approximately 30mA. This prevents the inductor current from reversing in polarity, improving efficiency at light loads. This comparator is only active in Burst Mode operation.

#### **Anti-Ringing Control**

The anti-ringing control connects a resistor from SW1 and SW2 to PGND to prevent high frequency ringing during discontinuous current mode operation in Burst Mode. Although the ringing of the resonant circuit formed by L and CSW (capacitance on SW pin) is low energy, it can cause EMI radiation.

#### Shutdown

Shutdown of the converter is accomplished by pulling  $\overline{SHDN}$  below 0.3V and enabled by pulling  $\overline{SHDN}$  above 1.2V. Note that  $\overline{SHDN}$  can be driven above  $V_{IN}$  or  $V_{OUT}$ , as long as it is limited to less than the absolute maximum rating.

#### Thermal Shutdown

If the die temperature exceeds 150°C (typical) the LTC3127 will be disabled. All power devices will be turned off and both switch nodes will be high impedance. The LTC3127 will restart (if enabled) when the die temperature drops to approximately 140°C.

#### **Thermal Regulator**

To help prevent the part from going into thermal shutdown when charging very large capacitive loads, the LTC3127 is equipped with a thermal regulator. If the die temperature exceeds 130°C (typical) the average current limit is lowered to help reduce the amount of power being dissipated in the package. The current limit will be approximately 0A just before thermal shutdown. The current limit will return to its full value when the die temperature drops back below 130°C.

### **Undervoltage Lockout**

If the input supply voltage drops below 1.7V (typical), the LTC3127 will be disabled and all power devices will be turned off.

A typical LTC3127 application circuit is shown on the front page of this data sheet. The external component selection is determined by the desired output voltage, input current and ripple voltage requirements for each particular application. However, basic guidelines and considerations for the design process are provided in this section.

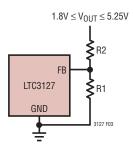

#### **Buck-Boost Output Voltage Programming**

The buck-boost output voltage is set by a resistive divider according to the following formula:

$$V_{OUT} = 1.195V \bullet \left(1 + \frac{R2}{R1}\right)V$$

The external divider is connected to the output as shown in Figure 3. The buck-boost converter utilizes input current mode control, and the output divider resistance does not play a role in the stability.

Figure 3. Setting the Buck-Boost Output Voltage

#### **Buck-Boost Inductor Selection**

To achieve high efficiency, a low ESR inductor should be utilized for the buck-boost converter. The inductor must have a saturation rating greater than the worst case average inductor current plus half the ripple current. The peak-to-peak inductor current ripple will be larger in buck and boost mode than in the buck-boost region. The peak-to-peak inductor current ripple for each mode can be calculated from the following formulas, where L is the inductance in  $\mu H\colon$

$$\Delta I_{L,P-P,BUCK} = \frac{V_{OUT} (V_{IN} - V_{OUT})}{V_{IN} \bullet L \bullet (1.35MHz)} (A)$$

$$\Delta I_{L,P-P,BOOST} = \frac{V_{IN} (V_{OUT} - V_{IN})}{V_{OUT} \bullet L \bullet (1.35MHz)} \quad (A)$$

The LTC3127 can utilize small surface mount inductors due to its fast 1.35MHz switching frequency. Inductor values between 2.2 $\mu$ H and 4.7 $\mu$ H are suitable for most applications. Larger values of inductance will allow slightly greater output current capability by reducing the inductor ripple current. Increasing the inductance above 10 $\mu$ H will increase size while providing little improvement in output current capability.

The inductor current ripple is typically set for 20% to 40% of the maximum inductor current. High frequency ferrite core inductor materials reduce frequency dependent power losses compared to cheaper powdered iron types, improving efficiency. The inductor should have low ESR (series resistance of the windings) to reduce the I2R power losses, and must be able to support the peak inductor current without saturating. Molded chokes and some chip inductors usually do not have enough core area to support the peak inductor currents of 2.5A seen on the LTC3127. To minimize radiated noise, use a shielded inductor. See Table 1 and the reference schematics for suggested components and suppliers.

Table 1. Recommended Inductors

| VENDOR                                                | PART/STYLE                                                                                |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Coilcraft<br>847-639-6400<br>www.coilcraft.com        | LP02506<br>LPS4012, LPS4018<br>MSS6122<br>MSS4020<br>M0S6020<br>DS1605, D01608<br>XPL4020 |

| Coiltronics<br>www.cooperet.com                       | SD52, SD53<br>SD3114, SD3118                                                              |

| Murata<br>714-852-2001<br>www.murata.com              | LQH55D                                                                                    |

| Sumida<br>847-956-0666<br>www.sumida.com              | CDH40D11                                                                                  |

| Taiyo-Yuden<br>www.t-yuden.com                        | NP04SB<br>NR3015<br>NR4018                                                                |

| TDK<br>847-803-6100<br>www.component.tdk.com          | VLP, LTF<br>VLF, VLCF                                                                     |

| Würth Elektronik<br>201-785-8800<br>www.we-online.com | WE-TPC Type S, M, MH                                                                      |

#### **Output and Input Capacitor Selection**

When selecting output capacitors for large pulsed loads, the magnitude and duration of the pulse current, together with the droop voltage specification, determine the choice of the output capacitor. Both the ESR of the capacitor and the charge stored in the capacitor each cycle contribute to the output voltage droop. The droop due to the charge is approximately:

$$V_{DROOP\_LOAD} = \frac{\left[I_{PULSE} - \left(\frac{V_{IN} \bullet I_{IN(MAX)} \bullet \eta}{V_{OUT}} - I_{STANDBY}\right)\right] \bullet D \bullet T}{(V)}$$

where

I<sub>PULSE</sub> = pulsed load current

I<sub>STANDBY</sub> = static load current in standby mode

$I_{IN(MAX)}$  = programmed input current limit in amps

T = period of the load pulse

D = load pulse's duty cycle

$V_{DROOP}$  = amount the output falls out of regulation in volts  $\eta$  = the efficiency of the converter at the input current limit point

The preceding equation is a worst-case approximation assuming all the pulsing energy comes from the output capacitor.

The droop due to the capacitor equivalent series resistance (ESR) is:

$$V_{DROOP\_ESR}$$

$$= \left[ I_{PULSE} - \left( \frac{V_{IN} \bullet I_{IN(MAX)} \bullet \eta}{V_{OUT}} - I_{STANDBY} \right) \right] \bullet ESR (V)$$

Low ESR and high capacitance are critical to maintaining low output droop. Table 2 and the Typical Applications schematics show a list of several reservoir capacitor manufacturers.

The total output voltage droop is given by:

$$V_{DROOP} = V_{DROOP LOAD} + V_{DROOP ESR}$$

(V)

High capacitance values and low ESR can lead to instability in typical internally compensated buck-boost converters. Using proportional compensation, the LTC3127 is stable with low ESR output capacitor values greater than 1000uF.

Multilayer ceramic capacitors are an excellent choice for input decoupling of the step-up converter as they have extremely low ESR and are available in small footprints. Input capacitors should be located as close as possible to the device. While a  $10\mu F$  input capacitor is sufficient for most applications, larger values may be used to improve input decoupling without limitation. Consult the manufacturers directly for detailed information on their selection of ceramic capacitors. Although ceramic capacitors are recommended, low ESR tantalum capacitors may be used as well.

When using a large capacitance to help with pulsed load applications, the maximum load for a given duty cycle, and the minimum capacitance can be calculated by:

$$I_{LOAD(MAX)} = \frac{V_{IN} \bullet I_{IN(MAX)} \bullet \eta}{D \bullet V_{OUT}} (A)$$

$$C_{OUT(MIN)} =$$

$$\left[I_{PULSE} - \left(\frac{V_{IN} \bullet I_{IN(MAX)} \bullet \eta}{V_{OUT}} - I_{STANDBY}\right)\right]$$

•

$$\frac{D \cdot T}{V_{DROOP}}$$

(F)

**Table 2. Capacitor Vendor Information**

| SUPPLIER        | PHONE        | WEB SITE               |

|-----------------|--------------|------------------------|

| Vishay          | 402-563-6866 | www.vishay.com         |

| AVX             | 803-448-9411 | www.avxcorp.com        |

| Cooper Bussmann | 516-998-4100 | www.cooperbussmann.com |

| CAP-XX          | 843-267-0720 | www.cap-xx.com         |

| Panasonic       | 800-394-2112 | www.panasonic.com      |

#### **Capacitor Selection Example**

In this example, a pulsed load application requires that  $V_{OUT}$  droops less than 300mV. The application is a Li-Ion battery input to a 3.6V output. The pulsed load is a no-load to a 1.5A step with a frequency of 217Hz and a duty cycle of 12.5%. The input current limit is set to 500mA. In order to meet the 300mV droop requirement, the amount of capacitance must be calculated at the highest  $V_{IN}$  to  $V_{OUT}$  step-up ratio. All of the following calculations assume a minimum  $V_{IN}$  of 3V and an efficiency of 90%.

Given the application, the following is known:

$$V_{INI} = 3V$$

$$V_{OUT} = 3.6V$$

$$I_{IN(MAX)} = 500 \text{mA}$$

$$I_{PIII,SF} = 1.5A$$

$$I_{STANDBY} = 0A$$

$$\eta = 0.9$$

$$D = 0.125$$

$$T = 1/217Hz = 4.6ms$$

$$V_{DROOP} = 300 \text{mV}$$

**Step 1:** Check to make sure the application can provide enough current to recover from the pulsed load using the  $I_{LOAD(MAX)}$  equation:

$$I_{LOAD(MAX)} = \frac{3V \cdot 500mA \cdot 0.9}{0.125 \cdot 3.6V} = 3A$$

The maximum load that can be pulsed at this  $V_{\text{IN}}$  to  $V_{\text{OUT}}$  combination is 3A.

**Step 2:** Calculate the minimum output capacitance required.

$$C_{OUT(MIN)} \ge \left(1.5A - \frac{3V \cdot 500\text{mA} \cdot 0.9}{3.6V}\right)$$

$$\cdot \frac{0.125 \cdot 4.6\text{ms}}{300\text{mV}} = 2.15\text{mF}$$

**Step 3:** For this application a 2.2mF Vishay Tantamount tantalum, low ESR capacitor is selected. This capacitor has a maximum ESR of  $0.04\Omega$ . With the selected capacitor, the amount of droop must be calculated:

$$V_{DROOP\_LOAD} = \frac{\left[1.5A - \left(\frac{3V \cdot 500mA \cdot 0.9}{3.6V} - 0A\right)\right] \cdot 0.125 \cdot 4.6ms}{2.2mF}$$

$$V_{DROOP\_ESR} =$$

$$\left[ 1.5A - \left( \frac{3V \cdot 500mA \cdot 0.9}{3.6V} - 0A \right) \right] \cdot 0.04\Omega$$

$$= 0.045V$$

=0.294V

$$V_{DROOP} = V_{DROOP\_LOAD} + V_{DROOP\_ESR} = 0.339V$$

Due to the ESR of the capacitor, the total droop is greater than 300mV. In this case, if the higher droop cannot be accepted, a larger valued, lower ESR capacitor can be selected.

#### **PCB Layout Considerations**

The LTC3127 switches large currents at high frequencies. Special care should be given to the PCB layout to ensure stable, noise-free operation. Figure 4 depicts the recommended PCB layout to be utilized for the LTC3127. A few key guidelines follow:

- 1. All circulating high current paths should be kept as short as possible. This can be accomplished by keeping the routes to all bold components in Figure 4 as short and as wide as possible. Capacitor ground connections should via down to the ground plane in the shortest route possible. The bypass capacitor on  $V_{\text{IN}}$  should be placed as close to the IC as possible and should have the shortest possible path to ground.

- 2. The small-signal ground pad (SGND) should have a single point connection to the power ground. A con-

- venient way to achieve this is to short the pin directly to the Exposed Pad as shown in Figure 4.

- 3. The components shown in bold and their connections should all be placed over a complete ground plane.

- 4. To prevent large circulating currents from disrupting the output voltage sensing, the ground for the resistor divider and R<sub>PROG</sub> should be returned directly to the small signal ground pin (SGND).

- 5. Use of vias in the die attach pad will enhance the thermal environment of the converter especially if the vias extend to a ground plane region on the exposed bottom surface of the PCB.

- Keep the connections to the FB and PROG pins as short as possible and away from the switch pin connections.

Figure 4. Recommended PCB Layout

# TYPICAL APPLICATIONS

#### USB (500mA Max), 3.8V GSM Pulsed Load

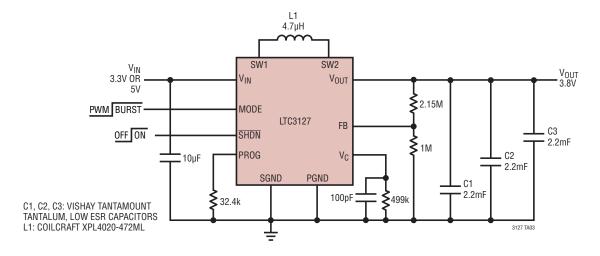

#### PCMCIA/Compact Flash (3.3V or 5V/500mA Max), 3.8V GPRS, Class 10 Pulsed Load

# TYPICAL APPLICATIONS

#### Stacked Supercapacitor Charger (1000mA Max Input Current)

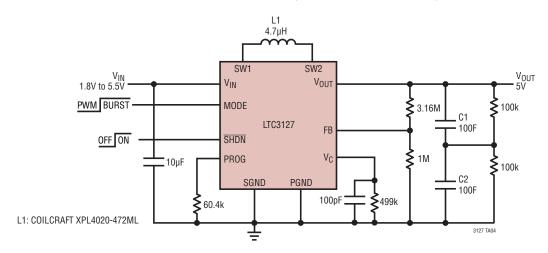

#### General Purpose Forced Continuous Conduction Application with 500µs Start-Up

# PACKAGE DESCRIPTION

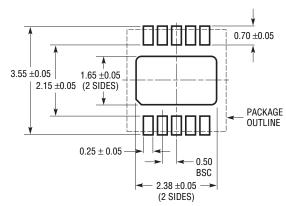

#### **DD Package** 10-Lead Plastic DFN (3mm × 3mm)

(Reference LTC DWG # 05-08-1699 Rev B)

- 1. DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE MO-229 VARIATION OF (WEED-2).

CHECK THE LTC WEBSITE DATA SHEET FOR CURRENT STATUS OF VARIATION ASSIGNMENT

2. DRAWING NOT TO SCALE

NOTE:

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- A. DIMENSIONS ARE IN MICEINICITIES

DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH, MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

# PACKAGE DESCRIPTION

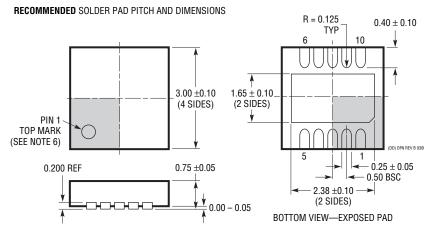

#### MSE Package 12-Lead Plastic MSOP, Exposed Die Pad

(Reference LTC DWG # 05-08-1666 Rev B)

- DHAWING NOT TO SCALEDIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

# TYPICAL APPLICATION

#### Single Supercapacitor Charger (1000mA Max Input Current)

# **RELATED PARTS**

| PART NUMBER                     | DESCRIPTION                                                                                              | COMMENTS                                                                                                                                                                          |

|---------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC3101                         | Wide V <sub>IN</sub> , 1MHz Multioutput DC/DC Converter and PowerPath™ Controller                        | 95% Efficiency, V <sub>IN</sub> : 1.8V to 5.5V, V <sub>OUT(MAX)</sub> : 1.8V to 5.25V, I <sub>Q</sub> = 35 $\mu$ A, I <sub>SD</sub> < 1 $\mu$ A, 4mm × 4mm QFN-24 Package         |

| LTC3125                         | 1.2A I <sub>OUT</sub> , 1.6MHz, Synchronous Boost DC/DC<br>Converter With Adjustable Input Current Limit | 94% Efficiency, V <sub>IN</sub> : 1.8V to 5.5V, V <sub>OUT(MAX)</sub> = 5.25V, I <sub>Q</sub> = 15 $\mu$ A, I <sub>SD</sub> < 1 $\mu$ A, 2mm × 3mm DFN-8 Package                  |

| LTC3606B                        | 800mA I <sub>OUT</sub> , Synchronous Step-Down DC/DC<br>Converter with Average Input Current Limit       | 95% Efficiency, V <sub>IN</sub> : 2.5V to 5.5V, V <sub>OUT(MAX)</sub> = 0.6V, I <sub>Q</sub> = 420 $\mu$ A, I <sub>SD</sub> < 1 $\mu$ A, 3mm × 3mm DFN-8 Package                  |

| LTC3440                         | 600mA I <sub>OUT</sub> , 2MHz, Synchronous Buck-Boost<br>DC/DC Converter                                 | 95% Efficiency, $V_{IN}$ : 2.5V to 5.5V, $V_{OUT}$ : 2.5V to 5.5V, $I_Q$ = 25 $\mu$ A, $I_{SD}$ < 1 $\mu$ A, 3mm $\times$ 3mm DFN-10 and MSOP-10 Packages                         |

| LTC3441/LTC3441-2/<br>LTC3441-3 | 1.2A I <sub>OUT</sub> , 2MHz, Synchronous Buck-Boost DC/DC Converter                                     | 95% Efficiency, V <sub>IN</sub> : 2.4V to 5.5V, V <sub>OUT</sub> : 2.4V to 5.25V, I <sub>Q</sub> = 50 $\mu$ A, I <sub>SD</sub> < 1 $\mu$ A, 3mm × 4mm DFN-12 Package              |

| LTC3520                         | 1A 2MHz, Synchronous Buck-Boost and 600mA<br>Buck Converter                                              | 95% Efficiency, V <sub>IN</sub> : 2.2V to 5.5V, V <sub>OUT(MAX)</sub> = 5.25V, I <sub>Q</sub> = 55 $\mu$ A, I <sub>SD</sub> < 1 $\mu$ A, 4mm × 4mm QFN-24 Package                 |

| LTC3530                         | 600mA I <sub>OUT</sub> , 2MHz, Synchronous Buck-Boost DC/DC Converter                                    | 95% Efficiency, V <sub>IN</sub> : 1.8V to 5.5V, V <sub>OUT</sub> : 1.8V to 5.25V, I <sub>Q</sub> = 40 $\mu$ A, I <sub>SD</sub> < 1 $\mu$ A, 3mm × 3mm DFN-10 and MSOP-10 Packages |

| LTC3532                         | 500mA I <sub>OUT</sub> , 2MHz, Synchronous Buck-Boost<br>DC/DC Converter                                 | 95% Efficiency, V <sub>IN</sub> : 2.4V to 5.5V, V <sub>OUT</sub> : 2.4V to 5.25V, I <sub>Q</sub> = 35 $\mu$ A, I <sub>SD</sub> < 1 $\mu$ A, 3mm × 3mm DFN-10 and MSOP-10 Packages |

| LTC3533                         | 2A I <sub>OUT</sub> , 2MHz, Synchronous Buck-Boost DC/DC Converter                                       | 95% Efficiency, $V_{IN}$ : 1.8V to 5.5V, $V_{OUT}$ : 1.8V to 5.25V, $I_Q$ = 40 $\mu$ A, $I_{SD}$ < 1 $\mu$ A, 3mm × 4mm DFN-14 Package                                            |

| LTC3538                         | 800mA I <sub>OUT</sub> , 1MHz, Synchronous Buck-Boost<br>DC/DC Converter                                 | 95% Efficiency, $V_{IN}$ : 2.4V to 5.5V, $V_{OUT}$ : 1.8V to 5.25V, $I_Q$ = 35 $\mu$ A, $I_{SD}$ < 1 $\mu$ A, 2mm $\times$ 3mm DFN-8 Package                                      |

| LTC3534                         | 500mA I <sub>OUT</sub> , 1MHz, Synchronous Buck-Boost<br>DC/DC Converter                                 | 95% Efficiency, $V_{IN}$ : 2.4V to 7V, $V_{OUT}$ : 1.8V to 2V, $I_Q$ = 25 $\mu$ A, $I_{SD}$ < 1 $\mu$ A, 3mm $\times$ 3mm DFN-16 and SSOP-16 Packages                             |