February 2008

# 74LCX574 Low Voltage Octal D-Type Flip-Flop with 5V Tolerant Inputs and Outputs

#### **Features**

- 5V tolerant inputs and outputs

- 2.3V-3.6V V<sub>CC</sub> specifications provided

- 7.5ns  $t_{PD}$  max.  $(V_{CC} = 3.3V)$ ,  $10\mu A I_{CC}$  max.

- Power down high impedance inputs and outputs

- Supports live insertion/withdrawal<sup>(1)</sup>

- $\pm 24$ mA output drive ( $V_{CC} = 3.0$ V)

- Implements proprietary noise/EMI reduction circuitry

- Latch-up performance exceeds JEDEC 78 conditions

- ESD performance

- Human body model > 2000V

- Machine model > 200V

#### Note:

To ensure the high impedance state during power up or down, OE should be tied to V<sub>CC</sub> through a pull-up resistor: the minimum value of the resistor is determined by the current-sourcing capability of the driver.

# **General Description**

The LCX574 is a high-speed, low power octal flip-flop with a buffered common Clock (CP) and a buffered common Output Enable  $(\overline{OE})$ . The information presented to the D inputs is stored in the flip-flops on the LOW-to-HIGH Clock (CP) transition.

The LCX574 is functionally identical to the LCX374 except for the pinouts.

The LCX574 is designed for low voltage applications with capability of interfacing to a 5V signal environment. The LCX574 is fabricated with an advanced CMOS technology to achieve high speed operation while maintaining CMOS low power dissipation.

# **Ordering Information**

| Order<br>Number            | Package<br>Number | Package Description                                                                         |

|----------------------------|-------------------|---------------------------------------------------------------------------------------------|

| 74LCX574WM                 | M20B              | 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide                  |

| 74LCX574SJ                 | M20D              | 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide                               |

| 74LCX574BQX <sup>(2)</sup> | MLP20B            | 20-Terminal Depopulated Quad Very-Thin Flat Pack No Leads (DQFN), JEDEC MO-241, 2.5 x 4.5mm |

| 74LCX574MSA                | MSA20             | 20-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm Wide                       |

| 74LCX574MTC                | MTC20             | 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide                 |

#### Note:

2. DQFN package available in Tape and Reel only.

Device also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering number.

All packages are lead free per JEDEC: J-STD-020B standard.

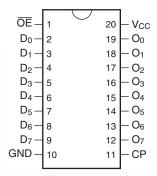

### **Connection Diagrams**

Pin Assignments for SOIC, SOP, SSOP, TSSOP

#### Pad Assignments for DQFN

(Top View)

# **Pin Descriptions**

| Pin Names Description          |                             |  |  |  |

|--------------------------------|-----------------------------|--|--|--|

| D <sub>0</sub> –D <sub>7</sub> | Data Inputs                 |  |  |  |

| СР                             | Clock Pulse Input           |  |  |  |

| ŌĒ                             | 3-STATE Output Enable Input |  |  |  |

| O <sub>0</sub> -O <sub>7</sub> | 3-STATE Outputs             |  |  |  |

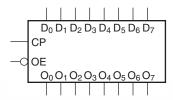

# **Logic Symbol**

#### **Truth Table**

| Ir | puts | ; | Internal | Outputs        |                   |

|----|------|---|----------|----------------|-------------------|

| ŌĒ | СР   | D | Q        | O <sub>n</sub> | Function          |

| Н  | Н    | L | NC       | Z              | Hold              |

| Н  | Н    | Н | NC       | Z              | Hold              |

| Н  | ~    | L | Н        | Z              | Load              |

| Н  | ~    | Н | L        | Z              | Load              |

| L  | ~    | L | Н        | L              | Data Available    |

| L  | ~    | Н | L        | Н              | Data Available    |

| L  | Н    | L | NC       | NC             | No Change in Data |

| L  | Н    | Н | NC       | NC             | No Change in Data |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = High Impedance

✓ = LOW-to-HIGH Transition

NC = No Change

# **Functional Description**

The LCX574 consists of eight edge-triggered flip-flops with individual D-type inputs and 3-STATE true outputs. The buffered clock and buffered Output Enable are common to all flip-flops. The eight flip-flops will store the state of their individual D inputs that meet the setup and hold time requirements on the LOW-to-HIGH Clock (CP) transition. With the Output Enable  $(\overline{\text{OE}})$  LOW, the contents of the eight flip-flops are available at the outputs. When  $\overline{\text{OE}}$  is HIGH, the outputs go to the high impedance state. Operation of the  $\overline{\text{OE}}$  input does not affect the loading of the flip-flops.

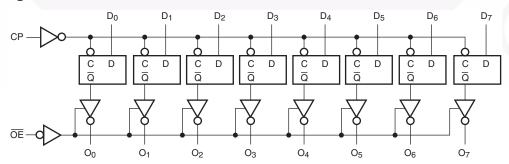

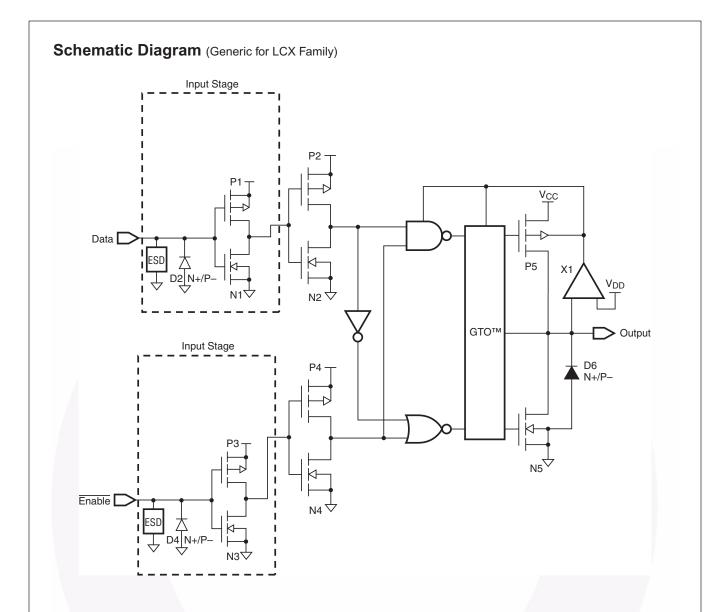

# **Logic Diagram**

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                        | Conditions                                 | Value                    | Units |

|------------------|----------------------------------|--------------------------------------------|--------------------------|-------|

| V <sub>CC</sub>  | Supply Voltage                   |                                            | -0.5 to +7.0             | V     |

| V <sub>I</sub>   | DC Input Voltage                 |                                            | -0.5 to +7.0             | V     |

| Vo               | DC Output Voltage                | Output in 3-STATE                          | -0.5 to +7.0             | V     |

|                  |                                  | Output in HIGH or LOW State <sup>(3)</sup> | $-0.5$ to $V_{CC} + 0.5$ |       |

| I <sub>IK</sub>  | DC Input Diode Current           | V <sub>I</sub> < GND                       | -50                      | mA    |

| I <sub>OK</sub>  | DC Output Diode Current          | V <sub>O</sub> < GND                       | -50                      | mA    |

|                  |                                  | $V_O > V_{CC}$                             | +50                      |       |

| Io               | DC Output Source/Sink Current    |                                            | ±50                      | mA    |

| I <sub>CC</sub>  | DC Supply Current per Supply Pin |                                            | ±100                     | mA    |

| I <sub>GND</sub> | DC Ground Current per Ground Pin |                                            | ±100                     | mA    |

| T <sub>STG</sub> | Storage Temperature              |                                            | -65 to +150              | °C    |

# Recommended Operating Conditions<sup>(4)</sup>

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol                           | Parameter                      | Conditions                            | Min. | Max.            | Units |

|----------------------------------|--------------------------------|---------------------------------------|------|-----------------|-------|

| V <sub>CC</sub>                  | Supply Voltage                 | Operating                             | 2.0  | 3.6             | V     |

|                                  |                                | Data Retention                        | 1.5  | 3.6             |       |

| V <sub>I</sub>                   | Input Voltage                  |                                       | 0    | 5.5             | V     |

| V <sub>O</sub>                   | Output Voltage                 | HIGH or LOW State                     | 0    | V <sub>CC</sub> | V     |

|                                  |                                | 3-STATE                               | 0    | 5.5             |       |

| I <sub>OH</sub> /I <sub>OL</sub> | Output Current                 | $V_{CC} = 3.0V - 3.6V$                |      | ±24             | mA    |

|                                  |                                | $V_{CC} = 2.7V - 3.0V$                |      | ±12             |       |

|                                  |                                | $V_{CC} = 2.3V - 2.7V$                | /    | ±8              |       |

| T <sub>A</sub>                   | Free-Air Operating Temperature |                                       | -40  | 85              | °C    |

| $\Delta t/\Delta V$              | Input Edge Rate                | $V_{IN} = 0.8V - 2.0V, V_{CC} = 3.0V$ | 0    | 10              | ns/V  |

#### Notes:

- 3. I<sub>O</sub> Absolute Maximum Rating must be observed.

- 4. Unused inputs must be held HIGH or LOW. They may not float.

#### **DC Electrical Characteristics**

|                  |                                       |                     |                                                   | $T_A = -40^{\circ}C$  | to +85°C |       |

|------------------|---------------------------------------|---------------------|---------------------------------------------------|-----------------------|----------|-------|

| Symbol           | Parameter                             | V <sub>CC</sub> (V) | Conditions                                        | Min.                  | Max.     | Units |

| V <sub>IH</sub>  | HIGH Level Input Voltage              | 2.3–2.7             |                                                   | 1.7                   |          | V     |

|                  |                                       | 2.7–3.6             |                                                   | 2.0                   |          |       |

| V <sub>IL</sub>  | LOW Level Input Voltage               | 2.3–2.7             |                                                   |                       | 0.7      | V     |

|                  |                                       | 2.7–3.6             |                                                   |                       | 0.8      |       |

| V <sub>OH</sub>  | HIGH Level Output Voltage             | 2.3-3.6             | $I_{OH} = -100 \mu A$                             | V <sub>CC</sub> - 0.2 |          | V     |

|                  |                                       | 2.3                 | $I_{OH} = -8mA$                                   | 1.8                   |          |       |

|                  |                                       | 2.7                 | $I_{OH} = -12mA$                                  | 2.2                   |          |       |

|                  |                                       | 3.0                 | $I_{OH} = -18mA$                                  | 2.4                   |          |       |

|                  |                                       |                     | $I_{OH} = -24mA$                                  | 2.2                   |          |       |

| V <sub>OL</sub>  | LOW Level Output Voltage              | 2.3-3.6             | $I_{OL} = 100 \mu A$                              |                       | 0.2      | V     |

|                  |                                       | 2.3                 | $I_{OL} = 8mA$                                    |                       | 0.6      |       |

|                  |                                       | 2.7                 | I <sub>OL</sub> = 12mA                            |                       | 0.4      |       |

|                  |                                       | 3.0                 | $I_{OL} = 16mA$                                   |                       | 0.4      |       |

|                  |                                       |                     | $I_{OL} = 24mA$                                   |                       | 0.55     |       |

| I <sub>I</sub>   | Input Leakage Current                 | 2.3-3.6             | $0 \le V_I \le 5.5V$                              |                       | ±5.0     | μA    |

| l <sub>OZ</sub>  | 3-STATE Output Leakage                | 2.3–3.6             | $0 \le V_O \le 5.5V$ , $V_I = V_{IH}$ or $V_{IL}$ |                       | ±5.0     | μA    |

| I <sub>OFF</sub> | Power-Off Leakage Current             | 0                   | $V_I$ or $V_O = 5.5V$                             |                       | 10       | μA    |

| I <sub>CC</sub>  | Quiescent Supply Current              | 2.3–3.6             | $V_I = V_{CC}$ or GND                             |                       | 10       | μA    |

|                  |                                       | 2.3–3.6             | $3.6V \le V_I, V_O \le 5.5V^{(5)}$                |                       | ±10      |       |

| $\Delta I_{CC}$  | Increase in I <sub>CC</sub> per Input | 2.3-3.6             | $V_{IH} = V_{CC} - 0.6V$                          |                       | 500      | μΑ    |

## **AC Electrical Characteristics**

|                                     |                                            | $T_A = -40^{\circ}C$ to +85°C, $R_L = 500\Omega$ |                    |                                                  |      |                                                                                        |      |       |

|-------------------------------------|--------------------------------------------|--------------------------------------------------|--------------------|--------------------------------------------------|------|----------------------------------------------------------------------------------------|------|-------|

|                                     |                                            |                                                  | 3V ± 0.3V,<br>50pF | V <sub>CC</sub> = 2.7V,<br>C <sub>L</sub> = 50pF |      | $\begin{aligned} V_{CC} &= 2.5 \pm 0.2 \text{V}, \\ C_L &= 30 \text{pF} \end{aligned}$ |      |       |

| Symbol                              | Parameter                                  | Min.                                             | Max.               | Min.                                             | Max. | Min.                                                                                   | Max. | Units |

| f <sub>MAX</sub>                    | Maximum Clock Frequency                    | 150                                              |                    |                                                  |      |                                                                                        |      | MHz   |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation Delay,<br>CP to O <sub>n</sub> | 1.5                                              | 8.5                | 1.5                                              | 9.5  | 1.5                                                                                    | 10.5 | ns    |

| t <sub>PZL</sub> , t <sub>PZH</sub> | Output Enable Time                         | 1.5                                              | 8.5                | 1.5                                              | 9.5  | 1.5                                                                                    | 10.5 | ns    |

| t <sub>PLZ</sub> , t <sub>PHZ</sub> | Output Disable Time                        | 1.5                                              | 6.5                | 1.5                                              | 7.0  | 1.5                                                                                    | 7.8  | ns    |

| t <sub>S</sub>                      | Setup Time                                 | 2.5                                              |                    | 2.5                                              |      | 4.0                                                                                    |      | ns    |

| t <sub>H</sub>                      | Hold Time                                  | 1.5                                              |                    | 1.5                                              |      | 2.0                                                                                    |      | ns    |

| t <sub>W</sub>                      | Pulse Width                                | 3.3                                              |                    | 3.3                                              |      | 4.0                                                                                    |      | ns    |

| toshL, toshH                        | Output to Output Skew <sup>(6)</sup>       |                                                  | 1.0                |                                                  |      |                                                                                        |      | ns    |

#### Notes:

- 5. Outputs disabled or 3-STATE only.

- 6. Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (t<sub>OSHL</sub>) or LOW-to-HIGH (t<sub>OSLH</sub>).

# **Dynamic Switching Characteristics**

|                  |                                             |                     |                                             | $T_A = 25^{\circ}C$ |       |

|------------------|---------------------------------------------|---------------------|---------------------------------------------|---------------------|-------|

| Symbol           | Parameter                                   | V <sub>CC</sub> (V) | Conditions                                  | Typical             | Units |

| V <sub>OLP</sub> | Quiet Output Dynamic Peak V <sub>OL</sub>   | 3.3                 | $C_L = 50 pF, V_{IH} = 3.3 V, V_{IL} = 0 V$ | 0.8                 | V     |

|                  |                                             | 2.5                 | $C_L = 30pF, V_{IH} = 2.5V, V_{IL} = 0V$    | 0.6                 |       |

| V <sub>OLV</sub> | Quiet Output Dynamic Valley V <sub>OL</sub> | 3.3                 | $C_L = 50pF, V_{IH} = 3.3V, V_{IL} = 0V$    | -0.8                | V     |

|                  |                                             | 2.5                 | $C_L = 30pF, V_{IH} = 2.5V, V_{IL} = 0V$    | -0.6                |       |

# Capacitance

| Symbol           | Parameter                     | Conditions                                                | Typical | Units |

|------------------|-------------------------------|-----------------------------------------------------------|---------|-------|

| C <sub>IN</sub>  | Input Capacitance             | $V_{CC} = Open, V_I = 0V \text{ or } V_{CC}$              | 7       | pF    |

| C <sub>OUT</sub> | Output Capacitance            | $V_{CC} = 3.3V, V_{I} = 0V \text{ or } V_{CC}$            | 8       | pF    |

| C <sub>PD</sub>  | Power Dissipation Capacitance | $V_{CC} = 3.3V, V_{I} = 0V \text{ or } V_{CC}, f = 10MHz$ | 25      | pF    |

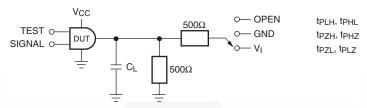

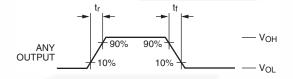

# AC Loading and Waveforms (Generic for LCX Family)

Figure 1. AC Test Circuit (C<sub>L</sub> includes probe and jig capacitance)

| Test                                | Switch                                                                        |

|-------------------------------------|-------------------------------------------------------------------------------|

| t <sub>PLH</sub> , t <sub>PHL</sub> | Open                                                                          |

| t <sub>PZL</sub> , t <sub>PLZ</sub> | 6V at $V_{CC} = 3.3 \pm 0.3V$<br>$V_{CC} \times 2$ at $V_{CC} = 2.5 \pm 0.2V$ |

| t <sub>PZH</sub> , t <sub>PHZ</sub> | GND                                                                           |

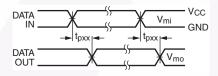

# Waveform for Inverting and Non-Inverting Functions

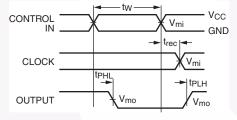

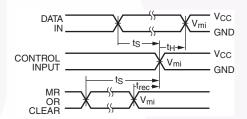

## Propagation Delay, Pulse Width and t<sub>rec</sub> Waveforms

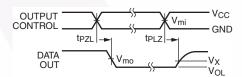

3-STATE Output Low Enable and Disable Times for Logic

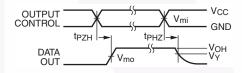

# 3-STATE Output High Enable and Disable Times for Logic

# Setup Time, Hold Time and Recovery Time for Logic

t<sub>rise</sub> and t<sub>fall</sub>

Figure 2. Waveforms (Input Characteristics; f = 1MHz,  $t_r = t_f = 3ns$ )

|                 | V <sub>CC</sub>        |                        |                         |  |

|-----------------|------------------------|------------------------|-------------------------|--|

| Symbol          | $3.3V \pm 0.3V$        | 2.7V                   | 2.5V ± 0.2V             |  |

| V <sub>mi</sub> | 1.5V                   | 1.5V                   | V <sub>CC</sub> /2      |  |

| V <sub>mo</sub> | 1.5V                   | 1.5V                   | V <sub>CC</sub> /2      |  |

| V <sub>x</sub>  | V <sub>OL</sub> + 0.3V | V <sub>OL</sub> + 0.3V | V <sub>OL</sub> + 0.15V |  |

| V <sub>y</sub>  | V <sub>OH</sub> – 0.3V | V <sub>OH</sub> – 0.3V | V <sub>OH</sub> – 0.15V |  |

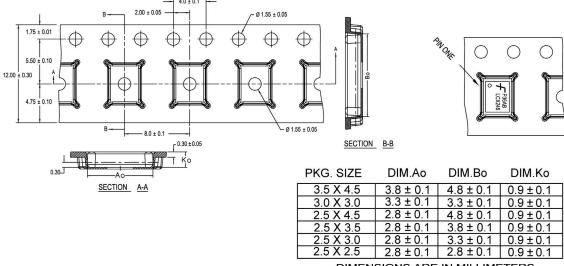

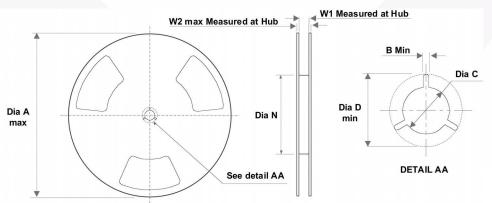

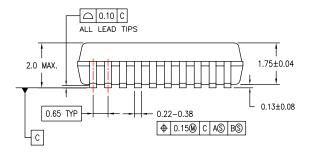

# **Tape and Reel Specification**

#### **Tape Format for DQFN**

| Package<br>Designator | Tape<br>Section    | Number<br>Cavities | Cavity<br>Status | Cover Tape<br>Status |

|-----------------------|--------------------|--------------------|------------------|----------------------|

| BQX                   | Leader (Start End) | 125 (typ)          | Empty            | Sealed               |

|                       | Carrier            | 3000               | Filled           | Sealed               |

|                       | Trailer (Hub End)  | 75 (typ)           | Empty            | Sealed               |

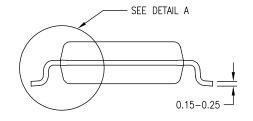

#### Tape Dimensions inches (millimeters)

#### DIMENSIONS ARE IN MILLIMETERS

#### NOTES: unless otherwise specified

- 1. Cummulative pitch for feeding holes and cavities (chip pockets) not to exceed 0.008[0.20] over 10 pitch span.

- 2. Smallest allowable bending radius.

- 3. Thru hole inside cavity is centered within cavity.

- 4. Tolerance is  $\pm 0.002[0.05]$  for these dimensions on all 12mm tapes.

- 5. Ao and Bo measured on a plane 0.120[0.30] above the bottom of the pocket.

- 6. Ko measured from a plane on the inside bottom of the pocket to the top surface of the carrier.

- 7. Pocket position relative to sprocket hole measured as true position of pocket. Not pocket hole.

- 8. Controlling dimension is millimeter. Diemension in inches rounded.

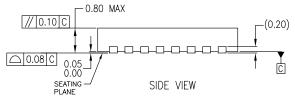

#### Reel Dimensions inches (millimeters)

| Tape Size | Α            | В            | С             | D             | N             | W1           | W2           |

|-----------|--------------|--------------|---------------|---------------|---------------|--------------|--------------|

| 12mm      | 13.0 (330.0) | 0.059 (1.50) | 0.512 (13.00) | 0.795 (20.20) | 2.165 (55.00) | 0.488 (12.4) | 0.724 (18.4) |

# **Physical Dimensions** 13.00 12.60 11.43 В 9.50 10.65 7.60 10.00 7.40 PIN ONE 0.35 INDICATOR **⊕** 0.25 **M** C B A LAND PATTERN RECOMMENDATION 2.65 MAX SEE DETAIL A 0.33 0.20 △ 0.10 C 0.30 0.10 0.75 SEATING PLANE NOTES: UNLESS OTHERWISE SPECIFIED (R0.10) A) THIS PACKAGE CONFORMS TO JEDEC GAGE PLANE MS-013, VARIATION AC, ISSUE E (R0.10) B) ALL DIMENSIONS ARE IN MILLIMETERS. 0.25 C) DIMENSIONS DO NOT INCLUDE MOLD FLASH OR BURRS. D) CONFORMS TO ASME Y14.5M-1994 0.40 SEATING PLANE E) LANDPATTERN STANDARD: SOIC127P1030X265-20L (1.40)DETAIL A F) DRAWING FILENAME: MKT-M20BREV3

Figure 3. 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

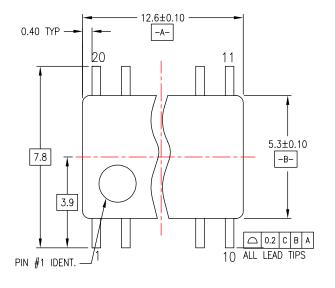

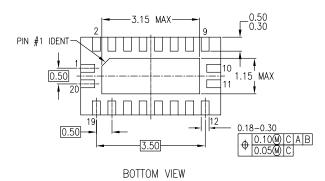

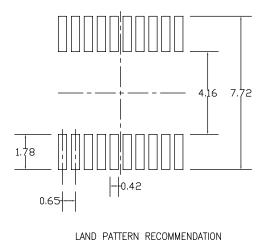

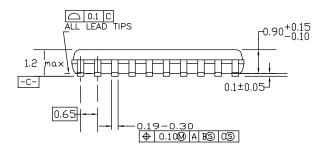

LAND PATTERN RECOMMENDATION

DIMENSIONS ARE IN MILLIMETERS

## NOTES:

- A. CONFORMS TO EIAJ EDR-7320 REGISTRATION, ESTABLISHED IN DECEMBER, 1998.

B. DIMENSIONS ARE IN MILLIMETERS.

C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS.

M20DREVC

Figure 4. 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/

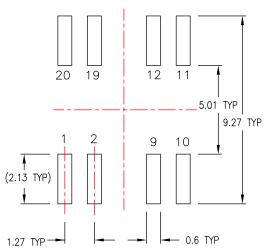

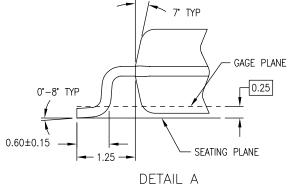

#### NOTES:

- A. CONFORMS TO JEDEC REGISTRATION MO-241, VARIATION AC

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994

MLP20BrevA

#### Figure 5. 20-Terminal Depopulated Quad Very-Thin Flat Pack No Leads (DQFN), JEDEC MO-241, 2.5 x 4.5mm

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

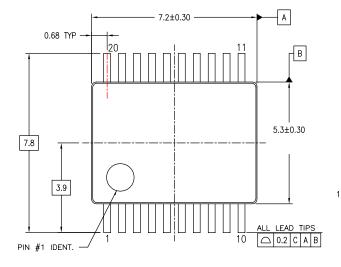

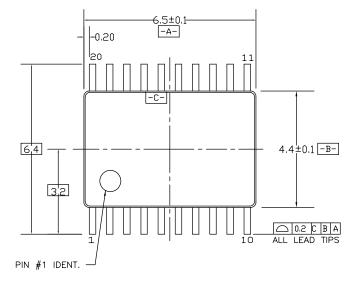

LAND PATTERN RECOMMENDATIONS

#### DIMENSIONS ARE IN MILLIMETERS

#### NOTES:

- A. CONFORMS TO JEDEC REGISTRATION MO-150, VARIATION AE, DATE 1/94.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS.

- D. DIMENSIONS AND TOLERANCES PER ASME Y14.5M 1994.

MSA20REVB

Figure 6. 20-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

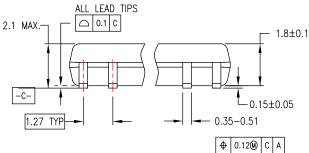

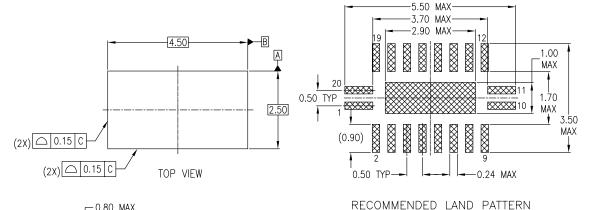

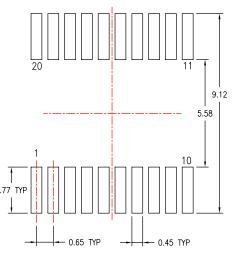

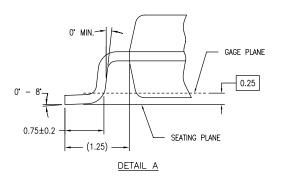

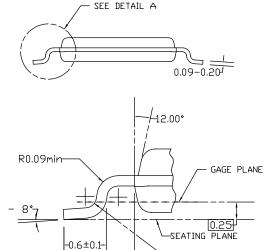

DIMENSIONS ARE IN MILLIMETERS

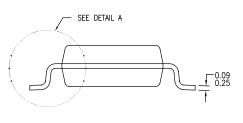

#### NOTES:

- A. CONFORMS TO JEDEC REGISTRATION MD-153, VARIATION AC, REF NOTE 6, DATE 7/93.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLDS FLASH, AND TIE BAR EXTRUSIONS.

- D. DIMENSIONS AND TOLERANCES PER ANSI Y14.5M, 1982.

DETAIL A

-1.00

R0.09min

#### MTC20REVD1

#### Figure 7. 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>

#### **TRADEMARKS**

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

ACEX®

Build it Now™

CorePLUS™

CROSSVOLT™

CTL™

Current Transfer Logic™ EcoSPARK<sup>®</sup> EZSWITCH™ \*

**E**7™ **F**®

Fairchild<sup>®</sup>

Fairchild Semiconductor<sup>®</sup>

FACT Quiet Series<sup>™</sup>

FACT<sup>®</sup>

FAST<sup>®</sup>

FastvCore<sup>™</sup>

FlashWriter<sup>® \*</sup>

FPS™ FRFET®

Global Power Resource<sup>sм</sup>

Green FPS™

Green FPS™e-Series™

GTO™

i-Lo™

IntelliMAX™

ISOPLANAR™

MegaBuck™

MICROCOUPLER™

MicroFET™

MicroPak™ MillerDrive™ Motion-SPM™ OPTOLOGIC® OPTOPLANAR® PDP-SPM™ Power220® POWEREDGE® Power-SPM™ PowerTrench®

Programmable Active Droop™

QFET<sup>®</sup> QS™

QT Optoelectronics™

Quiet Series™

RapidConfigure™

SMART START™

SPM®

STEALTH™

SuperFET™

SuperFOT™3

SuperSOT™6

SuperSOT™-8

Franchise

FinyBoost™

FinyBuck™

FinyLogic®

FinyLogic®

FinyOPTO™

FinyPower™

FinyPower™

FinyPwire™

FinyWire™

SerDes™

UHC®

FinyBoost

FinyBo

The Power Franchise®

SupreMOS™

SyncFET™

SYSTEM®

GENERAL

Ultra FRFET™ UniFET™ VCX™

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification | Product Status         | Definition                                                                                                                                                                                               |  |  |  |

|--------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Advance Information      | Formative or In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |  |  |

| Preliminary              | First Production       | This datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |  |

| No Identification Needed | Full Production        | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |  |  |  |

| Obsolete                 | Not In Production      | This datasheet contains specifications on a product that has been discontinued by Fairchild Semiconductor. The datasheet is printed for reference information only.                                      |  |  |  |

Rev. I33

<sup>\*</sup> EZSWITCH™ and FlashWriter® are trademarks of System General Corporation, used under license by Fairchild Semiconductor.