# SmartLEWIS<sup>TM</sup> TRX

TDA5340

High Sensitivity Multi-Channel Transceiver

# **Data Sheet**

Revision 1.2, 13.06.2012

Wireless Sense & Control

Edition 13.06.2012

Published by Infineon Technologies AG 81726 Munich, Germany © 2012 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

## **Warnings**

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Revision History |                                                                                         |  |  |  |

|------------------|-----------------------------------------------------------------------------------------|--|--|--|

| Page or Item     | e or Item Subjects (major changes since previous revisions)                             |  |  |  |

| Revision 1.2, 1  | 3.06.2012                                                                               |  |  |  |

| Page 62          | Package Outline Information added                                                       |  |  |  |

| Revision 1.1, 3  | 0.05.2012                                                                               |  |  |  |

| Page 40          | Page 40 Voltage at PA Pin changed to Peak Voltage at pin RFOUT with max 10% TX Duty Cyc |  |  |  |

| Page 40          | Inserted maximum Peak Voltage at pin RFOUT with TX Duty Cycle above 10%                 |  |  |  |

| Page 40          | Inserted maximum DC Voltage at pin RFOUT                                                |  |  |  |

| Page 54          | Inserted Definition for reception parameters                                            |  |  |  |

|                  |                                                                                         |  |  |  |

|                  |                                                                                         |  |  |  |

|                  |                                                                                         |  |  |  |

# **Trademarks of Infineon Technologies AG**

AURIX $^{\text{TM}}$ , C166 $^{\text{TM}}$ , Canpak $^{\text{TM}}$ , CIPOS $^{\text{TM}}$ , CIPURSE $^{\text{TM}}$ , EconoPack $^{\text{TM}}$ , CoolMos $^{\text{TM}}$ , CoolSet $^{\text{TM}}$ , CORECONTROL $^{\text{TM}}$ , CROSSAVE $^{\text{TM}}$ , DAVE $^{\text{TM}}$ , EasyPIM $^{\text{TM}}$ , EconoBRIDGE $^{\text{TM}}$ , EconoDUAL $^{\text{TM}}$ , EconoPIM $^{\text{TM}}$ , EiceDRIVER $^{\text{TM}}$ , eupec $^{\text{TM}}$ , FCOS $^{\text{TM}}$ , HITFET $^{\text{TM}}$ , HybridPack $^{\text{TM}}$ , ISOFACE $^{\text{TM}}$ , IsoPack $^{\text{TM}}$ , MiPaQ $^{\text{TM}}$ , ModSTACK $^{\text{TM}}$ , my-d $^{\text{TM}}$ , NovalithIC $^{\text{TM}}$ , OptiMoS $^{\text{TM}}$ , ORIGA $^{\text{TM}}$ , PRIMARION $^{\text{TM}}$ , PrimePack $^{\text{TM}}$ , PrimeSTACK $^{\text{TM}}$ , PRO-SIL $^{\text{TM}}$ , PROFET $^{\text{TM}}$ , RASIC $^{\text{TM}}$ , ReverSave $^{\text{TM}}$ , Satric $^{\text{TM}}$ , Sieget $^{\text{TM}}$ , Sindrion $^{\text{TM}}$ , Sipmos $^{\text{TM}}$ , SmartLewis $^{\text{TM}}$ , Solid Flash $^{\text{TM}}$ , Tempfet $^{\text{TM}}$ , thinQ! $^{\text{TM}}$ , Trenchstop $^{\text{TM}}$ , TriCore $^{\text{TM}}$ .

#### **Other Trademarks**

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™, PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. AUTOSAR™ is licensed by AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hilgraeve Incorporated. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. Mifare™ of NXP. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2011-02-24

# **Table of Contents**

# **Table of Contents**

|                   | Table of Contents                                       | 4   |

|-------------------|---------------------------------------------------------|-----|

|                   | List of Figures                                         | 6   |

|                   | List of Tables                                          | 7   |

| 1                 | Product Description                                     | . 8 |

| 1.1               | Overview                                                | 8   |

| 1.2               | Key Features                                            | 9   |

| 1.3               | Target Applications                                     | 9   |

| 1.4               | Application Example                                     | 10  |

| 2                 | Functional Overview                                     | 12  |

| 2.1               | Pin Configuration                                       |     |

| 2.1.1             | Pin Definition                                          |     |

| 2.2               | Functional Block Diagram                                |     |

| 2.3               | Architecture Overview                                   |     |

| 2.4               | Block Overview                                          |     |

| 2.5               | Operating Modes                                         |     |

| 2.6               | Block Description                                       |     |

| 2.6.1             | Power Supply Circuitry                                  |     |

| 2.6.2             | Chip Reset                                              |     |

| 2.6.3             | RF / IF Receiver                                        |     |

| 2.6.4             | Transmitter                                             |     |

| 2.6.5             | Crystal Oscillator and Clock Divider                    |     |

| 2.6.6             | Sigma-Delta Fractional-N PLL Block                      |     |

| 2.6.6.1           | PLL Dividers                                            |     |

| 2.6.6.2           | Digital Modulator                                       |     |

| 2.6.7             | Decoding/Encoding Modes                                 |     |

| 2.6.8             | ASK and FSK Demodulator                                 |     |

| 2.6.8.1           | ASK Demodulator                                         |     |

| 2.6.8.2           | FSK Demodulator                                         |     |

| 2.6.8.3           | Automatic Frequency Control Unit (AFC)                  |     |

| 2.6.8.4           | Digital Automatic Gain Control Unit (AGC)               |     |

| 2.6.8.5           | Digital Baseband (DBB) Receiver                         |     |

| 2.6.8.6           | Clock and Data Recovery (CDR)                           |     |

| 2.6.8.7           | Wake-Up Generator                                       |     |

| 2.6.8.8           | Frame Synchronization                                   |     |

| 2.6.8.9           | Message ID Scanning                                     |     |

| 2.6.8.10<br>2.6.9 | RUNIN, Synchronization Search Time and Inter-Frame Time |     |

|                   | Application Interface                                   |     |

| 2.6.9.1           | Digital Control (4-wire SPI Bus)                        |     |

| 2.6.10            | Chip Serial Number                                      |     |

| 3                 | Reference                                               |     |

| 3.1               | Electrical Data                                         |     |

| 3.1.1             | Absolute Maximum Ratings                                |     |

| 3.1.2             | Operating Range                                         |     |

| 3.1.3             | AC/DC Characteristics                                   |     |

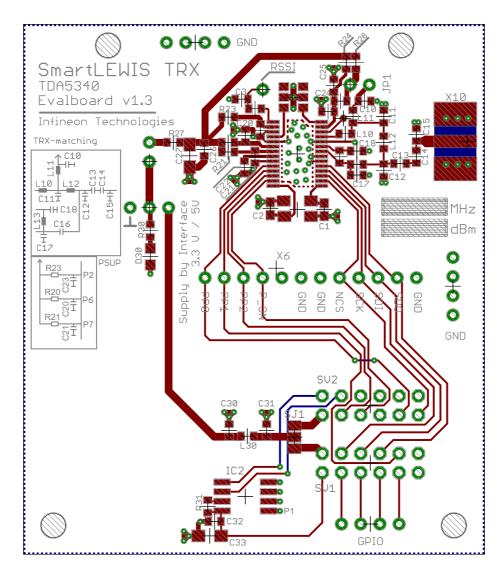

| 3.2               | Test Circuitry Evaluation Board V1.3                    |     |

| 3.3               | Test Board Layout, Evaluation Board V1.3                |     |

| 3.4               | Bill of Material                                        | 57  |

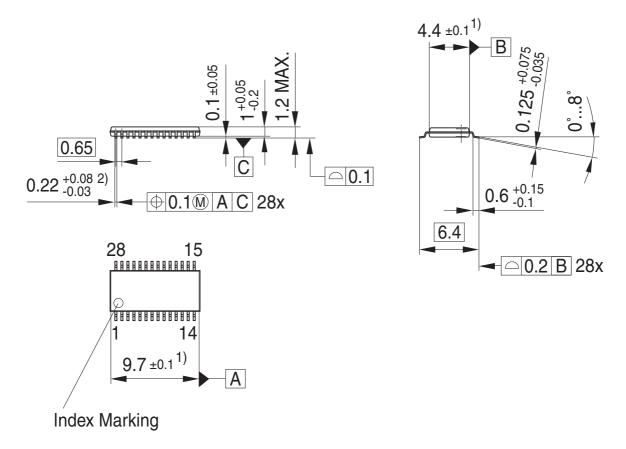

| 4 | Package Outlines |  | . 62 | 2 |

|---|------------------|--|------|---|

|---|------------------|--|------|---|

Data Sheet 5 Revision 1.2, 13.06.2012

# **List of Figures**

# **List of Figures**

| Figure 1  | Application Example optimized for System Costs (3V3 Supply)                   | 10 |

|-----------|-------------------------------------------------------------------------------|----|

| Figure 2  | Application Example optimized for RF performance (5V Supply)                  | 11 |

| Figure 3  | Pin-Out                                                                       | 12 |

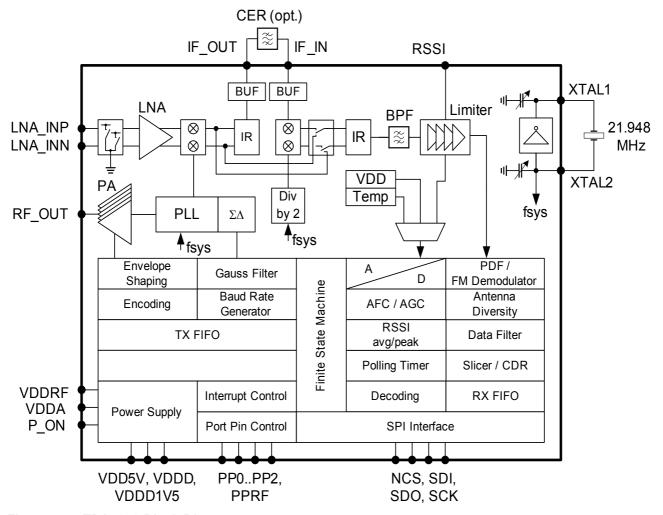

| Figure 4  | TDA5340 Block Diagram                                                         | 20 |

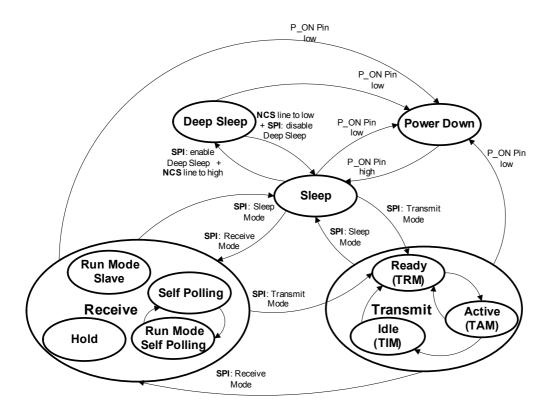

| Figure 5  | Main State Diagram                                                            | 22 |

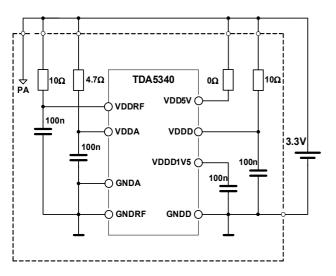

| Figure 6  | 3.3 Volts and 5 Volts Applications                                            | 23 |

| Figure 7  | Reset Behavior                                                                | 24 |

| Figure 8  | Block Diagram RF Receiver Section                                             | 25 |

| Figure 9  | Crystal Oscillator                                                            | 26 |

| Figure 10 | External Clock Generation Unit                                                | 26 |

| Figure 11 | Synthesizer Block Diagram                                                     | 27 |

| Figure 12 | Encoding/Decoding Schemes                                                     | 28 |

| Figure 13 | Functional Block Diagram ASK/FSK Demodulator                                  | 29 |

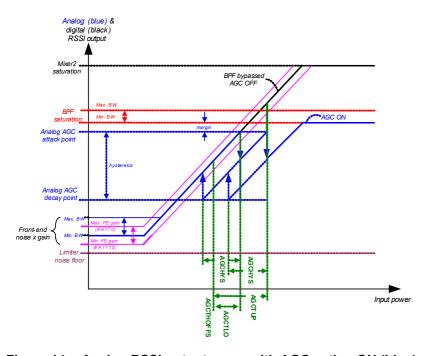

| Figure 14 | Analog RSSI output curve with AGC action ON (blue) vs. OFF (black)            | 30 |

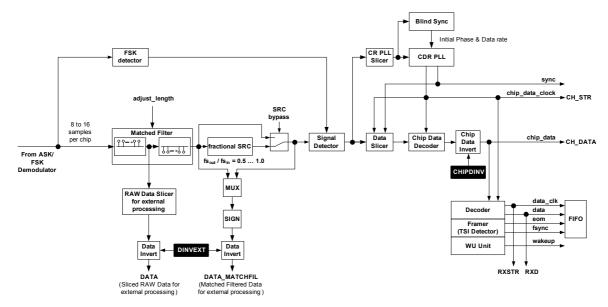

| Figure 15 | Functional Block Diagram Digital Baseband Receiver                            | 31 |

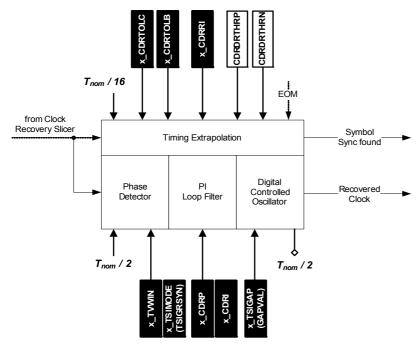

| Figure 16 | Clock Recovery (ADPLL)                                                        | 31 |

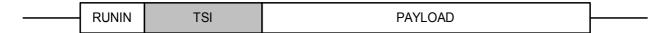

| Figure 17 | Structure of Payload Frame                                                    | 33 |

| Figure 18 | Burst Write Registers                                                         | 35 |

| Figure 19 | Write Register                                                                | 35 |

| Figure 20 | Read Register                                                                 | 36 |

| Figure 21 | Burst Read Registers                                                          | 36 |

| Figure 22 | Read FIFO                                                                     | 36 |

| Figure 23 | Write TX FIFO                                                                 | 37 |

| Figure 24 | Transparent TX Command                                                        | 37 |

| Figure 25 | SPI Checksum Generation                                                       | 38 |

| Figure 26 | Chip Serial Number                                                            | 38 |

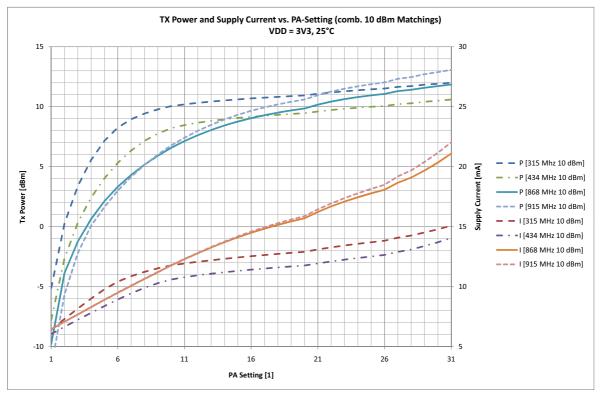

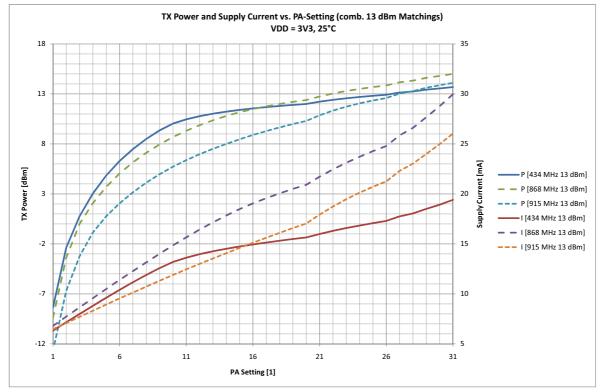

| Figure 27 | 10dBm Matching, Output Power and Supply Current in TX vs. Output power stages | 55 |

| Figure 28 | 13dBm Matching, Output Power and Supply Current in TX vs. Output power stages | 55 |

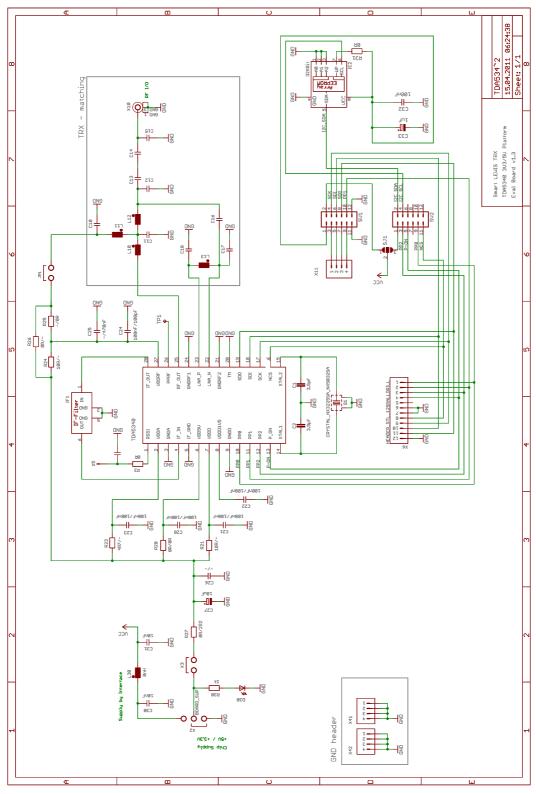

| Figure 29 | Test CircuitSchematic                                                         | 56 |

| Figure 30 | Test Board Layout                                                             | 57 |

| Figure 31 | PG-TSSOP-28 Package Outline (green package)                                   | 62 |

# **List of Tables**

# **List of Tables**

| . 34 |

|------|

| . 39 |

|      |

| 40   |

| . 40 |

| . 41 |

| . 43 |

| . 46 |

| . 46 |

| . 48 |

| . 49 |

| . 50 |

| . 51 |

| . 52 |

| . 57 |

|      |

# 1 Product Description

#### 1.1 Overview

The IC is a low power ASK/FSK/GFSK Transceiver for the frequency bands 300-320, 415-495, 863-960 MHz. Biphase modulation schemes, like Manchester, bi-phase mark, bi-phase space and differential Manchester as well as NRZ are supported.

The chip offers a high level of integration and needs only a few external components, like a crystal, several blocking capacitors and the necessary matching elements. The IF-filter is integrated but depending on the performance requirements an external ceramic IF-filter can be used. For low cost applications an external passive antenna switch configuration can be used.

The device is qualified according to automotive quality standards and operates between -40 and +110 °C at supply voltage ranges of 3.0-3.6 Volts or 4.5-5.5 Volts.

A fully integrated Sigma-Delta Fractional-N PLL Synthesizer, with high frequency resolution and a crystal oscillator as reference, generates the necessary frequencies for the power amplifier or down conversion mixers. The on-chip temperature sensor may be utilized for temperature drift compensation of the crystal oscillator.

The receiver portion is realized as a double down conversion super-heterodyne / low-IF architecture each with image rejection supplemented by digital signal processing in the baseband. This architecture enables outstanding sensitivity performance in combination with very good blocking performance values.

The transmitter section comprises a class C/E power amplifier with a high efficiency and an output power level of up to 14 dBm. A tuning feature for the output power is possible via several switchable parallel output stages, of course matching to lower power levels is always possible. For higher power applications an external power amplifier can be used and the internal PA serves as a power driver. For ASK modulation a programmable data shaping is provided. With the fractional-N PLL synthesizer and a selectable Gaussian data shaping filter a very accurate and precise FSK modulation is achieved. The transmit data can be either stored in a separate FIFO data buffer or directly provided via the bus interface.

The receiver portion is able to scan autonomuosly for incoming data by using the self polling feature while the host micro controller can stay in power down mode, which reduces the system current consumption significanty.

The digital baseband processing unit together with the high performance downconverter is the key element for the exceptional sensitivity performance of the device which take it close to the theoretical top-performance limits. It comprises signal and noise detectors, matched data filter, clock and data recovery, data slicer and a format decoder. It demodulates the received ASK or FSK data stream and recovers the data clock out of the received data with very fast synchronization times which can then be either accessed via separate pins or used for further processing like frame synchronization and intermediate storage in the on-chip FIFO.

The RSSI output signal is converted to the digital domain with an ADC. All these signals are accessible via the 4-wire SPI interface bus.

Up to 4 pre-configured telegram formats with different data rates and filter bandwidths can be stored into the device offering independent pre-processing of the received and transmitted data. The downconverter can be also configured to single-conversion mode at moderately reduced selectivity and image rejection performance but at the advantage of saving the external IF filter.

# 1.2 Key Features

#### **Transceiver**

- Multiband / Multichannel (300-320 MHz, 415-495 MHz, 863-960 MHz)

- High receiver sensitivity better than -116 dBm

- · Power amplifier with up to 14 dBm output power

- Very Low Current consumption:

- Receive Mode: 12 mA (typ)

- Transmit Mode at 10 dBm and 434 MHz: 12 mA (typ)

- Sleep Mode (XTAL ON): 40 uA (typ)

- Deep Sleep Mode (XTAL OFF): 7 μA (typ)

- Power down Mode: 0.9 uA (typ)

- ASK and FSK capability with programmable Gaussian data shaping

- 20 dB programable output power range

- · On-chip IF filter with selectable bandwidth (optional an external CER-filter is possible)

- Sigma-delta fractional-N PLL synthesizer with high resolution

- Automatic Frequency Control function (AFC) for offset carrier frequency

#### **Digital Baseband**

- Multi protocol handling: Up to 4 parallel parameter sets for autonomous scanning and receiving from different sources

- Integrated data and clock recovery

- · Autonomous receive functionality: Frame synchronisation, format decoding, message ID screening

- 288 Bit RX/TX-FIFO for receive and transmit data

- Wake-up generator and polling timer unit

- · Ultra-fast wake-up on RSSI

- Supports all bi-phase format schemes and NRZ

### General

- Operating temperature range -40 to +110°C

- Supply voltage range 3.0 to 3.6 V or 4.5 to 5.5 V

- Brownout detector

- Integrated 4-wire SPI bus interface

- 32-bit wide Unique ID on chip

- · On-chip temperature sensor

- ESD protection +/- 2 kV on all pins (HBM)

- PG-TSSOP-28 package

## 1.3 Target Applications

- Remote keyless entry (RKE)

- Remote start applications

- Passive Keyless Entry (PKE)

- Security Alarm Systems

- Automatic Meter Reading (AMR) and Infrastructure (AMI)

- Home Automation

- Remote Control

- Sensor Networks

- Short range radio data transmission

Data Sheet 9 Revision 1.2, 13.06.2012

# 1.4 Application Example

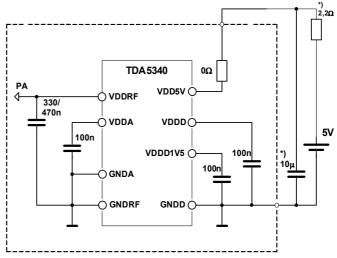

The Application examples within this section where optimezed for performance and sytem costs. Of course there exists several steps inbetween which can be realized by the customer to fullfill the application specific needs.

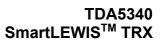

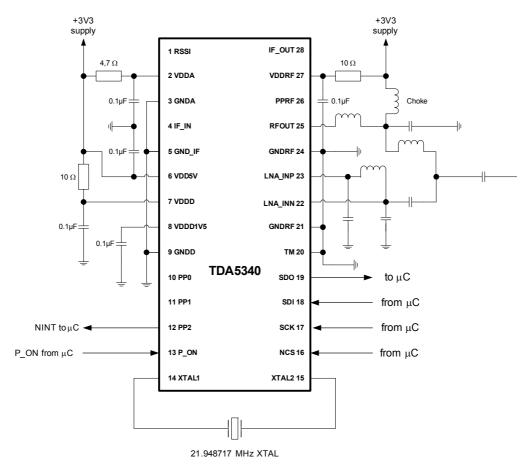

Figure 1 Application Example optimized for System Costs (3V3 Supply)

Figure 2 Application Example optimized for RF performance (5V Supply)

# 2 Functional Overview

# 2.1 Pin Configuration

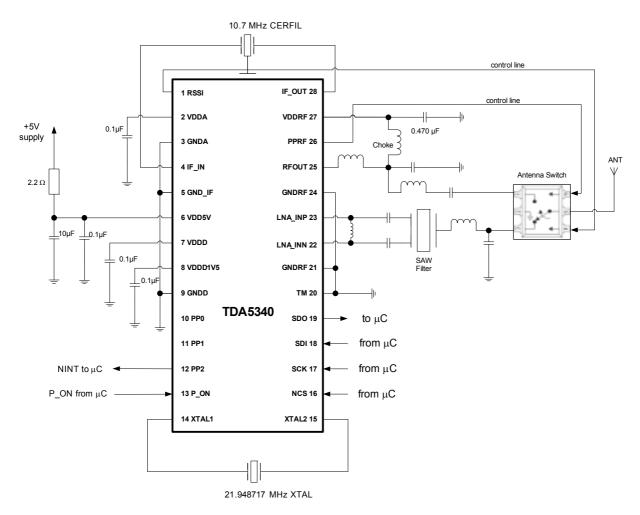

Figure 3 Pin-Out

# 2.1.1 Pin Definition

Table 1 Pin Definition and Function

| Pin Nr | Pad Name  | Equivalent I/O Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Function                                                                                                                                                                                                                                     |

|--------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | PPRF_RSSI | VDDA  VDDA  VDDA  VDDA  Vm_p  Vm_n  GNDA  GNDRF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Analog output Digital output with weak driver capability, always in 3V domain CLK_OUT, RX_RUN, NINT, ANT_EXTSW1, ANT_EXTSW1, DATA, DATA_MATCHFIL, CH_DATA, CH_STR, RXD, RXSTR, TXSTR and TRISTATE are programmable via SFR default: TRISTATE |

| 2      | VDDA      | VDD5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Analog input Analog supply                                                                                                                                                                                                                   |

|        |           | VDDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                              |

| 3      | GNDA      | VDDA  THE STATE OF | Analog Ground                                                                                                                                                                                                                                |

|        |           | analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                              |

Table 1 Pin Definition and Function

| Pin Nr | Pad Name | Equivalent I/O Schematic                                                | Function                          |

|--------|----------|-------------------------------------------------------------------------|-----------------------------------|

| 4      | IF_IN    | VDDA  not sel_inp  3200  mimcAP 10p  sel_inp  GNDIF  VDDA  NAND2  GNDIF | Analog input IF mixer input       |

| 5      | GND_IF   | GNDIF GNDA                                                              | Analog Ground                     |

| 6      | VDD5V    | VDD5V  GNDD GNDD  5V supply                                             | Analog input 5 Volt supply input  |

| 7      | VDDD     | VDD5V  VReg  VDDD  GNDD                                                 | Analog input digital supply input |

Table 1 Pin Definition and Function

| Pin Nr | Pad Name | Equivalent I/O Schematic   | Function                                                                                                                                                                     |

|--------|----------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8      | VDDD1V5  | VDDD VReg VDD1V5           | Analog output 1.5V regulator                                                                                                                                                 |

| 9      | GNDD     | VDDD  A GNDD               | Digital ground                                                                                                                                                               |

| 10     | PP0      | VDD5V VDD5V Vm_p Vm_n GNDD | Digital output CLK_OUT, RX_RUN, NINT, ANT_EXTSW1, ANT_EXTSW1, DATA, DATA_MATCHFIL, CH_DATA, CH_STR, RXD, RXSTR, TXSTR and TRISTATE are programmable via SFR default: CLK_OUT |

| 11     | PP1      | same as PP0                | Digital output CLK_OUT, RX_RUN, NINT, ANT_EXTSW1, ANT_EXTSW1, DATA, DATA_MATCHFIL, CH_DATA, CH_STR, RXD, RXSTR, TXSTR and TRISTATE are programmable via SFR default: DATA    |

Table 1 Pin Definition and Function

| l able 1 | Pin Definition and Function |                                          |                                                                                                                                                                           |  |  |  |

|----------|-----------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Nr   | Pad Name                    | Equivalent I/O Schematic                 | Function                                                                                                                                                                  |  |  |  |

| 12       | PP2                         | same as PP0                              | Digital output CLK_OUT, RX_RUN, NINT, ANT_EXTSW1, ANT_EXTSW1, DATA, DATA_MATCHFIL, CH_DATA, CH_STR, RXD, RXSTR, TXSTR and TRISTATE are programmable via SFR default: NINT |  |  |  |

| 13       | P_ON                        | VDD5V VDDD  500Ω  GNDD  GNDD             | Digital input power-on reset                                                                                                                                              |  |  |  |

| 14       | XTAL1                       | VDDD VDDD  XTAL1  GNDD  GNDD  GNDD       | Analog input crystal oscillator input                                                                                                                                     |  |  |  |

| 15       | XTAL2                       | VDDD VDDD  A A A A A A A A A A A A A A A | Analog output crystal oscillator output                                                                                                                                   |  |  |  |

| 16       | NCS                         | VDD5V VDDD  500Ω  GNDD  GNDD             | Digital input<br>SPI Not Chip select                                                                                                                                      |  |  |  |

Table 1 Pin Definition and Function

| Pin Nr | Pad Name | Equivalent | I/O Schematic         |                         | Function                                |

|--------|----------|------------|-----------------------|-------------------------|-----------------------------------------|

| 17     | SCK      | SCK ■      | VDD5V  500Ω  GNDD     | VDDD<br>A<br>GNDD       | Digital input<br>SPI clock              |

| 18     | SDI      | SDI ■      | VDD5V<br>500Ω<br>GNDD | VDDD                    | Digital input<br>SPI data in            |

| 19     | SDO      | SDO •      | VDD5V                 | VDD5V  vm_p  vm_n  GNDD | Digital output<br>SPI data out          |

| 20     | TM       | тм         | VDD5V  500Ω  GNDD     | VDDD<br>GNDD            | Digital input connect to digital ground |

Table 1 Pin Definition and Function

| Pin Nr | Pad Name | Equivalent I/O Schematic | Function                             |

|--------|----------|--------------------------|--------------------------------------|

| 21     | GNDRF    | VDDRF                    | Analog ground                        |

| 22     | LNA_INN  | LNA_INN LNA GNDRF        | Analog input - RF input              |

| 23     | LNA_INP  | LNA_INP LNA GNDRF        | Analog input<br>+RF input            |

| 24     | GNDRF    | VDDRF                    | Analog ground                        |

| 25     | RFOUT    | RFOUT                    | Analog output power amplifier output |

Table 1 Pin Definition and Function

| Pin Nr | Pad Name | Equivalent I/O Schematic                            | Function                                                                                                                                                                                          |

|--------|----------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26     | PPRF     | VDDRF  VDDRF  Vm_p  GNDRF  GNDRF                    | Digital output always in 3V domain CLK_OUT, RX_RUN, NINT, ANT_EXTSW1, ANT_EXTSW1, DATA, DATA_MATCHFIL, CH_DATA, CH_STR, RXD, RXSTR, TXSTR and TRISTATE are programmable via SFR default: TRISTATE |

| 27     | VDDRF    | VDD5V<br>VRed<br>VDDRF<br>VDDRF                     | Analog input<br>RF supply                                                                                                                                                                         |

| 28     | IF_OUT   | VDDRF VDDRF  330Ω  F-OUT  GNDRF GNDRF  VDDRF  GNDRF | Analog output Mixer output                                                                                                                                                                        |

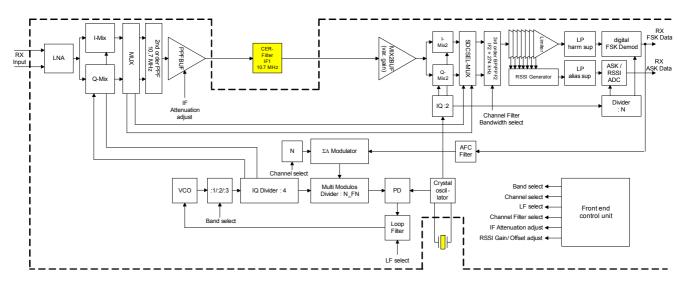

# 2.2 Functional Block Diagram

Figure 4 TDA5340 Block Diagram

### 2.3 Architecture Overview

A fully integrated Sigma-Delta Fractional-N PLL Synthesizer covers the frequency bands 300-320 MHz, 415-495 MHz, 860-960 MHz with a high frequency resolution, using only one VCO running at around 3.6 GHz. This makes the IC most suitable for Multi-Band/Multi-Channel applications. For Multi-Channel applications a very good channel separation is essential. To achieve the necessary high sensitivity and selectivity a double down conversion super-heterodyne architecture is used. The first IF frequency is located at 10.7 MHz and the second IF frequency at 274 kHz. For both IF frequencies an adjustment-free image frequency rejection feature is realized. In the second IF domain the filtering is done with an on-chip third order bandpass polyphase filter. A multi-stage bandpass limiter completes the RF/IF path of the receiver. For Single-Channel applications with relaxed requirements to selectivity, a single down conversion low-IF scheme can be selected.

A highly efficient Class C/E Power amplifier with an output level of +14dBm combined with a Gaussian Filter for GFSK and amplitude ramping functions for shaped ASK is implemented. A high resolution power adjustment can be done to trim the output power for highest system power savings. The data can be either shifted out of a on-chip transmit FIFO or directly provided on an input pin.

An RSSI generator delivers a DC signal proportional to the applied input power and is also used as an ASK demodulator. Via an anti-aliasing filter this signal feeds an ADC with 10 bits resolution. The limiter output signal

feeds a digital FSK demodulator. This block demodulates the FSK data and delivers an AFC signal which controls the divider factor of the PLL synthesizer. A digital receiver, which comprises RSSI peak detectors, a matched data filter, a clock and data recovery, a data slicer, a frame synchronization and a data FIFO, decodes the received ASK or FSK data stream. The recovered data and clock signals are accessible via 2 separate pins. The FIFO data buffer is accessible via the SPI bus interface. The crystal oscillator serves as the reference frequency for the PLL phase detector, the clock signal of the Sigma-Delta modulator and divided by two as the 2nd local oscillator signal. To accelerate the start up of the crystal oscillator two modes are selectable: a Low Power Mode (with lower precision) and a High Precision Mode.

#### 2.4 Block Overview

The TDA5340 is separated into the following main blocks:

- RF / IF Receiver

- Power Amplifier

- Crystal Oscillator and Clock Divider

- Sigma-Delta Fractional-N PLL Synthesizer

- · ASK / FSK Demodulator incl. AFC and AGC

- · RSSI Peak Detector

- Digital Baseband Receiver

- Digital Baseband Transmitter

- · Power Supply Circuitry

- · System Interface

- · System Management Unit

# 2.5 Operating Modes

The transceiver has three different power saving modes, two receive modes and a transmit mode. The different operating modes are used to adjust the transceiver functionality to the needs of the application. Depending on the used communication protocols the appropriate power saving mode can be selected. In the table below all different modes are listed and corresponding to the modes the active blocks and current consumptions are shown.

Table 2 Operating Modes

| Operating Mode    | Transceive | typ. Current |                  |     |     |     |     |     |                       |

|-------------------|------------|--------------|------------------|-----|-----|-----|-----|-----|-----------------------|

|                   | Dig. Vreg  | Ana. Vreg    | XTAL             | SFR | SPI | PLL | PA  | RX  | Consumption           |

| Power Down        | OFF        | OFF          | OFF              | OFF | OFF | OFF | OFF | OFF | 0.9 μΑ                |

| Deep Sleep        | ON         | OFF          | OFF              | ON  | OFF | OFF | OFF | OFF | 7 μΑ                  |

| Sleep             | ON         | OFF          | ON <sup>1)</sup> | ON  | ON  | OFF | OFF | OFF | 40 μA <sup>2)</sup>   |

| Sleep ADC enabled | ON         | ON           | ON <sup>1)</sup> | ON  | ON  | OFF | OFF | OFF | 1 mA                  |

| Transmit Ready    | ON         | ON           | ON               | ON  | ON  | ON  | OFF | OFF | 5.8 mA                |

| Transmit Idle     | ON         | ON           | ON               | ON  | ON  | OFF | OFF | OFF | <3 mA                 |

| Transmit          | ON         | ON           | ON               | ON  | ON  | ON  | ON  | OFF | 12.5 mA <sup>3)</sup> |

| Receive           | ON         | ON           | ON               | ON  | ON  | ON  | OFF | ON  | 11 mA <sup>4)</sup>   |

- 1) selectable between XTAL in high or low precision mode

- 2) XTAL in low precision mode

- 3) 10dBm Output power at 434MHz

- 4) single down conversion Mode (no external CER Filter used)

Figure 5 Main State Diagram

# 2.6 Block Description

## 2.6.1 Power Supply Circuitry

The chip may be operated within a 5 Volts or a 3.3 Volts environment.

For operation within a 5 Volts environment (supply voltage range 1), the chip is supplied via the VDD5V pin. In this configuration the digital I/O pads are supplied via VDD5V and a 5 V to 3.3 V voltage regulator supplies the analog/RF section (only active in Run Modes). When operating within a 3.3 Volts environment (supply voltage range 2), the VDD5V, VDDA, VDDD and VDDRF pins must be supplied. The 5 V to 3.3 V voltage regulators are inactive in this configuration. The internal digital core is supplied by an additional 3.3 V to 1.5 V regulator. The regulators for the digital section are controlled by the signal at P\_ON (Power On) pin. A low signal at P\_ON disables all regulators and set the IC in Power Down Mode. A low to high transition at P\_ON enables the regulators for the digital section and initiates a power on reset. The regulator for the analog section is controlled by the Master Control Unit and is active only when the RF section is active. To provide data integrity within the digital units, a brownout detector monitors the digital supply. In case a voltage drop of VDDD below approximately 2.45 V is detected a RESET will be initiated. A typical power supply application for a 3.3 Volts and a 5 Volts environment is shown in the figure below.

Supply-Application in 5V environment

Figure 6 3.3 Volts and 5 Volts Applications

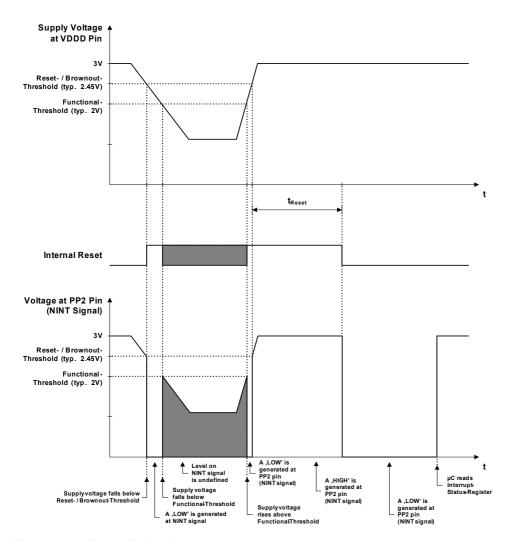

## 2.6.2 Chip Reset

Power down and power on are controlled by the P\_ON pin. A LOW at this pin keeps the IC in Power Down Mode. All voltage regulators and the internal biasing are switched off. A high transition at P\_ON pin activates the appropriate voltage regulators and the internal biasing of the chip. A power up reset is generated at the same time.

When operating in a 5V environment, the voltage-drop across the voltage regulators 5 → 3.3V has to be limited, to keep the regulators in a safe operating range. Resistive or capacitive loads (in excess to the scheme shown above) on pins VDDA and VDDD are not recommended.

Figure 7 Reset Behavior

A second source that can trigger a reset is a brownout event. Whenever the integrated brownout detector measures a voltage drop below the brownout threshold on the digital supply, the integrity of the stored data and configuration can no longer be guaranteed; thus a reset is generated. While the supply voltage stays between the brownout and the functional threshold of the chip, the NINT signal is forced to low. When the supply voltage drops below the functional threshold, the levels of all digital output pins are undefined. When the supply voltage raises above the brownout threshold, the IC generates a high pulse at NINT and remains in the reset state for the duration of the reset time. When the IC leaves the reset state, the Interrupt Status registers are set to 0xFF and the NINT signal is forced to low. Now, the IC starts operation in the SLEEP Mode, ready to receive commands via the SPI interface. The NINT signal will go high, when one of the Interrupt Status registers is read for the first time.

#### 2.6.3 RF / IF Receiver

The receiver path uses a double down conversion super-heterodyne/low-IF architecture, where the first IF frequency is located at 10.7 MHz and the second IF frequency at 274 kHz. For the first IF frequency an adjustment-free image frequency rejection is realized by means of two I/Q-mixers followed by a second order passive polyphase filter centered at 10.7 MHz (PPF). The I/Q-oscillator signals for the first down conversion are delivered from the PLL synthesizer. The frequency selection in the first IF domain is done by an external CER filter. For moderate or low performance applications, this ceramic filter can be substituted by a simple LC Pi-filter or completely by-passed using the receiver as a single down conversion low-IF scheme with 274 kHz IF frequency.

The down conversion to the second IF frequency is done by means of two high-side injected I/Q-mixers together with an on-chip third order bandpass polyphase filter (PPF2 + BPF). The I/Q-oscillator signals for the second down conversion are directly derived by division of two from the crystal oscillator frequency. The bandwidth of the bandpass filter (BPF) can be selected from 50 kHz to 300 kHz in 5 steps. For a frequency offset of 150 kHz to 120 kHz, the AFC (Automatic Frequency Control) function is mandatory. Activated AFC option might require a longer preamble sequence in the receive data stream.

The receiver enable signal (RX\_RUN) can be offered at each of the port pins to control external components. Whenever the receiver is active, the RX\_RUN output signal is active. Active high or active low is configurable via PPCFG2 register.

Figure 8 Block Diagram RF Receiver Section

#### 2.6.4 Transmitter

A highly efficient Class C/E Power amplifier with output levels of +14 dBm combined with a Gaussian Filter for GFSK and amplitude ramping functions for shaped ASK is implemented. A high resolution power adjustment can be done to trim the output power for highest system power savings. The data can be either shifted out of a on-chip transmit FIFO or directly provided on an input pin.

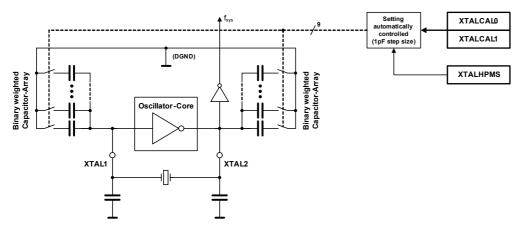

# 2.6.5 Crystal Oscillator and Clock Divider

The crystal oscillator is a Pierce type oscillator. An automatic amplitude regulation circuitry allows the oscillator to operate with minimum current consumption. In SLEEP Mode, where the current consumption should be as low as possible, the load capacitor must be small and the frequency is slightly detuned, therefore all internal trim capacitors are disconnected. The internal capacitors are controlled by the crystal oscillator calibration registers XTALCALx. With a binary weighted capacitor array the necessary load capacitor can be selected.

Whenever a XTALCALx register value is updated, the selected trim capacitors are automatically connected to the crystal so that the frequency is precise at the specified value. Step size is 1 pF. The SFR control bit XTALHPMS can be used to activate the High Precision Mode also during SLEEP Mode.

Figure 9 Crystal Oscillator

#### **External Clock Generation Unit**

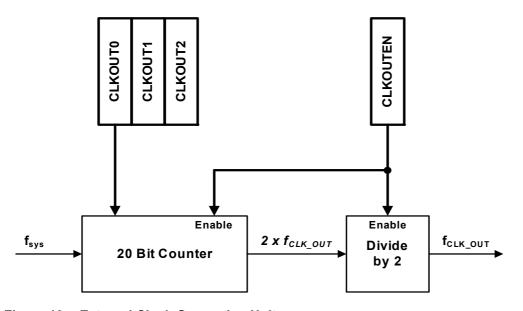

A built-in programmable frequency divider can be used to generate an external clock source out of the crystal reference. The 20 bit wide division factor is stored in the registers CLKOUT0, CLKOUT1 and CLKOUT2. The minimum value of the programmable frequency divider is 1. This programmable divider is followed by an additional divider by 2, which generates a 50% duty cycle of the CLK\_OUT signal. So the maximum frequency at the CLK\_OUT signal is the crystal frequency divided by 4. The minimum CLK\_OUT frequency is the crystal frequency divided by 2<sup>21</sup>.

To save power, this programmable clock signal can be disabled by the SFR control bit CLKOUTEN. In this case the external clock signal is set to low.

Figure 10 External Clock Generation Unit

## 2.6.6 Sigma-Delta Fractional-N PLL Block

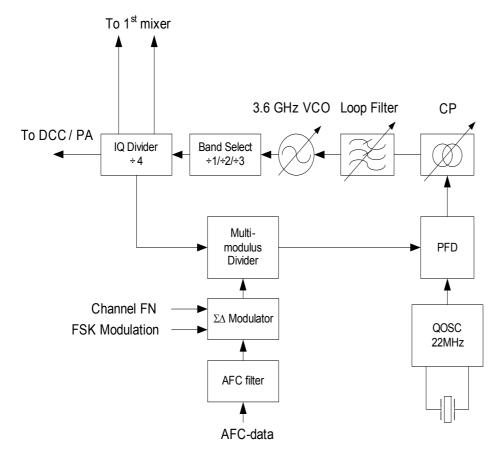

The Sigma-Delta Fractional-N PLL is fully integrated on chip. The Voltage Controlled Oscillator (VCO) with on-chip LC-tank runs at approximately 3.6 GHz and is first divided with a band select divider by 1, 2 or 3 and then with an I/Q-divider by 4 which provides an orthogonal local oscillator signal for the first image reject mixer with the necessary high accuracy.

The multi-modulus divider determines the channel selection and is controlled by a 3rd order Sigma-Delta Modulator (SDM). A type IV phase detector, a charge pump with programmable current and an on-chip loop filter closes the phase locked loop.

Figure 11 Synthesizer Block Diagram

### 2.6.6.1 PLL Dividers

The divider chain consists of a band select divider 1/2/3, an I/Q-divider by 4 which provides an orthogonal 1st local oscillator signal for the first image reject mixer with the necessary high accuracy and a multi-modulus divider controlled by the Sigma-Delta Modulator. With the band select divider, the wanted frequency band is selected. Divide by 1 selects the 915 MHz and 868 MHz band, divide by 2 selects the 434 MHz band and divide by 3 selects the 315 MHz band. The ISM band selection is done via bit group BANDSEL in x\_PLLINTC1 register.

# 2.6.6.2 Digital Modulator

The 3<sup>rd</sup> order Sigma-Delta Modulator (SDM) has a 22 bit wide input word, however the LSB is always high, and is clocked by the XTAL oscillator. This determines the achievable frequency resolution.

The Automatic Frequency Control (AFC) Unit filters the actual frequency offset from the FSK demodulator data and calculates the necessary correction of the divider factor to achieve the nominal IF center frequency.

# 2.6.7 Decoding/Encoding Modes

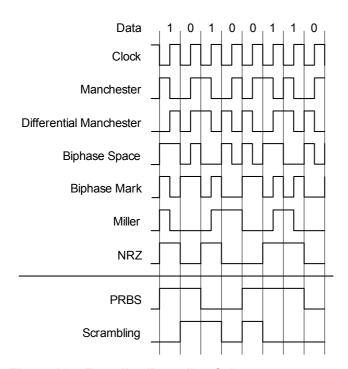

The IC supports the following Bi-phase encodings:

- · Manchester code

- · Differential Manchester code

- · Bi-phase space code

- Bi-phase mark code

- Miller code (TX only)

- NRZ

The encoding mode is set and enabled by bit group CODE in  $x_DIGRXC$  (receiver) and  $x_TXCFG$  (transmitter) configuration register.

Figure 12 Encoding/Decoding Schemes

#### 2.6.8 ASK and FSK Demodulator

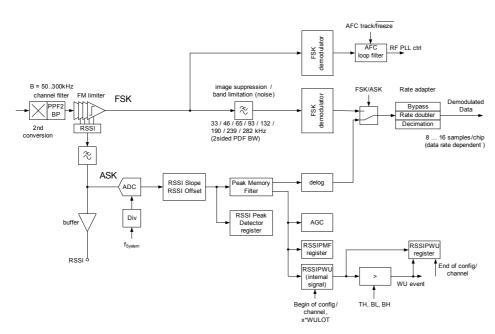

The IC comprises two separate demodulators for ASK and FSK.

After combining FSK and ASK data path, a sampling rate adaptation follows to meet an output oversampling between 8 and 16 samples per chip. Finally, an oversampling of 8 samples per chip can be achieved using a fractional sample rate converter (SRC) with linear interpolation

Figure 13 Functional Block Diagram ASK/FSK Demodulator

#### 2.6.8.1 ASK Demodulator

The RSSI generator delivers a DC signal proportional to the applied input power at a logarithmic scale (dBm) and is also used as an ASK demodulator. Via a programmable anti-aliasing filter this signal is converted to the digital domain by means of a 10-bit ADC. For the AM demodulation a signal proportional to the linear power is required. Therefore a conversion from logarithmic scale to linear scale is necessary. This is done in the digital domain by a nonlinear filter together with an exponential function. The analog RSSI signal after the anti-aliasing filter is available at the RSSI pin via a buffer amplifier. To enable this buffer the SFR control bit RSSIMONEN must be set. The anti-aliasing filter can be by-passed for visualization on the RSSI pin (see AAFBYP control bit).

#### 2.6.8.2 FSK Demodulator

The limiter output signal, which has a constant amplitude over a wide range of the input signal, feeds the FSK demodulator. There is a configurable lowpass filter in front of the FSK demodulation to suppress the down conversion image and noise/limiter harmonics (FSK Pre-Demodulation Filter, PDF). This is realized as a 3<sup>rd</sup> order digital filter. The sampling rate after FSK demodulation is fixed and independent from the target data rate.

# 2.6.8.3 Automatic Frequency Control Unit (AFC)

In front of the image suppression filter a second FSK demodulator is used to derive the control signal for the Automatic Frequency Control Unit, which is actually the DC value of the FSK demodulated signal. This makes the AFC loop independent from signal path filtering and allow so a wider frequency capture range of the AFC. The derivation of the AFC control signal is preferably done during the DC-free preamble and is then frozen for the rest of the datagram.

Since the digital FSK demodulator determines the exact frequency offset between the received input frequency and the programmed input center frequency of the receiver, this offset can be corrected through the sigma delta control of the PLL.

# 2.6.8.4 Digital Automatic Gain Control Unit (AGC)

Automatic Gain Control (AGC) is necessary mainly because of the limited dynamic range of the on-chip bandpass filter (BPF). The BPF dynamic range reduces to less than 60dB in case of minimum BPF bandwidth.

AGC is used to cover the following cases:

- 1. ASK demodulation at large input signals

- 2. RSSI reading at large input signals

- 3. Improve IIP3 performance in either FSK or ASK mode

The 1<sup>st</sup> IF buffer can be fine tuned "manually" by means of 4 bits thus optimizing the overall gain to the application (attenuation of 0dB to -12dB by means of IFATT0 to IFATT15). This buffer allows the production spread of external components to be trimmed.

The gain of the 2<sup>nd</sup> IF path is set to three different values by means of an AGC algorithm. Depending on whether the receiver is used in single down conversion or in double down conversion mode the gain control in the 2<sup>nd</sup> IF path is either after the 2<sup>nd</sup> poly-phase network or in front of the 2<sup>nd</sup> mixer.

The AGC action is illustrated in the RSSI curve below:

Figure 14 Analog RSSI output curve with AGC action ON (blue) vs. OFF (black)

# 2.6.8.5 Digital Baseband (DBB) Receiver

Figure 15 Functional Block Diagram Digital Baseband Receiver

The digital baseband receiver comprises a matched data filter, a clock and data recovery, a data slicer, a line decoder, a wake-up generator, a frame synchronization and a data FIFO. The recovered data and clock signals are accessible via 2 separate pins. The FIFO data buffer is accessible via the SPI bus interface.

# 2.6.8.6 Clock and Data Recovery (CDR)

An all-digital PLL (ADPLL) recovers the data clock from the incoming data stream. The second main function is the generation of a signal indicating symbol synchronization. Synchronization on the incoming data stream generally occurs within the first 4 bits of a telegram.

Figure 16 Clock Recovery (ADPLL)

Data Sheet 31 Revision 1.2, 13.06.2012

Clock Recovery is implemented as standard ADPLL PI regulator with Timing Extrapolation Unit for fast settling. In the unlocked state, the Timing Extrapolation Unit calculates the frequency offset for the incoming data stream. If the defined number of Bi-phase encoded bits are detected (the RUNIN length can be set in the x\_CDRRI register), the I-part and the PLL oscillator will be set and the PLL will be locked. When x\_CDRRI.RUNLEN is set to small values, then the I-part is less accurate (residual error) and can lead to a longer needed PLL settling time and worse performance in the first following bits. Therefore the selected default value is a good compromise between fast symbol synchronization and accuracy/performance. Duty cycle and data rate acceptance limits are adjustable via registers. After locking, the clock must be stable and must follow the reference input. Therefore, a rapid settling procedure (Timing Extrapolation Unit) and a slow PLL are implemented. If the PLL is locked, the reference signal from the Clock Recovery Slicer is used in the phase detector block to compute the actual error. The error is used in the PI loop filter to set the digital controlled oscillator running frequency. For the P, I and Timing Extrapolation Unit settings, the default values for the x\_CDRP and x\_CDRI control registers are recommended. The PLL will be unlocked, if a code violation of more than the defined length is detected, which is set in the x\_TVWIN control register. Another criterion for PLL resynchronization is an End Of Message (EOM) signalled by the Framer block. The PLL oscillator generates the chip clock frequency is equal to 2 times the data rate.

## 2.6.8.7 Wake-Up Generator

A wake-up generation unit is used only in the Self Polling Mode for the detection of a predefined wake-up criterion in the received pattern. There are two groups of configurable wake-up criteria:

- · Wake-up on Level criteria

- Wake-up on Data criteria

The search for the wake-up data criterion is started if data chip synchronization has occurred within the predefined number of symbols, otherwise the wake-up search is aborted. Several different wake-up patterns, like random bit, equal bit, bit pattern or bit synchronization, are programmable. Additional level criterion fulfilment for RSSI or Signal Recognition can lead to a fast wake-up and to a change to Run Mode Self Polling. Whenever one of these Wake-up Level criteria is enabled and exceeds a programmable threshold, a wake-up has been detected. The Wake-up Level criterion can be used very effectively in combination with the Ultrafast Fall Back to SLEEP Mode for further decreasing the needed active time of the autonomous receive mode. A configurable observation time for Wake-up on Level can be set in the x\_WULOT register.

## 2.6.8.8 Frame Synchronization

The Frame Synchronization Unit (Framer) synchronizes to a specific pattern to identify the exact start of a payload data frame within the data stream. This pattern is called Telegram Start Identifier (TSI). There are different TSI modes selectable via the configuration:

- 16-Bit TSI Mode, supporting a TSI length of up to 16 bits or 32 chips

- 8-Bit Parallel TSI Mode, supporting two independent TSI pattern of up to 8 bits length each. Different payload length is possible for these two TSI pattern.

- 8-Bit Extended TSI Mode, identical to 8-Bit Parallel TSI Mode, but identifies which pattern matches by adding

a single bit at the beginning of the data frame

- 8-Bit TSI Gap Mode, supporting two independent TSI pattern separated by a discontinuity

All SFRs configuring the Frame Synchronization Unit support the Multi-Configuration capability (Config A, B, C and D). The Framer starts working in Run Mode Slave after Symbol Sync found and in Self Polling Mode after wake-up found and searches for a frame until TSI is found or synchronization is lost. The input of the Framer is a sequence of Bi-phase encoded data (chips). Basically the Framer consists of two identical correlators of 16 chips in length. It allows a Telegram Start Identifier (TSI) to be composed of Bi-phase encoded "Zeros" and "Ones". The active length of each of the 16 chips correlators is defined independently in the x\_TSILENA and x\_TSILENB registers. The pattern to match is defined as a sequence of chips in the x\_TSIPTA0, x\_TSIPTA1, x\_TSIPTB0 and x\_TSIPTB1 registers.

# 2.6.8.9 Message ID Scanning

This unit is used to define an ID or special combination of bits in the payload data stream, which identifies the pattern. All SFRs configuring the Message ID Scanning Unit feature the Multi-Configuration capability. Furthermore, it is available in the Slave and Self Polling Mode. The MID Unit can be mainly configured in two modes: 4-Byte and 2-Byte organized Message ID. For each configuration there are 20 8-bit registers designed for ID storage. SFRs are used to configure the MID Unit: Enabling of the MID scanning, setting of the ID storage organization, the starting position of the comparison and number of bytes to scan. When the Message ID Scanning Unit is activated, the incoming data stream is compared bit-wise serially with all stored IDs. If the Scan End Position is reached and all received data have matched the observed part of at least one MID the Message ID Scanning Unit indicates a successful MID scanning to the Master FSM, which generates an MID interrupt. Please note that the default register value of the MID registers is set to 0x00. All MID registers must be set to a pattern value to avoid matching to default value 0x00. If the MID Unit finishes ID matching without success, the data receiving is stopped and the FSM waits again for a Frame Start criterion. The received bits are still stored in the FIFO.

# 2.6.8.10 RUNIN, Synchronization Search Time and Inter-Frame Time

The functionality of the Digital Baseband Receiver is divided into four consecutive data processing stages; the data filter, clock and data recovery, data slicer and frame synchronization unit. The architecture of the Digital Baseband Receiver is optimized for processing bi-phase coded data streams. The basic structure of a payload frame is shown in **Figure 17**. The protocol starts with a so called RUNIN. The RUNIN with the minimum length of four bi-phase coded symbols is used for internal filter settling and frequency adjustment. The TSI (Telegram Start Identifier), which is used as framing word, follows the RUNIN sequence. The payload contains the effective data. The length of the valid payload data is defined as the length itself or additional criteria (e.g. loss of Sync). Please note that almost all transmitted protocols send a wake-up sequence before the payload frame. This wake-up sequence allows a very fast decision, whether there is a suitable message available or not.

Figure 17 Structure of Payload Frame

# 2.6.9 Application Interface

## **Transparent Mode**

The TDA5340 supports two levels of integration. In the most elementary fashion, it provides a rather rudimentary interface.

The incoming RF signal is demodulated and the corresponding data is made available to the Application Controller. Optionally, a chip clock is generated by the TDA5340.

The Application Controller can provide the baseband data to a single input pin which is modulated and amplified via the PLL and Power amplifier.

Since the data signal is always directly the baseband representation of the RF signal, we call this mode the Transparent Mode.

#### **Packet Oriented Mode**

Alternatively, the TDA5340 features the so-called Packet Oriented Mode which supports the autonomous reception and transmission of data telegrams. The Packet Oriented Mode provides a high-level System Interface which greatly simplifies the integration of the transceiver in data-centric applications. In Packet Oriented Mode, the data interface is based on chunks of synchronous data which are received in packets. In the easiest way, the Application Controller only reacts on the synchronous data it receives. The receiver autonomously handles the line decoding and the deframing of these data, and supports the timed reception of packets. Data is buffered in a receive FIFO and can be read out via the data interface. Further, the receiver provides support for the identification of wake-up signals.

# 2.6.9.1 Digital Control (4-wire SPI Bus)

The control interface used for device control and data transmission is a 4-wire SPI interface.

- NCS select input, active low

- SDI data input

- SDO data output

- SCK clock input:

Data bits on SDI are read in at rising SCK edges and written out on SDO at falling SCK edges.

#### **Level Definition:**

logic 0 = low voltage

level logic 1 = high voltage level

Note: It is possible to send multiple frames while the device is selected. It is also possible to change the access mode while the device is selected by sending a different instruction. Note: In all bus transfers MSB is sent first, except for the received data read from the FIFO. There the bit order is given as first bit received is first bit transferred via the bus.

Table 3 Instruction Set

| Instruction | Description                  | Instruction<br>Format |

|-------------|------------------------------|-----------------------|

| WRB         | Write to chip in Burst mode  | 0x01                  |

| WR          | Write to chip                | 0x02                  |

| RD          | Read from chip               | 0x03                  |

| RDF         | Read FIFO from chip          | 0x04                  |

| RDB         | Read from chip in Burst mode | 0x05                  |

Table 3 Instruction Set

| Instruction | Description                                             | Instruction<br>Format |

|-------------|---------------------------------------------------------|-----------------------|

| WRF         | Write FIFO                                              | 0x06                  |

| WRT0        | Write transparent transmit data with starting low data  | 0x08                  |

| WRT1        | Write transparent transmit data with starting high data | 0x07                  |

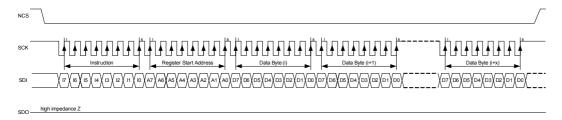

#### **Burst Write Command**

To write to the device in Burst mode, the SPI master has to select the SPI slave unit first. Therefore the master has to drive the NCS line to low. After the instruction byte and the start address byte have been transferred to the SPI slave (MSB first) the successive data bytes will be stored into the automatically addressed registers. To verify the SPI Burst Write transfer, the current address (start address, start address + 1, etc.) is stored in register SPIAT and the current data field of the frame is stored in register SPIDT. At the end of the Burst Write frame the latest address as well as the latest data field can be read out to verify the transfer. Note that some error in one of the intermediate data bytes can not be detected by reading SPIDT. Driving the NCS line to high will end the Burst frame. A single SPI Burst Write command can be applied very efficiently for data transfer either within a register block of configuration dependent registers or within the block of configuration independent registers.

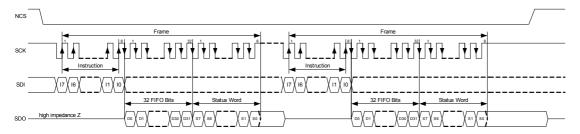

Figure 18 Burst Write Registers

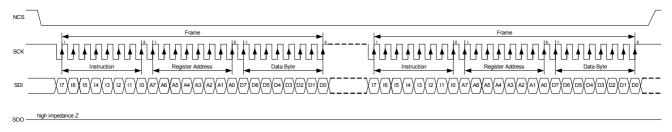

#### **Write Command**

To write to the device, the SPI master has to select the SPI slave unit first. Therefore, the master must set the NCS line to low. After this, the instruction byte and the address byte are shifted in on SDI and stored in the internal instruction and address register. The following data byte is then stored at this address. After completing the writing operation, either the master sets the NCS line to high or continues with another SPI command. Additionally the received address byte is stored into the register SPIAT and the received data byte is stored into the register SPIDT. These two trace registers are readable. Therefore, an external controller is able to check the correct address and data transmission by reading out these two registers after each write instruction. The trace registers are updated at every write instruction, so only the last transmission can be checked by a read out of these two registers.

Figure 19 Write Register

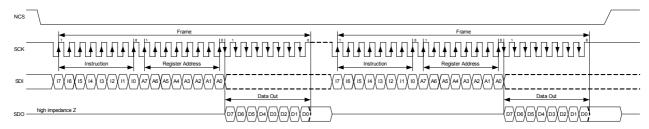

#### **Read Command**

To read from the device, the SPI master has to select the SPI slave unit first. Therefore, the master must set the NCS line to low. After this, the instruction byte and the address byte are shifted in on SDI and stored in the internal instruction and address register. The data byte at this address is then shifted out on SDO. After completing the read operation, either the master sets the NCS line to high or continues with another SPI command.

Figure 20 Read Register

#### **Burst Read Command**

To read from the device in Burst mode, the SPI master has to select the SPI slave unit first. Therefore the master has to drive the NCS line to low. After the instruction byte and the start address byte have been transferred to the SPI slave (MSB first), the slave unit will respond by transferring the register contents beginning from the given start address (MSB first). Driving the NCS line to high will end the Burst frame.

Figure 21 Burst Read Registers

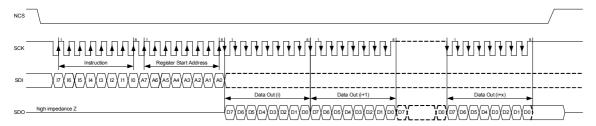

#### **Read FIFO Command**

To read the FIFO, the SPI master has to select the SPI slave unit first. Therefore, the master must set the NCS line to low. After this, the instruction byte is shifted in on SDI and stored in the internal instruction register. The data bits of the FIFO are then shifted out on SDO. The following byte is a status word that contains the number of valid bits in the data packet. After completing the read operation, either the master sets the NCS line to high or continues with a other SPI command.

Figure 22 Read FIFO

**Functional Overview**

#### **Write FIFO Command**

To write to the TX FIFO the SPI master has to select the SPI slave unit first. Therefore the master has to drive the NCS line to low. After the instruction byte (MSB first) the next byte contains the number of data items (chip or bit) minus 1 to be transferred to the FIFO. Therefore 0x00 means a single data item, whereas 0xFF means 256 data items. Successive data bytes contain the data items to be stored into the FIFO. Only the number of data items specified in the 2nd byte of the instruction will be stored into the FIFO. Other bits are skipped. At the end of the access frame the master has to deselect the slave unit by driving the NCS line to high.

Figure 23 Write TX FIFO

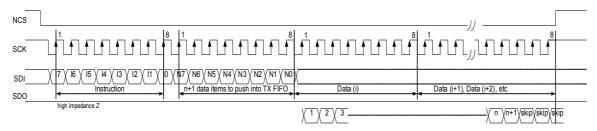

#### **Transparent TX Command**

To transfer data items (chip/bit) via SPI in transparent TX mode the SPI master has to select the SPI slave unit first. Therefore the master has to drive the NCS line to low. After the instruction byte (MSB first) the SCK should stay static to reduce noise during transmit.

Note that there are 2 versions of the same command available. They differ only in the LSB of the instruction. The intent of this is to pre-set the level of the SDI line to the level of the first TX data item (chip/bit). A new data item is asserted every "k" Gaussian Filter strobes (depends on the configuration, k strobes per chip).

Figure 24 Transparent TX Command

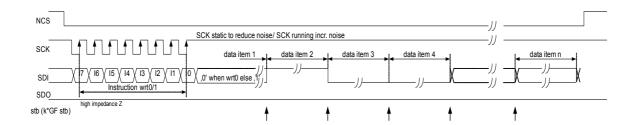

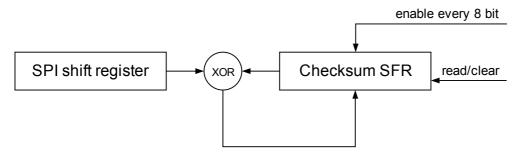

#### **SPI Check Sum**

The SPI also includes a safety feature by which the checksum is calculated with an XOR operation from the address and the data when writing SFR registers content. The checksum is in fact an XOR of the data 8-bitwise after every 8 bits of the SPI write command. The calculated checksum value is automatically written in the SPICHKSUM register and can be compared with the expected value. After the SPICHKSUM register is read, its value is cleared. In case of an SPI Burst Write and Write FIFO frame, a checksum is calculated from the SPI start address and consecutive data fields.

**Functional Overview**

Figure 25 SPI Checksum Generation

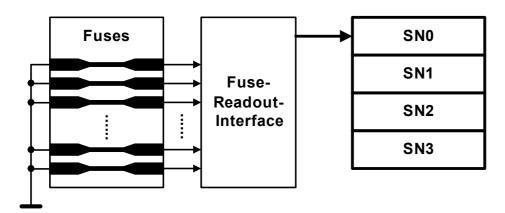

## 2.6.10 Chip Serial Number

Every device contains a unique, preprogrammed 32-bit wide serial number. This number can be read out from SN3, SN2, SN1 and SN0 registers via the SPI interface. The TDA5340 always has SN0.6 set to 1 and SN0.5 is reserved.

Figure 26 Chip Serial Number

Data Sheet 38 Revision 1.2, 13.06.2012

## 3 Reference

### 3.1 Electrical Data

## 3.1.1 Absolute Maximum Ratings

■ not subject to production test - verified by characterization/design

Attention: The maximum ratings must not be exceeded under any circumstances, not even momentarily and individually, as permanent damage to the IC may result.

Table 4 Absolute Maximum Ratings

| Parameter                                                                    | Symbol                |      | Value | S    | Unit | Note /                                             | Test | Numb  |

|------------------------------------------------------------------------------|-----------------------|------|-------|------|------|----------------------------------------------------|------|-------|

|                                                                              |                       | Min. | Тур.  | Max. |      | Test Condition                                     |      | er    |

| Supply Voltage at VDD5V pin                                                  | V <sub>smax</sub>     | -0.3 |       | +6   | V    |                                                    | -    | 1.1   |

| Supply Voltage at VDDD, VDDA, VDDRF pin                                      | V <sub>smax</sub>     | -0.3 |       | +4   | V    |                                                    | •    | 1.2   |

| Voltage between<br>VDD5V vs VDDD ,<br>VDD5V vs VDDA<br>and VDD5V vs<br>VDDRF | V <sub>smax</sub>     | -0.3 |       | +4   | V    |                                                    | •    | 1.3   |