### **DUAL EPAD® ULTRA MICROPOWER CMOS OPERATIONAL AMPLIFIER**

#### **KEY FEATURES**

- EPAD (Electrically Programmable Analog Device)

- User programmable Vos trimmer

- Computer-assisted trimming

- Rail-to-rail input/output

- Compatible with standard EPAD Programmer

- Each amplifier Vos can be trimmed to a different Vos level

- · High precision through in-system circuit precision trimming

- Reduces or eliminates Vos, PSRR, CMRR and TCVos errors

- · System level "calibration" capability

- Application Specific Programming mode

- In-System Programming mode

- Electrically programmable to compensate for external component tolerances

- Achieves 0.01pA input bias current and 35μV input offset voltage simultaneously

- ±1V to ±5V operation

#### **GENERAL DESCRIPTION**

The ALD2726E/ALD2726 is a dual monolithic rail-to-rail precision CMOS operational amplifier with integrated user programmable EPAD (Electrically Programmable Analog Device) based offset voltage adjustment. The ALD2726E/ALD2726 is a dual version of the ALD1726E/ALD2726 operational amplifier. Each ALD2721E/ALD2721 operational amplifier features individual user-programming offset voltage trimming, resulting in significantly enhanced total system performance and user flexibility. EPAD technology is an exclusive ALD design which has been refined for analog applications where precision voltage trimming is necessary to achieve a desired performance. It utilizes CMOS FETs as in-circuit elements for trimming of offset voltage bias characteristics with the aid of a personal computer under software control. Once programmed, the set parameters are stored indefinitely within the device even after power-down. EPAD offers the circuit designer a convenient and cost-effective trimming solution for achieving the very highest amplifier/system performance.

The ALD2726E/ALD2726 dual operational amplifier features rail-to-rail input and output voltage ranges, tolerance to over-voltage input spikes of 300mV beyond supply rails, capacitive loading up to 25pF, extremely low input currents of 0.01pA typical, high open loop voltage gain, useful bandwidth of 700KHz, slew rate of 0.7V/ $\mu s$ , and low typical supply current of  $50\mu A$  for both amplifiers.

### ORDERING INFORMATION

| Оре            | Operating Temperature Range |                 |  |  |  |  |  |  |  |

|----------------|-----------------------------|-----------------|--|--|--|--|--|--|--|

| 0°C to +70°C   | 0°C to +70°C                | -55°C to +125°C |  |  |  |  |  |  |  |

| 14-Pin         | 14-Pin                      | 14-Pin          |  |  |  |  |  |  |  |

| Small Outline  | Plastic Dip                 | CERDIP          |  |  |  |  |  |  |  |

| Package (SOIC) | Package                     | Package         |  |  |  |  |  |  |  |

| ALD2726ESB     | ALD2726EPB                  | ALD2726EDB      |  |  |  |  |  |  |  |

| ALD2726SB      | ALD2726PB                   | ALD2726DB       |  |  |  |  |  |  |  |

<sup>\*</sup> Contact factory for high temperature versions.

### **BENEFITS**

- Eliminates manual and elaborate system trimming procedures

- Remote controlled automated trimming

- · In-System Programming capability

- No external components

- No internal clocking noise source

- Simple and cost effective

- Small package size

- Extremely small total functional volume size

- Low system implementation cost

- Micropower

#### **APPLICATIONS**

- · Sensor interface circuits

- Transducer biasing circuits

- · Capacitive and charge integration circuits

- · Biochemical probe interface

- Signal conditioning

- · Portable instruments

- High source impedance electrode amplifiers

- Precision Sample and Hold amplifiers

- · Precision current to voltage converter

- Error correction circuits

- · Sensor compensation circuits

- Precision gain amplifiers

- Periodic In-system calibration

- System output level shifter

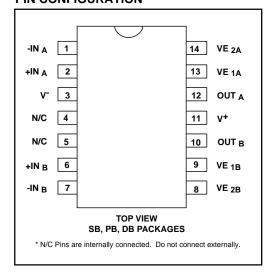

### PIN CONFIGURATION

#### **FUNCTIONAL DESCRIPTION**

The ALD2726E/ALD2726 uses EPADs as in-circuit elements for trimming of offset voltage bias characteristics. Each ALD2726E/ALD2726 has a pair of EPAD-based circuits connected such that one circuit is used to adjust VOS in one direction and the other circuit is used to adjust VOS in the other direction. While each of the EPAD devices is a monotonically adjustable programmable device, the VOS of the ALD2726E can be adjusted many times in both directions. Once programmed, the set VOS levels are stored permanently, even when the device power is removed.

### Functional Description of ALD2726E

The ALD2726E is pre-programmed at the factory under standard operating conditions for minimum equivalent input offset voltage. It also has a guaranteed offset voltage program range, which is ideal for applications that require electrical offset voltage programming.

The ALD2726E is an operational amplifier that can be trimmed with user application-specific programming or insystem programming conditions. User application-specific circuit programming refers to the situation where the Total Input Offset Voltage of the ALD2726E can be trimmed with the actual intended operating conditions.

For example, an application circuit may have +1V and -1V power supplies, and the operational amplifier input is biased at +1V, and an average operating temperature at +85°C. The circuit can be wired up to these conditions within an environmental chamber with the ALD2726E inserted into a test socket connected to this circuit while it is being electrically trimmed. Any error in Vos due to these bias conditions can be automatically zeroed out. The Total Vos error is now limited only by the adjustable range and the stability of Vos, and the input noise voltage of the operational amplifier. Therefore, this Total Vos error now includes Vos as Vos is traditionally specified; plus the Vos error contributions from PSRR, CMRR, TCVos, and noise. Typically this total Vos error (Vost) is approximately ±35μV for the ALD2726E.

In-System Programming refers to the condition where the EPAD adjustment is made after the ALD2726E has been inserted into a circuit board. In this case, the circuit design must provide for the ALD2721E to operate in normal mode and in programming mode. One of the benefits of in-system programming is that not only is the ALD2726E offset voltage from operating bias conditions accounted for, any residual errors introduced by other circuit components, such as resistor or sensor induced voltage errors, can also be corrected. In this way, the "in-system" circuit output can be adjusted to a desired level, eliminating the need for another trimming function.

### **Functional Description of ALD2726**

The ALD2726 is pre-programmed at the factory under standard operating conditions for minimum equivalent input off-set voltage. The ALD2726 offers similar programmable features as the ALD2726E, but with a more limited offset voltage program range. In is intended for standard operational amplifier applications, where little or no electrical porggramming by the user is necessary.

### USER PROGRAMMABLE VOS FEATURE

Each ALD2726E/ALD2726 has four additional pins, compared to a conventional dual operational amplifier which has eight pins. These four additional pins are named VE1A, VE2A for op amp A and VE1B, VE2B for op amp B. Each of these pins VE1A, VE2A, VE1B, VE2B (represented by VExx) are connected to a separate, internal offset bias circuit. VExx pins have initial internal bias voltage values of approximately 1V to 2V. The voltage on these pins can be programmed using the ALD E100 EPAD Programmer and the appropriate Adapter Module. The useful programming range of voltages on VExx pins are 1V to 3V.

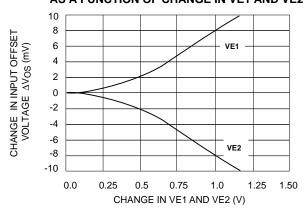

VExx pins are programming pins, used during electrical programming mode to inject charge into the internal EPADs. Increasing voltage on VE1A/VE1B increases the offset voltage whereas increasing voltage on VE2A/VE2B decreases the offset voltage of op amp A and op amp B, respectively. The injected charge is then permanently stored. After programming, VExx pins must be left open in order for these voltages to remain at the programmed levels.

During programming, voltages on VExx pins are increased incrementally to program the offset voltage of the operational amplifier to the desired VOS. Note that desired VOS can be any value within the offset voltage programmable ranges, and can be equal zero, a positive value or a negative value. This VOS value can also be reprogrammed to a different value at a later time, provided that the useful VE1x or VE2x programming voltage range has not been exceeded. VExx pins can also serve as capacitively coupled input pins.

Internally, VE1 and VE2 are programmed and connected differentially. Temperature drift effects between the two internal offset bias circuits cancel each other and introduce less net temperature drift coefficient change than offset voltage trimming techniques such as offset adjustment with an external trimmer potentiometer.

While programming, V+, VE1 and VE2 pins may be alternately pulsed with 12V (approximately) pulses generated by the EPAD Programmer. In-system programming requires the ALD2726E application circuit to accommodate these programming pulses. This can be accomplished by adding resistors at certain appropriate circuit nodes. For more information, see Application Note AN1700.

### **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage, V+               |                 | 10.6V             |

|----------------------------------|-----------------|-------------------|

| Differential input voltage range |                 | -0.3V to V+ +0.3V |

| Power dissipation                |                 | 600 mW            |

| Operating temperature range      | SB, PB packages | 0°C to +70°C      |

|                                  | DB package      | 55°C to +125°C    |

| Storage temperature range        |                 | 65°C to +150°C    |

| Lead temperature, 10 seconds     |                 | +260°C            |

**CAUTION:** ESD Sensitive Device. Use static control procedures in ESD controlled environment.

# OPERATING ELECTRICAL CHARACTERISTICS $T_A = 25$ °C $V_S = \pm 2.5$ V unless otherwise specified

|                                                       |                   | 2726E        |                | 2726         |              |                |              |              |                                                                         |

|-------------------------------------------------------|-------------------|--------------|----------------|--------------|--------------|----------------|--------------|--------------|-------------------------------------------------------------------------|

| Parameter                                             | Symbol            | Min          | Тур            | Max          | Min          | Тур            | Max          | Unit         | Test Conditions                                                         |

| Supply Voltage                                        | VS<br>V+          | ±1.0<br>2.0  |                | ±5.0<br>10.0 | ±1.0<br>2.0  |                | ±5.0<br>10.0 | V<br>V       | Dual Supply<br>Single Supply                                            |

| Initial Input Offset Voltage <sup>1</sup>             | Vosi              |              | 35             | 100          |              | 50             | 150          | μV           | R <sub>S</sub> ≤ 100KΩ                                                  |

| Offset Voltage Program Range <sup>2</sup>             | ΔVOS              | ±7           | ±15            |              | ±0.7         | ±4             |              | mV           |                                                                         |

| Programmed Input Offset<br>Voltage Error <sup>3</sup> | Vos               |              | 50             | 100          |              | 50             | 150          | μV           | At user specified target offset voltage                                 |

| Total Input Offset Voltage 4                          | Vost              |              | 50             | 100          |              | 50             | 150          | μV           | At user specified target offset voltage                                 |

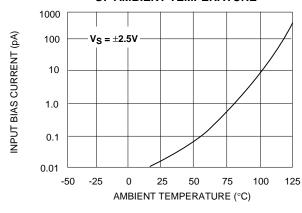

| Input Offset Current <sup>5</sup>                     | los               |              | 0.01           | 10<br>240    |              | 0.01           | 10<br>240    | pA<br>pA     | $T_A = 25^{\circ}C$<br>$0^{\circ}C \le T_A \le +70^{\circ}C$            |

| Input Bias Current <sup>5</sup>                       | lΒ                |              | 0.01           | 10<br>240    |              | 0.01           | 10<br>240    | pA<br>pA     | $T_A = 25^{\circ}C$<br>$0^{\circ}C \le T_A \le +70^{\circ}C$            |

| Input Voltage Range <sup>6</sup>                      | VIR               | -0.3<br>-2.8 |                | 5.3<br>+2.8  | -0.3<br>-2.8 |                | 5.3<br>+2.8  | V<br>V       | V+ = +5V<br>VS = ±2.5V                                                  |

| Input Resistance                                      | R <sub>IN</sub>   |              | 1014           |              |              | 1014           |              | Ω            |                                                                         |

| Input Offset Voltage Drift 7                          | TCVOS             |              | 7              |              |              | 7              |              | μV/°C        | R <sub>S</sub> ≤100KΩ                                                   |

| Initial Power Supply Rejection Ratio 8                | PSRR <sub>i</sub> |              | 90             |              |              | 90             |              | dB           | R <sub>S</sub> ≤100KΩ                                                   |

| Initial Common Mode<br>Rejection Ratio <sup>8</sup>   | CMRRi             |              | 90             |              |              | 90             |              | dB           | RS ≤100KΩ                                                               |

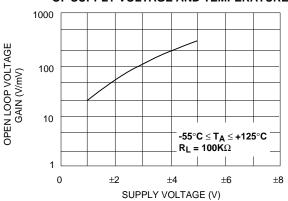

| Large Signal Voltage Gain                             | AV                | 15<br>10     | 100            |              | 15<br>10     | 100            |              | V/mV<br>V/mV | RL =100K $\Omega$<br>0°C ≤ TA ≤ +70°C                                   |

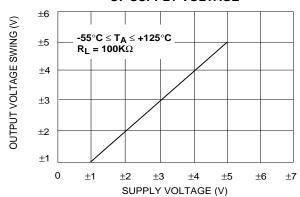

| Output Voltage Range                                  | VO low            | 4.99         | 0.001<br>4.999 | 0.01         | 4.99         | 0.001<br>4.999 | 0.01         | V<br>V       | R <sub>L</sub> =1M $\Omega$ V =5V<br>0°C ≤ T <sub>A</sub> ≤ +70°C       |

|                                                       | VO low            | 2.40         | -2.48<br>2.48  | -2.40        | 2.40         | -2.48<br>2.48  | -2.40        | V<br>V       | R <sub>L</sub> =100K $\Omega$<br>0°C $\leq$ T <sub>A</sub> $\leq$ +70°C |

| Output Short Circuit Current                          | Isc               |              | 200            |              |              | 200            |              | μА           |                                                                         |

<sup>\*</sup> NOTES 1 through 9, see section titled "Definitions and Design Notes".

## **OPERATING ELECTRICAL CHARACTERISTICS (cont'd)**

$T_A = 25$ °C  $V_S = \pm 2.5$ V unless otherwise specified

|                                |                 |     | 2726E |     |     | 2726 |     |                    |                                                                             |

|--------------------------------|-----------------|-----|-------|-----|-----|------|-----|--------------------|-----------------------------------------------------------------------------|

| Parameter                      | Symbol          | Min | Тур   | Max | Min | Тур  | Max | Unit               | Test Conditions                                                             |

| Supply Current                 | IS              |     | 50    | 80  |     | 50   | 80  | μА                 | V <sub>IN</sub> = 0V<br>No Load                                             |

| Power Dissipation              | PD              |     |       | 400 |     |      | 400 | mW                 | V <sub>S</sub> = ±2.5V                                                      |

| Input Capacitance              | C <sub>IN</sub> |     | 1     |     |     | 1    |     | pF                 |                                                                             |

| Maximum Load Capacitance       | CL              |     | 25    |     |     | 25   |     | pF                 |                                                                             |

| Equivalent Input Noise Voltage | en              |     | 55    |     |     | 55   |     | nV/√Hz             | f = 1KHz                                                                    |

| Equivalent Input Noise Current | in              |     | 0.6   |     |     | 0.6  |     | fA/√ <del>Hz</del> | f =10Hz                                                                     |

| Bandwidth                      | BW              |     | 200   |     |     | 200  |     | KHz                |                                                                             |

| Slew Rate                      | SR              |     | 0.1   |     |     | 0.1  |     | V/μs               | AV = +1<br>$R_L = 100K\Omega$                                               |

| Rise time                      | tr              |     | 1.0   |     |     | 1.0  |     | μs                 | RL = 100KΩ                                                                  |

| Overshoot Factor               |                 |     | 20    |     |     | 20   |     | %                  | RL=100KΩ<br>CL=50pF                                                         |

| Settling Time                  | ts              |     | 10    |     |     | 10   |     | μs                 | 0.1% A <sub>V</sub> = -1<br>R <sub>L</sub> = 100KΩ<br>C <sub>L</sub> = 50pF |

| Channel Separation             | CS              |     | 140   |     |     | 140  |     | dB                 | Ay =100                                                                     |

$T_A = 25$ °C  $V_S = \pm 2.5$ V unless otherwise specified

|                                                    |                                                  |     | 2726E |     |     | 2726 |     |                 |                 |

|----------------------------------------------------|--------------------------------------------------|-----|-------|-----|-----|------|-----|-----------------|-----------------|

| Parameter                                          | Symbol                                           | Min | Тур   | Max | Min | Тур  | Max | Unit            | Test Conditions |

| Average Long Term Input Offset Voltage Stability 9 | $\frac{\Delta \text{ VOS}}{\Delta \text{ time}}$ |     | 0.02  |     |     | 0.02 |     | μV/<br>1000 hrs |                 |

| Initial VE Voltage                                 | VE1 j, VE2 j                                     |     | 1.5   |     |     | 1.8  |     | ٧               |                 |

| Programmable Change of VE Range                    | ΔVE1, ΔVE2                                       | 0.5 | 1.0   |     |     | 0.5  |     | V               |                 |

| Programmed VE Voltage Error                        | e(VE1-VE2)                                       |     | 0.1   |     |     | 0.1  |     | %               |                 |

| VE Pin Leakage Current                             | i <sub>eb</sub>                                  |     | -5    |     |     | -5   |     | μА              |                 |

<sup>\*</sup> NOTES 1 through 9, see section titled "Definitions and Design Notes".

## **OPERATING ELECTRICAL CHARACTERISTICS (cont'd)**

$V_{\mbox{\scriptsize S}}$  =  $\pm 2.5 \mbox{\scriptsize V}$  -55°C  $\leq$   $T_{\mbox{\scriptsize A}} \leq$  +125°C unless otherwise specified

|                                                     |                   |      | 2726E         |       |      | 2726          |       |        |                        |

|-----------------------------------------------------|-------------------|------|---------------|-------|------|---------------|-------|--------|------------------------|

| Parameter                                           | Symbol            | Min  | Тур           | Max   | Min  | Тур           | Max   | Unit   | Test Conditions        |

| Initial Input offset Voltage                        | Vosi              |      | 0.7           |       |      | 0.7           |       | mV     | R <sub>S</sub> ≤ 100KΩ |

| Input Offset Current                                | los               |      |               | 2.0   |      |               | 2.0   | nA     |                        |

| Input Bias Current                                  | IB                |      |               | 2.0   |      |               | 2.0   | nA     |                        |

| Initial Power Supply Rejection Ratio 8              | PSRR <sub>i</sub> |      | 85            |       |      | 85            |       | dB     | R <sub>S</sub> ≤ 100KΩ |

| Initial Common Mode<br>Rejection Ratio <sup>8</sup> | CMRR <sub>i</sub> |      | 83            |       |      | 83            |       | dB     | R <sub>S</sub> ≤ 100KΩ |

| Large Signal Voltage Gain                           | AV                | 15   | 50            |       | 15   | 50            |       | V/mV   | $R_L = 1M\Omega$       |

| Output Voltage Range                                | VO low<br>VO high | 2.35 | -2.47<br>2.45 | -2.40 | 2.35 | -2.47<br>2.45 | -2.40 | V<br>V | R <sub>L</sub> = 1MΩ   |

$T_A = 25$ °C  $V_S = \pm 5.0$ V unless otherwise specified

|                                                      |                   |     | 2726E         |      |     | 2726          |      |      |                        |

|------------------------------------------------------|-------------------|-----|---------------|------|-----|---------------|------|------|------------------------|

| Parameter                                            | Symbol            | Min | Тур           | Max  | Min | Тур           | Max  | Unit | Test Conditions        |

| Initial Power Supply<br>Rejection Ratio <sup>8</sup> | PSRR <sub>i</sub> |     | 80            |      |     | 80            |      | dB   | R <sub>S</sub> ≤ 100KΩ |

| Initial Common Mode<br>Rejection Ratio <sup>8</sup>  | CMRRi             |     | 80            |      |     | 80            |      | dB   | R <sub>S</sub> ≤ 100KΩ |

| Large Signal Voltage Gain                            | Ay                |     | 50            |      |     | 50            |      | V/mV | R <sub>L</sub> = 1MΩ   |

| Output Voltage Range                                 | VO low            | 0.9 | -0.95<br>0.95 | -0.9 | 0.9 | -0.95<br>0.95 | -0.9 | V    | $R_L = 1M\Omega$       |

| Bandwidth                                            | BW                |     | 0.2           |      |     | 0.2           |      | MHz  |                        |

| Slew Rate                                            | SR                |     | 1.0           |      |     | 1.0           |      | V/μs | $A_V = +1, C_L = 25pF$ |

#### **DEFINITIONS AND DESIGN NOTES:**

- 1. Initial Input Offset Voltage is the initial offset voltage of the ALD2726E/ALD2726 operational amplifier when shipped from the factory. The device has been pre-programmed and tested for programmability.

- 2. Offset Voltage Program Range is the range of adjustment of user specified target offset voltage. This is typically an adjustment in either the positive or the negative direction of the input offset voltage from an initial input offset voltage. The input offset programming pins, VE1A/VE1B or VE2A/VE2B, change the input offset voltage in the negative or positive direction, for each of the amplifiers, A or B respectively. User specified target offset voltage can be any offset voltage within this programming range.

- 3. Programmed Input Offset Voltage Error is the final offset voltage error after programming when the Input Offset Voltage is at target Offset Voltage. This parameter is sample tested.

- 4. Total Input Offset Voltage is the same as Programmed Input Offset Voltage, corrected for system offset voltage error. Usually this is an all inclusive system offset voltage, which also includes offset voltage contributions from input offset voltage, PSRR, CMRR, TCVOS and noise. It can also include errors introduced by external components, at a system level. Programmed Input Offset Voltage and Total Input Offset Voltage is not necessarily zero offset voltage, but an offset voltage set to compensate for other system errors as well. This parameter is sample tested.

- 5. The Input Offset and Bias Currents are essentially input protection diode reverse bias leakage currents. This low input bias current assures that the analog signal from the source will not be distorted by it. For applications where source impedance is very high, it may be necessary to limit noise and hum pickup through proper shielding.

- 6. Input Voltage Range is determined by two parallel complementary input stages that are summed internally, each stage having a separate input offset voltage. While Total Input Offset Voltage can be trimmed to a desired target value, it is essential to note that this trimming occurs at only one user selected input bias voltage. Depending on the selected input bias voltage relative to the power supply voltages, offset voltage trimming may affect one or both input stages. For the ALD2726E/ALD2726, the switching point between the two stages occurs at approximately 1.5V below positive supply voltage.

- 7. Input Offset Voltage Drift is the average change in Total Input Offset Voltage as a function of ambient temperature. This parameter is sample tested.

- 8. Initial PSRR and initial CMRR specifications are provided as reference information. After programming, error contribution to the offset voltage from PSRR and CMRR is set to zero under the specific power supply and common mode conditions, and becomes part of the Programmed Input Offset Voltage Error.

- 9. Average Long Term Input Offset Voltage Stability is based on input offset voltage shift through operating life test at 125°C extrapolated to TA = 25°C, assuming activation energy of 1.0eV. This parameter is sample tested.

#### **ADDITIONAL DESIGN NOTES:**

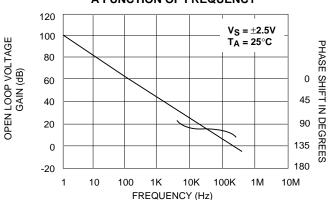

- A. The ALD2726E/ALD2726 is internally compensated for unity gain stability using a novel scheme which produces a single pole role off in the gain characteristics while providing more than 70 degrees of phase margin at unity gain frequency. A unity gain buffer using the ALD2726E/ALD2726 will typically drive 25pF of external load capacitance.

- B. The ALD2726E/ALD2726 has complementary p-channel and n-channel input differential stages connected in parallel to accomplish rail-to-rail input common mode voltage range. The switching point between the two differential stages is 1.5V below positive supply voltage. For applications such as inverting amplifiers or non-inverting amplifiers with a gain larger than 2.5 (5V operation), the common mode voltage does not make excursions below this switching point. However, this switching does take place if the operational amplifier is connected as a rail-to-rail unity gain buffer and the design must allow for input offset voltage variations.

- C. The output stage consists of class AB complementary output drivers. The oscillation resistant feature, combined with the rail-to-rail input and output feature, makes the ALD2726E/ALD2726 an effective analog signal buffer for high source impedance sensors, transducers, and other circuit networks.

- D. The ALD2726E/ALD2726 has static discharge protection. However, care must be exercised when handling the device to avoid strong static fields that may degrade a diode junction, causing increased input leakage currents. The user is advised to power up the circuit before, or simultaneously with, any input voltages applied and to limit input voltages not to exceed 0.3V of the power supply voltage levels.

- E. VExx are high impedance terminals, as the internal bias currents are set very low to a few microamperes to conserve power. For some applications, these terminals may need to be shielded from external coupling sources. For example, digital signals running nearby may cause unwanted offset voltage fluctuations. Care during the printed circuit board layout, to place ground traces around these pins and to isolate them from digital lines, will generally eliminate such coupling effects. In addition, optional decoupling capacitors of 1000pF or greater value can be added to VExx terminals.

- F. The ALD2726E/ALD2726 is designed for use in low voltage, micropower circuits. The maximum operating voltage during normal operation should remain below 10V at all times. Care should be taken to insure that the application in which the device is used does not experience any positive or negative transient voltages that will cause any of the terminal voltages to exceed this limit.

- G. All inputs or unused pins except VExx pins should be connected to a supply voltage such as Ground so that they do not become floating pins, since input impedance at these pins is very high. If any of these pins are left undefined, they may cause unwanted oscillation or intermittent excessive current drain. As these devices are built with CMOS technology, normal operating and storage temperature limits, ESD and latchup handling precautions pertaining to CMOS device handling should be observed.

### TYPICAL PERFORMANCE CHARACTERISTICS

## OPEN LOOP VOLTAGE GAIN AS A FUNCTION OF SUPPLY VOLTAGE AND TEMPERATURE

## OUTPUT VOLTAGE SWING AS A FUNCTION OF SUPPLY VOLTAGE

## INPUT BIAS CURRENT AS A FUNCTION OF AMBIENT TEMPERATURE

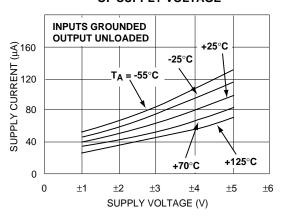

## SUPPLY CURRENT AS A FUNCTION OF SUPPLY VOLTAGE

### ADJUSTMENT IN INPUT OFFSET VOLTAGE AS A FUNCTION OF CHANGE IN VE1 AND VE2

## OPEN LOOP VOLTAGE GAIN AS A FUNCTION OF FREQUENCY

### TYPICAL PERFORMANCE CHARACTERISTICS (cont'd)

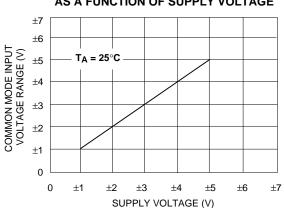

COMMON MODE INPUT VOLTAGE RANGE AS A FUNCTION OF SUPPLY VOLTAGE

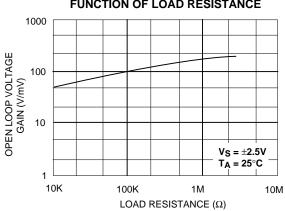

OPEN LOOP VOLTAGE GAIN AS A FUNCTION OF LOAD RESISTANCE

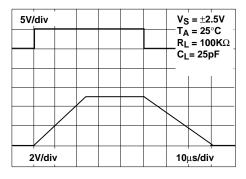

LARGE - SIGNAL TRANSIENT RESPONSE

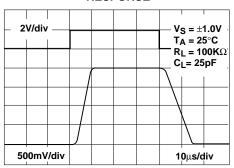

LARGE - SIGNAL TRANSIENT RESPONSE

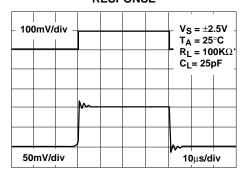

SMALL - SIGNAL TRANSIENT RESPONSE

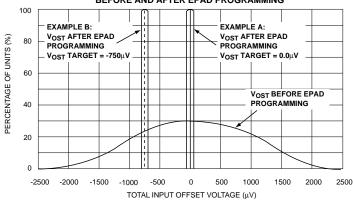

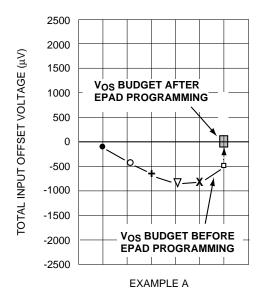

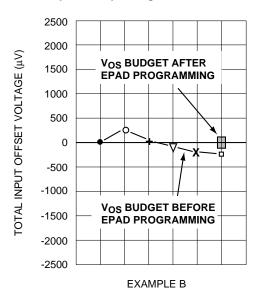

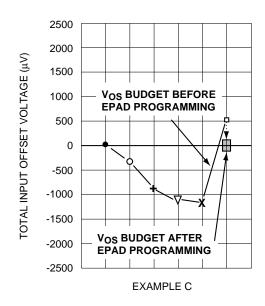

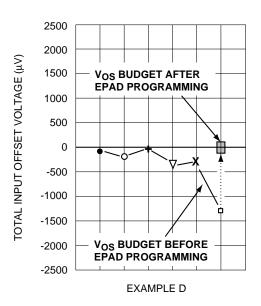

DISTRIBUTION OF TOTAL INPUT OFFSET VOLTAGE BEFORE AND AFTER EPAD PROGRAMMING

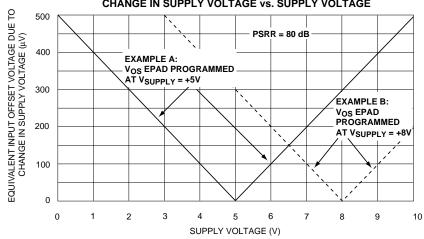

### TYPICAL PERFORMANCE CHARACTERISTICS (cont'd)

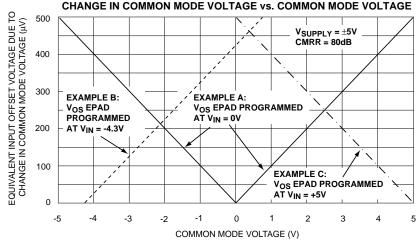

## THREE EXAMPLES OF EQUIVALENT INPUT OFFSET VOLTAGE DUE TO CHANGE IN COMMON MODE VOLTAGE vs. COMMON MODE VOLTAGE

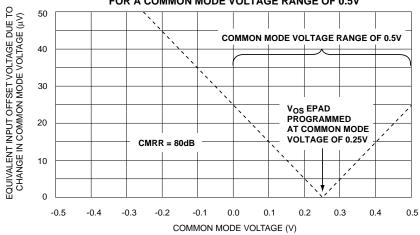

### EXAMPLE OF MINIMIZING EQUIVALENT INPUT OFFSET VOLTAGE FOR A COMMON MODE VOLTAGE RANGE OF 0.5V

### TYPICAL PERFORMANCE CHARACTERISTICS (cont'd)

### **APPLICATION SPECIFIC / IN-SYSTEM PROGRAMMING**

Examples of applications where accumulated total input offset voltage from various contributing sources is minimized under different sets of user-specified operating conditions

Device input V<sub>OS</sub>

PSRR equivalent V<sub>OS</sub>

+ CMRR equivalent V<sub>OS</sub>

∇ T<sub>A</sub> equivalent V<sub>OS</sub>

X Noise equivalent V<sub>OS</sub>

External Error equivalent V<sub>OS</sub>

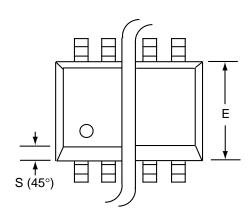

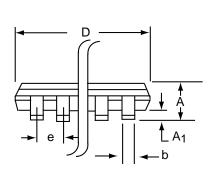

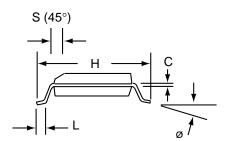

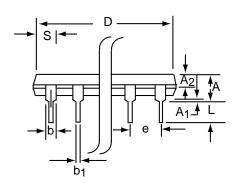

## **SOIC-14 PACKAGE DRAWING**

### 14 Pin Plastic SOIC Package

|                | Millin | neters | Inc   | hes   |

|----------------|--------|--------|-------|-------|

| Dim            | Min    | Max    | Min   | Max   |

| Α              | 1.35   | 1.75   | 0.053 | 0.069 |

| A <sub>1</sub> | 0.10   | 0.25   | 0.004 | 0.010 |

| b              | 0.35   | 0.45   | 0.014 | 0.018 |

| С              | 0.18   | 0.25   | 0.007 | 0.010 |

| D-14           | 8.55   | 8.75   | 0.336 | 0.345 |

| E              | 3.50   | 4.05   | 0.140 | 0.160 |

| е              | 1.27   | BSC    | 0.050 | BSC   |

| Н              | 5.70   | 6.30   | 0.224 | 0.248 |

| L              | 0.60   | 0.937  | 0.024 | 0.037 |

| Ø              | 0°     | 8°     | 0°    | 8°    |

| S              | 0.25   | 0.50   | 0.010 | 0.020 |

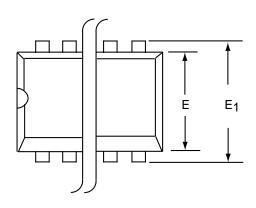

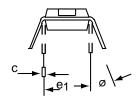

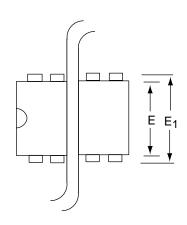

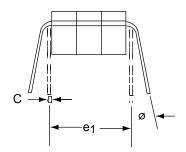

## **PDIP-14 PACKAGE DRAWING**

## 14 Pin Plastic DIP Package

|                | Millin | neters | Inc   | hes   |

|----------------|--------|--------|-------|-------|

| Dim            | Min    | Max    | Min   | Max   |

| Α              | 3.81   | 5.08   | 0.105 | 0.200 |

| A <sub>1</sub> | 0.38   | 1.27   | 0.015 | 0.050 |

| A <sub>2</sub> | 1.27   | 2.03   | 0.050 | 0.080 |

| b              | 0.89   | 1.65   | 0.035 | 0.065 |

| b <sub>1</sub> | 0.38   | 0.51   | 0.015 | 0.020 |

| С              | 0.20   | 0.30   | 0.008 | 0.012 |

| D-14           | 17.27  | 19.30  | 0.680 | 0.760 |

| E              | 5.59   | 7.11   | 0.220 | 0.280 |

| E <sub>1</sub> | 7.62   | 8.26   | 0.300 | 0.325 |

| е              | 2.29   | 2.79   | 0.090 | 0.110 |

| e <sub>1</sub> | 7.37   | 7.87   | 0.290 | 0.310 |

| L              | 2.79   | 3.81   | 0.110 | 0.150 |

| S-14           | 1.02   | 2.03   | 0.040 | 0.080 |

| a              | 0°     | 15°    | 0°    | 15°   |

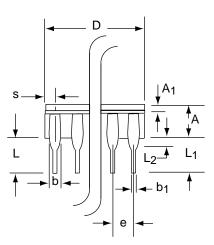

## **CERDIP-14 PACKAGE DRAWING**

## 14 Pin CERDIP Package

|                | Millim | neters | Inc       | hes   |  |

|----------------|--------|--------|-----------|-------|--|

| Dim            | Min    | Max    | Min       | Max   |  |

| Α              | 3.55   | 5.08   | 0.140     | 0.200 |  |

| A <sub>1</sub> | 1.27   | 2.16   | 0.050     | 0.085 |  |

| b              | 0.97   | 1.65   | 0.038     | 0.065 |  |

| b <sub>1</sub> | 0.36   | 0.58   | 0.014     | 0.023 |  |

| С              | 0.20   | 0.38   | 0.008     | 0.015 |  |

| D-14           |        | 19.94  |           | 0.785 |  |

| E              | 5.59   | 7.87   | 0.220     | 0.310 |  |

| E <sub>1</sub> | 7.73   | 8.26   | 0.290     | 0.325 |  |

| е              | 2.54 E | BSC    | 0.100 BSC |       |  |

| e <sub>1</sub> | 7.62 E | BSC    | 0.300     | BSC   |  |

| L              | 3.81   | 5.08   | 0.150     | 0.200 |  |

| L <sub>1</sub> | 3.18   |        | 0.125     |       |  |

| L <sub>2</sub> | 0.38   | 1.78   | 0.015     | 0.070 |  |

| S              |        | 2.49   |           | 0.098 |  |

| Ø              | 0°     | 15°    | 0°        | 15°   |  |