### QUAD/DUAL N-CHANNEL ENHANCEMENT MODE EPAD® PRECISION MATCHED PAIR MOSFET ARRAY

VGS(th) = +1.40V

#### **GENERAL DESCRIPTION**

ALD110814/ALD110914 are high precision monolithic quad/dual enhancement mode N-Channel MOSFETs matched at the factory using ALD's proven EPAD® CMOS technology. These devices are intended for low voltage, small signal applications.

The ALD110814/ALD110914 MOSFETs are designed and built with exceptional device electrical characteristics matching. Since these devices are on the same monolithic chip, they also exhibit excellent tempco tracking characteristics. Each device is versatile as a circuit element and is a useful design component for a broad range of analog applications. They are basic building blocks for current sources, differential amplifier input stages, transmission gates, and multiplexer applications. For most applications, connect the V- and IC pins to the most negative voltage in the system and the V+ pin to the most positive voltage. All other pins must have voltages within these voltage limits at all times.

The ALD110814/ALD110914 devices are built for minimum offset voltage and differential thermal response, and they are designed for switching and amplifying applications in +1.5V to +10V systems where low input bias current, low input capacitance and fast switching speed are desired. Since these are MOSFET devices, they feature very large (almost infinite) current gain in a low frequency, or near DC, operating environment.

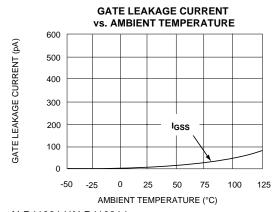

The ALD110814/ALD110914 are suitable for use in precision applications which require very high current gain, beta, such as current mirrors and current sources. The high input impedance and the high DC current gain of the Field Effect Transistors result in extremely low current loss through the control gate. The DC current gain is limited by the gate input leakage current, which is specified at 30pA at room temperature. For example, DC beta of the device at a drain current of 3mA and input leakage current of 30pA at 25°C is = 3mA/30pA = 100,000,000.

#### **FEATURES**

- Enhancement-mode (normally off)

- Standard Gate Threshold Voltages: +1.40V

- Matched MOSFET to MOSFET characteristics

- Tight lot to lot parametric control

- Parallel connection of MOSFETs to increase drain currents

- Low input capacitance

- VGS(th) match to 10mV

- High input impedance  $10^2\Omega$  typical

- Positive, zero, and negative \GS(th) temperature coefficient

- DC current gain >109

- Low input and output leakage currents

### ORDERING INFORMATION ("L" suffix denotes lead-free (RoHS))

| 0°C to                    | Operating Temp<br>+70°C          | erature Range*<br>0°C to +7 | 70°C                            |

|---------------------------|----------------------------------|-----------------------------|---------------------------------|

| 16-Pin<br>SOIC<br>Package | 16-Pin<br>Plastic Dip<br>Package | 8-Pin<br>SOIC<br>Package    | 8-Pin<br>Plastic Dip<br>Package |

| ALD110814SCL              | ALD110814PCL                     | ALD110914SA                 | L ALD110914PAL                  |

<sup>\*</sup> Contact factory for industrial temp. range or user-specified threshold voltage values.

#### **APPLICATIONS**

- · Precision current mirrors

- · Precision current sources

- Voltage choppers

- Differential amplifier input stages

- Discrete voltage comparators

- · Voltage bias circuits

- Sample and Hold circuits

- Analog inverters

- · Level shifters

- Source followers and buffers

- Current multipliers

- · Discrete analog multiplexers/matrices

- Discrete analog switches

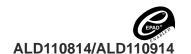

#### **PIN CONFIGURATION**

#### **ABSOLUTE MAXIMUM RATINGS**

| Drain-Source voltage, V <sub>DS</sub>                  | 10.6V           |

|--------------------------------------------------------|-----------------|

| Gate-Source voltage, VGS                               | 10.6V           |

| Power dissipation                                      | 500 mW          |

| Operating temperature range SCL, PCL, SAL, PAL package | 0°C to +70°C    |

| Storage temperature range                              | -65°C to +150°C |

| Lead temperature, 10 seconds                           | +260°C          |

CAUTION: ESD Sensitive Device. Use static control procedures in ESD controlled environment.

# OPERATING ELECTRICAL CHARACTERISTICS $V^+ = +5V \quad V^- = GND \quad T_A = 25^{\circ}C \ unless \ otherwise \ specified$

|                                           |                   | ALD110814/ALD110914 |                     |          |          |                                                                                                                         |

|-------------------------------------------|-------------------|---------------------|---------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------|

| Parameter                                 | Symbol            | Min                 | Тур                 | Max      | Unit     | Test Conditions                                                                                                         |

| Gate Threshold Voltage                    | VGS(th)           | 1.38                | 1.40                | 1.42     | V        | $I_{DS} = 1\mu A, V_{DS} = 0.1V$                                                                                        |

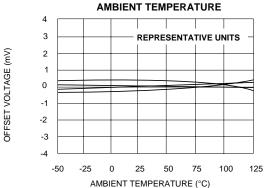

| Offset Voltage<br>VGS(th)1-VGS(th)2       | Vos               |                     | 3                   | 10       | mV       | IDS = 1μA                                                                                                               |

| Offset VoltageTempco                      | TC <sub>VOS</sub> |                     | 5                   |          | μV/°C    | V <sub>DS1</sub> = V <sub>DS2</sub>                                                                                     |

| GateThreshold Voltage Tempco              | TCVGS(th)         |                     | -1.7<br>0.0<br>+1.6 |          | mV/ °C   | $\begin{split} &ID = 1 \mu A,  VDS = 0.1 V \\ &ID = 20 \mu A,  VDS = 0.1 V \\ &ID = 40 \mu A,  VDS = 0.1 V \end{split}$ |

| On Drain Current                          | IDS (ON)          |                     | 12.0<br>3.0         |          | mA       | VGS = +10.6V, VDS = +5V<br>VGS = +5.4V, VDS = +5V                                                                       |

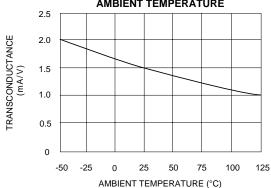

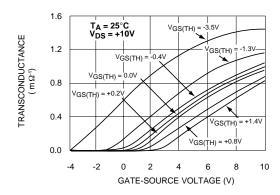

| Forward Transconductance                  | GFS               |                     | 1.4                 |          | mmho     | VGS = +5.4V<br>VDS = +10.4V                                                                                             |

| Transconductance Mismatch                 | ΔGFS              |                     | 1.8                 |          | %        |                                                                                                                         |

| Output Conductance                        | GOS               |                     | 68                  |          | μmho     | VGS = +5.4V<br>VDS = +10.4V                                                                                             |

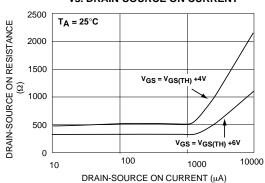

| Drain Source On Resistance                | RDS (ON)          |                     | 500                 |          | Ω        | V <sub>DS</sub> = +0.1V<br>V <sub>GS</sub> = +5.6V                                                                      |

| Drain Source On Resistance<br>Mismatch    | ΔRDS (ON)         |                     | 0.5                 |          | %        |                                                                                                                         |

| Drain Source Breakdown<br>Voltage         | BVDSX             | 10                  |                     |          | V        | IDS = 1.0μA<br>VGS = +0.4V                                                                                              |

| Drain Source Leakage Current <sup>1</sup> | IDS (OFF)         |                     | 10                  | 400      | рА       | VGS = +0.4V, VDS =+5V<br>V- = -5V                                                                                       |

|                                           |                   |                     |                     | 4        | nA       | T <sub>A</sub> = 125°C                                                                                                  |

| Gate Leakage Current <sup>1</sup>         | IGSS              |                     | 3                   | 200<br>1 | pA<br>nA | VDS = 0V, VGS = 5V<br>T <sub>A</sub> =125°C                                                                             |

| Input Capacitance                         | CISS              |                     | 2.5                 |          | pF       |                                                                                                                         |

| Transfer Reverse Capacitance              | C <sub>RSS</sub>  |                     | 0.1                 |          | pF       |                                                                                                                         |

| Turn-on Delay Time                        | ton               |                     | 10                  |          | ns       | V+ = 5V, R <sub>L</sub> = 5KΩ                                                                                           |

| Turn-off Delay Time                       | toff              |                     | 10                  |          | ns       | V+ = 5V, R <sub>L</sub> = 5KΩ                                                                                           |

| Crosstalk                                 |                   |                     | 60                  |          | dB       | f = 100KHz                                                                                                              |

Notes: <sup>1</sup> Consists of junction leakage currents

# PERFORMANCE CHARACTERISTICS OF EPAD® PRECISION MATCHED PAIR MOSFET FAMILY

ALD1108xx/ALD1109xx/ALD1148xx/ALD1149xx are monolithic quad/dual N-Channel MOSFETs matched at the factory using ALD's proven EPAD® CMOS technology. These devices are intended for low voltage, small signal applications.

ALD's Electrically Programmable Analog Device (EPAD) technology provides the industry's only family of matched transistors with a range of precision threshold values. All members of this family are designed and actively programmed for exceptional matching of device electrical characteristics. Threshold values range from -3.50V Depletion to +3.50V Enhancement devices, including standard products specified at -3.50V, -1.30V, -0.40V, +0.00V, +0.20V, +0.40V, +0.80V, +1.40V, and +3.30V. ALD can also provide any customer desired value between -3.50V and +3.50V. For all these devices, even the depletion and zero threshold transistors, ALD EPAD technology enables the same well controlled turn-off, subthreshold, and low leakage characteristics as standard enhancement mode MOSFETs. With the design and active programming, even units from different batches and different date of manufacture have well matched characteristics. As these devices are on the same monolithic chip, they also exhibit excellent tempco tracking.

This EPAD MOSFET Array product family (EPAD MOSFET) is available in the three separate categories, each providing a distinctly different set of electrical specifications and characteristics. The first category is the ALD110800/ALD110900 Zero-Threshold<sup>TM</sup> mode EPAD MOSFETs. The second category is the ALD1108xx/ALD1109xx enhancement mode EPAD MOSFETs. The third category is the ALD1148xx/ALD1149xx depletion mode EPAD MOSFETs. (The suffix "xx" denotes threshold voltage in 0.1 V steps, for example, xx=08 denotes 0.80V).

The ALD110800/ALD110900 (quad/dual) are EPAD MOSFETs in which the individual threshold voltage of each MOSFET is fixed at zero. The threshold voltage is defined as  $I_{DS}=1 uA @ V_{DS}=0.1 V$  when the gate voltage  $V_{GS}=0.00 V$ . Zero threshold devices operate in the enhancement region when operated above threshold voltage and current level ( $V_{GS}>0.00 V$  and  $I_{DS}>1 uA$ ) and subthreshold region when operated at or below threshold voltage and current level ( $V_{GS}<=0.00 V$  and  $I_{DS}<1 uA$ ). This device, along with other very low threshold voltage members of the product family, constitute a class of EPAD MOSFETs that enable ultra low supply voltage operation and nanopower type of circuit designs, applicable in either analog or digital circuits.

The ALD1108xx/ALD1109xx (quad/dual) product family features precision matched enhancement mode EPAD MOSFET devices, which require a positive bias voltage to turn on. Precision threshold values such as +1.40V, +0.80V, +0.20V are offered. No conductive channel exists between the source and drain at zero applied gate voltage for these devices, except that the +0.20V version has a subthreshold current at about 20nA.

The ALD1148xx/ALD1149xx (quad/dual) features depletion mode EPAD MOSFETs, which are normally-on devices when the gate bias voltage is at zero volt. The depletion mode threshold voltage is at a negative voltage level at which the EPAD MOSFET turns off. Without a supply voltage and/or with  $V_{GS}=0.0V$  the EPAD MOSFET device is already turned on and exhibits a defined and controlled on-resistance between the source and drain terminals.

The ALD1148xx/ALD1149xx depletion mode EPAD MOSFETs are different from most other types of depletion mode MOSFETs and certain types of JFETs in that they do not exhibit high gate leakage

currents and channel/junction leakage currents. When negative signal voltages are applied to the gate terminal, the designer/user can depend on the EPAD MOSFET device to be controlled, modulated and turned off precisely. The device can be modulated and turned-off under the control of the gate voltage in the same manner as the enhancement mode EPAD MOSFET and the same device equations apply.

EPAD MOSFETs are ideal for minimum offset voltage and differential thermal response, and they are used for switching and amplifying applications in low voltage (1V to 10V or +/-0.5V to +/-5V) or ultra low voltage (less than 1V or +/-0.5V) systems. They feature low input bias current (less than 30pA max.), ultra low power (microWatt) or Nanopower (power measured in nanoWatt) operation, low input capacitance and fast switching speed. These devices can be used where a combination of these characteristics are desired.

#### **KEY APPLICATION ENVIRONMENT**

EPAD( MOSFET Array products are for circuit applications in one or more of the following operating environments:

- \* Low voltage: 1V to 10V or +/- 0.5V to +/- 5V

- \* Ultra low voltage: less than 1V or +/- 0.5V

- \* Low power: voltage x current = power measured in microwatt

- \* Nanopower: voltage x current = power measured in nanowatt

- \* Precision matching and tracking of two or more MOSFETs

#### **ELECTRICAL CHARACTERISTICS**

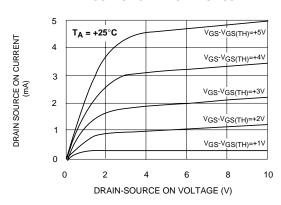

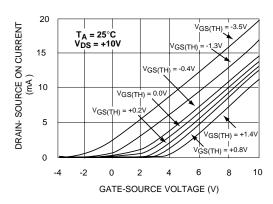

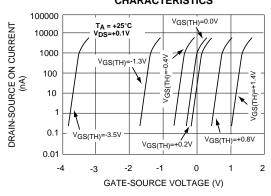

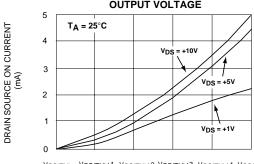

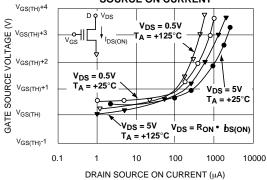

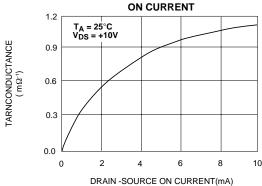

The turn-on and turn-off electrical characteristics of the EPAD MOSFET products are shown in the Drain-Source On Current vs Drain-Source On Voltage and Drain-Source On Current vs Gate-Source Voltage graphs. Each graph show the Drain-Source On Current versus Drain-Source On Voltage characteristics as a function of Gate-Source voltage in a different operating region under different bias conditions. As the threshold voltage is tightly specified, the Drain-Source On Current at a given gate input voltage is better controlled and more predictable when compared to many other types of MOSFETs.

EPAD MOSFETs behave similarly to a standard MOSFET, therefore classic equations for a n-channel MOSFET applies to EPAD MOSFET as well. The Drain current in the linear region ( $V_{DS} < V_{GS} - V_{GS(th)}$ ) is given by:

$I_D = u \cdot C_{OX} \cdot W/L \cdot [V_{GS} - V_{GS(th)} - V_{DS}/2] \cdot V_{DS}$

where:

u = Mobility

$C_{OX}$  = Capacitance / unit area of Gate electrode

$V_{GS}$  = Gate to Source voltage  $V_{GS(th)}$  = Turn-on threshold voltage

V<sub>DS</sub> = Drain to Source voltage

W = Channel width L = Channel length

In this region of operation the IDS value is proportional to VDS value and the device can be used as gate-voltage controlled resistor.

For higher values of  $V_{DS}$  where  $V_{DS} >= V_{GS} - V_{GS(th)}$ , the saturation current  $I_{DS}$  is now given by (approx.):

$I_{DS} = u \cdot C_{OX} \cdot W/L \cdot [V_{GS} - V_{GS(th)}]2$

# PERFORMANCE CHARACTERISTICS OF EPAD® PRECISION MATCHED PAIR MOSFET FAMILY (cont.)

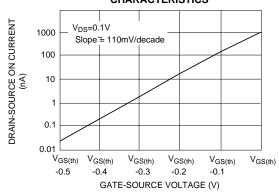

#### SUB-THRESHOLD REGION OF OPERATION

Low voltage systems, namely those operating at 5V, 3.3V or less, typically require MOSFETs that have threshold voltage of 1V or less. The threshold, or turn-on, voltage of the MOSFET is a voltage below which the MOSFET conduction channel rapidly turns off. For analog designs, this threshold voltage directly affects the operating signal voltage range and the operating bias current levels.

At or below threshold voltage, an EPAD MOSFET exhibits a turnoff characteristic in an operating region called the subthreshold region. This is when the EPAD MOSFET conduction channel rapidly turns off as a function of decreasing applied gate voltage. The conduction channel induced by the gate voltage on the gate electrode decreases exponentially and causes the drain current to decrease exponentially. However, the conduction channel does not shut off abruptly with decreasing gate voltage, but decreases at a fixed rate of approximately 116mV per decade of drain current decrease. Thus if the threshold voltage is +0.20V, for example, the drain current is 1uA at  $V_{GS} = +0.20$ V. At  $V_{GS} = +0.09$ V, the drain current would decrease to 0.1uA. Extrapolating from this, the drain current is 0.01uA(10nA) at  $V_{GS} = -0.03V$ , 1nA at  $V_{GS} = -0.14V$ , and so forth. This subthreshold characteristic extends all the way down to current levels below 1nA and is limited by other currents such as junction leakage currents.

At a drain current to be declared "zero current" by the user, the Vgs voltage at that zero current can now be estimated. Note that using the above example, with  $V_{GS(th)} = +0.20V$ , the drain current still hovers around 20nA when the gate is at zero volt, or ground.

#### LOW POWER AND NANOPOWER

When supply voltages decrease, the power consumption of a given load resistor decreases as the square of the supply voltage. So one of the benefits in reducing supply voltage is to reduce power consumption. While decreasing power supply voltages and power consumption go hand-in-hand with decreasing useful AC bandwidth and at the same time increases noise effects in the circuit, a circuit designer can make the necessary tradeoffs and adjustments in any given circuit design and bias the circuit accordingly.

With EPAD MOSFETs, a circuit that performs a specific function can be designed so that power consumption can be minimized. In some cases, these circuits operate in low power mode where the power consumed is measure in micro-watts. In other cases, power dissipation can be reduced to nano-watt region and still provide a useful and controlled circuit function operation.

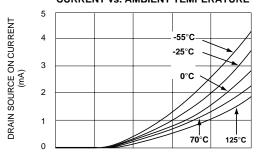

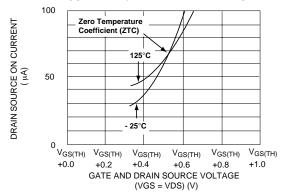

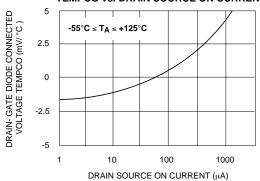

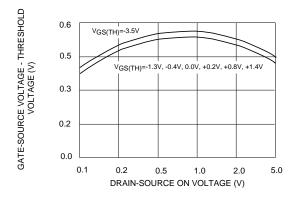

#### ZERO TEMPERATURE COEFFICIENT (ZTC) OPERATION

For an EPAD MOSFET in this product family, there exist operating points where the various factors that cause the current to increase as a function of temperature balance out those that cause the current to decrease, thereby canceling each other, and resulting in net temperature coefficient of near zero. One of this temperature stable operating point is obtained by a ZTC voltage bias condition, which is 0.55V above a threshold voltage when VGS = VDS, resulting in a temperature stable current level of about 68uA. For other ZTC operating points, see ZTC characteristics.

#### PERFORMANCE CHARACTERISTICS

Performance characteristics of the EPAD MOSFET product family are shown in the following graphs. In general, the threshold voltage shift for each member of the product family causes other affected electrical characteristics to shift with an equivalent linear shift in  $V_{GS(th)}$  bias voltage. This linear shift in  $V_{GS}$  causes the subthreshold I-V curves to shift linearly as well. Accordingly, the subthreshold operating current can be determined by calculating the gate voltage drop relative from its threshold voltage,  $V_{GS(th)}$ .

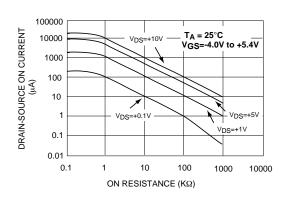

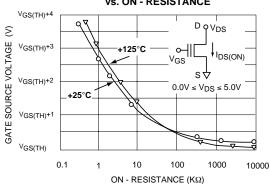

#### RDS(ON) AT VGS=GROUND

Several of the EPAD MOSFETs produce a fixed resistance when their gate is grounded. For ALD110800, the drain current at  $V_{DS} = 0.1 \text{V}$  is at 1uA at  $V_{GS} = 0.0 \text{V}$ . Thus just by grounding the gate of the ALD110800, a resistor with  $R_{DS(ON)} = \sim \!\! 100 \text{KOhm}$  is produced. When an ALD114804 gate is grounded, the drain current  $I_{DS} = 18.5$  uA@  $V_{DS} = 0.1 \text{V}$ , producing  $R_{DS(ON)} = 5.4 \text{KOhm}$ . Similarly, ALD114813 and ALD114835 produces 77uA and 185uA, respectively, at  $V_{GS} = 0.0 \text{V}$ , producing  $R_{DS(ON)}$  values of 1.3 KOhm and 540Ohm, respectively.

#### **MATCHING CHARACTERISTICS**

A key benefit of using matched-pair EPAD MOSFET is to maintain temperature tracking. In general, for EPAD MOSFET matched pair devices, one device of the matched pair has gate leakage currents, junction temperature effects, and drain current temperature coefficient as a function of bias voltage that cancel out similar effects of the other device, resulting in a temperature stable circuit. As mentioned earlier, this temperature stability can be further enhanced by biasing the matched-pairs at Zero Tempco (ZTC) point, even though that could require special circuit configuration and power consumption design consideration.

#### TYPICAL PERFORMANCE CHARACTERISTICS

#### **OUTPUT CHARACTERISTICS**

## DRAIN-SOURCE ON RESISTANCE vs. DRAIN-SOURCE ON CURRENT

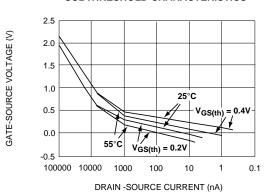

#### FORWARD TRANSFER CHARACTERISTICS

# TRANSCONDUCTANCE vs. AMBIENT TEMPERATURE

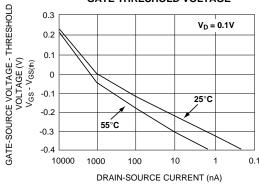

#### SUBTHRESHOLD FORWARD TRANSFER CHARACTERISTICS

## SUBTHRESHOLD FORWARD TRANSFER CHARACTERISTICS

### **TYPICAL PERFORMANCE CHARACTERISTICS (cont.)**

#### DRAIN SOURCE ON CURRENT, BIAS CURRENT vs. AMBIENT TEMPERATURE

VGS(TH)-1 VGS(TH) VGS(TH)+1 VGS(TH)+2 VGS(TH)+3 VGS(TH)+4

GATE AND DRAIN SOURCE VOLTAGE

(VGS = VDS) (V)

#### DRAIN-SOURCE ON CURRENT vs. ON RESISTANCE

## DRAIN SOURCE ON CURRENT vs. OUTPUT VOLTAGE

$\begin{array}{ccccc} \text{V}_{\text{GS(TH)}} & \text{V}_{\text{GS(TH)}+1} & \text{V}_{\text{GS(TH)}+2} & \text{V}_{\text{GS(TH)}+3} & \text{V}_{\text{GS(TH)}+4} & \text{V}_{\text{GS(TH)}+5} \\ & & \text{OUTPUT VOLTAGE (V)} \end{array}$

#### DRAIN SOURCE ON CURRENT, BIAS CURRENT vs. AMBIENT TEMPERATURE

## GATE SOURCE VOLTAGE vs. DRAIN SOURCE ON CURRENT

## OFFSET VOLTAGE vs.

## GATE SOURCE VOLTAGE vs. ON - RESISTANCE

### **TYPICAL PERFORMANCE CHARACTERISTICS (cont.)**

## DRAIN - GATE DIODE CONNECTED VOLTAGE TEMPCO vs. DRAIN SOURCE ON CURRENT

#### TRANSFER CHARACTERISTICS

#### ZERO TEMPERETURE COEFFICIENT CHARACTERISTIC

#### SUBTHRESHOLD CHARACTERISTICS

## TRANCONDUCTANCE vs. DRAIN-SOURCE

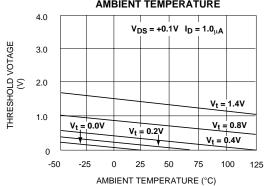

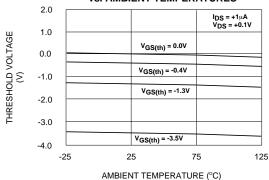

THRESHOLD VOLTAGE vs.

AMBIENT TEMPERATURE

#### NORMALIZED SUBTHRESHOLD CHARACTERISTICS RELATIVE GATE THRESHOLD VOLTAGE

ALD110814/ALD110914

THRESHOLD VOLTAGES vs. AMBIENT TEMPERATURES

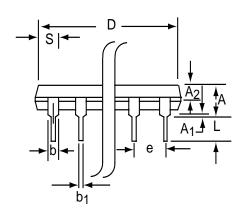

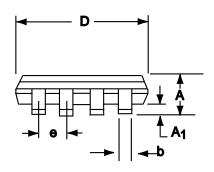

### **SOIC-16 PACKAGE DRAWING**

## 16 Pin Plastic SOIC Package

|                | Millimeters |       | Inches    |       |

|----------------|-------------|-------|-----------|-------|

| Dim            | Min         | Max   | Min       | Max   |

| Α              | 1.35        | 1.75  | 0.053     | 0.069 |

| A <sub>1</sub> | 0.10        | 0.25  | 0.004     | 0.010 |

| b              | 0.35        | 0.45  | 0.014     | 0.018 |

| С              | 0.18        | 0.25  | 0.007     | 0.010 |

| D-16           | 9.80        | 10.00 | 0.385     | 0.394 |

| E              | 3.50        | 4.05  | 0.140     | 0.160 |

| е              | 1.27 BSC    |       | 0.050 BSC |       |

| н              | 5.70        | 6.30  | 0.224     | 0.248 |

| L              | 0.60        | 0.937 | 0.024     | 0.037 |

| Ø              | 0°          | 8°    | 0°        | 8°    |

| s              | 0.25        | 0.50  | 0.010     | 0.020 |

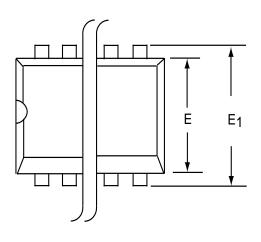

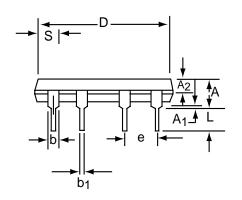

### **PDIP-16 PACKAGE DRAWING**

## 16 Pin Plastic DIP Package

|                | Millimeters |       | Inches |       |

|----------------|-------------|-------|--------|-------|

| Dim            | Min         | Max   | Min    | Max   |

| Α              | 3.81        | 5.08  | 0.105  | 0.200 |

| A <sub>1</sub> | 0.38        | 1.27  | 0.015  | 0.050 |

| A <sub>2</sub> | 1.27        | 2.03  | 0.050  | 0.080 |

| b              | 0.89        | 1.65  | 0.035  | 0.065 |

| b <sub>1</sub> | 0.38        | 0.51  | 0.015  | 0.020 |

| С              | 0.20        | 0.30  | 0.008  | 0.012 |

| D-16           | 18.93       | 21.33 | 0.745  | 0.840 |

| E              | 5.59        | 7.11  | 0.220  | 0.280 |

| E <sub>1</sub> | 7.62        | 8.26  | 0.300  | 0.325 |

| е              | 2.29        | 2.79  | 0.090  | 0.110 |

| e <sub>1</sub> | 7.37        | 7.87  | 0.290  | 0.310 |

| L              | 2.79        | 3.81  | 0.110  | 0.150 |

| S-16           | 0.38        | 1.52  | 0.015  | 0.060 |

| ø              | 0°          | 15°   | 0°     | 15°   |

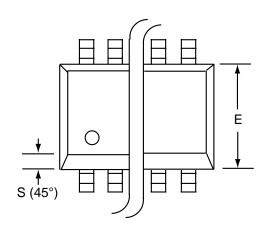

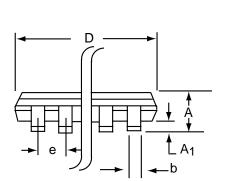

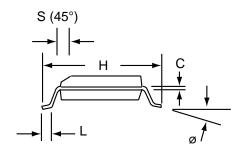

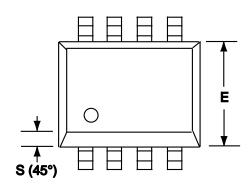

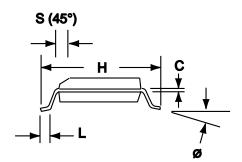

## **SOIC-8 PACKAGE DRAWING**

## 8 Pin Plastic SOIC Package

|                | Millimeters |       | Inches    |       |

|----------------|-------------|-------|-----------|-------|

| Dim            | Min         | Max   | Min       | Max   |

| Α              | 1.35        | 1.75  | 0.053     | 0.069 |

| A <sub>1</sub> | 0.10        | 0.25  | 0.004     | 0.010 |

| b              | 0.35        | 0.45  | 0.014     | 0.018 |

| С              | 0.18        | 0.25  | 0.007     | 0.010 |

| D-8            | 4.69        | 5.00  | 0.185     | 0.196 |

| Е              | 3.50        | 4.05  | 0.140     | 0.160 |

| е              | 1.27 BSC    |       | 0.050 BSC |       |

| н              | 5.70        | 6.30  | 0.224     | 0.248 |

| L              | 0.60        | 0.937 | 0.024     | 0.037 |

| Ø              | 0°          | 8°    | 0°        | 8°    |

| S              | 0.25        | 0.50  | 0.010     | 0.020 |

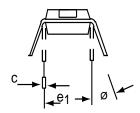

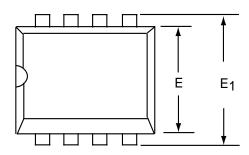

## **PDIP-8 PACKAGE DRAWING**

## 8 Pin Plastic DIP Package

|                | Millimeters |       | Inches |       |

|----------------|-------------|-------|--------|-------|

| Dim            | Min         | Max   | Min    | Max   |

| Α              | 3.81        | 5.08  | 0.105  | 0.200 |

| A <sub>1</sub> | 0.38        | 1.27  | 0.015  | 0.050 |

| A <sub>2</sub> | 1.27        | 2.03  | 0.050  | 0.080 |

| b              | 0.89        | 1.65  | 0.035  | 0.065 |

| b <sub>1</sub> | 0.38        | 0.51  | 0.015  | 0.020 |

| С              | 0.20        | 0.30  | 0.008  | 0.012 |

| D-8            | 9.40        | 11.68 | 0.370  | 0.460 |

| E              | 5.59        | 7.11  | 0.220  | 0.280 |

| E <sub>1</sub> | 7.62        | 8.26  | 0.300  | 0.325 |

| е              | 2.29        | 2.79  | 0.090  | 0.110 |

| e <sub>1</sub> | 7.37        | 7.87  | 0.290  | 0.310 |

| L              | 2.79        | 3.81  | 0.110  | 0.150 |

| S-8            | 1.02        | 2.03  | 0.040  | 0.080 |

| Ø              | 0°          | 15°   | 0°     | 15°   |