#### **Features and Benefits**

- Low quiescent current draw (0.01 μA in shutdown mode)

- Primary-side output voltage sensing; no resistor divider required

- User-adjustable current limit from 0.4 to 1.2 A

- 1.1 V logic (V<sub>HI</sub>(min)) compatibility

- Integrated IGBT driver with internal gate resistors

- Flexible dual trigger inputs for IGBT driver

- Optimized for mobile phone, 1-cell Li+ battery applications

- No primary-side Schottky diode needed

- Zero-voltage switching for lower loss

- >75% efficiency

- Charge complete indication

- Integrated 40 V DMOS switch

## **Applications**

- Mobile phone flash

- Digital and film camera flash

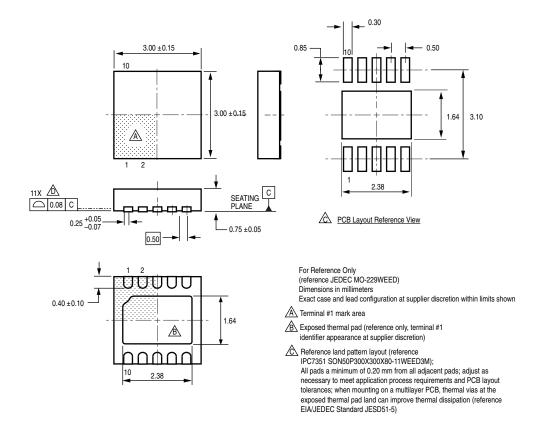

# Package: 10-contact DFN with exposed thermal pad (package EJ)

#### **Description**

The Allegro® A8731 Xenon photoflash charger IC is designed to meet the needs of ultra-low power, small form factor cameras, particularly camera-phones.

The charge time is adjustable by setting the charge current limit from 0.4 to 1.2 A maximum. By using primary-side voltage sensing, the need for a secondary-side resistive voltage divider is eliminated. This has the additional benefit of reducing leakage currents on the secondary side of the transformer. To extend battery life, the A8731 features very low supply current draw—typically 0.01  $\mu A$  in shutdown mode and 10  $\mu A$  in standby mode.

The A8731 has a flash dual trigger IGBT driver. The IGBT driver also has internal gate resistors for minimum external component count. The charge and trigger voltage logic thresholds are set at 1.1  $V_{\rm HI}$  (min) to support applications implementing low voltage control logic.

The A8731 is available in a 10-contact 3 mm  $\times$  3 mm DFN package with a 0.75 nominal overall package height, and an exposed pad for enhanced thermal performance.

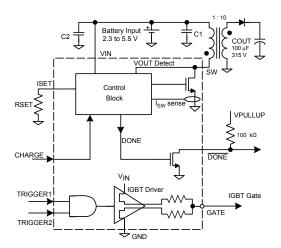

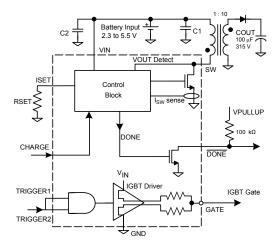

# **Typical Applications**

Figure 1. Typical application with separate trigger inputs.

Figure 2. Typical application with single trigger input.

#### **Selection Guide**

| Part Number  | Package        | Packing                             |

|--------------|----------------|-------------------------------------|

| A8731EEJTR-T | 10-contact DFN | Tape and reel, 1500 pieces per reel |

<sup>\*</sup>Contact Allegro for additional ordering information.

#### **Absolute Maximum Ratings**

| Characteristic                | Symbol               | Notes                                                                                                                                                                                                               | Rating                          | Units |

|-------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------|

|                               |                      | DC voltage.                                                                                                                                                                                                         |                                 |       |

| SW Pin                        | $V_{\mathrm{SW}}$    | (V <sub>SW</sub> is self-clamped by internal active clamp<br>and is allowed to exceed 40 V during flyback<br>spike durations. Maximum repetitive energy<br>during flyback spike: 0.5 µJ at frequency<br>≤ 400 kHz.) | -0.3 to 40                      | V     |

| VIN Pin                       | V <sub>IN</sub>      |                                                                                                                                                                                                                     | -0.3 to 6.0                     | V     |

| CHARGE, TRIGGERx, DONE Pins   |                      | Care should be taken to limit the current when -0.6 V is applied to these pins.                                                                                                                                     | -0.6 to V <sub>IN</sub> + 0.3 V | V     |

| Remaining Pins                |                      |                                                                                                                                                                                                                     | -0.3 to V <sub>IN</sub> + 0.3 V | V     |

| Operating Ambient Temperature | T <sub>A</sub>       | Range E                                                                                                                                                                                                             | -40 to 85                       | °C    |

| Maximum Junction              | T <sub>J</sub> (max) |                                                                                                                                                                                                                     | 150                             | °C    |

| Storage Temperature           | T <sub>stg</sub>     |                                                                                                                                                                                                                     | -55 to 150                      | °C    |

#### **Thermal Characteristics**

| Characteristic             | Symbol | Test Conditions*                                                                                  | Value | Units |

|----------------------------|--------|---------------------------------------------------------------------------------------------------|-------|-------|

| Package Thermal Resistance | 1      | On 2-layer PCB with 0.88 in. <sup>2</sup> area of 2 oz. copper each side, based on JEDEC standard | 65    | °C/W  |

|                            | OUA    | On 4-layer PCB based on JEDEC standard                                                            | 45    | °C/W  |

<sup>\*</sup>Additional thermal information available on Allegro website.

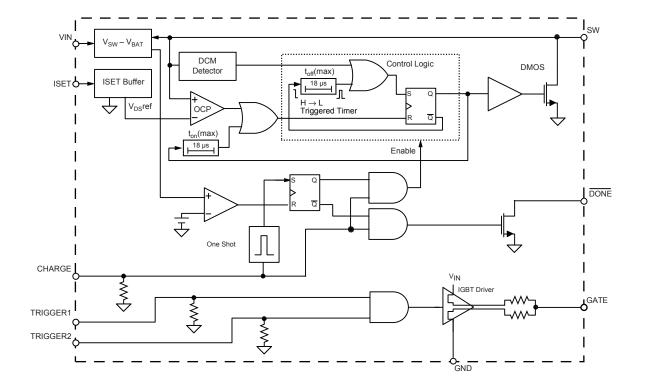

# **Functional Block Diagram**

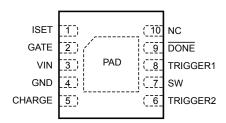

#### **Pin-out Diagram**

(Contacts Down View)

#### **Terminal List Table**

| Number | Name     | Function                                                                                                                   |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------|

| 1      | ISET     | Sets the maximum switch current; connect an external resistor to GND to set the desired peak current                       |

| 2      | GATE     | IGBT gate drive – sink/source                                                                                              |

| 3      | VIN      | Input voltage; connect to a 2.3 to 5.5 V battery supply                                                                    |

| 4      | GND      | Ground connection                                                                                                          |

| 5      | CHARGE   | Pull high to initiate charging; pull low to enter low-power standby mode                                                   |

| 6      | TRIGGER2 | IGBT input trigger 2                                                                                                       |

| 7      | SW       | Drain connection of internal power MOSFET switch; connect to transformer primary winding                                   |

| 8      | TRIGGER1 | IGBT input trigger 1                                                                                                       |

| 9      | DONE     | Pulls low when output reaches target value and CHARGE pin is high; goes high during charging or whenever CHARGE pin is low |

| 10     | NC       | No connection , electrically floating pin                                                                                  |

| _      | PAD      | Exposed pad for enhanced thermal dissipation; connect to ground plane                                                      |

**ELECTRICAL CHARACTERISTICS** typical values valid at  $V_{IN}$  = 3.6 V,  $R_{SET}$  = 33 k $\Omega$ ,  $I_{SWlim}$  = 1.0 A, and  $T_A$  =25°C, unless otherwise noted

| Characteristics                              | Symbol                            | Test Conditions                                                                                             | Min.     | Тур. | Max. | Unit |

|----------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------|----------|------|------|------|

| VIN Voltage Range                            | V <sub>IN</sub>                   |                                                                                                             | 2.3      | _    | 5.5  | V    |

| UVLO Enable Threshold                        | V <sub>INUV</sub>                 | V <sub>IN</sub> rising                                                                                      | _        | 2.05 | 2.2  | V    |

| UVLO Hysteresis                              | V <sub>INUVhys</sub>              |                                                                                                             | _        | 150  | _    | mV   |

|                                              |                                   | Shutdown (CHARGE = 0 V,<br>TRIGGER1 and TRIGGER2 = 0 V)                                                     | _        | 0.01 | 0.5  | μA   |

| VIN Supply Current                           | I <sub>IN</sub>                   | Charging complete                                                                                           | <b>-</b> | 10   | 50   | μA   |

|                                              |                                   | Charging (CHARGE = VIN,<br>TRIGGER1 and TRIGGER2 = 0 V)                                                     | _        | 2    | _    | mA   |

| Current Limits                               |                                   |                                                                                                             |          |      |      |      |

| Conitab Compant Limit1                       | I <sub>SWIimMAX</sub>             | $R_{SET}$ = 26.7 k $\Omega$                                                                                 | 1.08     | 1.2  | 1.32 | Α    |

| Switch Current Limit <sup>1</sup>            | I <sub>SWIimMIN</sub>             | $R_{SET}$ = 85 k $\Omega$                                                                                   | _        | 0.4  | _    | Α    |

| SW / ISET Current Ratio                      | I <sub>SW</sub> /I <sub>SET</sub> | CHARGE = high                                                                                               | _        | 28   | _    | kA/A |

| ISET Pin Voltage While Charging              | $V_{SET}$                         | CHARGE = high                                                                                               | _        | 1.2  | _    | V    |

| ISET Pin Internal Resistance                 | R <sub>SET(INT)</sub>             |                                                                                                             | _        | 1000 | _    | Ω    |

| Switch On-Resistance                         | R <sub>SWDS(on)</sub>             | V <sub>IN</sub> = 3.6 V, I <sub>D</sub> = 800 mA, T <sub>A</sub> = 25°C                                     | _        | 0.25 | _    | Ω    |

|                                              | 2112 2(411)                       | $V_{SW} = V_{IN}(max)$ , over temperature range                                                             | _        | -    | 2    | μA   |

| Switch Leakage Current <sup>2</sup>          | I <sub>SWIk</sub>                 | Combined V <sub>IN</sub> and SW leakage current at T <sub>A</sub> =25°C V <sub>IN</sub> = 5.5 V in Shutdown | _        | _    | 0.5  | μA   |

| CHARGE Input Current                         | I <sub>CHARGE</sub>               | V <sub>CHARGE</sub> = V <sub>IN</sub>                                                                       | _        | 36   | _    | μA   |

| OLIABOE lawyt Vallage 2                      | V <sub>CHARGE</sub>               | High, over input supply range                                                                               | 1.1      | _    | _    | V    |

| CHARGE Input Voltage <sup>2</sup>            |                                   | Low, over input supply range                                                                                | _        | _    | 0.4  | V    |

| CHARGE Pull-Down Resistor Value              | R <sub>CHPD</sub>                 |                                                                                                             | _        | 100  | _    | kΩ   |

| CHARGE ON/OFF Delay                          | t <sub>CH</sub>                   | Time between CHARGE = 1 and charging enabled                                                                | _        | 20   | _    | us   |

| Maximum Switch-Off Timeout                   | t <sub>offMAX</sub>               |                                                                                                             | _        | 18   | _    | μs   |

| Maximum Switch-On Timeout                    | t <sub>onMAX</sub>                |                                                                                                             | _        | 18   | _    | μs   |

| DONE Output Leakage Current <sup>2</sup>     | I <sub>DONEIk</sub>               |                                                                                                             | _        | -    | 1    | μΑ   |

| DONE Output Low Voltage <sup>2</sup>         | $V_{DONEL}$                       | 32 μA into DONE pin                                                                                         | _        | _    | 100  | mV   |

| Output Comparator Trip Voltage <sup>2</sup>  | V <sub>OUTTRIP</sub>              | Measured as V <sub>SW</sub> – V <sub>IN</sub>                                                               | 31       | 31.5 | 32   | V    |

| Output Comparator Overdrive                  | V <sub>OUTOV</sub>                | Pulse width = 200 ns (90% to 90%)                                                                           | _        | 200  | 400  | mV   |

| dV/dt Threshold of ZVS Comparator            | dV/dt                             | Measured at SW pin                                                                                          | _        | 20   | _    | V/µs |

| IGBT Driver                                  |                                   |                                                                                                             |          |      |      |      |

| TRIGGER, TRIGGER2 Input Voltage <sup>2</sup> | V <sub>TRIG(H)</sub>              | Input = logic high, over input supply range                                                                 | 1.1      | _    | _    | V    |

|                                              | V <sub>TRIG(L)</sub>              | Input = logic low, over input supply range                                                                  | _        | _    | 0.4  | V    |

| TRIGGER, TRIGGER2 Pull-Down Resistor         | R <sub>TRIGPD</sub>               |                                                                                                             | _        | 100  | _    | kΩ   |

| GATE Resistance to VIN                       | R <sub>SrcDS(on)</sub>            | V <sub>IN</sub> = 3.6 V, V <sub>GATE</sub> =1.8 V                                                           | _        | 23   | _    | Ω    |

| GATE Resistance to GND                       | R <sub>SnkDS(on)</sub>            | V <sub>IN</sub> = 3.6 V, V <sub>GATE</sub> = 1.8 V                                                          | _        | 30   | _    | Ω    |

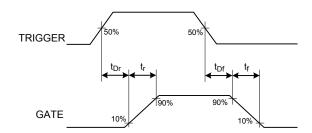

| Propagation Delay (Rising)                   | t <sub>Dr</sub>                   |                                                                                                             | _        | 110  | _    | ns   |

| Propagation Delay (Falling)                  | t <sub>Df</sub>                   | -<br>- Measurement taken at pin, C <sub>L</sub> = 6500 pF, V <sub>IN</sub> = 3.6 V                          |          | 140  | _    | ns   |

| Output Rise Time                             |                                   | Twicasurement taken at pin, CL - 0000 pr, V <sub>IN</sub> = 3.0 V                                           |          | 290  | _    | ns   |

| Output Fall Time                             | t <sub>f</sub>                    |                                                                                                             |          | 360  | _    | ns   |

<sup>&</sup>lt;sup>1</sup>Current limit guaranteed by design and correlation to static test. Refer to application section for peak current in actual circuits.

$<sup>^2</sup>$ Specifications over the range  $T_A$ =  $-40^{\circ}$ C to  $85^{\circ}$ C; guaranteed by design and characterization.

# **IGBT Drive Timing Definition**

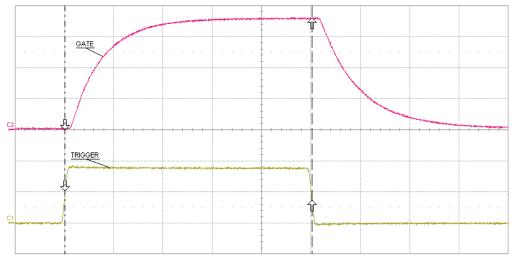

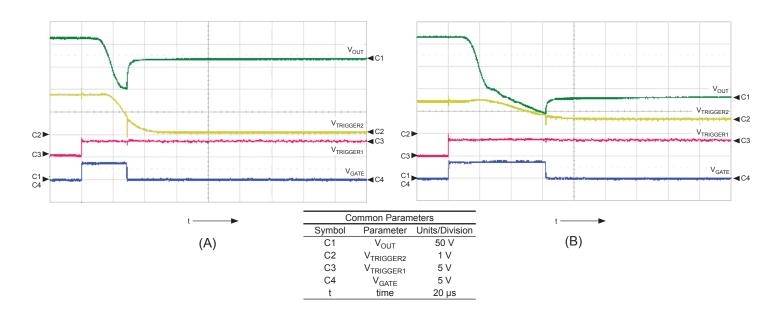

# **IGBT Drive Timing Characteristic Performance**

$C_{GATE}$  = 6200 pF.  $V_{IN}$  = 3.6 V, Time = 200 ns/div; CH1 = TRIGGER input, 2 V/div, CH2 = Gate driver output, 1 V/div

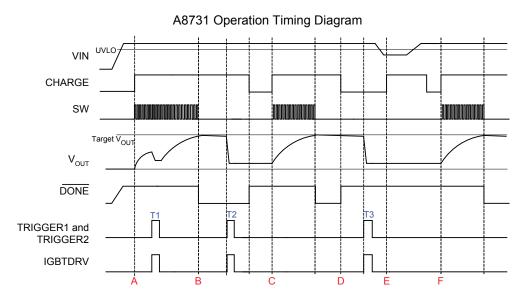

#### **Explanation of Events**

- A: Start charging by pulling CHARGE to high, provided that  $V_{\rm IN}$  is above UVLO level.

- B: Charging stops when  $\boldsymbol{V}_{\text{OUT}}$  reaches the target voltage.

- C: Start a new charging process with a low-to-high transition at the CHARGE pin.

- D: Pull CHARGE to low to put the controller in low-power standby mode.

- E: Charging does not start, because  $V_{\mathrm{IN}}$  is below UVLO level when CHARGE goes high.

- F: After  $\rm V_{IN}$  goes above UVLO , another low-to-high transition at the CHARGE pin is required to start the charging.

- T1, T2, T3 (Trigger instances): IGBT driver output pulled high whenever both TRIGGER pins are logic high. It is recommended to avoid applying any trigger pulses during charging.

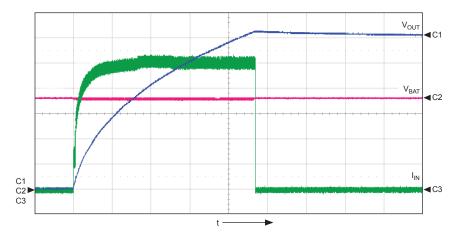

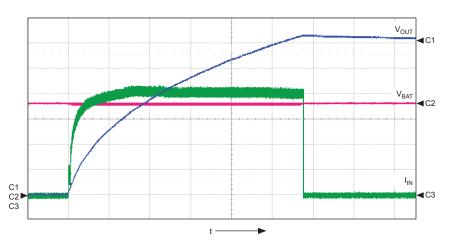

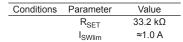

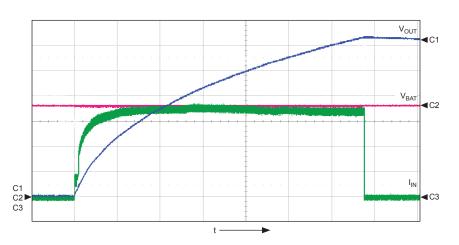

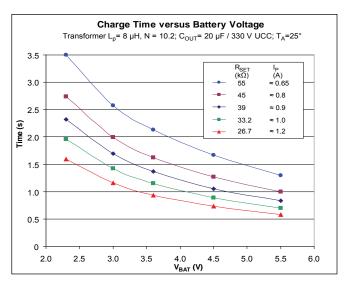

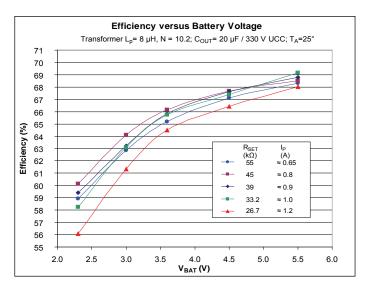

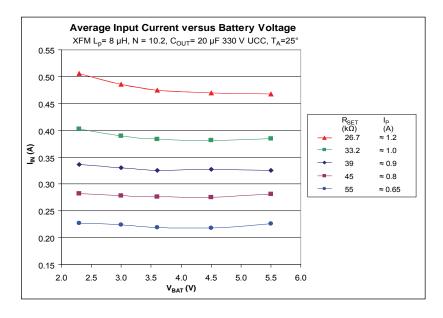

# **Performance Characteristics**

Charging Time at Various Peak Current Levels

| Common Parameters |                  |                |  |  |

|-------------------|------------------|----------------|--|--|

| Symbol            | Parameter        | Units/Division |  |  |

| C1                | V <sub>OUT</sub> | 50 V           |  |  |

| C2                | $V_{BAT}$        | 1 V            |  |  |

| C3                | I <sub>IN</sub>  | 100 mA         |  |  |

| t                 | time             | 200 ms         |  |  |

| Conditions        | Parameter        | Value          |  |  |

|                   | $V_{BATT}$       | 3.6 V          |  |  |

|                   | C <sub>OUT</sub> | 20 μF          |  |  |

| Conditions | Parameter        | Value   |

|------------|------------------|---------|

|            | R <sub>SET</sub> | 26.7 kΩ |

|            | Iswiim           | ≈1.2 A  |

Conditions Parameter R<sub>SET</sub> 39 kΩ  $\mathrm{I}_{\mathrm{SWlim}}$

$C_{OUT}$ = 20  $\mu$ F. For larger or smaller capacitances, charging time scales proportionally.

Special low-profile transformer with relatively low inductance (Lp= 8  $\mu$ H) and high winding resistance (Rp = 0.37  $\Omega$ ). Higher efficiency can be achieved by using transformers with higher Lp, which reduces switching frequency and therefore switching loses, and lower resistance, which reduces conduction losses.

An increase in I<sub>SWlim</sub> with respect to V<sub>BAT</sub> actually keeps the average input current roughly constant throughout the battery voltage range. Normally, if  $I_{SWlim}$  is kept constant, the average current will drop as V<sub>BAT</sub> goes higher.

# **Application Information**

## **General Operation Overview**

The CHARGE pin enables the part and starts charging. The DONE open-drain indicator is pulled low when CHARGE is high and target output voltage is reached. Pulling the CHARGE pin low stops charging and forces the chip into low-power standby mode.

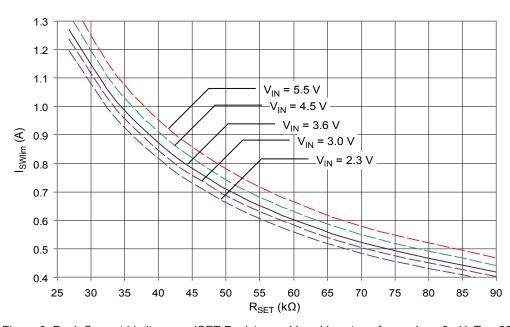

## Selection of Switching Current Limit

The A8731 features continuously adjustable peak switching current between 0.4 and 1.2A. This is done by selecting the value of an external resistor RSET, connected from the ISET pin to GND, which determines the ISET bias current, and therefore the switching current limit,  $I_{\text{SWlim}}$ .

To the first order approximation,  $I_{SWlim}$  is related to  $I_{SET}$  and  $R_{SET}$  according to the following equations:

$$I_{\text{SWlim}} = I_{\text{SET}} \times K = V_{\text{SET}} / R_{\text{SET}} \times K , \qquad (1)$$

where K = 28000 when battery voltage is 3.6 V.

In real applications, the actual switching current limit is affected by input battery voltage, and also the transformer primary inductance, Lp. If necessary, the following expressions can be used to determine  $I_{SWlim}$  more accurately:

$$I_{\text{SET}} = V_{\text{SET}} / (R_{\text{SET}} + R_{\text{SET(INT)}} - K \times R_{\text{GND(INT)}}), (2)$$

where:

$R_{SET(INT)}$  is the internal resistance of the  $I_{SET}$  pin (1 k $\Omega$  typical),

$R_{GND(INT)}$  is the internal resistance of the bonding wire for the GND pin (27 m $\Omega$  typical), and

$$K = (K' + V_{IN} \times K'')$$

, with  $K' = 24350$  and  $K'' \approx 1040$  at  $T_A = 25$ °C. Then,

$$I_{\text{SWlim}} = I_{\text{SET}} \times K + V_{\text{BAT}} / L_{\text{P}} \times t_{\text{D}}, \qquad (3)$$

where  $t_D$  is the delay in SW turn-off (0.1 µs typical).

Figure 3 can be used to determine the relationship between  $R_{SET}$  and  $I_{SWlim}$  at various battery voltages.

Figure 3. Peak Current Limit versus ISET Resistance.  $V_{IN} = V_{BAT}$ , transformer  $L_P = 8 \mu H$ ,  $T_A = 25 ^{\circ} C$ .

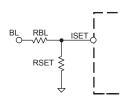

## Smart Current Limit (Optional)

With the help of some simple external logic, the user can change the charging current according to the battery voltage. For example, assume that  $I_{SET}$  is normally 36  $\mu A$  (for  $I_{SWlim}$  = 1.0 A). Referring to figure 4, when the battery voltage drops below 2.5 V, the signal at BL (battery-low) goes high. The resistor RBL, connecting BL to the ISET pin, then injects 10  $\mu A$  into RSET. This effectively reduces ISET current to 26  $\mu A$  (for  $I_{SWLIM}$  = 0.73 A).

## Timer Mode and Fast Charging Mode

The A8731 achieves fast charging times and high efficiency by operating in discontinuous conduction mode (DCM) through most of the charging process The

Figure 4. Smart Current Limit reference circuit

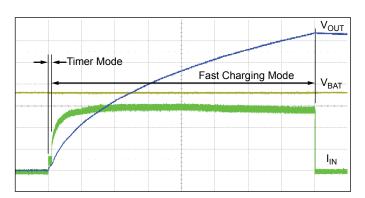

Figure 5. Timer Mode and Fast Charging Mode. t =200 ms/div, V<sub>OUT</sub> =50 V/div, V<sub>BAT</sub> =1 V/div., I<sub>IN</sub> =100 mA/div., V<sub>BAT</sub> =3.6 V, C<sub>OUT</sub> =20  $\mu$ F/330 V, R<sub>SET</sub>=46 k $\Omega$  (I<sub>SWIim</sub>≈0.75 A).

relationship of Timer Mode and Fast Charging Mode is shown in figure 5.

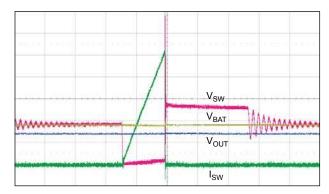

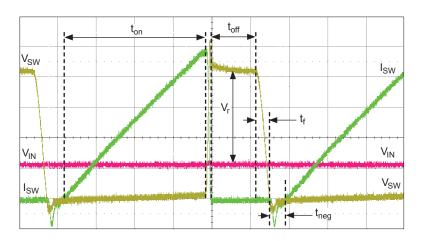

The IC operates in Timer Mode when beginning to charge a completely discharged photoflash capacitor, usually when the output voltage,  $V_{OUT}$ , is less than approximately 15 to 20 V. Timer Mode is a fixed period, 18  $\mu$ s, off-time control. One advantage of having Timer Mode is that it limits the initial battery current surge and thus acts as a "soft-start." A time-expanded view of a Timer Mode interval is shown in figure 6.

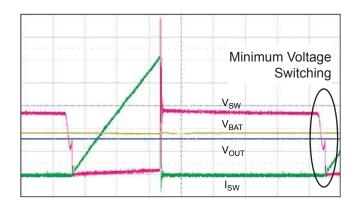

As soon as a sufficient voltage has built up at the output capacitor, the IC enters Fast-Charging Mode. In this mode, the next switching cycle starts after the secondary side current has stopped flowing, and the switch voltage has dropped to a minimum value. A proprietary circuit is used to allow minimum-voltage switching, even if the SW pin voltage does not drop to 0 V. This enables Fast-Charging Mode to start earlier

Figure 6. Timer Mode expanded view.  $V_{OUT} \le$  14 V, t = 2  $\mu s$  / div.,  $V_{BAT}$  = 3.6 V,  $R_{SET}$  = 33.2  $k\Omega$ .

than previously possible, thereby reducing the overall charging time. Minimum-voltage switching is shown in figure 7.

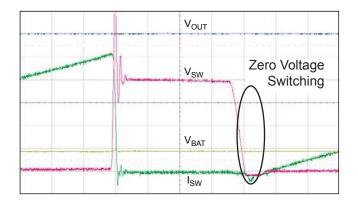

During Fast-Charging Mode, when  $V_{OUT}$  is high enough (over 50 V), true zero-voltage switching (ZVS) is achieved. This further improves efficiency as well as reduces switching noise. A ZVS interval is shown in figure 8.

## **IGBT Gate Driver Inputs**

The TRIGGER1 and TRIGGER2 pins are ANDed together inside the IC to control the IGBT gate driver. If only one trigger signal is needed, tie both trigger pins together and use as a single input.

### **Ambient Light Sensing**

Ambient Light Sensing (ALS) can be easily implemented for the A8731 using the TRIGGER2 pin plus three external components. This configuration is shown in figure 9.

The phototransistor current is proportional to the intensity of the light that it receives. When there is

sufficient ambient light (for example, during daylight outdoor photographing), a current of about 30  $\mu$ A can flow through the phototransistor. This forces the voltage at TRIGGER2 pin to fall to 0.8 V or lower, so it prohibits TRIGGER1 from firing the flash. The exact threshold of ambient light required to prohibit flash firing can be adjusted by  $R_{TGR1}$ . The smaller this resistance, the brighter the ambient light must be to prohibit flash firing.

When ambient conditions are dark, the current flowing through the phototransistor is in less than 1  $\mu$ A. Because the TRIGGER2 pin is biased at 1.4 V or higher, TRIGGER1 is allowed to activate the IGBT gate driver (and thereby fire the flash).

The capacitor CTGR1 and resistor RTGR1 form an integrator for light exposure. When the flash fires, bright light bounces back from subject and enters the phototransistor. In example A in figure 10, the flash terminates after just 30  $\mu$ s, without fully discharging the photoflash capacitor.

Figure 7. Minimum voltage switching.  $V_{OUT} \ge$  15 V; t =1  $\mu s/div.$ ,  $V_{BAT}$  = 3.6 V,  $R_{SET}$  = 33.2 k $\Omega$ .

Figure 8. Zero voltage switching.  $V_{OUT}$  = 120 V. t = 0.2  $\mu$ s/div.,  $V_{BAT}$  = 3.6 V,  $R_{SET}$  = 33.2  $k\Omega$ .

**Battery Input** 2.5 to 5.5 V If the subject is far away, the reflected light intensity is lower, so the phototransistor current is also lower. In example B, the flash stays on for longer time (60 µs) and VIN discharges more energy from the photo-VOUT Detect flash capacitor. Control Using a larger C<sub>TGR1</sub> causes the time Block ISW sens constant of the integrator to increase, so a VPULLUP longer pulse is required before the flash is terminated. DONE CHARGE DONE  $V_{IN}$ IGBT Driver TRIGGER1 **IGBT** Gate TRIGGER2  $C_{\text{TGR1}}$ **GND**  $100 \text{ k}\Omega$ (A) It is recommend to use a regulated system voltage for the bias. If battery **PNZ121S** voltage is used, the ALS sensitivity will vary with battery voltage, and there Phototransistor would be a small leakage current even when the camera is turned off.

Figure 9. ALS typical application

Figure 10. Adaptive timing of photoflash. (A) Subject near to camera, and (B) subject far from camera.

#### **Transformer Selection**

1. The transformer turns ratio, N, determines the output voltage:

$$N = N_{\rm S} / N_{\rm P} \tag{4}$$

$$V_{\rm OUT} = 31.5 \times N - V_{\rm d}$$

, (5)

where 31.5 is the typical value of  $V_{OUTTRIP}$ , and  $V_d$  is the forward drop of the output diode.

2. The primary inductance, L<sub>P</sub>, determines the on-time of the switch:

$$t_{\rm on} = (-L_{\rm P}/R) \times \ln\left(1 - I_{\rm SWlim} \times R/V_{\rm IN}\right) , \qquad (6)$$

where R is the total resistance in the primary current path (including  $R_{SWDS(on)}$  and the DC resistance of the transformer).

If  $V_{IN}$  is much larger than  $I_{SWlim} \times R$ , then  $t_{on}$  can be approximated by:

$$t_{\rm on} = I_{\rm SWlim} \times L_{\rm P} / V_{\rm IN} . \tag{7}$$

3. The secondary inductance, L<sub>S</sub>, determines the off-time of the switch. Given:

$$L_{\rm S}/L_{\rm P} = N \times N$$

, then

$t_{\rm off} = (I_{\rm SWlim}/N) \times L_{\rm S}/V_{\rm OUT}$  (8)

$$= (I_{\text{SWlim}} \times L_{\text{P}} \times N) / V_{\text{OUT}} . \tag{9}$$

The minimum pulse width for  $t_{off}$  determines what is the minimum  $L_P$  required for the transformer. For example, if  $I_{SWlim}$  = 0.7 A, N = 10, and  $V_{OUT}$  = 315 V, then  $L_P$  must be at least 9  $\mu$ H in order to keep  $t_{off}$  at 200 ns or longer. These relationships are illustrated in figure 11.

In general, choosing a transformer with a larger  $L_P$  results in higher efficiency (because a larger  $L_P$  means lower switch frequency and hence lower switching loss). But transformers with a larger  $L_P$  also require more windings and larger magnetic cores. Therefore, a trade-off must be made between transformer size and efficiency.

## Component Selection

Selection of the flyback transformer should be based on the peak current, according to the following table:

| I <sub>Peak</sub> Range |            |            |                 | $L_P$ |

|-------------------------|------------|------------|-----------------|-------|

|                         | (A)        | Supplier   | Part Number     | (µH)  |

|                         | 0.4 to 1.0 | TDK        | LDT565630T-002  | 14.5  |

|                         | 0.5 to 1.2 | TDK        | LDT565630T-003  | 10.5  |

|                         | 0.7 to 1.0 | TDK        | LDT565620ST-203 | 8.2   |

|                         | 0.7 to 1.2 | Mitsumi    | C5-KT2.2L       | 8.0   |

|                         | 0.8 to 1.2 | Tokyo Coil | T-19-243        | 6.5   |

Figure 11. Pulse width relationship definitions.

### Package EJ, 3 mm x 3 mm 10-Contact DFN with Exposed Thermal Pad

A8731

# Mobile Phone Xenon Photoflash Capacitor Charger With IGBT Driver

#### **Revision History**

|                       | Revision Revision Date |                | Description of Revision      |  |

|-----------------------|------------------------|----------------|------------------------------|--|

| Rev. 1 April 19, 2012 |                        | April 19, 2012 | Miscellaneous format changes |  |

|                       |                        |                |                              |  |

$Copyright @2008-2012, Allegro\ MicroSystems, Inc.$

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com