#### **Features and Benefits**

- AEC Q-100 qualified

- LED drive current up to 350 mA

- 6 to 40 V supply

- Reverse battery protection

- Low drop-out voltage

- LED short circuit and thermal protection

- 10 μA maximum shutdown current

- PWM dimming control input

- Current slew rate limiting

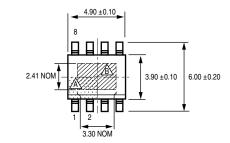

# Package: 8-pin SOICN with exposed thermal pad (suffix LJ)

Not to scale

Not to scale

#### Description

The A6260 is a linear, programmable current regulator providing up to 350 mA for driving high-brightness LEDs. The LED current, accurate to 4%, is set by a single low-power sense resistor. Driving LEDs with constant current ensures safe operation with maximum possible light output. For automotive applications, optimum performance is achieved when driving between 1 and 3 LEDs at currents up to 350 mA.

The low dropout voltage of the A6260 allows a single white LED to be driven safely, at full current, with a supply voltage down to 6 V.

An enable input allows PWM dimming and can be used to enable low-current sleep mode. The rate of change of current during PWM switching is limited to reduce EMI.

Overcurrent detection is provided to protect the LEDs and the A6260 during short-to-supply or short-to-ground at any LED terminal.

The integrated temperature monitor can be used to reduce the LED drive current if the chip temperature exceeds the thermal limit

The device is available in an 8-pin SOIC package with exposed thermal pad (suffix LJ). The device is lead (Pb) free with 100% matte-tin leadframe plating.

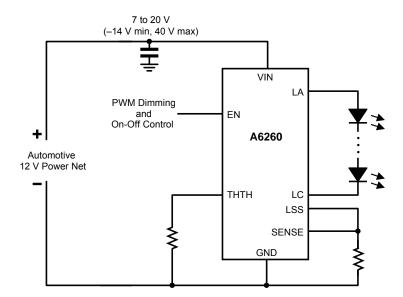

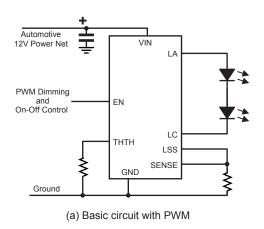

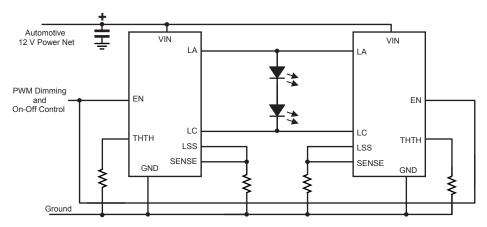

#### **Typical Application**

#### **Selection Guide**

| Part Number  | Packing              | Ambient Temperature, T <sub>A</sub> (°C) |  |  |

|--------------|----------------------|------------------------------------------|--|--|

| A6260KLJTR-T | 3000 pieces per reel | -40 to 125                               |  |  |

| A6260SLJTR-T | 3000 pieces per reel | –20 to 85                                |  |  |

#### **Absolute Maximum Ratings\***

| Characteristic                       | Symbol           | Notes                  | Rating      | Units |

|--------------------------------------|------------------|------------------------|-------------|-------|

| Load Supply Voltage                  | $V_{IN}$         |                        | -14 to 40   | V     |

| EN Pin Voltage                       | $V_{EN}$         |                        | -14 to 40   | V     |

| LA and LC Pins Voltage               | $V_{Lx}$         |                        | -0.3 to 40  | V     |

| LSS Pin Voltage                      | $V_{LSS}$        |                        | -0.3 to 0.3 | V     |

| SENSE Pin Voltage                    | $V_{SENSE}$      |                        | -0.3 to 0.3 | V     |

| THTH Pin Voltage                     | $V_{THTH}$       |                        | –0.3 to 7   | V     |

| Ambient Operating Temperature Range  | <b>T</b>         | Range K                | -40 to 125  | °C    |

| Ambient Operating Temperature Range  | T <sub>A</sub>   | Range S                | –20 to 85   | °C    |

| Junction Operating Temperature Range | $T_J$            |                        | -40 to 150  | °C    |

| Storage Temperature Range            | T <sub>stg</sub> |                        | -55 to 150  | °C    |

| ESD Rating, Human Body Model         |                  | AEC-Q100-002, all pins | 2000        | V     |

| ESD Rating, Charged Device Model     |                  | AEC-Q100-011, all pins | 1050        | V     |

<sup>\*</sup>With respect to GND.

#### Thermal Characteristics\*may require derating at maximum conditions, see application section for optimization

| Characteristic                                      | Symbol          | Test Conditions*                                                   | Value | Unit |

|-----------------------------------------------------|-----------------|--------------------------------------------------------------------|-------|------|

| Package Thermal Resistance<br>(Junction to Ambient) | $R_{\theta,JA}$ | On 4-layer PCB based on JEDEC standard                             | 35    | °C/W |

|                                                     |                 | On 2-layer generic test PCB with 0.8 in.2 of copper area each side | 62    | °C/W |

| Package Thermal Resistance (Junction to Pad)        |                 |                                                                    | 2     | °C/W |

<sup>\*</sup>Additional thermal information available on the Allegro® website.

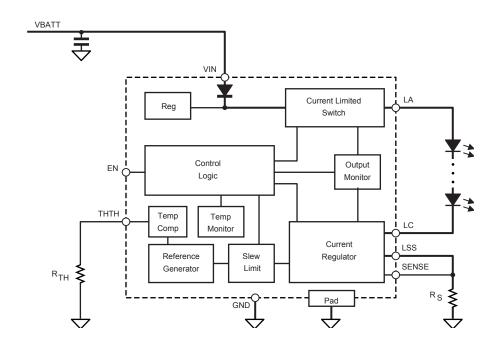

#### **Functional Block Diagram**

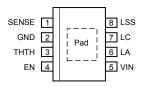

#### **Pin-out Diagram**

#### **Terminal List Table**

| Number | Name  | Description                                  |  |

|--------|-------|----------------------------------------------|--|

| 1      | SENSE | Current sense input                          |  |

| 2      | GND   | Ground reference                             |  |

| 3      | THTH  | Thermal threshold input                      |  |

| 4      | EN    | Enable input                                 |  |

| 5      | VIN   | Main supply                                  |  |

| 6      | LA    | LED anode (+) connection                     |  |

| 7      | LC    | LED cathode (-) connection                   |  |

| 8      | LSS   | Low-side sense connection                    |  |

| 9      | Pad   | Exposed pad for enhanced thermal dissipation |  |

#### ELECTRICAL CHARACTERISTICS valid at $T_J$ = -40°C to 150°C, $V_{IN}$ = 7 to 40 V, unless noted otherwise

| Characteristics                                            | Symbol              | Test Conditions                                                   | Min. | Тур.                      | Max. | Units |  |

|------------------------------------------------------------|---------------------|-------------------------------------------------------------------|------|---------------------------|------|-------|--|

| Supply and Reference                                       |                     |                                                                   |      |                           |      |       |  |

| V <sub>IN</sub> Functional Operating Range <sup>1</sup>    | V <sub>IN</sub>     |                                                                   | 6    | _                         | 40   | V     |  |

| V <sub>IN</sub> Quiescent Current                          | I <sub>INQ</sub>    | LA, LC unconnected                                                | _    | -                         | 4    | mA    |  |

| V <sub>IN</sub> Shutdown Current                           | I <sub>INS</sub>    | EN < 400 mV                                                       | _    | 1                         | 10   | μA    |  |

| Startup Time                                               | t <sub>ON</sub>     | EN 2 V to 35 mA I <sub>LC</sub>                                   | 9    | 18                        | 27   | μs    |  |

| Current Regulation                                         |                     |                                                                   | '    |                           | '    |       |  |

| Maximum Current Sink                                       | I <sub>LCmax</sub>  | $R_S = 250 \text{ m}\Omega, V_{IN} - V_{LA} > 2 \text{ V}$        | 350  | _                         | _    | mA    |  |

| Current Sink                                               | I <sub>LC</sub>     | $R_S = 286 \text{ m}\Omega, V_{IN} - V_{LA} > 2 \text{ V}$        | 333  | 350                       | 367  | mA    |  |

| Current Sink Accuracy                                      | err <sub>ILC</sub>  | 100 mA < I <sub>LC</sub> < 350 mA                                 | -5   | ±4                        | 5    | %     |  |

| SENSE Reference Voltage                                    | V <sub>SENREF</sub> | $260 \text{ m}\Omega < R_S < 1\Omega$                             | 97   | 102                       | 107  | mV    |  |

| Switch Proposit Voltage                                    |                     | $V_{IN} - V_{LA}$ , $I_{LOAD} = 350 \text{ mA}$                   | _    | 2.25                      | 2.35 | V     |  |

| Switch Dropout Voltage                                     | V <sub>DO</sub>     | $V_{IN} - V_{LA}$ , $I_{LOAD} = 150 \text{ mA}$                   | _    | 1.35                      | 1.4  | V     |  |

| Degulator Caturation Valtage                               | \ \/                | V <sub>LC</sub> – V <sub>SENSE</sub> , I <sub>LOAD</sub> = 350 mA | _    | 500                       | 550  | mV    |  |

| Regulator Saturation Voltage                               | V <sub>SAT</sub>    | V <sub>LC</sub> – V <sub>SENSE</sub> , I <sub>LOAD</sub> = 150 mA | _    | 250                       | 275  | mV    |  |

| Outrout Commant Class Times                                | t <sub>r</sub>      | Current rising from 10% to 90%                                    | 50   | 80                        | 120  | μs    |  |

| Output Current Slew Time                                   | t <sub>f</sub>      | Current falling from 90% to 10%                                   | 60   | 100                       | 150  | μs    |  |

| Logic Input                                                |                     |                                                                   |      |                           |      |       |  |

| Input Low Voltage                                          | V <sub>IL</sub>     |                                                                   | _    | _                         | 0.8  | V     |  |

| Input High Voltage                                         | V <sub>IH</sub>     |                                                                   | 2    | _                         | _    | V     |  |

| Input Hysteresis V <sub>Ihys</sub>                         |                     |                                                                   | 150  | 350                       | _    | mV    |  |

| Protection                                                 |                     |                                                                   |      |                           |      |       |  |

| Switch Overcurrent Trip Level                              | I <sub>LAOC</sub>   |                                                                   | -600 | -500                      | -400 | mA    |  |

| Overcurrent Detection Time <sup>2</sup>                    | t <sub>OCD</sub>    | From detection to I <sub>SCU</sub> > -1.2 mA                      | _    | 3                         | _    | μs    |  |

| Switch Current Limit                                       | I <sub>LALIM</sub>  |                                                                   | _    | 1.5×<br>I <sub>LAOC</sub> | _    | mA    |  |

| LC Short Circuit Release Voltage V <sub>SCCR</sub>         |                     | Measured at V <sub>LC</sub> , when rising                         | 1.0  | 1.2                       | 1.4  | V     |  |

| Short Circuit Source Current <sup>2</sup> I <sub>SCU</sub> |                     | When short is detected                                            | -1.5 | -1.1                      | -0.7 | mA    |  |

| Thermal Monitor Activation Temperature T <sub>JM</sub>     |                     | T <sub>J</sub> at I <sub>LC</sub> = 90%, THTH open                | 90   | 105                       | 120  | °C    |  |

| Thermal Monitor Low Current Temperature                    | T <sub>JL</sub>     | T <sub>J</sub> at I <sub>LC</sub> = 25%, THTH open                | 110  | 130                       | 150  | °C    |  |

| Overtemperature Shutdown Threshold                         | T <sub>JF</sub>     | Temperature increasing                                            | _    | 165                       | -    | °C    |  |

| Overtemperature Hysteresis                                 | T <sub>Jhys</sub>   | Recovery = T <sub>JF</sub> - T <sub>Jhys</sub>                    | _    | 15                        | _    | °C    |  |

|                                                            |                     |                                                                   |      |                           |      |       |  |

<sup>&</sup>lt;sup>1</sup>Functions correctly, but parameters are not guaranteed, below the general limit (7 V).

<sup>&</sup>lt;sup>2</sup>For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device pin.

#### **Functional Description**

The A6260 is a linear current regulator that is designed to provide drive current and protection for series-connected, high brightness LEDs in automotive applications. It provides programmable current output at load voltages up to 3 V below the main supply voltage. For automotive applications optimum performance is achieved when driving 1 to 3 LEDs at currents up to 350 mA.

The LED current is set by a single low-power sense resistor and the LED brightness can be further controlled by a PWM input to the EN pin. The EN input can also be used as an on/off switched input and the A6260 will enter a low current ( $<10~\mu A$ ) sleep mode if EN is held low.

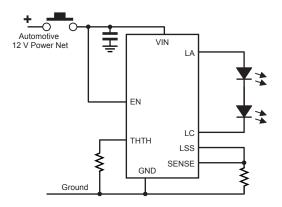

For incandescent replacement configurations, the EN input can be connected directly to the VIN pin with the supply to VIN controlled by a simple on/off switch.

The LEDs and the regulator are protected from excessive currents caused by short circuits to ground or supply or by reversal of the power supply connections.

Integrated thermal management circuits can be used to reduce the regulated current level at high temperatures to limit power dissipation.

#### **Pin Functions**

**VIN Pin** Supply to the control circuit. A small-value ceramic bypass capacitor (typically 100 nF) should be connected from close to this pin to the GND pin.

**GND Pin** Ground reference connection. Should be connected directly to the negative supply as close as possible to the bottom (ground connection) of the sense resistor.

**EN Pin** Logic input to enable operation. Can be used as a direct PWM input. Chip enters a low-power sleep mode when this pin is held low.

**THTH Pin** Sets the thermal monitor threshold,  $T_{JM}$ , where the output current starts to be reduced with increasing temperature. When this pin is left open, the threshold temperature will typically be the specified default value. A resistor connected between THTH and GND can be used to increase the threshold temperature. A resistor connected between THTH and VIN can be used to decrease the threshold temperature. Connecting THTH directly to GND disables the thermal monitor function.

**LA Pin** Switched and protected current source connected to the anode of the LEDs.

**LC Pin** Controlled current sink connected to the cathode of the LEDs.

**LSS Pin** Low-side current sink connection from the current regulator to power ground via a sense resistor. A current sense resistor (240 m $\Omega$  to 3  $\Omega$ ) is connected between LSS and power ground.

**SENSE Pin** LED current sense input. The high impedance SENSE input should have an independent connection to the top (LSS connection side) of the sense resistor.

#### **LED Current Level**

The LED current is controlled by the internal current regulator between the LC and LSS pins. This current, defined as the current into the LC pin,  $I_{LC}$ , is set by the value,  $R_{\rm S}$ , of the sense resistor. The voltage across the sense resistor, measured between the SENSE pin and the GND pin, is compared to a reference voltage, nominally 102 mV, allowing the use of a low-value sense resistor with low power dissipation.

The LED current is thus defined as:

$$I_{LC} = V_{SENREF} / R_S$$

(1)

conversely:

$$R_S = V_{SENREF} / I_{LC}$$

The nominal output current settings,  $I_{LC}$ , versus the current setting resistor values,  $R_S$ , are given in the following table. The current level defined here is the 100% current level before any current reduction effects due to the temperature monitor, described later in this document.

#### **Sense Resistor Selection**

| _ | I <sub>LC</sub><br>(mA) | R <sub>S</sub><br>(mΩ) | P <sub>D(RS)</sub> (mW) | I <sub>LC</sub> (mA) | R <sub>S</sub><br>(mΩ) | P <sub>D(RS)</sub><br>(mW) |

|---|-------------------------|------------------------|-------------------------|----------------------|------------------------|----------------------------|

|   | 350                     | 286                    | 35                      | 125                  | 800                    | 13                         |

|   | 300                     | 333                    | 30                      | 100                  | 1000                   | 10                         |

|   | 250                     | 400                    | 25                      | 70                   | 1429                   | 7                          |

|   | 200                     | 500                    | 20                      | 50                   | 2000                   | 5                          |

|   | 150                     | 667                    | 15                      | 35                   | 2857                   | 4                          |

#### Parallel operation

The A6260 is a constant current controller, that is, it controls the output current irrespective of output voltage (within the compliance range). This allows the outputs of two or more A6260s to be connected in parallel (see figure 4e, in the Applications Information section). In this configuration, each A6260 must have a

dedicated sense resistor, which determines its share of the current provided to the LED.

#### **LED Brightness**

Although the LED brightness can be controlled by changing the current (intensity) this may slightly affect the color or the color temperature of the light from the LED. When multiple LEDs are used, it is usually more desirable to control the brightness by switching the fixed LED current with a pulse width modulated signal. This allows the LED brightness to be set using a digital control input with little effect on the LED color.

In the A6260, the brightness level can be controlled by a PWM signal applied to the EN input. This controls both the low-side linear regulator and the high-side switch.

When EN is switched from high to low, the low-side regulator reduces the current to zero before allowing the high-side switch to turn off.

When EN is switched from low to high, the high-side switch is turned on before the low-side regulator increases the current to the full operating level.

To assist EMC, the rate of change of the LED current is limited and the current will rise and fall within the limits  $(t_r, t_f)$  defined in the Electrical Characteristics table.

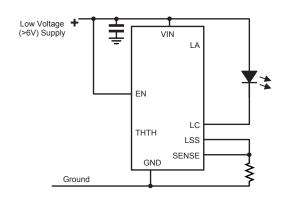

Note that EN can be used for PWM dimming even when the high-side switch is bypassed. (See figure 4(d)).

#### Sleep Mode

When EN is held low, the A6260 will be in shutdown mode and all internal circuits will be in a low-power sleep mode. In this mode, the input current,  $I_{INS}$ , will be less than 10  $\mu$ A. This means

that the complete circuit, including LEDs, may remain connected to the power supply under all conditions.

#### **Safety Features**

The circuit includes several features to ensure safe operation and to protect the LEDs and the A6260:

- The high-side switch between VIN and LA has overcurrent detection and a current limiter. It assumes that a short circuit is present if the current exceeds the trip value, I<sub>LAOC</sub>, for longer than the overcurrent detection time, t<sub>OCD</sub>.

- The current regulator between LC and LSS provides a natural current limit due to the regulation.

- The thermal monitor reduces the regulated current as the temperature rises.

- Thermal shutdown completely disables the outputs under extreme overtemperature conditions.

#### **Short Circuit Detection**

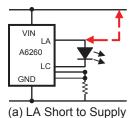

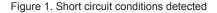

A total of five short circuit conditions can exist as illustrated in figure 1.

**LA Short to Supply** (figure 1a) This condition is permitted because the current remains regulated by the current sink. This configuration may also be used in applications with low supply voltages (see figure 4d in the Applications Information section).

**LA Short to Ground** (figure 1b) This condition is detected when the high-side switch current exceeds the trip value,  $I_{LAOC}$ , for longer than the overcurrent detection time,  $t_{OCD}$  (3  $\mu s$  typical). When a short is detected, the switch and the regulator are both disabled. When the voltage at LC drops below the short release voltage,  $V_{SCCR}$ , a low value current,  $I_{SCU}$  (1.1 mA typical), is then sourced from LA to provide a short circuit monitor. When

Permitted because current remains regulated

(b) LA Short to Ground

Detected when switch current exceeds trip value for longer than 3 µs, released when  $V_{LC} > V_{SCCR}$

(c) LC Short to Supply

Current remains regulated, thermal shutdown provides protection

(d) LC Short to Ground

Detected when switch current exceeds trip value for longer than 3 µs, released when  $V_{LC} > V_{SCCR}$

(e) LA Short to LC

Current remains regulated, thermal shutdown provides protection

the short circuit is removed the short circuit source current,  $I_{SCU}$ , pulls the voltage at the LC pin above  $V_{SCCR}$ , and the switch and regulator are re-enabled.

LC Short to Supply (figure 1c) In this condition, the current into the LC pin remains regulated but the power dissipated in the A6260 increases. This higher dissipation causes the thermal monitor to reduce the current to protect the regulator. In extreme cases, or in cases where the thermal monitor is disabled, the increased dissipation may cause temperature to reach the thermal shutdown level, at which point the regulator will be disabled.

**LC Short to Ground** (figure 1d) This condition is detected when the high-side switch current exceeds the trip value,  $I_{LAOC}$ , for longer than the overcurrent detection time,  $t_{OCD}$  (3  $\mu$ s typical). When a short is detected, the switch and the regulator are both disabled. When the voltage at LC drops below the short release voltage,  $V_{SCCR}$ , a low value current,  $I_{SCU}$  (1.1 mA typical), is then sourced from LA to provide a short circuit monitor. When the short circuit is removed,  $I_{SCU}$  pulls the voltage at the LC pin above  $V_{SCCR}$ , and the switch and regulator are re-enabled.

**LA Short to LC** (figure 1e) This condition is effectively the same as the LC Short-to-Supply condition. In this condition, the current into the LC pin remains regulated but the power dissipated in the A6260 increases. This higher dissipation causes the thermal monitor to reduce the current to protect the regulator. In extreme cases, or in cases where the thermal monitor is disabled, the increased dissipation may cause temperature to reach the thermal shutdown level, at which point the regulator will be disabled.

#### **Temperature Monitor**

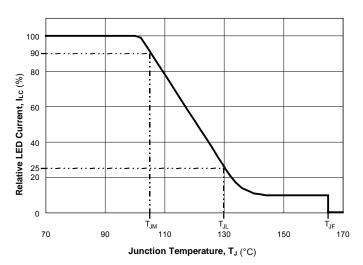

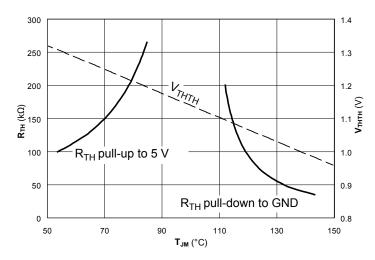

The primary function of the temperature monitor included in the A6260 is to limit the power dissipation of the A6260 and maintain the junction temperature below the maximum. However, it can also be used to reduce LED current as LED temperature increases. This can be achieved by mounting the A6260 on the same thermal substrate as the LEDs, so that temperature rise in the LEDs would also affect the A6260. As the junction temperature of the A6260 increases, the integrated temperature monitor lowers the regulated current level, reducing the dissipated power in the A6260 and in the LEDs. As shown in figure 2, from the full 100% current level (see the LED Current Level section), current is reduced at a rate of 4% per degree Celsius typically, until the point at which the current drops to 25% of the full level. The junction temperature at the 25% current level is defined as  $T_{\rm JL}$ . If the temperature continues to rise above

$T_{JL}$ , the temperature monitor would continue to reduce current, but at a slower rate, until the temperature reaches the overtemperature shutdown temperature,  $T_{JF}$ .

The temperature at which the current reduction begins can be adjusted by changing the voltage on the THTH pin. When THTH is left open, the temperature at which the current reduction begins is typically 98°C. The thermal monitor activation temperature,  $T_{\rm JM}$ , is defined in the Electrical Characteristics table at the 90% current level.

$T_{JM}$  can be increased by reducing the voltage at the THTH pin,  $V_{THTH}$ , and is defined as approximately:

$$T_{\rm JM} = \frac{1.503 - V_{\rm THTH}}{0.00363} \tag{2}$$

where  $T_{IM}$  is in °C.

The equivalent circuit of the THTH pin is a 1.124 V source with a series 5 k $\Omega$  resistor. A resistor connected between THTH and GND will reduce  $V_{THTH}$  and increase  $T_{JM}$ , according to the following formula:

$$V_{\rm THTH} = 1.124 \times \frac{R_{\rm TH}}{5 + R_{\rm TH}} \tag{3}$$

where  $R_{TH}$ , in k $\Omega$ , is the resistor between THTH and GND.

A resistor connected between THTH and a reference supply greater than 2 V will increase  $V_{THTH}$  and reduce  $T_{JM}$ . For

Figure 2. Temperature monitor current reduction

example, with  $R_{TH}$  connected to 5 V,  $V_{THTH}$  will be:

$$V_{\text{THTH}} = 1.124 + (V_{\text{R}} - 1.124) \times \frac{5}{5 + R_{\text{TH}}}$$

(4)

Figure 3 shows how the nominal value of the thermal monitor activation temperature varies with the voltage at THTH and with a pull-down resistor,  $R_{\rm TH}$ , to GND or with a pull-up resistor,  $R_{\rm TH}$ , to 5V.

In extreme cases, if the chip temperature exceeds the overtemperature limit,  $T_{JF}$ , both the sink regulator and the source switch will be disabled. The temperature will continue to be monitored and the output re-activated when the temperature drops below the threshold provided by the specified hysteresis,  $T_{Jhys}$ .

Figure 3.  $T_{JM}$  versus  $R_{TH}$  (pull-up or –down), and  $V_{THTH}$

#### **Thermal Dissipation**

The amount of heat that can pass from the silicon of the A6269 to the surrounding ambient environment depends on the thermal resistance of the structures connected to the A6269. The thermal resistance,  $R_{\theta JA}$ , is a measure of the temperature rise created by power dissipation and is usually measured in degrees Celsius per watt (°C/W).

The temperature rise,  $\Delta T$ , is calculated from the power dissipated,  $P_D$ , and the thermal resistance,  $R_{\theta JA}$ , as:

$$\Delta T = P_{\rm D} \times R_{\rm \theta JA} \tag{5}$$

A thermal resistance from silicon to ambient,  $R_{\theta JA}$ , of approximately 35°C/W can be achieved by mounting the A6269 on a standard FR4 double-sided printed circuit board (PCB) with a copper area of a few square inches on each side of the board under the A6269. Additional improvements in the range of 20% may be achieved by optimizing the PCB design.

#### **Optimizing Thermal Layout**

The features of the printed circuit board, including heat conduction and adjacent thermal sources such as other components, have a very significant effect on the thermal performance of the device. To optimize thermal performance, the following should be taken into account:

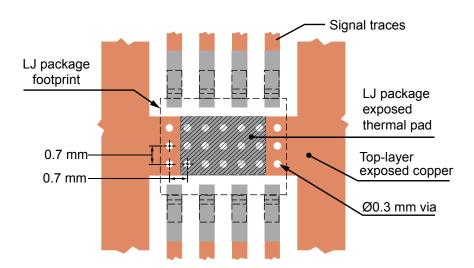

- The device exposed thermal pad should be connected to as much copper area as is available.

- Copper thickness should be as high as possible (for example,

2 oz. or greater for higher power applications).

- The greater the quantity of thermal vias, the better the dissipation. If the expense of vias is a concern, studies have shown that concentrating the vias directly under the device in a tight pattern, as shown in figure 4, has the greatest effect.

- Additional exposed copper area on the opposite side of the board should be connected by means of the thermal vias. The copper should cover as much area as possible.

- Other thermal sources should be placed as remote from the device as possible

Figure 4. Suggested PCB layout for thermal optimization (maximum available bottom-layer copper recommended)

### **Applications Information**

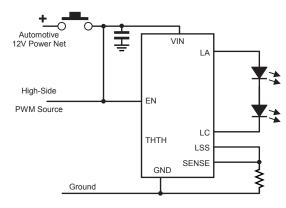

(b) Switched supply plus high-side PWM source

(c) Simple switched supply (lamp replacement)

(d) Low voltage operation

(e) Parallel operation for higher LED current

Figure 4. Typical applications circuits

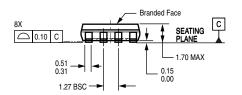

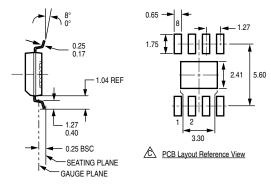

### Package LJ 8-Pin SOICN with Exposed Thermal Pad

For Reference Only; not for tooling use (reference MS-012BA)

Dimensions exclusive of mold flash, gate burrs, and dambar protrusions Exact case and lead configuration at supplier discretion within limits shown

A Terminal #1 mark area

A Exposed thermal pad (bottom surface); dimensions may vary with device

Reference land pattern layout (reference IPC7351 SOIC127P600X175-9AM); all pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to meet application process requirements and PCB layout tolerances; when mounting on a multilayer PCB, thermal vias at the exposed thermal pad land can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

### A6260

## High Brightness LED Current Regulator

#### **Revision History**

| Revision                | Revision Date | Description of Revision     |

|-------------------------|---------------|-----------------------------|

| Rev. 5 January 16, 2013 |               | Add application information |

|                         |               |                             |

$Copyright @2007\mbox{-}2013, Allegro\ MicroSystems, Inc.$

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com