165-Bump BGA Commercial Temp Industrial Temp

# 72Mb SigmaQuad<sup>TM</sup>-II+ Burst of 4 ECCRAM<sup>TM</sup>

400 MHz–300 MHz 1.8 V  $\rm V_{DD}$  1.5 V I/O

#### **Features**

- 2.0 Clock Latency

- On-Chip ECC with virtually zero SER

- Simultaneous Read and Write SigmaQuad™ Interface

- JEDEC-standard pinout and package

- Dual Double Data Rate interface

- Byte Write Capability due to ECC

- Burst of 4 Read and Write

- On-Die Termination (ODT) on Data (D), Byte Write  $(\overline{BW})$ , and Clock  $(K, \overline{K})$  outputs

- 1.8 V + 100/-100 mV core power supply

- 1.5 V HSTL Interface

- Pipelined read operation

- Fully coherent read and write pipelines

- ZQ pin for programmable output drive strength

- IEEE 1149.1 JTAG-compliant Boundary Scan

- Pin-compatible with 18Mb, 36Mb and 144Mb devices

- 165-bump, 15 mm x 17 mm, 1 mm bump pitch BGA package

- RoHS-compliant 165-bump BGA package available

## SigmaQuad™ ECCRAM Overview

The GS8672D19/37BE are built in compliance with the SigmaQuad-II+ ECCRAM pinout standard for Separate I/O synchronous ECCRAMs. They are 75,497,472-bit (72Mb) ECCRAMs. The GS8672D19/37BE SigmaQuad ECCRAMs are just one element in a family of low power, low voltage HSTL I/O ECCRAMs designed to operate at the speeds needed to implement economical high performance networking systems.

## **Clocking and Addressing Schemes**

The GS8672D19/37BE SigmaQuad-II+ ECCRAMs are synchronous devices. They employ two input register clock inputs, K and  $\overline{K}$ . K and  $\overline{K}$  are independent single-ended clock inputs, not differential inputs to a single differential clock input buffer.

Each internal read and write operation in a SigmaQuad-II+ B4 ECCRAM is four times wider than the device I/O bus. An input data bus de-multiplexer is used to accumulate incoming data before it is simultaneously written to the memory array. An output data multiplexer is used to capture the data produced from a single memory array read and then route it to the appropriate output drivers as needed. Therefore the address field of a SigmaQuad-II+ B4 ECCRAM is always two address pins less than the advertised index depth (e.g., the 4M x18 has a 1M addressable index).

## **On-Chip Error Correction Code**

GSI's ECCRAMs implement an ECC algorithm that detects and corrects all single-bit memory errors, including those induced by Soft Error Rate (SER) events such as cosmic rays, alpha particles. The resulting SER of these devices is anticipated to be <0.002 FITs/Mb — a 5-order-of-magnitude improvement over comparable ECCRAMs with no On-Chip ECC, which typically have an SER of 200 FITs/Mb or more. SER quoted above is based on reading taken at sea level.

However, the On-Chip Error Correction (ECC) will be disabled if a "Half Write" operation is initiated. See the **Byte Write Contol** section for further information.

## **Parameter Synopsis**

|       | -400    | -375    | -333    | -300    |

|-------|---------|---------|---------|---------|

| tKHKH | 2.5 ns  | 2.67 ns | 3.0 ns  | 3.3 ns  |

| tKHQV | 0.45 ns | 0.45 ns | 0.45 ns | 0.45 ns |

## 2M x 36 SigmaQuad-II+ ECCRAM—Top View

|   | 1    | 2                | 3         | 4                | 5               | 6               | 7               | 8                | 9         | 10               | 11  |

|---|------|------------------|-----------|------------------|-----------------|-----------------|-----------------|------------------|-----------|------------------|-----|

| A | CQ   | NC<br>(288Mb)    | SA        | W                | BW2             | K               | BW1             | R                | SA        | NF<br>(144Mb)    | CQ  |

| В | Q27  | Q18              | D18       | SA               | BW3             | K               | BW0             | SA               | D17       | Q17              | Q8  |

| С | D27  | Q28              | D19       | V <sub>SS</sub>  | SA              | NF              | SA              | V <sub>SS</sub>  | D16       | Q7               | D8  |

| D | D28  | D20              | Q19       | $V_{SS}$         | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub>  | Q16       | D15              | D7  |

| E | Q29  | D29              | Q20       | V <sub>DDQ</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DDQ</sub> | Q15       | D6               | Q6  |

| F | Q30  | Q21              | D21       | $V_{DDQ}$        | $V_{DD}$        | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>DDQ</sub> | D14       | Q14              | Q5  |

| G | D30  | D22              | Q22       | $V_{DDQ}$        | $V_{DD}$        | $V_{SS}$        | $V_{DD}$        | $V_{DDQ}$        | Q13       | D13              | D5  |

| Н | Doff | V <sub>REF</sub> | $V_{DDQ}$ | $V_{DDQ}$        | $V_{DD}$        | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>DDQ</sub> | $V_{DDQ}$ | V <sub>REF</sub> | ZQ  |

| J | D31  | Q31              | D23       | $V_{DDQ}$        | $V_{DD}$        | V <sub>SS</sub> | $V_{DD}$        | V <sub>DDQ</sub> | D12       | Q4               | D4  |

| K | Q32  | D32              | Q23       | $V_{DDQ}$        | $V_{DD}$        | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>DDQ</sub> | Q12       | D3               | Q3  |

| L | Q33  | Q24              | D24       | $V_{DDQ}$        | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DDQ</sub> | D11       | Q11              | Q2  |

| М | D33  | Q34              | D25       | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub>  | D10       | Q1               | D2  |

| N | D34  | D26              | Q25       | V <sub>SS</sub>  | SA              | SA              | SA              | V <sub>SS</sub>  | Q10       | D9               | D1  |

| P | Q35  | D35              | Q26       | SA               | SA              | QVLD            | SA              | SA               | Q9        | D0               | Q0  |

| R | TDO  | тск              | SA        | SA               | SA              | ODT             | SA              | SA               | SA        | TMS              | TDI |

11 x 15 Bump BGA—15 x 17 mm<sup>2</sup> Body—1 mm Bump Pitch

### Notes:

1. BW0 controls writes to D0:D8; BW1 controls writes to D9:D17; BW2 controls writes to D18:D26; BW3 controls writes to D27:D35.

<sup>2.</sup> Pins A2 and A10 are the expansion addresses.

## 4M x 18 SigmaQuad-II+ ECCRAM—Top View

|   | 1    | 2                | 3                | 4                | 5               | 6               | 7               | 8                | 9                | 10               | 11  |

|---|------|------------------|------------------|------------------|-----------------|-----------------|-----------------|------------------|------------------|------------------|-----|

| A | CQ   | NC<br>(144Mb)    | SA               | w                | BW1             | K               | NF              | R                | SA               | SA               | CQ  |

| В | NC   | Q9               | D9               | SA               | NF              | K               | BW0             | SA               | NC               | NC               | Q8  |

| С | NC   | NC               | D10              | V <sub>SS</sub>  | SA              | NF              | SA              | V <sub>SS</sub>  | NC               | Q7               | D8  |

| D | NC   | D11              | Q10              | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub>  | NC               | NC               | D7  |

| E | NC   | NC               | Q11              | V <sub>DDQ</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DDQ</sub> | NC               | D6               | Q6  |

| F | NC   | Q12              | D12              | V <sub>DDQ</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>DDQ</sub> | NC               | NC               | Q5  |

| G | NC   | D13              | Q13              | $V_{DDQ}$        | V <sub>DD</sub> | V <sub>SS</sub> | $V_{DD}$        | $V_{DDQ}$        | NC               | NC               | D5  |

| Н | Doff | V <sub>REF</sub> | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>REF</sub> | ZQ  |

| J | NC   | NC               | D14              | $V_{DDQ}$        | $V_{DD}$        | V <sub>SS</sub> | V <sub>DD</sub> | $V_{DDQ}$        | NC               | Q4               | D4  |

| K | NC   | NC               | Q14              | $V_{DDQ}$        | $V_{DD}$        | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>DDQ</sub> | NC               | D3               | Q3  |

| L | NC   | Q15              | D15              | V <sub>DDQ</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DDQ</sub> | NC               | NC               | Q2  |

| M | NC   | NC               | D16              | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub>  | NC               | Q1               | D2  |

| N | NC   | D17              | Q16              | V <sub>SS</sub>  | SA              | SA              | SA              | V <sub>SS</sub>  | NC               | NC               | D1  |

| P | NC   | NC               | Q17              | SA               | SA              | QVLD            | SA              | SA               | NC               | D0               | Q0  |

| R | TDO  | тск              | SA               | SA               | SA              | ODT             | SA              | SA               | SA               | TMS              | TDI |

11 x 15 Bump BGA—15 x 17 mm<sup>2</sup> Body—1 mm Bump Pitch

- 1. BW0 controls writes to D0:D8. BW1 controls writes to D9:D17.

- 2. Pin A2 is the expansion address.

## **Pin Description Table**

| Symbol           | Description                     | Туре   | Comments      |

|------------------|---------------------------------|--------|---------------|

| SA               | Synchronous Address Inputs      | Input  | _             |

| R                | Synchronous Read                | Input  | Active Low    |

| W                | Synchronous Write               | Input  | Active Low    |

| BW0-BW3          | Synchronous Byte Writes         | Input  | Active Low    |

| K                | Input Clock                     | Input  | Active High   |

| K                | Input Clock                     | Input  | Active Low    |

| TMS              | Test Mode Select                | Input  | _             |

| TDI              | Test Data Input                 | Input  | _             |

| TCK              | Test Clock Input                | Input  | _             |

| TDO              | Test Data Output                | Output | _             |

| V <sub>REF</sub> | HSTL Input Reference Voltage    | Input  | _             |

| ZQ               | Output Impedance Matching Input | Input  | _             |

| Qn               | Synchronous Data Outputs        | Output | _             |

| Dn               | Synchronous Data Inputs         | Input  | _             |

| Doff             | Disable DLL when low            | Input  | Active Low    |

| CQ               | Output Echo Clock               | Output | _             |

| CQ               | Output Echo Clock               | Output | _             |

| $V_{DD}$         | Power Supply                    | Supply | 1.8 V Nominal |

| V <sub>DDQ</sub> | Isolated Output Buffer Supply   | Supply | 1.5 V Nominal |

| V <sub>SS</sub>  | Power Supply: Ground            | Supply | _             |

| QVLD             | Q Valid Output                  | Output | _             |

| ODT              | On-Die Termination              | Input  | _             |

| NC               | No Connect                      | _      |               |

| NF               | No Function                     | _      | _             |

- 1. NC = Not Connected to die or any other pin

- 2. NF= No Function. There is an electrical connection to this input pin, but the signal has no function in the device. It can be left unconnected, or tied to V<sub>SS</sub> or V<sub>DDQ</sub>.

- 3. K, or  $\overline{K}$  cannot be set to  $V_{REF}$  voltage.

## **Background**

Separate I/O SRAMs, from a system architecture point of view, are attractive in applications where alternating reads and writes are needed. Therefore, the SigmaQuad-II+ ECCRAM interface and truth table are optimized for alternating reads and writes. Separate I/O SRAMs are unpopular in applications where multiple reads or multiple writes are needed because burst read or write transfers from Separate I/O SRAMs can cut the RAM's bandwidth in half.

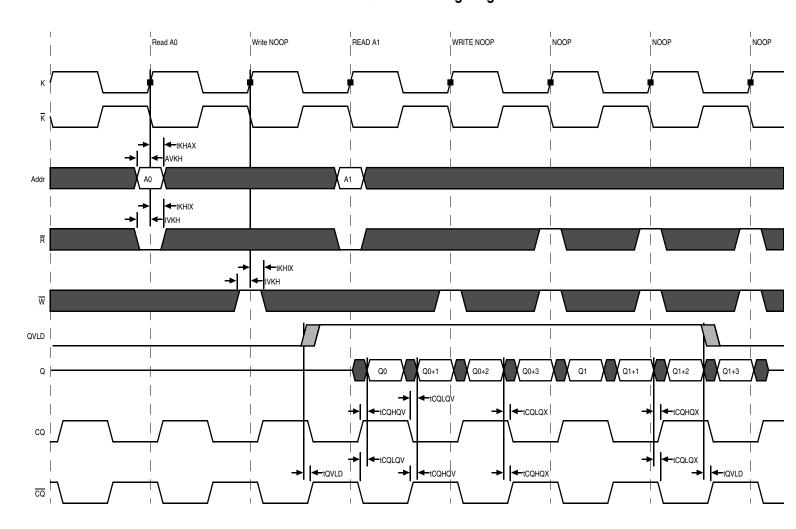

## SigmaQuad-II+ B4 ECCRAM DDR Read

The status of the Address Input,  $\overline{W}$ , and  $\overline{R}$  pins are sampled by the rising edges of K.  $\overline{W}$  and  $\overline{R}$  high causes chip disable. A low on the Read Enable-bar pin,  $\overline{R}$ , begins a read cycle.  $\overline{R}$  is always ignored if the previous command loaded was a read command. Clocking in a high on the Read Enable-bar pin,  $\overline{R}$ , begins a read port deselect cycle.

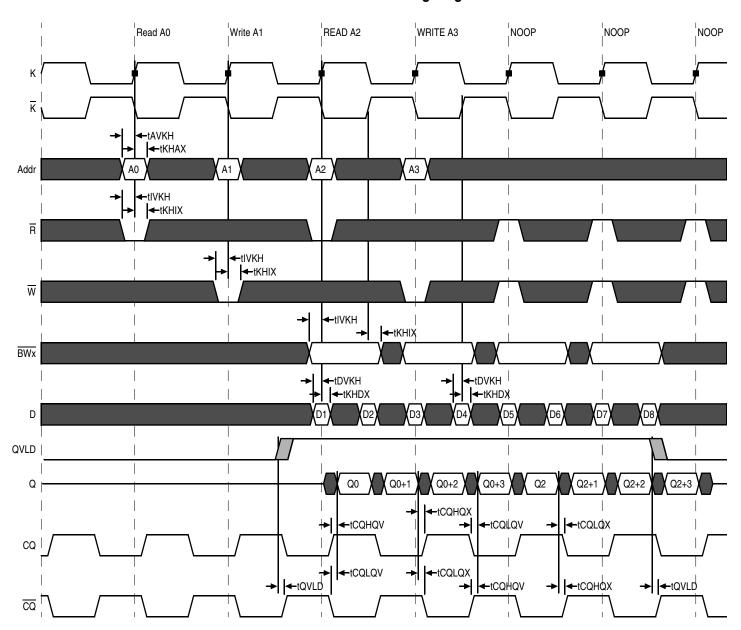

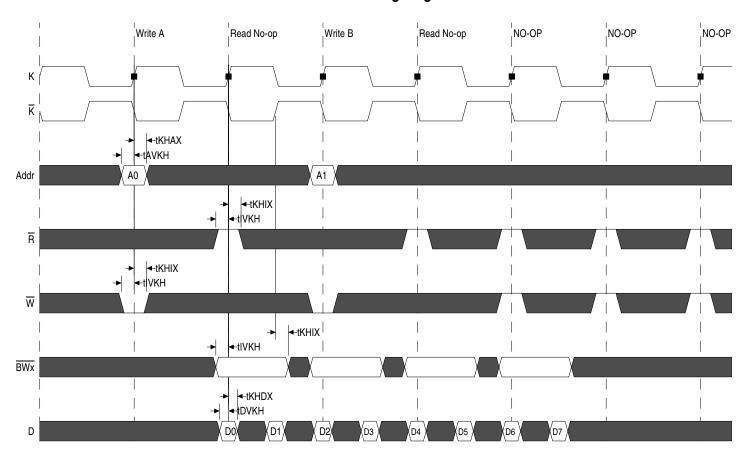

### SigmaQuad-II+ B4 ECCRAM DDR Write

The status of the Address Input,  $\overline{W}$ , and  $\overline{R}$  pins are sampled by the rising edges of K.  $\overline{W}$  and  $\overline{R}$  high causes chip disable. A low on the Write Enable-bar pin,  $\overline{W}$ , and a high on the Read Enable-bar pin,  $\overline{R}$ , begins a write cycle.  $\overline{W}$  is always ignored if the previous command was a write command. Data is clocked in by the next rising edge of K, the rising edge of  $\overline{K}$  after that, the next rising edge of K, and finally by the next rising edge of the K that follows.

## Power-Up Sequence for SigmaQuad-II+ ECCRAMs

SigmaQuad-II+ ECCRAMs must be powered-up in a specific sequence in order to avoid undefined operations.

- 1. After power supplies power-up and clocks  $(K, \overline{K})$  are stablized, 163,840 cycles are required to set Output Driver Impedance.

- 2. Thereafter, an additional 65,536 clock cycles are required to lock the DLL after it has been enabled.

- 3. Begin Read and Write operations.

For more information, read AN1021 SigmaQuad and SigmaDDR Power-Up.

### **On-Chip Error Correction**

SigmaQuad-II+ ECCRAMs implement a single-bit error detection and correction algorithm (specifically, a Hamming Code) on each DDR data word (comprising two 9-bit data bytes) transmitted on each 9-bit data bus (i.e., transmitted on D/Q[8:0], D/Q[17:9], D/Q[26:18], or D/Q[35:27]). To accomplish this, 5 ECC parity bits (invisible to the user) are utilized per every 18 data bits (visible to the user).

The ECC algorithm neither corrects nor detects multi-bit errors. However, GSI ECCRAMs are architected in such a way that a single SER event very rarely causes a multi-bit error across any given "transmitted data unit", where a "transmitted data unit" represents the data transmitted as the result of a single read or write operation to a particular address. The extreme rarity of multi-bit errors results in the SER mentioned previously (i.e., <0.002 FITs/Mb measured at sea level).

Not only does the on-chip ECC significantly improve SER performance, but it also frees up the entire memory array for data storage. Very often SRAM applications allocate 1/9th of the memory array (i.e., one "error bit" per eight "data bits", in any 9-bit "data byte") for error detection (either simple parity error detection, or system-level ECC error detection and correction). Such error-bit allocation is unnecessary with ECCRAMs —the entire memory array can be utilized for data storage, effectively providing 12.5% greater storage capacity compared to SRAMs of the same density not equipped with on-chip ECC.

## **Special Functions**

### **Byte Write Control**

Byte Write Enable pins are sampled at the same time that Data In is sampled. A High on the Byte Write Enable pin associated with a particular byte (e.g.,  $\overline{BW0}$  controls D0–D8 inputs) will inhibit the storage of that particular byte, leaving whatever data may be stored at the current address at that byte location undisturbed. Any or all of the Byte Write Enable pins may be driven High or Low during the data in sample times in a write sequence.

Each write enable command and write address loaded into the RAM provides the base address for a 4-beat data transfer. The x18 version of the RAM, for example, may write 72 bits in association with each address loaded. Any 9-bit byte may be masked in any write sequence.

**Note:** If "Half Write" operations (i.e., write operations in which a  $\overline{BW}n$  pin is asserted for only half of a DDR write data transfer on the associated 9-bit data bus, causing only 9 bits of the 18-bit DDR data word to be written) are initiated, the on-chip ECC will be disabled for as long as the SRAM remains powered up thereafter. This must be done because ECC is implemented across entire 18-bit data words, rather than across individual 9-bit data bytes.

### **Byte Write Truth Table**

The truth table below applies to write operations to Address "m", where Address "m" is the 18-bit memory location comprising the 2 beats of DDR write data associated with each  $\overline{BW}n$  pin in a given clock cycle.

| B\              | Nn                         | Input Data Byte n |                            |            |                                |

|-----------------|----------------------------|-------------------|----------------------------|------------|--------------------------------|

| ↑ K<br>(Beat 1) | ↑ <del>K</del><br>(Beat 2) | ↑K<br>(Beat 1)    | ↑ <del>K</del><br>(Beat 2) | Operation  | Result                         |

| 0               | 0                          | D0                | D1                         | Full Write | D0 and D1 written to Address m |

| 0               | 1                          | D0                | Х                          | Half Write | Only D0 written to Address m   |

| 1               | 0                          | Х                 | D1                         | Half Write | Only D1 written to Address m   |

| 1               | 1                          | Х                 | Х                          | Abort      | Address m unchanged            |

- 1. BW0 is associated with Input Data Byte D[8:0].

- 2. BW1 is associated with Input Data Byte D[17:9].

- 3. BW2 is associated with Input Data Byte D[26:18] (in x36 only).

- 4. BW3 is associated with Input Data Byte D[35:27] (in x36 only).

- 5. ECC is disabled if a "Half Write" operation is initiated.

- 6. Although these devices execute Burst of 4 (i.e., 4-beat) write operations, for the purposes of this table they should be viewed as a pair of Burst of 2 (i.e., 2-beat) write operations. As such, valid/allowable Burst of 4 write operations only comprise (any combination of) Burst of 2 Full Write and/or Abort Write operations, as defined above.

### **FLXDrive-II Output Driver Impedance Control**

HSTL I/O SigmaQuad-II+ ECCRAMs are supplied with programmable impedance output drivers. The ZQ pin must be connected to  $V_{SS}$  via an external resistor, RQ, to allow the ECCRAM to monitor and adjust its output driver impedance. The value of RQ must be 5X the value of the desired RAM output impedance. The allowable range of RQ to guarantee impedance matching continuously is between 175 $\Omega$  and 350 $\Omega$ . Periodic readjustment of the output driver impedance is necessary as the impedance is affected by drifts in supply voltage and temperature. The ECCRAM's output impedance circuitry compensates for drifts in supply voltage and temperature. A clock cycle counter periodically triggers an impedance evaluation, resets and counts again. Each impedance evaluation may move the output driver impedance level one step at a time towards the optimum level. The output driver is implemented with discrete binary weighted impedance steps.

## **Input Termination Impedance Control**

These SigmaQuad-II+ ECCRAMs are supplied with programmable input termination on Data (D), Byte Write  $(\overline{BW})$ , and Clock  $(K/\overline{K})$  input receivers. Input termination can be enabled or disabled via the ODT pin (6R). When the ODT pin is tied Low (or left floating -the pin has a small pull-down resistor), input termination is disabled. When the ODT pin is tied High, input termination is enabled. Termination impedance is programmed via the same RQ resistor (connected between the ZQ pin and  $V_{SS}$ ) used to program output driver impedance, and is nominally RQ\*0.6 Thevenin-equivalent when RQ is between 175 $\Omega$  and 250 $\Omega$ . Periodic readjustment of the termination impedance occurs to compensate for drifts in supply voltage and temperature, in the same manner as for driver impedance (see above).

#### Note:

When ODT = 1, Data (D), Byte Write ( $\overline{BW}$ ), and Clock (K,  $\overline{K}$ ) input termination is always enabled. Consequently, D,  $\overline{BW}$ , K,  $\overline{K}$  inputs should always be driven High or Low; they should never be tri-stated (i.e., in a High-Z state). If the inputs are tri-stated, the input termination will pull the signal to  $V_{DDQ}/2$  (i.e., to the switch point of the diff-amp receiver), which could cause the receiver to enter a meta-stable state, resulting in the receiver consuming more power than it normally would. This could result in the device's operating currents being higher.

## Separate I/O SigmaQuad II+ B4 ECCRAM Truth Table

| Previous<br>Operation      | A                           | R                           | w                           | Current<br>Operation     | D                          | D                               | D                          | D                                   | Q                          | Q                               | Q                          | Q                                  |

|----------------------------|-----------------------------|-----------------------------|-----------------------------|--------------------------|----------------------------|---------------------------------|----------------------------|-------------------------------------|----------------------------|---------------------------------|----------------------------|------------------------------------|

| K ↑<br>(t <sub>n-1</sub> ) | K<br>↑<br>(t <sub>n</sub> ) | K<br>↑<br>(t <sub>n</sub> ) | K<br>↑<br>(t <sub>n</sub> ) | K ↑<br>(t <sub>n</sub> ) | K ↑<br>(t <sub>n+1</sub> ) | <b>K</b> ↑ (t <sub>n+1½</sub> ) | K ↑<br>(t <sub>n+2</sub> ) | <del>K</del> ↑ (t <sub>n+2½</sub> ) | K ↑<br>(t <sub>n+2</sub> ) | <b>K</b> ↑ (t <sub>n+2½</sub> ) | K ↑<br>(t <sub>n+3</sub> ) | <b>K</b> ↑<br>(t <sub>n+3½</sub> ) |

| Deselect                   | Х                           | 1                           | 1                           | Deselect                 | Х                          | Х                               | _                          | _                                   | Hi-Z                       | Hi-Z                            | _                          |                                    |

| Write                      | Х                           | 1                           | Х                           | Deselect                 | D2                         | D3                              | _                          | _                                   | Hi-Z                       | Hi-Z                            | _                          | _                                  |

| Read                       | Х                           | Х                           | 1                           | Deselect                 | Х                          | Х                               | _                          | _                                   | Q2                         | Q3                              | _                          | _                                  |

| Deselect                   | ٧                           | 1                           | 0                           | Write                    | D0                         | D1                              | D2                         | D3                                  | Hi-Z                       | Hi-Z                            | _                          | _                                  |

| Deselect                   | ٧                           | 0                           | Х                           | Read                     | Х                          | Х                               | _                          | _                                   | Q0                         | Q1                              | Q2                         | Q3                                 |

| Read                       | ٧                           | Х                           | 0                           | Write                    | D0                         | D1                              | D2                         | D3                                  | Q2                         | Q3                              | _                          | _                                  |

| Write                      | ٧                           | 0                           | Х                           | Read                     | D2                         | D3                              | _                          | _                                   | Q0                         | Q1                              | Q2                         | Q3                                 |

- 1. "1" = input "high"; "0" = input "low"; "V" = input "valid"; "X" = input "don't care"

- 2. "—" indicates that the input requirement or output state is determined by the next operation.

- 3. Q0, Q1, Q2, and Q3 indicate the first, second, third, and fourth pieces of output data transferred during Read operations.

- 4. D0, D1, D2, and D3 indicate the first, second, third, and fourth pieces of input data transferred during Write operations.

- 5. Users should not clock in metastable addresses.

- 6. When On-Die Termination is disabled (ODT = 0), Q drivers are disabled (i.e., Q pins are tri-stated) for one cycle in response to NOP and Write commands, 2.0 cycles after the command is sampled, except when preceded by a Read command.

- 7. When On-Die Termination is enabled (ODT = 1), Q drivers are enabled Low (i.e., Q pins are driven Low) for one cycle in response to NOP and Write commands, 2.0 cycles after the command is sampled, except when preceded by a Read command. This is done so that the ASIC/ Controller can enable On-Die Termination on its data inputs without having to cope with the termination pulling tri-stated data inputs to V<sub>DDQ</sub>/2 (i.e., to the switch point of the data input receivers).

## **Byte Write Clock Truth Table**

| BW                         | BW                              | BW                         | BW                              | Current Operation                                                                                      | D                          | D                               | D                          | D                           |

|----------------------------|---------------------------------|----------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------|----------------------------|-----------------------------|

| K ↑<br>(t <sub>n+1</sub> ) | <b>K</b> ↑ (t <sub>n+1½</sub> ) | K ↑<br>(t <sub>n+2</sub> ) | <b>K</b> ↑ (t <sub>n+2½</sub> ) | K ↑<br>(t <sub>n</sub> )                                                                               | K ↑<br>(t <sub>n+1</sub> ) | <b>K</b> ↑ (t <sub>n+1½</sub> ) | K ↑<br>(t <sub>n+2</sub> ) | ⊼ ↑<br>(t <sub>n+2½</sub> ) |

| Т                          | Т                               | Т                          | Т                               | $\frac{\text{Write}}{\text{Dx stored if }\overline{\text{BWn}} = 0 \text{ in all four data transfers}$ | D0                         | D2                              | D3                         | D4                          |

| Т                          | F                               | F                          | F                               | $\frac{\text{Write}}{\text{Dx stored if }\overline{\text{BWn}} = 0 \text{ in 1st data transfer only}$  | D0                         | Х                               | X                          | Х                           |

| F                          | Т                               | F                          | F                               | $\frac{\text{Write}}{\text{Dx stored if }\overline{\text{BWn}} = 0 \text{ in 2nd data transfer only}$  | Х                          | D1                              | Х                          | х                           |

| F                          | F                               | Т                          | F                               | $\frac{\text{Write}}{\text{Dx stored if }\overline{\text{BWn}} = 0 \text{ in 3rd data transfer only}}$ | Х                          | Х                               | D2                         | Х                           |

| F                          | F                               | F                          | T                               | $\frac{\text{Write}}{\text{Dx stored if }\overline{\text{BWn}} = 0 \text{ in 4th data transfer only}}$ | Х                          | Х                               | Х                          | D3                          |

| F                          | F                               | F                          | F                               | Write Abort<br>No Dx stored in any of the four data transfers                                          | Х                          | Х                               | Х                          | Х                           |

- "1" = input "high"; "0" = input "low"; "X" = input "don't care"; "T" = input "true"; "F" = input "false".

If one or more BWn = 0, then BW = "T", else BW = "F".

## x36 Byte Write Enable (BWn) Truth Table

| BW0 | BW1 | BW2 | BW3 | D0-D8      | D9-D17             | D18-D26            | D27-D35    |

|-----|-----|-----|-----|------------|--------------------|--------------------|------------|

| 1   | 1   | 1   | 1   | Don't Care | Don't Care         | Don't Care         | Don't Care |

| 0   | 1   | 1   | 1   | Data In    | Don't Care         | Don't Care         | Don't Care |

| 1   | 0   | 1   | 1   | Don't Care | Data In Don't Care |                    | Don't Care |

| 0   | 0   | 1   | 1   | Data In    | Data In Don't Care |                    | Don't Care |

| 1   | 1   | 0   | 1   | Don't Care | Don't Care         | Data In            | Don't Care |

| 0   | 1   | 0   | 1   | Data In    | Don't Care Data In |                    | Don't Care |

| 1   | 0   | 0   | 1   | Don't Care | Data In            | Data In Data In    |            |

| 0   | 0   | 0   | 1   | Data In    | Data In            | Data In            | Don't Care |

| 1   | 1   | 1   | 0   | Don't Care | Don't Care         | Don't Care         | Data In    |

| 0   | 1   | 1   | 0   | Data In    | Don't Care         | Don't Care         | Data In    |

| 1   | 0   | 1   | 0   | Don't Care | Data In            | Don't Care         | Data In    |

| 0   | 0   | 1   | 0   | Data In    | Data In            | Don't Care         | Data In    |

| 1   | 1   | 0   | 0   | Don't Care | Don't Care         | Data In            | Data In    |

| 0   | 1   | 0   | 0   | Data In    | Don't Care         | Don't Care Data In |            |

| 1   | 0   | 0   | 0   | Don't Care | Data In            | Data In Data In    |            |

| 0   | 0   | 0   | 0   | Data In    | Data In            | Data In            | Data In    |

## x18 Byte Write Enable (BWn) Truth Table

| BW0 | BW1 | D0-D8      | D9-D17     |

|-----|-----|------------|------------|

| 1   | 1   | Don't Care | Don't Care |

| 0   | 1   | Data In    | Don't Care |

| 1   | 0   | Don't Care | Data In    |

| 0   | 0   | Data In    | Data In    |

### **Absolute Maximum Ratings**

(All voltages reference to  $V_{SS}$ )

| Symbol           | Description                                   | Value                                                | Unit  |

|------------------|-----------------------------------------------|------------------------------------------------------|-------|

| $V_{DD}$         | Voltage on V <sub>DD</sub> Pins               | -0.5 to 2.4                                          | V     |

| V <sub>DDQ</sub> | Voltage in V <sub>DDQ</sub> Pins              | -0.5 to V <sub>DD</sub>                              | V     |

| V <sub>REF</sub> | Voltage in V <sub>REF</sub> Pins              | -0.5 to V <sub>DDQ</sub>                             | V     |

| V <sub>I/O</sub> | Voltage on I/O Pins                           | $-0.5$ to V <sub>DDQ</sub> +0.5 ( $\leq$ 2.4 V max.) | V     |

| V <sub>IN</sub>  | Input Voltage (Address, Control, Data, Clock) | $-0.5$ to V <sub>DDQ</sub> +0.5 ( $\leq$ 2.4 V max.) | V     |

| V <sub>TIN</sub> | Input Voltage (TCK, TMS, TDI)                 | $-0.5$ to V <sub>DDQ</sub> +0.5 ( $\leq$ 2.4 V max.) | V     |

| I <sub>IN</sub>  | Input Current on Any Pin                      | +/-100                                               | mA dc |

| I <sub>OUT</sub> | Output Current on Any I/O Pin                 | +/-100                                               | mA dc |

| T <sub>J</sub>   | Maximum Junction Temperature                  | 120                                                  | °C    |

| T <sub>STG</sub> | Storage Temperature                           | -55 to 125                                           | °C    |

#### Note:

Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Recommended Operating Conditions, for an extended period of time, may affect reliability of this component.

## **Recommended Operating Conditions**

## **Power Supplies**

| Parameter          | Symbol    | Min.                       | Тур. | Max.               | Unit |

|--------------------|-----------|----------------------------|------|--------------------|------|

| Supply Voltage     | $V_{DD}$  | 1.7                        | 1.8  | 1.9                | V    |

| I/O Supply Voltage | $V_{DDQ}$ | 1.4                        | _    | 1.6                | V    |

| Reference Voltage  | $V_{REF}$ | V <sub>DDQ</sub> /2 – 0.05 |      | $V_{DDQ}/2 + 0.05$ | V    |

### Note:

The power supplies need to be powered up simultaneously or in the following sequence:  $V_{DD}$ ,  $V_{DDQ}$ ,  $V_{REF}$ , followed by signal inputs. The power down sequence must be the reverse.  $V_{DDQ}$  must not exceed  $V_{DD}$ . For more information, read **AN1021 SigmaQuad and SigmaDDR Power-Up**.

## **Operating Temperature**

| Parameter                                            | Symbol         | Min. | Тур. | Max. | Unit |

|------------------------------------------------------|----------------|------|------|------|------|

| Junction Temperature<br>(Commercial Range Versions)  | TJ             | 0    | 25   | 85   | °C   |

| Junction Temperature<br>(Industrial Range Versions)* | T <sub>J</sub> | -40  | 25   | 100  | °C   |

### Note:

Rev: 1.01b 6/2012 12/29 © 2011, GSI Technology

<sup>\*</sup> The part numbers of Industrial Temperature Range versions end with the character "I". Unless otherwise noted, all performance specifications quoted are evaluated for worst case in the temperature range marked on the device.

## Thermal Impedance

| Package | Test PCB<br>Substrate | θ JA (C°/W)<br>Airflow = 0 m/s | $\theta$ JA (C°/W)<br>Airflow = 1 m/s | $\theta$ JA (C°/W)<br>Airflow = 2 m/s | θ JB (C°/W) | θ JC (C°/W) |

|---------|-----------------------|--------------------------------|---------------------------------------|---------------------------------------|-------------|-------------|

| 165 BGA | 4-layer               | 15.25                          | 12.38                                 | 11.41                                 | 4.79        | 1.31        |

### Notes:

- 1. Thermal Impedance data is based on a number of of samples from mulitple lots and should be viewed as a typical number.

- Please refer to JEDEC standard JESD51-6.

- 3. The characteristics of the test fixture PCB influence reported thermal characteristics of the device. Be advised that a good thermal path to the PCB can result in cooling or heating of the RAM depending on PCB temperature.

## **HSTL I/O DC Input Characteristics**

| Parameter               | Symbol           | Min                        | Max                        | Units | Notes |

|-------------------------|------------------|----------------------------|----------------------------|-------|-------|

| Input Reference Voltage | V <sub>REF</sub> | V <sub>DDQ</sub> /2 – 0.05 | V <sub>DDQ</sub> /2 + 0.05 | V     | _     |

| Input High Voltage      | V <sub>IH1</sub> | V <sub>REF</sub> + 0.1     | V <sub>DDQ</sub> + 0.3     | V     | 1     |

| Input Low Voltage       | V <sub>IL1</sub> | -0.3                       | V <sub>REF</sub> – 0.1     | V     | 1     |

| Input High Voltage      | V <sub>IH2</sub> | 0.7 * V <sub>DDQ</sub>     | V <sub>DDQ</sub> + 0.3     | V     | 2,3   |

| Input Low Voltage       | V <sub>IL2</sub> | -0.3                       | 0.3 * V <sub>DDQ</sub>     | V     | 2,3   |

### Notes:

- 1. Parameters apply to  $\underline{K}, \overline{K}, SA, D, \overline{R}, \overline{W}, \overline{BW}$  during normal operation and JTAG boundary scan testing.

- 2. Parameters apply to Doff, ODT during normal operation and JTAG boundary scan testing.

- 3. Parameters apply to ZQ during JTAG boundary scan testing only.

## **HSTL I/O AC Input Characteristics**

| Parameter               | Symbol           | Min                        | Max                        | Units | Notes |

|-------------------------|------------------|----------------------------|----------------------------|-------|-------|

| Input Reference Voltage | V <sub>REF</sub> | V <sub>DDQ</sub> /2 – 0.08 | V <sub>DDQ</sub> /2 + 0.08 | V     | _     |

| Input High Voltage      | V <sub>IH1</sub> | V <sub>REF</sub> + 0.2     | V <sub>DDQ</sub> + 0.5     | V     | 1,2,3 |

| Input Low Voltage       | V <sub>IL1</sub> | -0.5                       | V <sub>REF</sub> - 0.2     | V     | 1,2,3 |

| Input High Voltage      | V <sub>IH2</sub> | V <sub>DDQ</sub> - 0.2     | V <sub>DDQ</sub> + 0.5     | V     | 4,5   |

| Input Low Voltage       | V <sub>IL2</sub> | -0.5                       | 0.2                        | V     | 4,5   |

#### Notes:

- 1.  $V_{IH(MAX)}$  and  $V_{IL(MIN)}$  apply for pulse widths less than one-quarter of the cycle time.

- 2. Input rise and fall times must be a minimum of 1 V/ns, and within 10% of each other.

- 3. Parameters apply to K, K, SA, D, R, W, BW during normal operation and JTAG boundary scan testing.

- 4. Parameters apply to Doff, ODT during normal operation and JTAG boundary scan testing.

Rev: 1.01b 6/2012 13/29 © 2011, GSI Technology

## Capacitance

$(T_A = 25^{\circ}C, f = 1 \text{ MHz}, V_{DD} = 1.8 \text{ V})$

| Parameter          | Symbol           | Test conditions        | Тур. | Max. | Unit |

|--------------------|------------------|------------------------|------|------|------|

| Input Capacitance  | C <sub>IN</sub>  | V <sub>IN</sub> = 0 V  | 4    | 5    | pF   |

| Output Capacitance | C <sub>OUT</sub> | V <sub>OUT</sub> = 0 V | 4.5  | 5.5  | pF   |

### Note:

This parameter is sample tested.

## **AC Test Conditions**

| Parameter              | Conditions          |

|------------------------|---------------------|

| Input high level       | 1.25 V              |

| Input low level        | 0.25 V              |

| Max. input slew rate   | 2 V/ns              |

| Input reference level  | 0.75 V              |

| Output reference level | V <sub>DDQ</sub> /2 |

### Note:

Test conditions as specified with output loading as shown unless otherwise noted.

## **AC Test Load Diagram**

$$\begin{array}{c|c}

DQ \\

\hline

& & \\

\hline

& & \\

\hline

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

&$$

$$\begin{split} RQ &= 250~\Omega~(HSTL~I/O) \\ V_{REF} &= 0.75~V \end{split}$$

## **Input and Output Leakage Characteristics**

| Parameter                                | Symbol              | Test Conditions                                             | Min.    | Max    |

|------------------------------------------|---------------------|-------------------------------------------------------------|---------|--------|

| Input Leakage Current (except mode pins) | I <sub>IL</sub>     | V <sub>IN</sub> = 0 to V <sub>DDQ</sub>                     | –2 uA   | 2 uA   |

| Doff                                     | I <sub>ILDOFF</sub> | $V_{IN} = 0$ to $V_{DDQ}$                                   | –100 uA | 2 uA   |

| ODT                                      | I <sub>IL ODT</sub> | $V_{IN} = 0$ to $V_{DDQ}$                                   | –2 uA   | 100 uA |

| Output Leakage Current                   | l <sub>OL</sub>     | Output Disable,<br>V <sub>OUT</sub> = 0 to V <sub>DDQ</sub> | −2 uA   | 2 uA   |

Rev: 1.01b 6/2012 14/29 © 2011, GSI Technology

## **Programmable Impedance HSTL Output Driver DC Electrical Characteristics**

| Parameter               | Symbol           | Min.                       | Max.                       | Units | Notes |

|-------------------------|------------------|----------------------------|----------------------------|-------|-------|

| Output High Voltage     | V <sub>OH1</sub> | V <sub>DDQ</sub> /2 – 0.12 | V <sub>DDQ</sub> /2 + 0.12 | V     | 1     |

| Output Low Voltage      | V <sub>OL1</sub> | V <sub>DDQ</sub> /2 – 0.12 | V <sub>DDQ</sub> /2 + 0.12 | V     | 2     |

| Output High Voltage     | V <sub>OH2</sub> | V <sub>DDQ</sub> – 0.2     | $V_{\mathrm{DDQ}}$         | V     | 3, 4  |

| Output Low Voltage      | V <sub>OL2</sub> | V <sub>ss</sub>            | 0.2                        | V     | 3, 5  |

| Output Driver Impedance | R <sub>OUT</sub> | (RQ/5) * 0.88              | (RQ/5) * 1.12              | Ω     | 6, 7  |

- 1.  $I_{OH} = (V_{DDQ}/2) / (RQ/5) + /-15\% @ V_{OH} = V_{DDQ}/2 (for: 175\Omega \le RQ \le 275\Omega)$

- 2.  $I_{OL} = (V_{DDQ}/2) / (RQ/5) + /-15\% @ V_{OL} = V_{DDQ}/2 \text{ (for: } 175\Omega \le RQ \le 275\Omega)$

- 3.  $0\Omega \le RQ \le \infty\Omega$

- 4.  $I_{OH} = -1.0 \text{ mA}$

- 5.  $I_{OL} = 1.0 \text{ mA}$

- 6. Parameter applies when  $175\Omega \le RQ \le 275\Omega$

- 7. Tested at  $V_{OUT} = V_{DDQ} * 0.2$  and  $V_{DDQ} * 0.8$

## **Operating Currents**

|                                 |                 |                                                                             | -4               | .00                | -3               | 75                 | -3               | 33                 | -3               | 00                 | S     |

|---------------------------------|-----------------|-----------------------------------------------------------------------------|------------------|--------------------|------------------|--------------------|------------------|--------------------|------------------|--------------------|-------|

| Parameter                       | Symbol          | Test Conditions                                                             | 0°<br>to<br>70°C | –40°<br>to<br>85°C | 0°<br>to<br>70°C | –40°<br>to<br>85°C | 0°<br>to<br>70°C | –40°<br>to<br>85°C | 0°<br>to<br>70°C | –40°<br>to<br>85°C | Notes |

| Operating Current (x36):<br>DDR | I <sub>DD</sub> | $V_{DD}$ = Max, $I_{OUT}$ = 0 mA<br>Cycle Time $\geq t_{KHKH}$ Min          | 1860<br>mA       | 1880<br>mA         | 1760<br>mA       | 1780<br>mA         | 1600<br>mA       | 1620<br>mA         | 1480<br>mA       | 1500<br>mA         | 2, 3  |

| Operating Current (x18):<br>DDR | I <sub>DD</sub> | $V_{DD}$ = Max, $I_{OUT}$ = 0 mA<br>Cycle Time $\geq$ t <sub>KHKH</sub> Min | 1360<br>mA       | 1380<br>mA         | 1300<br>mA       | 1320<br>mA         | 1190<br>mA       | 1210<br>mA         | 1100<br>mA       | 1120<br>mA         | 2, 3  |

- 1. Power measured with output pins floating.

- 2. Minimum cycle,  $I_{OUT} = 0 \text{ mA}$

- 3. Operating current is calculated with 50% read cycles and 50% write cycles.

### **AC Electrical Characteristics**

| D                                                       | 0                                            | -4    | 100  | -3    | 75   | -33   | 33   | -30   | 00   | its   | se        |

|---------------------------------------------------------|----------------------------------------------|-------|------|-------|------|-------|------|-------|------|-------|-----------|

| Parameter                                               | Symbol                                       | Min   | Max  | Min   | Max  | Min   | Max  | Min   | Max  | Units | Notes     |

| Clock                                                   |                                              |       |      |       | •    |       |      |       |      |       |           |

| K, K Clock Cycle Time                                   | t <sub>KHKH</sub>                            | 2.5   | 6.0  | 2.66  | 6.0  | 3.0   | 6.0  | 3.3   | 6.0  | ns    |           |

| tK Variable                                             | t <sub>KVar</sub>                            | _     | 0.2  | _     | 0.2  | _     | 0.2  | _     | 0.2  | ns    | 4         |

| K, K Clock High Pulse Width                             | t <sub>KHKL</sub>                            | 0.4   | _    | 0.4   | _    | 0.4   | _    | 0.4   | _    | cycle |           |

| K, K Clock Low Pulse Width                              | t <sub>KLKH</sub>                            | 0.4   | _    | 0.4   | _    | 0.4   | _    | 0.4   | _    | cycle |           |

| K to K High                                             | t <sub>KHK</sub> H                           | 1.06  | _    | 1.13  | _    | 1.28  | _    | 1.40  | _    | ns    |           |

| K to K High                                             | t <sub>K</sub> hkh                           | 1.06  | _    | 1.13  | _    | 1.28  | _    | 1.40  | _    | ns    |           |

| DLL Lock Time                                           | t <sub>KLock</sub>                           | 64K   | _    | 64K   | _    | 64K   | _    | 64K   | _    | cycle | 5         |

| K Static to DLL reset                                   | t <sub>KReset</sub>                          | 30    | _    | 30    | _    | 30    | _    | 30    | _    | ns    |           |

| Output Times                                            | L                                            |       |      | _1    |      |       | I    |       | I    |       | <u>.L</u> |

| K, K Clock High to Data Output Valid                    | t <sub>KHQV</sub>                            | _     | 0.45 | _     | 0.45 | _     | 0.45 | _     | 0.45 | ns    |           |

| K, K Clock High to Data Output Hold                     | t <sub>KHQX</sub>                            | -0.45 | _    | -0.45 | _    | -0.45 | _    | -0.45 | _    | ns    |           |

| K, K Clock High to Echo Clock Valid                     | t <sub>KHCQV</sub>                           | _     | 0.45 | _     | 0.45 | _     | 0.45 | _     | 0.45 | ns    |           |

| K, K Clock High to Echo Clock Hold                      | t <sub>KHCQX</sub>                           | -0.45 | _    | -0.45 | _    | -0.45 | _    | -0.45 | _    | ns    |           |

| CQ, CQ High Output Valid                                | t <sub>CQHQV</sub>                           | _     | 0.2  | _     | 0.2  | _     | 0.2  | _     | 0.2  | ns    |           |

| CQ, CQ High Output Hold                                 | t <sub>CQHQX</sub>                           | -0.2  | _    | -0.2  | _    | -0.2  | _    | -0.2  | _    | ns    |           |

| CQ, CQ High to QVLD                                     | t <sub>QVLD</sub>                            | -0.2  | 0.2  | -0.2  | 0.2  | -0.2  | 0.2  | -0.2  | 0.2  | ns    |           |

| CQ Phase Distortion                                     | tсан <del>са</del> н<br>t <del>са</del> нсан | 1.0   | _    | 1.08  | _    | 1.25  | _    | 1.40  | _    | ns    |           |

| K Clock High to Data Output High-Z                      | t <sub>KHQZ</sub>                            | _     | 0.45 | _     | 0.45 | _     | 0.45 | _     | 0.45 | ns    |           |

| K Clock High to Data Output Low-Z                       | t <sub>KHQX1</sub>                           | -0.45 | _    | -0.45 | _    | -0.45 | _    | -0.45 | _    | ns    |           |

| Setup Times                                             |                                              |       | !    | !     |      | •     | !    |       |      |       |           |

| Address Input Setup Time                                | t <sub>AVKH</sub>                            | 0.4   | _    | 0.4   | _    | 0.4   | _    | 0.4   | _    | ns    | 1         |

| Control Input Setup Time $(\overline{R}, \overline{W})$ | t <sub>IVKH</sub>                            | 0.4   | _    | 0.4   | _    | 0.4   | _    | 0.4   | _    | ns    | 2         |

| Control Input Setup Time (BWX)                          | t <sub>IVKH</sub>                            | 0.28  | _    | 0.28  | _    | 0.28  | _    | 0.28  | _    | ns    | 3         |

| Data Input Setup Time                                   | t <sub>DVKH</sub>                            | 0.28  | _    | 0.28  | _    | 0.28  | _    | 0.28  | _    | ns    |           |

| Hold Times                                              |                                              |       |      | _     |      |       |      | _     |      |       |           |

| Address Input Hold Time                                 | t <sub>KHAX</sub>                            | 0.4   | _    | 0.4   | _    | 0.4   | _    | 0.4   | _    | ns    | 1         |

| Control Input Hold Time $(\overline{R}, \overline{W})$  | t <sub>KHIX</sub>                            | 0.4   | _    | 0.4   | _    | 0.4   | _    | 0.4   | _    | ns    | 2         |

| Control Input Hold Time (BWX)                           | t <sub>KHIX</sub>                            | 0.28  | _    | 0.28  | _    | 0.28  | _    | 0.28  | _    | ns    | 3         |

| Data Input Hold Time                                    | t <sub>KHDX</sub>                            | 0.28  | _    | 0.28  | _    | 0.28  | _    | 0.28  | _    | ns    |           |

- 1. All Address inputs must meet the specified setup and hold times for all latching clock edges.

- 2. Control signals are  $\overline{R}$ ,  $\overline{W}$ .

- 3. Control signals are  $\overline{BW0}$ ,  $\overline{BW1}$  and  $(\overline{BW2}$ ,  $\overline{BW3}$  for x36).

- 4. Clock phase jitter is the variance from clock rising edge to the next expected clock rising edge.

- 5. V<sub>DD</sub> slew rate must be less than 0.1 V DC per 50 ns for DLL lock retention. DLL lock time begins once V<sub>DD</sub> and input clock are stable.

## Read NOP CQ-Based Timing Diagram

## **Read-Write CQ-Based Timing Diagram**

## **Write NOP TIming Diagram**

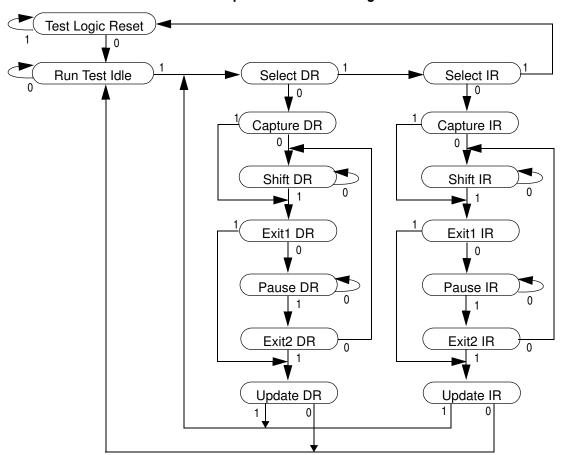

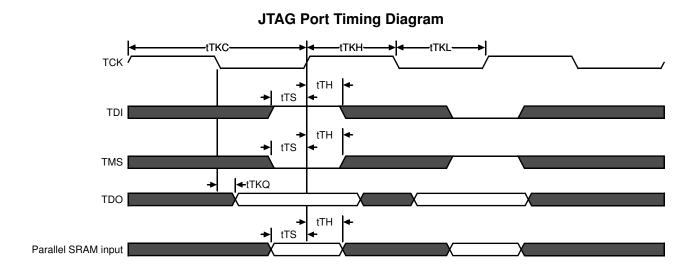

## **JTAG Port Operation**

#### Overview

The JTAG Port on this RAM operates in a manner that is compliant with IEEE Standard 1149.1-1990, a serial boundary scan interface standard (commonly referred to as JTAG). The JTAG Port input interface levels scale with  $V_{DD}$ . The JTAG output drivers are powered by  $V_{DD}$ .

### Disabling the JTAG Port

It is possible to use this device without utilizing the JTAG port. The port is reset at power-up and will remain inactive unless clocked. TCK, TDI, and TMS are designed with internal pull-up circuits. To assure normal operation of the RAM with the JTAG Port unused, TCK, TDI, and TMS may be left floating or tied to either  $V_{DD}$  or  $V_{SS}$ . TDO should be left unconnected.

## **JTAG Pin Descriptions**

| Pin | Pin Name         | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCK | Test Clock       | ln  | Clocks all TAP events. All inputs are captured on the rising edge of TCK and all outputs propagate from the falling edge of TCK.                                                                                                                                                                                                                                                                                                             |

| TMS | Test Mode Select | ln  | The TMS input is sampled on the rising edge of TCK. This is the command input for the TAP controller state machine. An undriven TMS input will produce the same result as a logic one input level.                                                                                                                                                                                                                                           |

| TDI | Test Data In     | In  | The TDI input is sampled on the rising edge of TCK. This is the input side of the serial registers placed between TDI and TDO. The register placed between TDI and TDO is determined by the state of the TAP Controller state machine and the instruction that is currently loaded in the TAP Instruction Register (refer to the TAP Controller State Diagram). An undriven TDI pin will produce the same result as a logic one input level. |

| TDO | Test Data Out    | Out | Output that is active depending on the state of the TAP state machine. Output changes in response to the falling edge of TCK. This is the output side of the serial registers placed between TDI and TDO.                                                                                                                                                                                                                                    |

#### Note:

This device does not have a TRST (TAP Reset) pin. TRST is optional in IEEE 1149.1. The Test-Logic-Reset state is entered while TMS is held high for five rising edges of TCK. The TAP Controller is also reset automaticly at power-up.

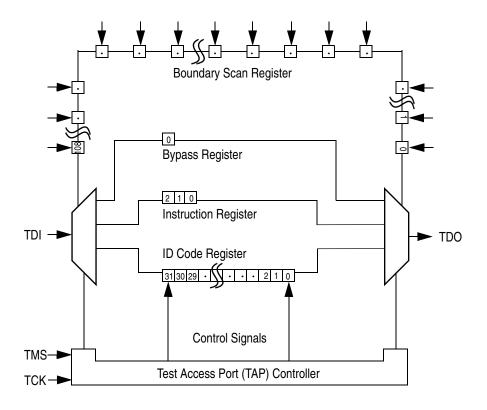

## JTAG Port Registers

### Overview

The various JTAG registers, refered to as Test Access Port or TAP Registers, are selected (one at a time) via the sequences of 1s and 0s applied to TMS as TCK is strobed. Each of the TAP Registers is a serial shift register that captures serial input data on the rising edge of TCK and pushes serial data out on the next falling edge of TCK. When a register is selected, it is placed between the TDI and TDO pins.

### Instruction Register

The Instruction Register holds the instructions that are executed by the TAP controller when it is moved into the Run, Test/Idle, or the various data register states. Instructions are 3 bits long. The Instruction Register can be loaded when it is placed between the TDI and TDO pins. The Instruction Register is automatically preloaded with the IDCODE instruction at power-up or whenever the controller is placed in Test-Logic-Reset state.

#### **Bypass Register**

The Bypass Register is a single bit register that can be placed between TDI and TDO. It allows serial test data to be passed through the RAM's JTAG Port to another device in the scan chain with as little delay as possible.

### **Boundary Scan Register**

The Boundary Scan Register is a collection of flip flops that can be preset by the logic level found on the RAM's input or I/O pins. The flip flops are then daisy chained together so the levels found can be shifted serially out of the JTAG Port's TDO pin. The Boundary Scan Register also includes a number of place holder flip flops (always set to a logic 1). The relationship between the device pins and the bits in the Boundary Scan Register is described in the Scan Order Table following. The Boundary Scan

Register, under the control of the TAP Controller, is loaded with the contents of the RAMs I/O ring when the controller is in Capture-DR state and then is placed between the TDI and TDO pins when the controller is moved to Shift-DR state. SAMPLE-Z, SAMPLE/PRELOAD and EXTEST instructions can be used to activate the Boundary Scan Register.

## **JTAG TAP Block Diagram**

### Identification (ID) Register

The ID Register is a 32-bit register that is loaded with a device and vendor specific 32-bit code when the controller is put in Capture-DR state with the IDCODE command loaded in the Instruction Register. The code is loaded from a 32-bit on-chip ROM. It describes various attributes of the RAM as indicated below. The register is then placed between the TDI and TDO pins when the controller is moved into Shift-DR state. Bit 0 in the register is the LSB and the first to reach TDO when shifting begins.

### **ID Register Contents**

|       |    |    |    |    |    |    |    |    | See | BSC | DL M | odel |    |    |    |    |    |    |    |    |    |    |   | ED | EC | hne<br>Ve<br>Cod | nd |   |   |   |   | Presence Register |

|-------|----|----|----|----|----|----|----|----|-----|-----|------|------|----|----|----|----|----|----|----|----|----|----|---|----|----|------------------|----|---|---|---|---|-------------------|

| Bit # | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23  | 22  | 21   | 20   | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7  | 6                | 5  | 4 | 3 | 2 | 1 | 0                 |

|       | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ   | Χ   | Χ    | Χ    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | 0  | 0  | 0 | 1  | 1  | 0                | 1  | 1 | 0 | 0 | 1 | 1                 |

Rev: 1.01b 6/2012 22/29 © 2011, GSI Technology

## **Tap Controller Instruction Set**

#### Overview

There are two classes of instructions defined in the Standard 1149.1-1990; the standard (Public) instructions, and device specific (Private) instructions. Some Public instructions are mandatory for 1149.1 compliance. Optional Public instructions must be implemented in prescribed ways. The TAP on this device may be used to monitor all input and I/O pads, and can be used to load address, data or control signals into the RAM or to preload the I/O buffers.

When the TAP controller is placed in Capture-IR state the two least significant bits of the instruction register are loaded with 01. When the controller is moved to the Shift-IR state the Instruction Register is placed between TDI and TDO. In this state the desired instruction is serially loaded through the TDI input (while the previous contents are shifted out at TDO). For all instructions, the TAP executes newly loaded instructions only when the controller is moved to Update-IR state. The TAP instruction set for this device is listed in the following table.

## **JTAG Tap Controller State Diagram**

## **Instruction Descriptions**

#### **BYPASS**

When the BYPASS instruction is loaded in the Instruction Register the Bypass Register is placed between TDI and TDO. This occurs when the TAP controller is moved to the Shift-DR state. This allows the board level scan path to be shortened to facilitate testing of other devices in the scan path.

### SAMPLE/PRELOAD

SAMPLE/PRELOAD is a Standard 1149.1 mandatory public instruction. When the SAMPLE / PRELOAD instruction is

loaded in the Instruction Register, moving the TAP controller into the Capture-DR state loads the data in the RAMs input and I/O buffers into the Boundary Scan Register. Boundary Scan Register locations are not associated with an input or I/O pin, and are loaded with the default state identified in the Boundary Scan Chain table at the end of this section of the datasheet. Because the RAM clock is independent from the TAP Clock (TCK) it is possible for the TAP to attempt to capture the I/O ring contents while the input buffers are in transition (i.e. in a metastable state). Although allowing the TAP to sample metastable inputs will not harm the device, repeatable results cannot be expected. RAM input signals must be stabilized for long enough to meet the TAPs input data capture set-up plus hold time (tTS plus tTH). The RAMs clock inputs need not be paused for any other TAP operation except capturing the I/O ring contents into the Boundary Scan Register. Moving the controller to Shift-DR state then places the boundary scan register between the TDI and TDO pins.

#### **EXTEST**

EXTEST is an IEEE 1149.1 mandatory public instruction. It is to be executed whenever the instruction register is loaded with all logic 0s. The EXTEST command does not block or override the RAM's input pins; therefore, the RAM's internal state is still determined by its input pins.

Typically, the Boundary Scan Register is loaded with the desired pattern of data with the SAMPLE/PRELOAD command. Then the EXTEST command is used to output the Boundary Scan Register's contents, in parallel, on the RAM's data output drivers on the falling edge of TCK when the controller is in the Update-IR state.

Alternately, the Boundary Scan Register may be loaded in parallel using the EXTEST command. When the EXTEST instruction is selected, the sate of all the RAM's input and I/O pins, as well as the default values at Scan Register locations not associated with a pin, are transferred in parallel into the Boundary Scan Register on the rising edge of TCK in the Capture-DR state, the RAM's output pins drive out the value of the Boundary Scan Register location with which each output pin is associated.

### **IDCODE**

The IDCODE instruction causes the ID ROM to be loaded into the ID register when the controller is in Capture-DR mode and places the ID register between the TDI and TDO pins in Shift-DR mode. The IDCODE instruction is the default instruction loaded in at power up and any time the controller is placed in the Test-Logic-Reset state.

#### SAMPLE-Z

If the SAMPLE-Z instruction is loaded in the instruction register, all RAM outputs are forced to an inactive drive state (high-Z) and the Boundary Scan Register is connected between TDI and TDO when the TAP controller is moved to the Shift-DR state.

## **JTAG TAP Instruction Set Summary**

| Instruction    | Code | Description                                                                                                                           | Notes |

|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------|-------|

| EXTEST         | 000  | Places the Boundary Scan Register between TDI and TDO.                                                                                | 1     |

| IDCODE         | 001  | Preloads ID Register and places it between TDI and TDO.                                                                               | 1, 2  |

| SAMPLE-Z       | 010  | Captures I/O ring contents. Places the Boundary Scan Register between TDI and TDO. Forces all RAM output drivers to High-Z except CQ. | 1     |

| GSI            | 011  | GSI private instruction.                                                                                                              | 1     |

| SAMPLE/PRELOAD | 100  | Captures I/O ring contents. Places the Boundary Scan Register between TDI and TDO.                                                    | 1     |

| GSI            | 101  | GSI private instruction.                                                                                                              | 1     |

| GSI            | 110  | GSI private instruction.                                                                                                              | 1     |

| BYPASS         | 111  | Places Bypass Register between TDI and TDO.                                                                                           | 1     |

### Notes:

- 1. Instruction codes expressed in binary, MSB on left, LSB on right.

- 2. Default instruction automatically loaded at power-up and in test-logic-reset state.

## JTAG Port Recommended Operating Conditions and DC Characteristics

| Parameter                              | Symbol            | Min.                  | Max.                  | Unit | Notes |

|----------------------------------------|-------------------|-----------------------|-----------------------|------|-------|

| Test Port Input Low Voltage            | V <sub>ILJ</sub>  | -0.3                  | 0.3 * V <sub>DD</sub> | V    | 1     |

| Test Port Input High Voltage           | V <sub>IHJ</sub>  | 0.7 * V <sub>DD</sub> | V <sub>DD</sub> +0.3  | V    | 1     |

| TMS, TCK and TDI Input Leakage Current | I <sub>INHJ</sub> | -300                  | 1                     | uA   | 2     |

| TMS, TCK and TDI Input Leakage Current | I <sub>INLJ</sub> | -1                    | 100                   | uA   | 3     |

| TDO Output Leakage Current             | I <sub>OLJ</sub>  | -1                    | 1                     | uA   | 4     |

| Test Port Output High Voltage          | V <sub>OHJ</sub>  | V <sub>DD</sub> – 0.2 | _                     | V    | 5, 6  |

| Test Port Output Low Voltage           | V <sub>OLJ</sub>  | _                     | 0.2                   | V    | 5, 7  |

| Test Port Output CMOS High             | V <sub>OHJC</sub> | V <sub>DD</sub> – 0.1 | _                     | ٧    | 5, 8  |

| Test Port Output CMOS Low              | V <sub>OLJC</sub> | _                     | 0.1                   | ٧    | 5, 9  |

#### Notes

- 1. Input Under/overshoot voltage must be  $-1 \text{ V} < \text{Vi} < \text{V}_{DDn} + 1 \text{ V}$  not to exceed 2.4 V maximum, with a pulse width not to exceed 20% tTKC.

- $2. \quad V_{ILJ} \leq V_{IN} \leq V_{DDn}$

- 3. 0  $V \le V_{IN} \le V_{ILJn}$

- 4. Output Disable,  $V_{OUT} = 0$  to  $V_{DDn}$

- 5. The TDO output driver is served by the V<sub>DD</sub> supply.

- 6.  $I_{OHJ} = -2 \text{ mA}$

- 7.  $I_{OLJ} = +2 \text{ mA}$

- 8.  $I_{OHJC} = -100 \text{ uA}$

- 9.  $I_{OLJC} = +100 \text{ uA}$

Rev: 1.01b 6/2012 25/29 © 2011, GSI Technology

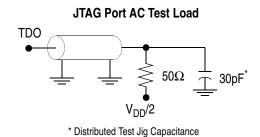

## **JTAG Port AC Test Conditions**

| Parameter              | Conditions              |

|------------------------|-------------------------|

| Input high level       | V <sub>DD</sub> – 0.2 V |

| Input low level        | 0.2 V                   |

| Input slew rate        | 1 V/ns                  |

| Input reference level  | V <sub>DD</sub> /2      |

| Output reference level | V <sub>DD</sub> /2      |

## Notes:

- I. Include scope and jig capacitance.

- 2. Test conditions as shown unless otherwise noted.

## **JTAG Port AC Electrical Characteristics**

| Parameter             | Symbol | Min | Max | Unit |

|-----------------------|--------|-----|-----|------|

| TCK Cycle Time        | tTKC   | 50  | 1   | ns   |

| TCK Low to TDO Valid  | tTKQ   | _   | 20  | ns   |

| TCK High Pulse Width  | tTKH   | 20  | _   | ns   |

| TCK Low Pulse Width   | tTKL   | 20  | _   | ns   |

| TDI & TMS Set Up Time | tTS    | 10  | _   | ns   |

| TDI & TMS Hold Time   | tTH    | 10  | _   | ns   |

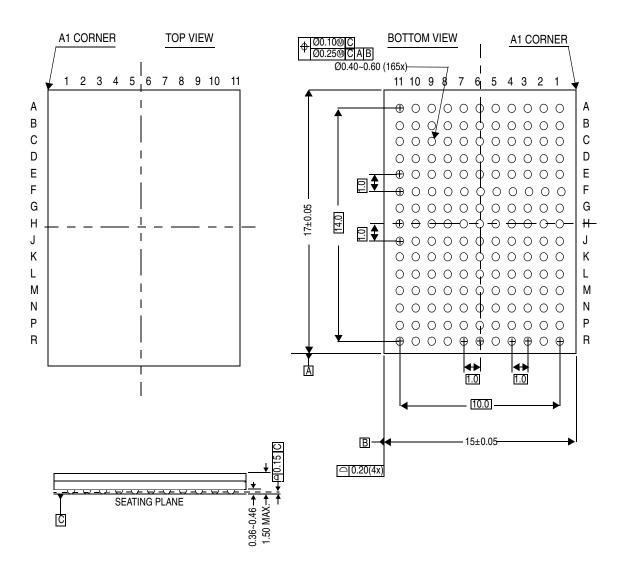

## Package Dimensions—165-Bump FPBGA (Package E)

## Ordering Information—GSI SigmaQuad-II+ ECCRAM

| Org     | Part Number <sup>1</sup> | Туре                 | Package                     | Speed<br>(MHz) | T <sub>J</sub> <sup>2</sup> |

|---------|--------------------------|----------------------|-----------------------------|----------------|-----------------------------|

| 4M x 18 | GS8672D19BE-400          | SigmaQuad-II+ ECCRAM | 165-bump BGA                | 400            | С                           |

| 4M x 18 | GS8672D19BE-375          | SigmaQuad-II+ ECCRAM | 165-bump BGA                | 375            | С                           |

| 4M x 18 | GS8672D19BE-333          | SigmaQuad-II+ ECCRAM | 165-bump BGA                | 333            | С                           |

| 4M x 18 | GS8672D19BE-300          | SigmaQuad-II+ ECCRAM | 165-bump BGA                | 300            | С                           |

| 4M x 18 | GS8672D19BE-400I         | SigmaQuad-II+ ECCRAM | 165-bump BGA                | 400            | I                           |

| 4M x 18 | GS8672D19BE-375I         | SigmaQuad-II+ ECCRAM | 165-bump BGA                | 375            | I                           |

| 4M x 18 | GS8672D19BE-333I         | SigmaQuad-II+ ECCRAM | 165-bump BGA                | 333            | I                           |

| 4M x 18 | GS8672D19BE-300I         | SigmaQuad-II+ ECCRAM | 165-bump BGA                | 300            | I                           |

| 2M x 36 | GS8672D37BE-400          | SigmaQuad-II+ ECCRAM | 165-bump BGA                | 400            | С                           |

| 2M x 36 | GS8672D37BE-375          | SigmaQuad-II+ ECCRAM | 165-bump BGA                | 375            | С                           |

| 2M x 36 | GS8672D37BE-333          | SigmaQuad-II+ ECCRAM | 165-bump BGA                | 333            | С                           |

| 2M x 36 | GS8672D37BE-300          | SigmaQuad-II+ ECCRAM | 165-bump BGA                | 300            | С                           |

| 2M x 36 | GS8672D37BE-400I         | SigmaQuad-II+ ECCRAM | 165-bump BGA                | 400            | I                           |

| 2M x 36 | GS8672D37BE-375I         | SigmaQuad-II+ ECCRAM | 165-bump BGA                | 375            | I                           |

| 2M x 36 | GS8672D37BE-333I         | SigmaQuad-II+ ECCRAM | 165-bump BGA                | 333            | I                           |

| 2M x 36 | GS8672D37BE-300I         | SigmaQuad-II+ ECCRAM | 165-bump BGA                | 300            | I                           |

| 4M x 18 | GS8672D19BGE-400         | SigmaQuad-II+ ECCRAM | RoHS-compliant 165-bump BGA | 400            | С                           |

| 4M x 18 | GS8672D19BGE-375         | SigmaQuad-II+ ECCRAM | RoHS-compliant 165-bump BGA | 375            | С                           |

| 4M x 18 | GS8672D19BGE-333         | SigmaQuad-II+ ECCRAM | RoHS-compliant 165-bump BGA | 333            | С                           |

| 4M x 18 | GS8672D19BGE-300         | SigmaQuad-II+ ECCRAM | RoHS-compliant 165-bump BGA | 300            | С                           |

| 4M x 18 | GS8672D19BGE-400I        | SigmaQuad-II+ ECCRAM | RoHS-compliant 165-bump BGA | 400            | I                           |

| 4M x 18 | GS8672D19BGE-375I        | SigmaQuad-II+ ECCRAM | RoHS-compliant 165-bump BGA | 375            | I                           |

| 4M x 18 | GS8672D19BGE-333I        | SigmaQuad-II+ ECCRAM | RoHS-compliant 165-bump BGA | 333            | I                           |

| 4M x 18 | GS8672D19BGE-300I        | SigmaQuad-II+ ECCRAM | RoHS-compliant 165-bump BGA | 300            | I                           |

| 2M x 36 | GS8672D37BGE-400         | SigmaQuad-II+ ECCRAM | RoHS-compliant 165-bump BGA | 400            | С                           |

| 2M x 36 | GS8672D37BGE-375         | SigmaQuad-II+ ECCRAM | RoHS-compliant 165-bump BGA | 375            | С                           |

| 2M x 36 | GS8672D37BGE-333         | SigmaQuad-II+ ECCRAM | RoHS-compliant 165-bump BGA | 333            | С                           |

| 2M x 36 | GS8672D37BGE-300         | SigmaQuad-II+ ECCRAM | RoHS-compliant 165-bump BGA | 300            | С                           |

| 2M x 36 | GS8672D37BGE-400I        | SigmaQuad-II+ ECCRAM | RoHS-compliant 165-bump BGA | 400            | I                           |

| 2M x 36 | GS8672D37BGE-375I        | SigmaQuad-II+ ECCRAM | RoHS-compliant 165-bump BGA | 375            | I                           |

| 2M x 36 | GS8672D37BGE-333I        | SigmaQuad-II+ ECCRAM | RoHS-compliant 165-bump BGA | 333            | I                           |

| 2M x 36 | GS8672D37BGE-300I        | SigmaQuad-II+ ECCRAM | RoHS-compliant 165-bump BGA | 300            | I                           |

- 1. For Tape and Reel add the character "T" to the end of the part number. Example: GS8672D37BE-300T.

- 2. C = Commercial Temperature Range. I = Industrial Temperature Range.

## SigmaQuad-II+ ECCRAM Revision History

| File Name         | Format/Content | Description of changes                                                                                        |

|-------------------|----------------|---------------------------------------------------------------------------------------------------------------|