Data Sheet March 9, 2006 FN9265.0

### **CCFL Brightness Controller**

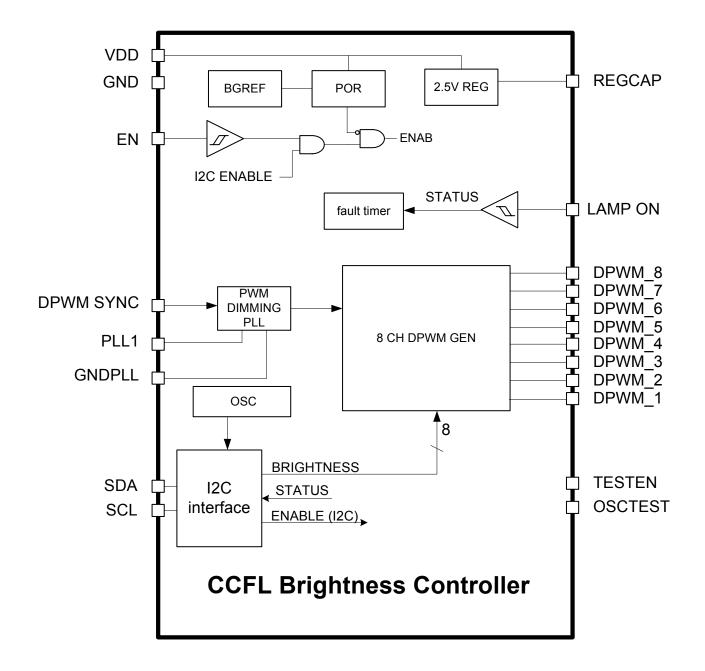

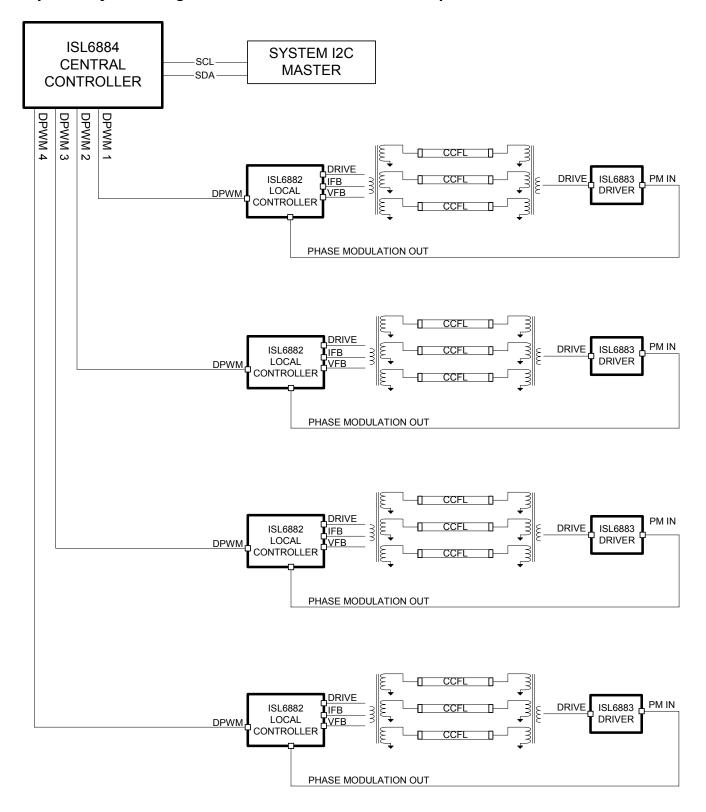

ISL6884 controls Pulse Width Modulated Dimming for up to 8 inverters to supply power to up to 40 Cold Cathode Fluorescent Lamps (CCFL) for back lighting in large LCD displays.

The ISL6884 brightness controller provides an I<sup>2</sup>C interface for dimming control, enable, status, and brightness balance. The duty cycle of all 8 DPWM outputs is adjusted with a Master Brightness Control register. The duty cycle of each of the 8 DPWM outputs can be offset from the master brightness to adjust for uniform brightness.

The PWM dimming frequency can be set by an internal, adjustable oscillator or synchronized to an external source to minimize interference with video.

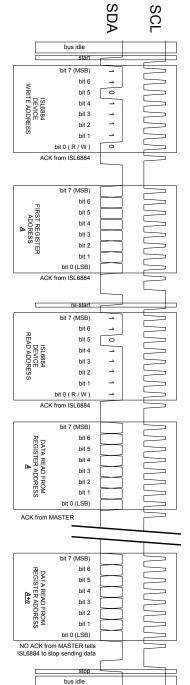

ISL6884's slave address is:

- 1101\_1111 for reading

- 1101\_1110 for writing

### **Ordering Information**

| PART<br>NUMBER             | TEMP. RANGE<br>(°C) | PACKAGE                                  | PKG.<br>DWG.# |

|----------------------------|---------------------|------------------------------------------|---------------|

| ISL6884IAZ<br>(See Note)   | -40 to 85           | 20 Ld SSOP<br>(Pb-free)                  | M20.15        |

| ISL6884IAZ-T<br>(See Note) | -40 to 85           | 20 Ld SSOP Tape<br>and Reel<br>(Pb-free) | M20.15        |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

### Features

- · Wide Supply Voltage Range of 3.0V to 5.5V

- Dimming

- I<sup>2</sup>C dimming control input

- PWM dimming can be synchronized to an external source or set by an internal, adjustable oscillator.

- 8 channel dimming allows the user to balance the brightness of the CCFL lamps via I<sup>2</sup>C control

- User programmable fault time out

- · User Programmable Fault Time Out

- I<sup>2</sup>C Status Output

- · Pb-Free Plus Anneal Available (RoHS Compliant)

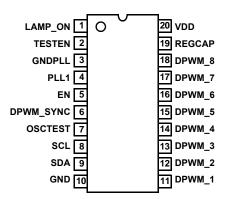

### **Pinout**

ISL6884 (20 LD SSOP) TOP VIEW

### **Block Diagram**

### Simplified System Diagram - Central Controller and Multiple Local Controllers

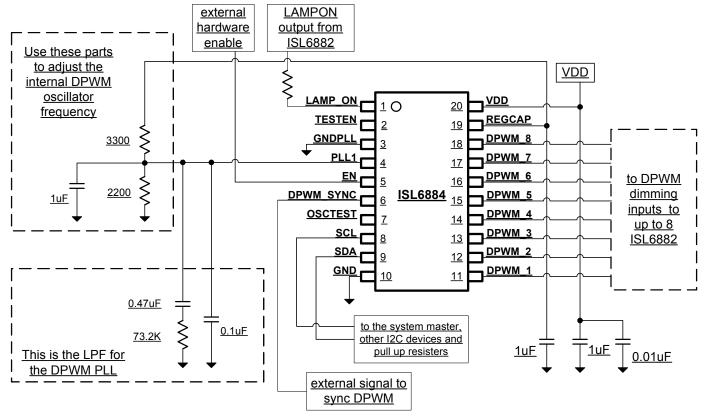

### ISL6884 Application Schematic

### **Absolute Maximum Ratings**

| Supply Voltage (VDD) | 0.3V to 6.0V        |

|----------------------|---------------------|

| Input/Output Voltage | -0.3V to VDD + 0.3V |

### **Recommended Operating Conditions**

| Ambient Temperature Range              | 40°C to 85°C |

|----------------------------------------|--------------|

| Maximum Operating Junction Temperature | 125°C        |

| Supply Voltage, VDD                    | 5V ±10%      |

### **Thermal Information**

| Thermal Resistance (Typical, Notes 1) | θ <sub>JA</sub> (°C/W) |

|---------------------------------------|------------------------|

| 20 Ld SSOP                            | 110                    |

### **Thermal Information**

| Maximum Junction Temperature             | 150°C         |

|------------------------------------------|---------------|

| Maximum Storage Temperature Range6       | 35°C to 150°C |

| Maximum Lead Temperature (Soldering 10s) | 300°C         |

| (SSOP - Lead Tips Only)                  |               |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

### NOTES:

1.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

### **Electrical Specifications** Recommended Operating Conditions, Unless Otherwise Noted

| PARAMETER                        | SYMBOL                 | TEST CONDITIONS                          | MIN     | TYP      | MAX     | UNITS |

|----------------------------------|------------------------|------------------------------------------|---------|----------|---------|-------|

| POWER ON RESET                   |                        |                                          | '       |          |         | l     |

| VDD Rising                       | POR <sub>rising</sub>  |                                          | 2.4     | 2.7      | 3.0     | V     |

| VDD Falling                      | POR <sub>falling</sub> |                                          | 2.2     | 2.5      | 2.7     | V     |

| POR Hysteresis                   | POR <sub>hyst</sub>    |                                          | -       | 200      | -       | mV    |

| VOLTAGE REGULATOR                | .l                     |                                          | 1       |          |         | 1     |

| Regulated Voltage                | V <sub>reg</sub>       | External Capacitor = 1μF, ESR<1Ω         | 2.3     | 2.5      | 2.7     | V     |

| LOGIC LEVEL INPUTS (EN, DPWM     | _SYNC, LAMPON          | l)                                       | 1       |          |         | 1     |

| V In High                        | VIH <sub>LOGIC</sub>   |                                          | 2.6     | -        | -       | V     |

| V In Low                         | VIL <sub>LOGIC</sub>   |                                          | -       | -        | 0.8     | V     |

| Hysteresis                       | Vhyst                  |                                          | -       | 140      | -       | mV    |

| Input Current                    | I_IN                   | V <sub>in</sub> = VDD                    | -       | 10       | -       | nA    |

|                                  |                        | V <sub>in</sub> = 0V                     | -       | -10      | -       | nA    |

| I <sup>2</sup> C                 | .l                     |                                          | 1       |          |         | 1     |

| V In Low                         | V <sub>IL</sub>        |                                          | -       | -        | 0.3*VDD | V     |

| V In High                        | V <sub>IH</sub>        |                                          | 0.7*VDD | -        | -       | V     |

| Schmitt Trigger Input Hysteresis | V <sub>hys</sub>       |                                          | -       | 0.05*VDD | -       | V     |

| V Out Low                        | V <sub>OL</sub>        | I in low = 3mA                           | -       | -        | 0.4     | V     |

| SDA, SCL Rise Time               | T <sub>rise_I2C</sub>  | Cload = 200pF<br>Rpullup = 1700, 30%-70% | -       | 300      | -       | ns    |

| SDA, SCL Fall Time               | T <sub>fall_l2C</sub>  | Cload = 200pF<br>Rpullup = 1700, 30%-70% | -       | -        | 300     | ns    |

intersil FN9265.0 March 9, 2006

Electrical Specifications Recommended Operating Conditions, Unless Otherwise Noted (Continued)

| PARAMETER                   | SYMBOL                 | TEST CONDITIONS        | MIN     | TYP | MAX     | UNITS |

|-----------------------------|------------------------|------------------------|---------|-----|---------|-------|

| DPWM                        |                        |                        |         |     |         |       |

| DPWM PLL Free Run Frequency | f <sub>freerun</sub>   |                        | -       | 160 | -       | Hz    |

| DPWM PLL Lock Frequency     | f <sub>lock</sub>      |                        | 120     | 160 | 200     | Hz    |

| Lock Time                   | T <sub>lock</sub>      |                        | -       | 150 | -       | ms    |

| DPWM Duty Cycle             | DPWM <sub>DCmin</sub>  | BRT_M = 00hex (Note 3) | 3       | 4   | 5       | %     |

| DPWM Duty Cycle             | DPWM <sub>DCmid</sub>  | BRT_M = 7Fhex (Note 3) | 49      | 50  | 51      | %     |

| DPWM Duty Cycle             | DPWM <sub>DCmax</sub>  | BRT_M = FFhex (Note 3) | 98      | -   | 100     | %     |

| DPWM Output High            | V <sub>OH</sub>        | I <sub>OH</sub> = 2mA  | 0.7*VDD | -   | -       | V     |

| DPWM Output Low             | V <sub>OL</sub>        | I <sub>OL</sub> = 2mA  | -       | -   | 0.3*VDD | V     |

| DPWM Rise Time              | T <sub>rise_DPWM</sub> | Cload = 200pF          | -       | -   | 500     | ns    |

| DPWM Fall Time              | T <sub>fall_DPWM</sub> | Cload = 200pF          | -       | -   | 500     | ns    |

NOTE:

2. Master enable (0X2B) = 01, channel enable (0X2C) = FF, all other registers in default mode

### Pin Description

**VDD -** Power input for digital systems. All functions are disabled unless this pin exceeds 3V (see Power On Reset specs). A 0.01µF decoupling cap should be placed between VDD and GND with the shortest possible traces.

GND - Ground for digital systems.

**REGCAP** - An external  $1\mu F$  capacitor to decouple the internal 2.5V regulator.

**EN** - Logic level input signal. Voltage at this pin above a threshold ENables circuit operation.

**DPWM SYNC** - A logic level input signal. The dimming PWM frequency oscillator will synchronize to this signal (if present). If no signal is present at this pin, the internal DPWM oscillator will free run at approximately 160Hz.

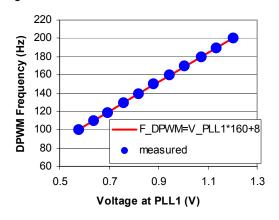

**PLL1** - Analog input. An RC network on these pins sets the loop response of the DPWM Phase Locked Loop. A voltage source or resister divider at this pin will set the DPWM frequency. See the graph below for approximate frequency vs voltage at PLL1.

6

**GNDPLL** - A separate ground terminal for the PLL. Filter and bias components on PLL1 should be connected to this ground with the shortest possible traces. This pin is also connected to the system ground with a trace that is not critical.

**DPWM 1:8** - Logic level outputs that control the analog and PWM dimming of each of 8 ISL6882s. The duty cycle of the DPWM signals range from 4% (minimum brightness) to 100% (maximum brightness). A low pass filter in the inverter Controller converts the DPWM duty cycle to a DC voltage that performs 3:1 analog dimming. The combined dimming range is 100:1. The dimming value is set by I<sup>2</sup>C registers.

**LAMP\_ON** - A logic level input signal. A high level on the pin indicates that all lamps are ON and operating normally. A low level at this pin indicates that at least one of the lamps is either not ignited or out of the circuit. When this pin is low, the fault timer runs. When this pin is high, the fault timer is reset. Because this is a high impedance line that may be routed near sources of EMI, it is recommended that a 10K resister is placed in series between the LAMP\_ON pin and all other circuits.

**SDA**, **SCL** - Logic level input/output signals. SDA is the  $I^2C$  data line and SCL is the  $I^2C$  clock line. The ISL6884 receives data via  $I^2C$  to enable or disable the inverters, set dimming for each channel, and set the number of channels. System status can be read via  $I^2C$ .

**TESTEN and OSCTEST -** These pins are used for internal tests. They should be left unconnected in normal operation.

### I<sup>2</sup>C Register Description

Register addresses and default values are given in the following Register Description Table.

I<sup>2</sup>C Slave Address - ISL6884's slave address is:

- · 1101 1111 for reading

- 1101 1110 for writing

**BRT\_M** - Master Brightness Control input. This register controls the duty cycle of al 8 DPWM outputs.

**BRT\_OS[1..8]** - Brightness offset. These registers allow the system designer to increase or decrease the duty cycle of individual channel to equalize the brightness of all lamps in a system. Note: Value is stored as 2's complement number.

**MSTR\_EN** - Master Enable, This signal is AND'ed with the EN pin to create the enable for the PWM dimming output. If this bit OR the EN pin is low the DPWM outputs are held low.

**CH\_EN** - Individual Channel Enables for each DPWM output. If only DPWM 1, 3, 5 and 7 are to be used, CH\_EN bits 1, 3, 5, and 7 should be set to 1 and bits 2, 4, 6, and 8 should be set to 0.

**FLT\_TOUT** - Fault Timer Time Out Setting. This register controls the response of the ISL6884 to a logic low input on the LAMPON pin (indicating that one or more lamps is NOT ON). A value between 0X01 and 0XFF in the FLT\_TOUT register will set the time that ISL6884 will operate with a low signal at the LAMPON pin (fault time out). The adjustment range is from less than 0.1 second to approximately 2 seconds. The power on reset default time out is 1 second. After a fault time out, all DPWM outputs are latched low until power is cycled. If FLT\_TOUT is set to 0X00, ISL6884 will not time out and will continue to operate even with a low signal at the LAMPON pin.

**STATUS -** indicates the status of the Time out Fault, LAMPON input signal and ENABLE (MSTR\_EN AND EN pin).

intersil FN9265.0 March 9, 2006

### Register Description Table

### Register Descriptions:

### NOTES:

- 1. sb denotes sign bit for 2's compliment numbers.

- 2. The second row shows the register's default value loaded at Power On Reset.

TABLE 1. REGISTER DESCRIPTION TABLE (READ/WRITE REGISTERS)

| WORD NAME       | DESCRIPTION                  |                    |                   |                    |                   |             |             |           |  |  |

|-----------------|------------------------------|--------------------|-------------------|--------------------|-------------------|-------------|-------------|-----------|--|--|

| BYTE<br>ADDRESS | MSB LABEL                    | BIT 6 LABEL        | BIT 5 LABEL       | BIT 4 LABEL        | BIT 3 LABEL       | BIT 2 LABEL | BIT 1 LABEL | LSB LABEL |  |  |

| POR             | POR VALUE                    | POR VALUE          | POR VALUE         | POR VALUE          | POR VALUE         | POR VALUE   | POR VALUE   | POR VALUE |  |  |

| BRT_M           | Brightness Magnitude Setting |                    |                   |                    |                   |             |             |           |  |  |

| 0x00            | b7                           | b6                 | b5                | b4                 | b3                | b2          | b1          | b0        |  |  |

| POR             | 0                            | 0                  | 1                 | 1                  | 1                 | 1           | 1           | 1         |  |  |

| brt_os1         | Brightness Offs              | set for Light Sens | sor 1. Note: Valu | e is stored as 2's | s complement nu   | ımber       |             |           |  |  |

| 0x01            |                              |                    | sb                | b4                 | b3                | b2          | b1          | b0        |  |  |

| POR             | 0                            | 0                  | 0                 | 0                  | 0                 | 0           | 0           | 0         |  |  |

| brt_os2         | Brightness Offs              | et for Light Sens  | sor 2. Note: Valu | e is stored as 2's | s complement nu   | ımber.      |             |           |  |  |

| 0x02            |                              |                    | sb                | b4                 | b3                | b2          | b1          | b0        |  |  |

| POR             | 0                            | 0                  | 0                 | 0                  | 0                 | 0           | 0           | 0         |  |  |

| brt_os3         | Brightness Offs              | et for Light Sens  | sor 3. Note: Valu | e is stored as 2's | s complement nu   | ımber       |             |           |  |  |

| 0x03            |                              |                    | sb                | b4                 | b3                | b2          | b1          | b0        |  |  |

| POR             | 0                            | 0                  | 0                 | 0                  | 0                 | 0           | 0           | 0         |  |  |

| brt_os4         | Brightness Offs              | et for Light Sens  | sor 4. Note: Valu | e is stored as 2's | s complement nu   | ımber.      |             |           |  |  |

| 0x04            |                              |                    | sb                | b4                 | b3                | b2          | b1          | b0        |  |  |

| POR             | 0                            | 0                  | 0                 | 0                  | 0                 | 0           | 0           | 0         |  |  |

| brt_os5         | Brightness Offs              | et for Light Sens  | sor 5. Note: Valu | e is stored as 2's | s complement nu   | ımber       |             |           |  |  |

| 0x05            |                              |                    | sb                | b4                 | b3                | b2          | b1          | b0        |  |  |

| POR             | 0                            | 0                  | 0                 | 0                  | 0                 | 0           | 0           | 0         |  |  |

| brt_os6         | Brightness Offs              | set for Light Sens | sor 6. Note: Valu | e is stored as 2's | s complement nu   | ımber.      |             |           |  |  |

| 0x06            |                              |                    | sb                | b4                 | b3                | b2          | b1          | b0        |  |  |

| POR             | 0                            | 0                  | 0                 | 0                  | 0                 | 0           | 0           | 0         |  |  |

| brt_os7         | Brightness Offs              | set for Light Sens | sor 7. Note: Valu | e is stored as 2's | s complement nu   | ımber.      |             |           |  |  |

| 0x07            |                              |                    | sb                | b4                 | b3                | b2          | b1          | b0        |  |  |

| POR             | 0                            | 0                  | 0                 | 0                  | 0                 | 0           | 0           | 0         |  |  |

| brt_os8         | Brightness Offs              | set for Light Sens | sor 8. Note: Valu | e is stored as 2's | s complement nu   | ımber.      |             |           |  |  |

| 0x08            |                              |                    | sb                | b4                 | b3                | b2          | b1          | b0        |  |  |

| POR             | 0                            | 0                  | 0                 | 0                  | 0                 | 0           | 0           | 0         |  |  |

| mstr en         | Master Enable,               | This signal is A   | ND'ed with the e  | n pin to create th | ne enable for the | PWM dimming | output.     |           |  |  |

| 0x2a            |                              |                    |                   |                    |                   |             |             | mstr_en   |  |  |

| POR             | 0                            | 0                  | 0                 | 0                  | 0                 | 0           | 0           | 0         |  |  |

| ch_en           |                              |                    | each DPWM out     |                    |                   |             |             |           |  |  |

| 0x2b            | b7                           | b6                 | b5                | b4                 | b3                | b2          | b1          | b0        |  |  |

| POR             | 0                            | 0                  | 0                 | 0                  | 0                 | 0           | 0           | 0         |  |  |

| flt_tout        | Fault Timer Tim              |                    |                   |                    |                   |             |             | _         |  |  |

intersil FN9265.0 March 9, 2006

TABLE 1. REGISTER DESCRIPTION TABLE (READ/WRITE REGISTERS) (Continued)

| WORD NAME                      |                                                                                                                               |                                                 | <del> </del> | DESCR       | RIPTION         | 1               | t           | t           |  |  |  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------|-------------|-----------------|-----------------|-------------|-------------|--|--|--|

| BYTE<br>ADDRESS                | MSB LABEL                                                                                                                     | BIT 6 LABEL                                     | BIT 5 LABEL  | BIT 4 LABEL | BIT 3 LABEL     | BIT 2 LABEL     | BIT 1 LABEL | LSB LABEL   |  |  |  |

| POR                            | POR VALUE                                                                                                                     | POR VALUE                                       | POR VALUE    | POR VALUE   | POR VALUE       | POR VALUE       | POR VALUE   | POR VALUE   |  |  |  |

| 0x2c                           | b7                                                                                                                            | b6                                              | b5           | b4          | b3              | b2              | b1          | b0          |  |  |  |

| POR                            | 1                                                                                                                             | 0                                               | 0            | 0           | 0               | 0               | 0           | 0           |  |  |  |

| CM                             | Maximum Fails Setting. This value determines how many consecutive I <sup>2</sup> C fails can occur before channel is faulted. |                                                 |              |             |                 |                 |             |             |  |  |  |

| 0x2d                           |                                                                                                                               |                                                 |              |             |                 |                 | b1          | b0          |  |  |  |

| POR                            | 0                                                                                                                             | 0                                               | 0            | 0           | 0               | 0               | 0           | 1           |  |  |  |

| i <sup>2</sup> c_suh<br>_pres  |                                                                                                                               | Preset Value. S<br>nging this regist            |              |             |                 | ictable behavio | r           |             |  |  |  |

| 0x2E                           |                                                                                                                               |                                                 | b5           | b4          | b3              | b2              | b1          | b0          |  |  |  |

| POR                            | 0                                                                                                                             | 0                                               | 0            | 0           | 0               | 1               | 1           | 0           |  |  |  |

| i <sup>2</sup> c_scl<br>_hpres |                                                                                                                               | Time Preset Valunging this regist               |              |             |                 | ictable behavio | r           |             |  |  |  |

| 0x2f                           |                                                                                                                               |                                                 | b5           | b4          | b3              | b2              | b1          | b0          |  |  |  |

| POR                            | 0                                                                                                                             | 0                                               | 0            | 0           | 0               | 1               | 0           | 0           |  |  |  |

| i <sup>2</sup> c_scl_<br>Ipres |                                                                                                                               | ime Preset Value                                |              |             |                 | ictable behavio | r           |             |  |  |  |

| 0x30                           |                                                                                                                               |                                                 | b5           | b4          | b3              | b2              | b1          | b0          |  |  |  |

| POR                            | 0                                                                                                                             | 0                                               | 0            | 1           | 0               | 0               | 1           | 0           |  |  |  |

| i <sup>2</sup> c_bfree         |                                                                                                                               | ime Value. See                                  |              |             | esult in unpred | ictable behavio | r           |             |  |  |  |

| 0x31                           |                                                                                                                               |                                                 | b5           | b4          | b3              | b2              | b1          | b0          |  |  |  |

| POR                            | 0                                                                                                                             | 0                                               | 0            | 0           | 1               | 0               | 1           | 1           |  |  |  |

| i <sup>2</sup> c<br>_stretch   |                                                                                                                               | ue See I <sup>2</sup> C Do<br>nging this regist |              |             | esult in unpred | ictable behavio | r           |             |  |  |  |

| 0x32                           |                                                                                                                               |                                                 |              |             |                 |                 |             | i2c_stretch |  |  |  |

| POR                            | 0                                                                                                                             | 0                                               | 0            | 0           | 0               | 0               | 0           | 0           |  |  |  |

| toc_spd<br>_ctrl               |                                                                                                                               | nter Speed Contro<br>nging this regist          |              |             |                 | ictable behavio | r           |             |  |  |  |

| 0x33                           |                                                                                                                               |                                                 |              |             |                 | b18             | b17         | b16         |  |  |  |

| POR                            | 0                                                                                                                             | 0                                               | 0            | 0           | 0               | 0               | 0           | 0           |  |  |  |

| toc_spd<br>_ctrl               |                                                                                                                               | nter Speed Contro<br>Inging this regist         |              |             |                 | ictable behavio | r           |             |  |  |  |

| 0x34                           | b15                                                                                                                           | b14                                             | b13          | b12         | b11             | b10             | b9          | b8          |  |  |  |

| POR                            | 1                                                                                                                             | 1                                               | 1            | 0           | 0               | 1               | 1           | 1           |  |  |  |

| toc_spd<br>_ctrl               |                                                                                                                               | nter Speed Contro<br>nging this regist          |              |             |                 | ictable behavio | r           |             |  |  |  |

| 0x35                           | b7                                                                                                                            | b6                                              | b5           | b4          | b3              | b2              | b1          | b0          |  |  |  |

| POR                            | 0                                                                                                                             | 0                                               | 1            | 1           | 1               | 0               | 0           | 0           |  |  |  |

| dc_max                         |                                                                                                                               | ximum Setting. S                                |              |             |                 | ictable behavio | r           |             |  |  |  |

| 0x36                           | b7                                                                                                                            | b6                                              | b5           | b4          | b3              | b2              | b1          | b0          |  |  |  |

| POR                            | 1                                                                                                                             | 1                                               | 1            | 1           | 1               | 1               | 1           | 1           |  |  |  |

| dc_min                         |                                                                                                                               | nimum Setting. Songing this regist              |              |             |                 | ictable behavio | r           |             |  |  |  |

TABLE 1. REGISTER DESCRIPTION TABLE (READ/WRITE REGISTERS) (Continued)

| WORD NAME                                            |                                                   |                                      |                                   | DESCR       | IPTION      |                 |                   |                   |  |

|------------------------------------------------------|---------------------------------------------------|--------------------------------------|-----------------------------------|-------------|-------------|-----------------|-------------------|-------------------|--|

| BYTE<br>ADDRESS                                      | MSB LABEL                                         | BIT 6 LABEL                          | BIT 5 LABEL                       | BIT 4 LABEL | BIT 3 LABEL | BIT 2 LABEL     | BIT 1 LABEL       | LSB LABEL         |  |

| POR                                                  | POR VALUE                                         | POR VALUE                            | POR VALUE                         | POR VALUE   | POR VALUE   | POR VALUE       | POR VALUE         | POR VALUE         |  |

| 0x37                                                 | b7                                                | b6                                   | b5                                | b4          | b3          | b2              | b1                | b0                |  |

| POR                                                  | 0                                                 | 0                                    | 0                                 | 0           | 1           | 0               | 0                 | 1                 |  |

| pwm_<br>sync_sel                                     | = '                                               |                                      |                                   |             |             |                 |                   |                   |  |

| 0x38                                                 |                                                   |                                      |                                   |             |             |                 | pwm_sync<br>_sel2 | pwm_sync<br>_sel1 |  |

| POR                                                  | 0                                                 | 0                                    | 0                                 | 0           | 0           | 0               | 0                 | 1                 |  |

| pll_bypass<br>pmp1<br>pmp0                           | Charge Pump E<br>Charge Pump E                    | Bit1. See Plan 9<br>Bit0. See Plan 9 | CDR Document<br>CDR Document      | •           |             | ictable behavio | r                 |                   |  |

| 0x39                                                 |                                                   |                                      |                                   |             |             | pll_bypass      | pmp1              | pmp0              |  |

| POR                                                  | 0                                                 | 0                                    | 0                                 | 0           | 0           | 0               | 0                 | 0                 |  |

| dpwm8 in funct<br>mx_sel = 1: dpv<br>mx_sel = 2: dpv | ional mode.<br>wm6 = vco_out,<br>wm6 in functiona | dpwm7 = div512<br>ıl mode, dpwm7     | _out, dpwm8 = c<br>= clk_d4, dpwm | div64_clk.  | ŭ           | 0.              | mx_sel = 0: dpwi  | n6, dpwm7,        |  |

| 0x3A |   |   |   |   | mx_sel<br>b3 | b2 | b1 | b0 |

|------|---|---|---|---|--------------|----|----|----|

| POR  | 0 | 0 | 0 | 0 | 0            | 0  | 0  | 0  |

### I<sup>2</sup>C Bus General Description

### Introduction

(Refer to Philips I<sup>2</sup>C Specification, Rev. 2.1)

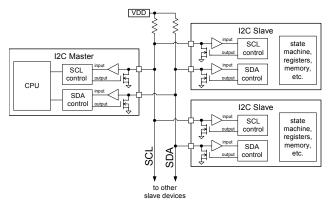

The  $I^2C$  bus is a 2 wire communication bus for integrated circuits.  $I^2C$ ,  $I^2C$  or IIC are commonly used instead of the formal name  $\underline{I}$ nter- $\underline{I}$ ntegrated- $\underline{C}$ ircuit bus. The 2 wires are the SCL ( $\underline{S}$ erial  $\underline{CL}$ ock) and SDA ( $\underline{S}$ erial  $\underline{DA}$ ta). All ICs on the bus are connected to the SCL and SDA lines. SCL and SDA pins on each device are bidirectional and can act as either inputs or open drain outputs. Which device is transmitting and receiving is determined by the bus protocol which will be described below.

A typical I<sup>2</sup>C bus system is made of a 'master' that initiates communication (usually a microprocessor) and one or more 'slaves' that respond to commands from the master. Each slave has a device address. In a typical communication sequence, the master will initiate communication with a 'start condition' followed by the address of one of the slave devices. The slave device must acknowledge that it recognizes its address. After receiving the acknowledge, the master will transmit one or more bytes of commands and data. If the slave device is an EEPROM the command is the address within the EEPROM that is to be read or written. If data is to be written to the EEPROM the master transmits it after the command.

### START and STOP Conditions

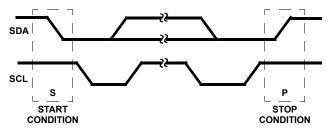

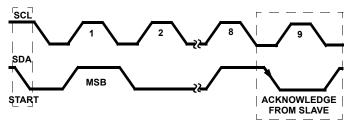

As shown in Figure 1, START condition is a HIGH to LOW transition of the SDA line while SCL is HIGH.

The STOP condition is a LOW to HIGH transition on the SDA line while SCL is HIGH. A STOP condition must be sent before each START condition.

FIGURE 1. START AND STOP WAVEFORMS

### **Data Validity**

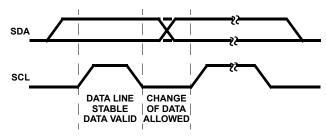

The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. Refer to Figure 2.

**FIGURE 2. DATA VALIDITY**

### Byte Format

Every byte put on the SDA line must be eight bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit first (MSB).

### Acknowledge

The master (microprocessor) puts a resistive HIGH level on the SDA line during the acknowledge clock pulse (Figure 3). The peripheral that acknowledges has to pull down (LOW) the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during this clock pulse. (Of course, set-up and hold times must also be taken into account.)

The peripheral which has been addressed has to generate an acknowledge after the reception of each byte, otherwise the SDA line remains at the HIGH level during the ninth clock pulse time. In this case, the master transmitter can generate the STOP information in order to abort the transfer.

FIGURE 3. ACKNOWLEDGE ON THE I<sup>2</sup>C BUS

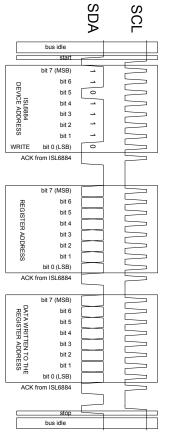

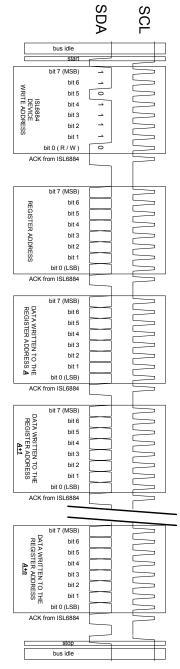

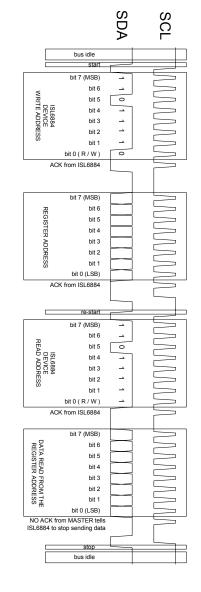

# Transactions Between the System Master and the ISL6884

Below are typical transactions between the system master and the ISL6884

### WRITING TO ONE REGISTER IN ISL6884

## WRITING N CONSECUTIVE REGISTERS TO ISL6884

### **READING ONE REGISTER IN ISL6884**

## READING CONSECUTIVE REGISTER FROM ISL6884

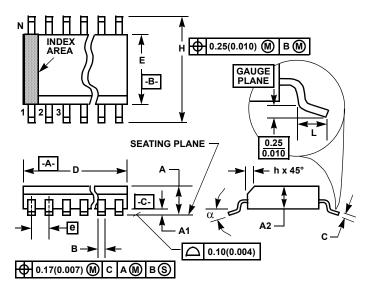

### Shrink Small Outline Plastic Packages (SSOP) Quarter Size Outline Plastic Packages (QSOP)

### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- Dimension "B" does not include dambar protrusion. Allowable dambar protrusion shall be 0.10mm (0.004 inch) total in excess of "B" dimension at maximum material condition.

- 10. Controlling dimension: INCHES. Converted millimeter dimensions are not necessarily exact.

M20.15

20 LEAD SHRINK SMALL OUTLINE PLASTIC PACKAGE (0.150" WIDE BODY)

|        | INCHES |        | MILLIM    | ETERS |       |

|--------|--------|--------|-----------|-------|-------|

| SYMBOL | MIN    | MAX    | MIN       | MAX   | NOTES |

| Α      | 0.053  | 0.069  | 1.35      | 1.75  | -     |

| A1     | 0.004  | 0.010  | 0.10      | 0.25  | -     |

| A2     | -      | 0.061  | -         | 1.54  | -     |

| В      | 0.008  | 0.012  | 0.20      | 0.30  | 9     |

| С      | 0.007  | 0.010  | 0.18      | 0.25  | -     |

| D      | 0.337  | 0.344  | 8.56      | 8.74  | 3     |

| Е      | 0.150  | 0.157  | 3.81      | 3.98  | 4     |

| е      | 0.025  | BSC    | 0.635 BSC |       | -     |

| Н      | 0.228  | 0.244  | 5.80      | 6.19  | -     |

| h      | 0.0099 | 0.0196 | 0.26      | 0.49  | 5     |

| L      | 0.016  | 0.050  | 0.41      | 1.27  | 6     |

| N      | 20     |        | 20        |       | 7     |

| α      | 0°     | 8°     | 0°        | 8°    | -     |

Rev. 1 6/04

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com