# SanKer

# SLA707xM Series

February, 2006

### **■**General Description

Combining low-power CMOS logic with high-current, high-voltage power FET outputs, the Series SLA707xM translator/drivers provide complete control and drive for a two-phase unipolar stepper motor with internal fixed off time and pulse-width modulation (PWM) control of the output current in a power multi-chip module (PMCMTM)

There are no phase-sequence tables, high-frequency control lines, or complex interfaces to program. The CMOS logic section provides the sequencing logic, direction, control, synchronous/asynchronous PWM operation, and a "sleep" function. The minimum CLOCK input is an ideal fit for applications where a complex  $\mu P$  is unavailable or overburdened. TTL or LSTTL may require the use of appropriate pull-up resistors to ensure a proper input-logic high. For PWM current control, the maximum output current is determined by the user's selection of a reference voltage and sensing resistor. The NMOS outputs are capable of sinking up to 1, 1.5, 2, or 3 A (depending on device) and withstanding 46 V in the off state.

Clamp diodes provide protection against inductive transients. Special power-up sequencing is not required.

Full-, and Half-step operation are externally selectable for the SLA7070/71/72/73MR. Full-, Half-, quarter-, and eighth-, and sixteenth-step operation are externally selectable for the SLA7075/76/77/78MR.

Half-step excitation alternates between the one-phase and two-phase modes (A-AB-B-AB-A-AB-BAB), providing an eight-step sequence.

### **■**Applications

- PPC

- Printer

- OA Equipment

### **■**Features

- To 3 A Output Rating

- Internal Sequencer for Microstepping Operation

- PWM Constant-Current Motor Drive

- Cost-Effective, Multi-Chip Solution

- 100 V, Avalanche-Rated NMOS Outputs

- Low RDS(on) NMOS Outputs (150 milliohms typical)

- Advanced, Improved Body Diodes

- Inputs Compatible with 3.3 V or 5 V Control Signals

- Sleep Mode

- Internal Clamp Diodes

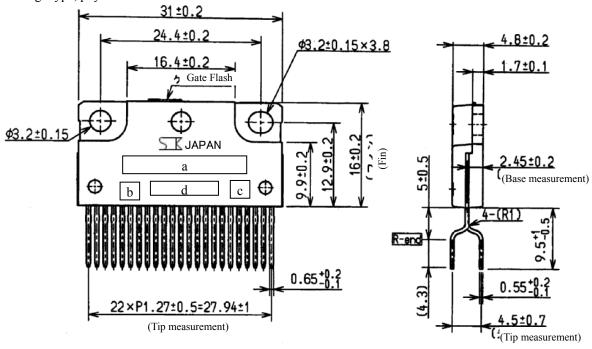

### ■Package—SLA23Pin

### **■**Key Specifications

- Motor Supply Voltage (VM): 44V max

- Load Supply Voltage (Vs): 10V to 44V

- Logic Supply Voltage (Vcc): 3V to 5.5V

- Output Current (Io): 1A(SLA7070MxRxx, SLA7075MxRxx)

1.5 A (SLA7071 Mx Rxx, SLA7076 Mx Rxx)

2A(SLA7072MxRxx, SLA7077MxRxx)

3A(SLA7073MxRxx, SLA7078MxRxx)

The x represents P, W, or R according to the functions (See App Note).

• Output Maximum Voltage (V<sub>DSS</sub>): 100V min

### **Typical Connection** Vs=10V~44V VBB Clock CW/CCW Ь м1 SLA707xMR M2 5 мз Sync N.C. Ref/Sleep1 SenseB r2≹ r3≷ Power Ground Logic Ground Ground

February, 2006

### Scope

The present specifications shall apply to a micro-stepping capable 2-phase unipolar stepper motor driver IC, SLA7077MR and shall apply to the devices compliant with RoHS Directive. Lead part solder: Pb free. Inner solder: Containing Pb > 85%.

### **Outline**

| Туре         | Hybrid integrated circuit                                                                 |

|--------------|-------------------------------------------------------------------------------------------|

| Structure    | Plastic molded (transfer mold)                                                            |

| Applications | To drive a 2-phase stepper motor. (Micro-Stepping Capable. PWM Constant-Current Control.) |

### Absolute maximum ratings

| Parameter                   | Symbol            | Ratings                      | Unit | Remarks            |

|-----------------------------|-------------------|------------------------------|------|--------------------|

| Load Supply Voltage         | $V_{\mathrm{M}}$  | 46                           | V    |                    |

| Main Power Supply Voltage   | $V_{\mathrm{BB}}$ | 46                           | V    |                    |

| Logic Supply Voltage        | $V_{ m DD}$       | 7                            | V    |                    |

| Output Current              | I <sub>O</sub>    | 2.0*                         | A    | Vref=0.4V, Mode F  |

| Logic Input Voltage         | V <sub>IN</sub>   | -0.3 to V <sub>DD</sub> +0.3 | V    |                    |

| REF Input Voltage           | $V_{REF}$         | -0.3 to V <sub>DD</sub> +0.3 | V    |                    |

| Sense Voltage               | VRS               | ±2                           | V    | Except for tw<1 µs |

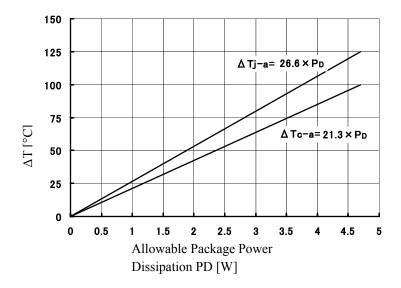

| Dower Dissination           | PD                | 4.7 W At Ta=25°C             |      | At Ta=25°C         |

| Power Dissipation           | PD                | 17                           | W    | At Tc=25°C         |

| Junction Temperature        | Tj                | 150                          | °C   |                    |

| Operating Temperature Range | Ta                | -20 to 85                    | °C   |                    |

| Storage Temperature Range   | Tstg              | -30 to 150                   | °C   |                    |

<sup>\*</sup>Output current rating may be limited by duty cycle, ambient temperature, and heat sinking. Under any conditions, do not exceed the specified junction temperature( $T_i$ ).

<sup>\*</sup> Please refer to the electric characteristics in the application note for other devices of the series.

February, 2006

### **Electrical characteristics**

Recommendable Operating Range

| Parameter                       | Symbol           | Ratings |       | Unit | Remarks                      |

|---------------------------------|------------------|---------|-------|------|------------------------------|

| Farameter                       | Syllibol         | MIN     | MAX   | Omt  | Remarks                      |

| Load Supply Voltage             | $V_{\mathrm{M}}$ |         | 44    | V    |                              |

| Main Power Supply Voltage Range | $V_{BB}$         | 10      | 44    | V    |                              |

| Logic Supply Voltage Range      | $V_{ m DD}$      | 3.0     | 5.5   | V    | Please adjust the Vcc surge  |

| Logic Supply Voltage Range      | <b>•</b> DD      |         |       |      | voltage to 0.5V or less.     |

| DEE Innut Voltage Dange         | W                | 0.04    | 0.4   | V    | The control current accuracy |

| REF Input Voltage Range         | $V_{REF}$        | 0.04    | 0.4 V |      | decreases in 0.1V or less.   |

| Casa Tamparatura                | т                |         | 90    | °C   | 12Pin temperature            |

| Case Temperature                | $T_{\rm C}$      |         | 90    |      | (With no Fin)                |

Electrical Characteristic (T<sub>a</sub>=25°C,V<sub>BB</sub>=24V,V<sub>DD</sub>=5V Unless Otherwise Noted.)

| Donomoton                  | Complete 1         |              | Limits |                        |      | Test Condition             |  |

|----------------------------|--------------------|--------------|--------|------------------------|------|----------------------------|--|

| Parameter                  | Symbol             | Min.         | Тур.   | Max.                   | Unit | Test Condition             |  |

| Main Power Supply Current  | $I_{BB}$           |              |        | 15                     | mA   | Regularity                 |  |

| Main I ower Supply Current | $I_{BBS}$          |              |        | 100                    | μΑ   | at SLEEP operation         |  |

| Logic Supply Current       | $I_{DD}$           |              |        | 5                      | mA   |                            |  |

| Drain-Source Breakdown     | V                  | 100          |        |                        | V    | $V_{BB}=44V$               |  |

| Diani-Source Breakdown     | $V_{(BR)DS}$       | 100          |        |                        | V    | $I_D=1mA$                  |  |

| Output On Resistance       | $R_{DS(on)}$       |              | 0.25   | 0.4                    | Ω    | Io=2A                      |  |

| Body Diode Forward Voltage | $V_{F}$            |              | 0.95   | 1.2                    | V    | Io=2A                      |  |

| Maximum Clock Frequency    | $f_{clk}$          | 250*         |        |                        | kHz  | duty=50%                   |  |

| Logic Input Voltage        | $V_{\rm LIL}$      |              |        | $0.25~\mathrm{V_{DD}}$ | V    |                            |  |

| Logic input voltage        | $V_{\mathrm{LIH}}$ | $0.75V_{DD}$ |        |                        | V    |                            |  |

| Logic Input Current        | $I_{LIL}$          |              | ±1     |                        | μΑ   |                            |  |

| Logic input Current        | $I_{LIH}$          |              | ±1     |                        | μΑ   |                            |  |

| REF Input Voltage Range    | $V_{REF}$          | 0            |        | 0.45                   | V    | Stationary current control |  |

| KLI input voitage Kange    | $V_{REFS}$         | 2.0          |        | $V_{DD}$               | V    | at SLEEP operation         |  |

<sup>\*</sup>Operation at a step frequency greater than the specified minimum value is possible but not warranted.

Note.

Negative current is defined as the outflowing current from the specified pin.

February, 2006

| REF Input Current    | $I_{REF}$ |                | ±10 |      | μA | $V_{REF}=0$ to $V_{DD}$     |

|----------------------|-----------|----------------|-----|------|----|-----------------------------|

| Logic Output Voltage | $V_{LOL}$ |                |     | 1.25 | V  | $I_{LOL} = 1.25 \text{mA}$  |

| Logic Output voltage | $V_{LOH}$ | $V_{DD}$ -1.25 |     |      | V  | $I_{LOH} = -1.25 \text{mA}$ |

| Logio Output Current | $I_{LOL}$ |                |     | 1.25 | mA |                             |

| Logic Output Current | $I_{LOH}$ | -1.25          |     |      | mA |                             |

Operation at a step frequency greater than the specified minimum value is possible but not warranted.

Note.

Negative current is defined as the outflowing current from the specified pin.

Electrical Characteristic(continued) (T<sub>a</sub>=25°C,V<sub>BB</sub>=24V,V<sub>DD</sub>=5V Unless Otherwise Noted.)

| Characteristic Continues     |                      | C, <b>v</b> BB -24 | Limits |       |      |                                  |

|------------------------------|----------------------|--------------------|--------|-------|------|----------------------------------|

| Characteristic               | Symbol               | Min.               | Тур.   | Max.  | Unit | Test Condition                   |

| Sense Voltage                | $V_{SENSE}$          |                    | 0.3    |       | V    | V <sub>REF</sub> =0.3V<br>Mode F |

| Current detection Resistance | Rs                   | 0.199              | 0.205  | 0.211 | Ω    |                                  |

|                              | Mode F               |                    | 100    |       | %    |                                  |

|                              | Mode E               |                    | 98.1   |       | %    |                                  |

|                              | Mode D               |                    | 95.7   |       | %    |                                  |

|                              | Mode C               |                    | 92.4   |       | %    |                                  |

|                              | Mode B               |                    | 88.2   |       | %    |                                  |

|                              | Mode A               |                    | 83.1   |       | %    |                                  |

|                              | Mode 9               |                    | 77.3   |       | %    | $V_{REF}=0.04V$ to               |

| Step Reference Current Ratio | Mode 8               |                    | 70.7   |       | %    | 0.4V                             |

|                              | Mode 7               |                    | 63.4   |       | %    |                                  |

|                              | Mode 6               |                    | 55.5   |       | %    |                                  |

|                              | Mode 5               |                    | 47.1   |       | %    |                                  |

|                              | Mode 4               |                    | 38.2   |       | %    |                                  |

|                              | Mode 3               |                    | 29.0   |       | %    |                                  |

|                              | Mode 2               |                    | 19.5   |       | %    |                                  |

|                              | Mode 1               |                    | 9.8    |       | %    |                                  |

| Wake-Up time                 | $t_{ m SE}$          | 100                |        |       | μs   | Sleep1 & Sleep2                  |

| Switching Time               | $t_{pdon}$           |                    | 2.0    |       | μs   | Clock→Out ON                     |

| Switching Time               | $t_{pdoff}$          |                    | 1.5    |       | μs   | Clock→Out OFF                    |

| PWM Minimum On Time          | t <sub>ON(min)</sub> |                    | 1.7    |       | μs   |                                  |

|                              | t <sub>OFF1</sub>    |                    | 12     |       | μs   | Mode 8 to F                      |

| PWM OFF Time                 | t <sub>OFF2</sub>    |                    | 9      |       | μs   | Mode 4 to 7                      |

|                              | t <sub>OFF3</sub>    |                    | 7      |       | μs   | Mode 1 to 3                      |

Note.

<sup>•</sup> Negative current is defined as coming out of the specified pin.

February, 2006

### Thermal Design Data

### Truth Table

### • Input Pin

| Name   | Low Level                  | High Level                | Clock |

|--------|----------------------------|---------------------------|-------|

| Reset  | Run                        | Logic Reset               | -     |

| CW/CCW | Forward (CW)               | Reverse(CCW)              |       |

| M1     |                            |                           |       |

| M2     | Micro-Stepping Ope         | <b>_</b>                  |       |

| M3     |                            |                           |       |

| Ref    |                            | Sleep Mode 1*             | -     |

| Sync   | Asynchronous PWM Operation | Synchronous PWM Operation | -     |

<sup>\*</sup> With a setup of a sleep mode 1, the operation is "Output Disable" and "Sequencer Enable"

February, 2006

### Micro-Stepping Operation Mode Setting

| Operation Mode         | M1 | M2 | M3 | Remarks              |

|------------------------|----|----|----|----------------------|

| 2 Phase(1 Step)        | L  | L  | L  | Mode 8 only          |

| 2Phase(1 Step)         | Н  | L  | L  | Mode F only          |

| 1-2 Phase(1/2 Step)    | L  | Н  | L  | Mode 8, F            |

| 1-2 Phase(1/2 Step)    | Н  | Н  | L  | Mode F               |

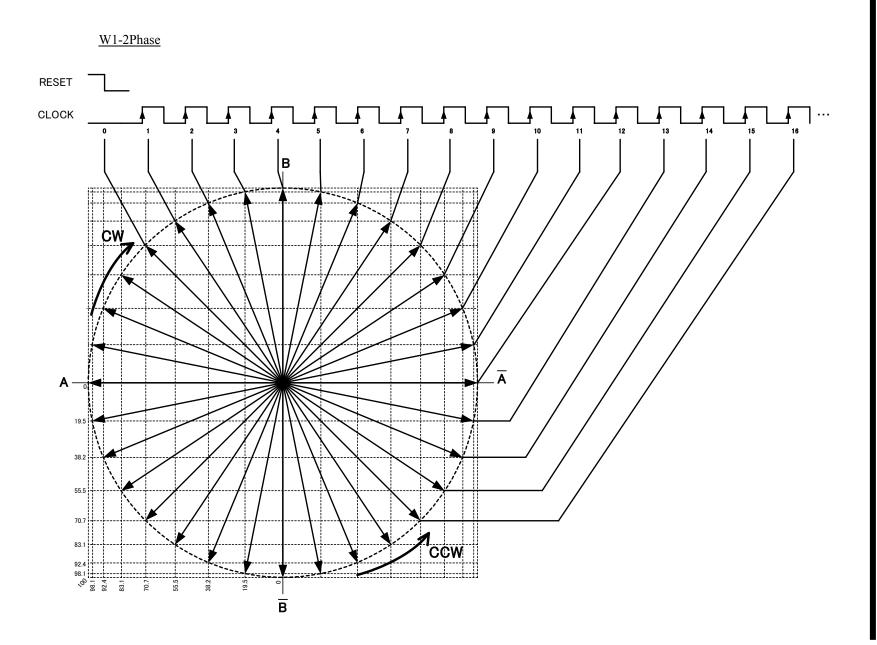

| W1-2 Phase(1/4 Step)   | L  | L  | Н  | Mode 4,8,C,F         |

| W1-2 Phase(1/8 Step)   | Н  | L  | Н  | Mode 2,4,6,8,A,C,E,F |

| 4W1-2 Phase(1/16 Step) | L  | Н  | Н  | Mode 1 to F          |

| Sleep Mode 2*          | Н  | Н  | Н  |                      |

<sup>\*</sup> With a setup of a sleep mode 2, the operation is "Output Disable" and "Sequencer Hold". Sleep mode 2 operates without depending on the Clock.

### Output Pin

| Pin Name | High Level                  | Low Level |

|----------|-----------------------------|-----------|

| Mo       | Half-Step Position (Mode 8) | -         |

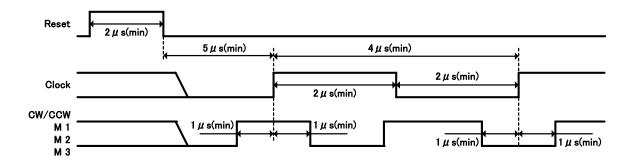

### Logic Input Timing Requirements

February, 2006

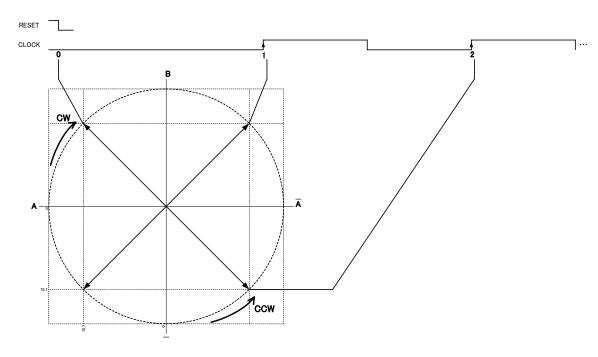

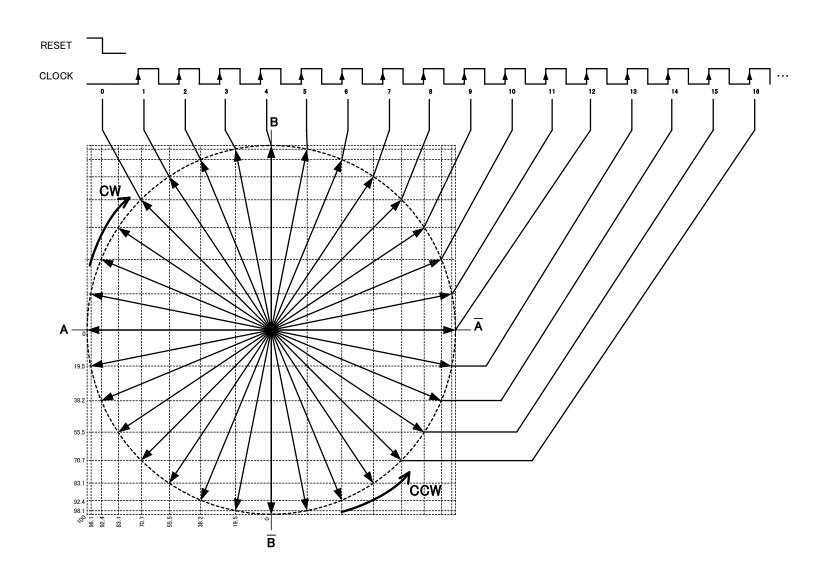

Step Sequencing Chart

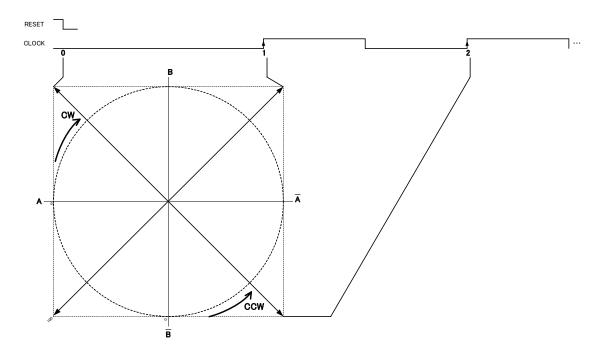

### 2Phase

Mode: 8 M1: L, M2: L, M3: L

Mode: F M1: H, M2: L, M3: L

February, 2006

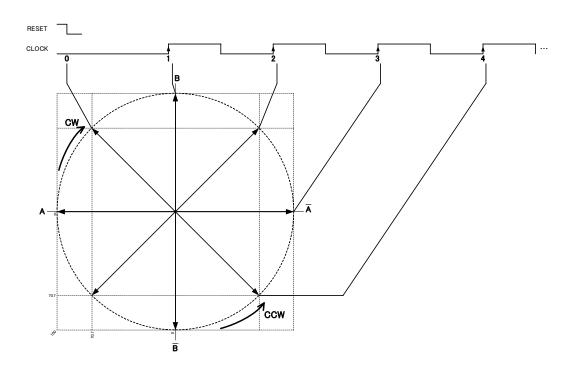

1-2Phase

Mode: 8 <=> F M1: L, M2: H, M3: L

Mode: F M1:H, M2: H, M3: L

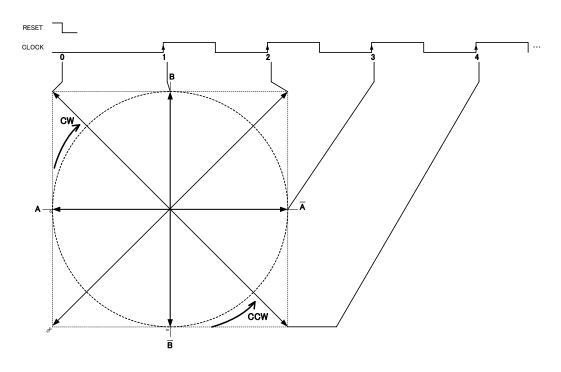

# 2-Phase Unipolar Stepper Motor Driver SLA707xM Series

February, 2006

February, 2006

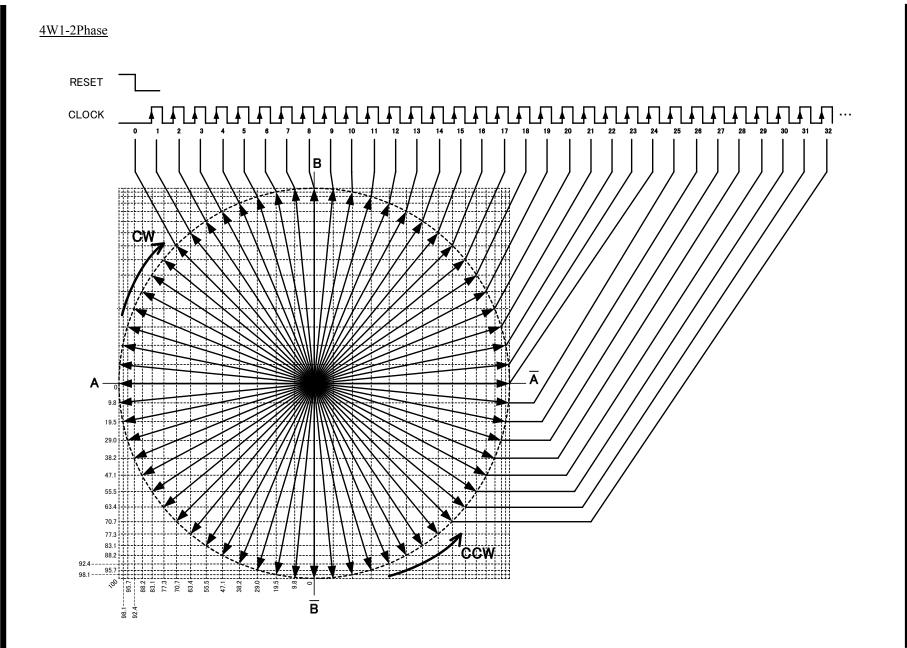

### 2W1-2Phase

February, 2006

February, 2006

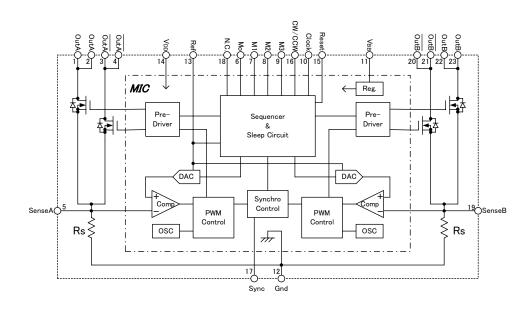

### **Block diagram (Connection diagram)**

Internal functional block diagram

Pin Assignment (Terminal Functions)

| Pin No. | Symbol      | Function                           |

|---------|-------------|------------------------------------|

| 1, 2    | Out A       | Phase A Output                     |

| 3, 4    | Out A/      | Phase A/ Output                    |

| 5       | Sense A     | Phase A Current Sense              |

| 6       | Mo          | Position Monitoring Output         |

| 7       | M1          | Micro-Stepping Operation Mode and  |

| 8       | M2          | Sleep Mode 2 Setting Input         |

| 9       | M3          | Sieep Wode 2 Setting input         |

| 10      | Clock       | Step Clock Input                   |

| 11      | $V_{ m BB}$ | Main Power Supply (For Motor)      |

| 12      | Gnd         | GND                                |

| 13      | Ref         | Control Current and Sleep Mode 1   |

| 13      | KCI         | Setting Input.                     |

| 14      | $V_{ m DD}$ | Logic Supply                       |

| 15      | Reset       | Reset Input for Logic Circuit      |

| 16      | CW/CCW      | Forward / Reverse Switch Input     |

| 17      | Sync        | PWM Chopping Function Select Input |

| 18      | N.C.        | Non Connection                     |

| 19      | Sense B     | Phase B Current Sense              |

| 20, 21  | Out B/      | Phase B/ Output                    |

| 22, 23  | Out B       | Phase B Output                     |

February, 2006

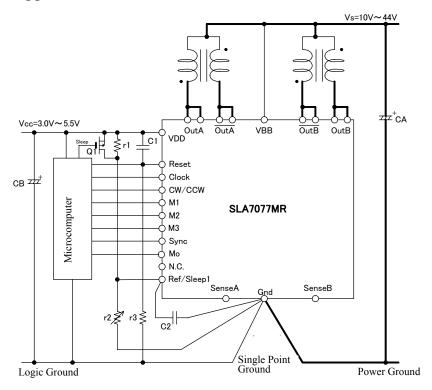

### **Example application circuit**

### Reference constant

$$\begin{split} R_1 &= 10k\Omega & C_A &= 100\mu F/50V \\ R_2 &= 5.1k\Omega(VR) & C_B &= 10\mu F/10V \\ R_3 &= 10k\Omega & C_1 &= 0.1\mu F \end{split}$$

Take precautions to avoid noise on the V<sub>DD</sub> line:

Switching noise from PCB traces, where high current flows, to the V<sub>DD</sub> line should be minimized because the noise level more than 0.5V on the V<sub>DD</sub> line may cause malfunctioning operation.

The tip for avoiding such problem is to separate the logic GND (S-GND) and the power GND (P-GND) on the PCB, and then connect them together at IC GND pin (pin 12).

February, 2006

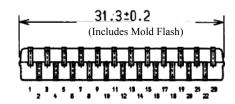

### **Package information**

Package type, physical dimensions and Material

Dimensions in millimeters Material of terminal : Cu

Treatment of terminal: Ni planting + solder dip (Pb Free)

Appearance

The body shall be clean and shall not bear any stain, rust or flaw. Marking

The part number and lot number shall be clearly marked in white.

a. Part Number (1) SLA707xMR\* W B b. Part Number (2) (Marked per functions.)\* c. Part Number (3) (Marked per functions.)\* d. Lot Number 1st letter The last digit of year 2nd letter Month 1 to 9 : Arabic Numerals for Jan. to Sep. October: O November: N December: D 3rd &4th letter Day

\* The letter x in Part Number (1) represents one number from 0 to 3 and 5 to 8 according to the combination of the current rating and sequencer.

01 to 31 : Arabic Numerals

The letter P, R, W, B represent the functions built-in. (No marking for non built-in functions.)

February, 2006

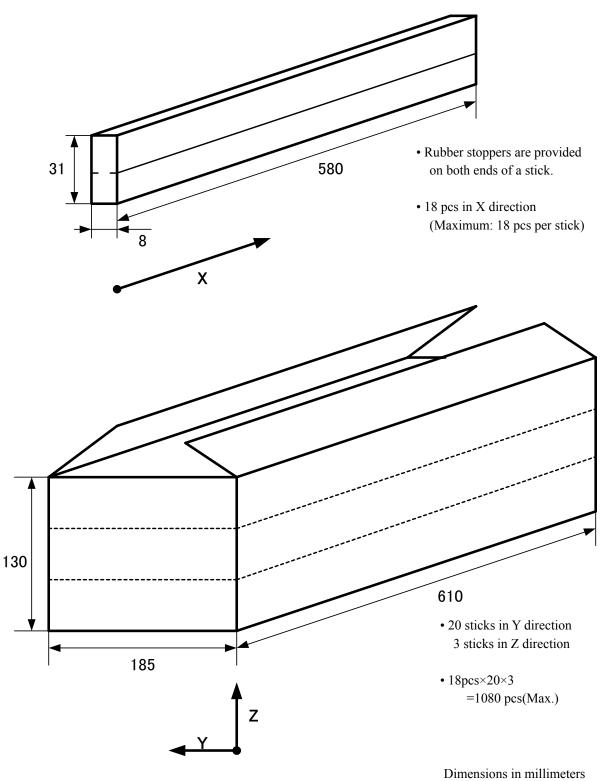

### **Packing specifications**

1

February, 2006

### Cautions and warnings

The calculation of control current

SLA707xMR control current Io (at Mode F) is calculated as follows:

$$I_O = \frac{V_{REF}}{R_S}$$

Setting the REF voltage more than 2V activates the sleep mode 1 (all outputs are in OFF state).

Even in this case, the internal logic circuit is alive.

Logic input/output (RESET, CLOCK, CW/CCW, M1, M2, M3, SYNC, Mo)

- The timing shown below shall comply with the "Logic input timing".

- -The rising edge timing of CW/CCW, M1, M2, M3 and CLOCK input

- -The RESET release timing (=the falling edge on RESET input) and the rising edge timing of CLOCK input

- \*In case the above does not comply with the "Logic input timing", the device may operate with an unexpected sequence.

- Be sure not to leave the logic inputs (RESET, CLOCK, CW/CCW, M1, M2, M3, SYNC) open. Be sure to connect the unused logic inputs to VDD or GND.

- \*In case any of the logic inputs are left "OPEN", malfunction may occur due to external noises.

- When the logic output (Mo) is not used, be sure to keep it "OPEN".

- \*In case it is connected to VDD or GND, it may cause the device's deterioration or/and breakdown.

Mounting on a heat sink

1) Recommended Mounting Torque (on an External Heat sink)

0.490 to 0.822N•m

2) Recommended Silicone

G746 {SHIN-ETSU CHEMICAL} YG6260 {TOSHIBA SILICONE}

SC102 {DOW CORNING TORAY SILICONE}

February, 2006

### Notice

This device has C-MOS inputs. Please note the following contents.

- When a static electricity is liable to be troublesome, especially in winter, be sure to control the room humidity properly.

- Be sure to take some proper measures for wirings from the IC input pins and for assembly processes in order not to apply static charges to IC leads. PC board pins should be shorted together to keep them in the same potential to avoid this kind of trouble.

February, 2006

### <Worldwide Contacts>

### **Asia Pacific**

### China

### Sanken Electric Hong Kong Co., Ltd.

Suite 1026 Ocean Centre, Canton Road, Tsimshatsui, Kowloon, Hong Kong

Tel: 852-2735-5262 Fax: 852-2735-5494

### Sanken Electric (Shanghai) Co., Ltd.

Room3202, Maxdo Centre, Xingyi Road 8, Changning district, Shanghai, China

Tel: 86-21-5208-1177 Fax: 86-21-5208-1757

### Taiwan Sanken Electric Co., Ltd.

Room 1801, 18th Floor, 88 Jung Shiau East Road, Sec. 2, Taipei 100, Taiwan R.O.C.

Tel: 886-2-2356-8161 Fax: 886-2-2356-8261

### India

### Saket Devices Pvt. Ltd.

Office No.13, First Floor, Bandal - Dhankude Plaza, Near PMT Depot, Paud Road, Kothrud, Pune - 411 038, India

Tel: 91-20-5621-2340 91-20-2528-5449 Fax: 91-20-2528-5459

### <u>Japan</u>

### Sanken Electric Co., Ltd. Overseas Sales Headquaters

Metropolitan Plaza Bldg. 1-11-1 Nishi-Ikebukuro, Toshima-ku, Tokyo 171-0021, Japan

Tel: 81-3-3986-6164 Fax: 81-3-3986-8637

### Korea

### Sanken Electric Korea Co., Ltd.

Mirae Asset Life Bldg. 6F, 168 Kongduk-dong, Mapo-ku, Seoul, 121-705, Korea

Tel: 82-2-714-3700 Fax: 82-2-3272-2145

### **Singapore**

### Sanken Electric Singapore Pte. Ltd.

150 Beach Road, #14-03 The Gateway West, Singapore 189720

Tel: 65-6291-4755 Fax: 65-6297-1744

February, 2006

### **Europe**

### **United Kingdom**

Sanken Power Systems (UK) Limited

Pencoed Technology Park, Pencoed, Bridgend CF35 5HY. UK

Tel: 44-1656-869-100 Fax: 44-1656-869-162

### **North America**

### **United States**

Allegro MicroSystems, Inc.

115 Northeast Cutoff, Worcester, Massachusetts 01606, U.S.A.

Tel: 1-508-853-5000 Fax: 1-508-853-3353

### Allegro MicroSystems, Inc. (Southern California)

14 Hughes Street, Suite B105, Irvine, CA 92618

Tel: 1-949-460-2003 Fax: 1-949-460-7837

February, 2006

### **CAUTION / WARNING**

- •The information in this publication has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies.

- Sanken reserves the right to make changes without further notice to any products herein in the interest of

improvements in the performance, reliability, or manufacturability of its products.

Before placing an order, Sanken advises its customers to obtain the latest version of the relevant information to verify

that the information being relied upon is current.

- Application and operation examples described in this catalog are quoted for the sole purpose of reference for the use of the products herein and Sanken can assume no responsibility for any infringement of industrial property rights, intellectual property rights or any other rights of Sanken or any third party which may result from its use.

- When using the products herein, the applicability and suitability of such products for the intended purpose or object shall be reviewed at the users' responsibility.

- Although Sanken undertakes to enhance the quality and reliability of its products, the occurrence of failure nd defect of semiconductor products at a certain rate is inevitable. Users of Sanken products are requested to take, at their own risk, preventative measures including safety design of the equipment or systems against any possible injury, death, fires or damages to the society due to device failure or malfunction.

- Sanken products listed in this catalog are designed and intended for the use as components in general purpose electronic equipment or apparatus (home appliances, office equipment, telecommunication equipment, measuring equipment, etc.). Before placing an order, the user's written consent to the specifications is requested. When considering the use of Sanken products in the applications where higher reliability is required (transportation equipment and its control systems, traffic signal control systems or equipment, fire/crime alarm systems, various safety devices, etc.), please contact your nearest Sanken sales representative to discuss and obtain written confirmation of your specifications. The use of Sanken products without the written consent of Sanken in the applications where extremely high reliability is required (aerospace equipment, nuclear power control systems, life support systems, etc.) is strictly prohibited.

- Anti radioactive ray design is not considered for the products listed herein.

- This publication shall not be reproduced in whole or in part without prior written approval from Sanken.

- This is notification that you, as purchaser of the products/technology, are not allowed to perform any of the following:

- 1. Resell or retransfer these products/technology to any party intending to disturb international peace and security.

- 2. Use these products/technology yourself for activities disturbing international peace and security.

- 3. Allow any other party to use these products/technology for activities disturbing international peace and security. Also, as purchaser of these products/technology, you agree to follow the procedures for the export or transfer of these products/technology, under the Foreign Exchange and Foreign Trade Law, when you export or transfer the products/technology abroad.